# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/109060/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Eblabla, A., Li, X., Wallis, D. J., Guiney, I. and Elgaid, K. 2018. High-performance MMIC inductors for GaN-on-low-resistivity silicon for microwave applications. IEEE Microwave and Wireless Components Letters 28 (2), pp. 99-101. 10.1109/LMWC.2018.2790705

Publishers page: http://dx.doi.org/10.1109/LMWC.2018.2790705

# Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# High-Performance MMIC Inductors for GaN-on-Low-Resistivity Silicon for Microwave Applications

A. Eblabla<sup>©</sup>, X. Li, D. J. Wallis, I. Guiney, and K. Elgaid

Abstract—Novel MMIC spiral inductors on GaN-on-low-resistivity silicon (LR-Si) substrates ( $\sigma$  < 40  $\Omega$  · cm) are demonstrated with enhanced self-resonance frequency ( $f_{\rm SRF}$ ) and Q-factor. The developed technology improves inductor performance by suppressing substrate coupling effects using air-bridge technology above benzocyclobutene dielectric as an interface layer on the lossy substrate. A 0.83-nH spiral inductor with peak Q-factor enhancement of 57% (Q = 22 at 24 GHz) and maximum  $f_{\rm SRF}$  of 59 GHz was achieved because of the extra 5- $\mu$ m elevation in air. An accurate broad-band model for the fabricated inductors has been developed and verified for further performance analysis up to 40 GHz. The proposed inductors utilize cost-effective, reliable, and MMIC-compatible technology for the realization of high-performance RF GaN-on-LR Si MMIC circuits for millimeter-wave applications.

$\label{localization} \emph{Index Terms} - \text{Benzocyclobutene} \quad (\text{BCB}), \quad \text{GaN-based high-electron-mobility transistors} \quad (\text{HEMTs}), \quad \text{high-} Q \quad \text{Inductors, low-resistivity silicon substrates, millimeter wave.}$

#### I. Introduction

aN-BASED devices offer inherent advantages for the realization of power switches operation at high temperature and high power for millimeter-wave applications. For example, an envelope tracking bandwidth of 20 MHz with power device switching frequencies up to 200 MHz has been demonstrated due to the ongoing work on the integration of GaN high-electron-mobility-transistor (HEMT)-based gate drivers, and buck converters on insulating SiC substrates [1]. The potential use of this circuit for 5G applications using GaN on LR Si substrates, where both power and RF GaN devices featured on the same chip, will introduce the additional advantage of low cost and large diameter wafers, compared with high-resistivity Si and SiC technologies.

High-performance on-chip inductors are one of the key passive components in MMIC circuit implementation [2]. However, substrate parasitics are a major factor that would inhibit the realization of high-performance inductors, with

Manuscript received September 27, 2017; accepted October 26, 2017. This work was supported by the Engineering and Physical Sciences Research Council under Grant EP/N014820/1. (Corresponding author: A. Eblabla.)

A. Eblabla and X. Li are with the School of Engineering, University of Glasgow, Glasgow G12 8LP, U.K. (e-mail: a.eblabla.1@research.gla.ac.uk).

D. J. Wallis and I. Guiney are with the Cambridge Centre for GaN, University of Cambridge, Cambridge CB3 0FS, U.K.

K. Elgaid is with the School of Engineering, Cardiff University, Cardiff CF24 3AA, U.K. (e-mail: elgaidk@cardiff.ac.uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2018.2790705

high Q-factors and high  $f_{\rm SRF}$  especially at higher microwave frequencies [3]. Therefore, overcoming these parasitics in on-chip inductors remains a key challenge when considering GaN-on-LR Si as a substrate for high-power, high-frequency applications.

Efforts have been reported to enhance inductor characteristics at microwave frequencies, including substrate removal and increased substrate resistivity by ion bombardment [4], [5]. However, these techniques are hindered by the additional fabrication processes, and hence increased cost, to a standard MMIC fabrication. Recently, shielded-elevated CPW (SE-CPW) on benzocyclobutene (BCB) technology was presented as an optimum solution to overcome substrate coupling effects associated with the lossy substrate for GaN-on-LR Si technology [6]. Therefore, the integration of SE-CPW to high Q-factor and  $f_{\rm SRF}$  inductors using reliable and MMIC compatible technology must be investigated for the realization of successful MMIC circuits.

In this letter, we report on the realization of a cost-effective MMIC-compatible on-chip inductor technology with reduced parasitics using elevated traces on air and a BCB interface layer. Inductors with various inductance values (0.81–4.3 nH) are designed, fabricated, and characterized based on the extracted inductors model. A maximum Q of 22 at 24 GHz along with peak  $f_{\rm SRF}$  of 59 GHz was obtained for 0.81-nH inductors. The developed inductor technology is compatible with many III–V technologies up to K-band applications.

#### II. DEVICE FABRICATION

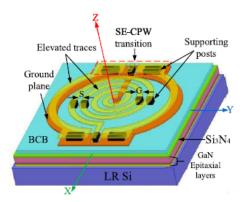

Inductors were fabricated on AlGaN/GaN HEMT layers grown on 1-mm-thick LR p-type Si (111) substrate, as shown in Fig. 1. Epitaxial layers and growth procedure are detailed in [7]. Optical lithography was used for all levels of device definition. As in a standard MMIC process, mesa isolation was initially performed followed by the deposition of a 200-nm Si<sub>3</sub>N<sub>4</sub> dielectric layer.

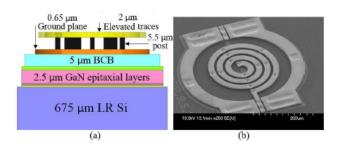

The fabrication process of the proposed MMIC spiral inductors started by spinning a 5- $\mu$ m-thick BCB film, which was subsequently fully cured at 250 °C in a N<sub>2</sub> atmosphere. A BCB thickness of 5  $\mu$ m was chosen, as greater dielectric thicknesses involve difficulties in creating via-holes connections through the BCB for device integration, and could cause additional inductance [6]. Next, alignment markers, SE-CPW ground planes, and inductor underpasses were patterned, followed by

Fig. 1. 3-D view of the fabricated MMIC spiral-elevated inductor integrated to 50- $\Omega$  SE-CPW on BCB.

Fig. 2. (a) Cross-sectional view. (b) SEM image of the fabricated elevated inductors.

the metallization and liftoff of a Ti/Au metal stack. Then, the SE-CPW and the inductor-elevated trace loops were achieved using standard air-bridge technology. Finally, the samples were metallized using  $2-\mu m$  Au electroplating (details of air-bridge fabrication process can be found in [8]). A final elevation high of 5.5  $\mu m$  was obtained. A cross-sectional view and scanned electron microscopy (SEM) images of the fabricated devices are shown in Fig. 2.

## III. INDUCTOR MODEL

Ansoft HFSS was employed to design the prefabricated devices to ensure best inductor performance. The geometrical parameters corresponding to peak Q-factor and  $f_{\rm SRF}$  for all inductor structures are found to be as follows: width  $(W) = 19~\mu{\rm m}$ , spacing  $(S) = 25~\mu{\rm m}$ , and an inner diameter of  $38~\mu{\rm m}$ .

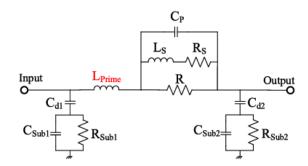

For better understanding of inductors' performance/loss mechanisms, an equivalent circuit model is required, especially at high frequencies (i.e., beyond the X-band). The proposed model (shown in Fig. 3) was extracted based on the measured S-parameters. The topology of this model is similar to that proposed in [5], where  $L_{\rm Prime}$  is the inductance, R represents the series resistance due to conductor loses, and  $R_S$  and  $L_S$  are the resistance and inductance associated with skin depth, respectively.  $C_P$  represents the capacitive coupling between the spiral turns and the underpass and between two adjacent spiral tracks.  $C_{d1}$  and  $C_{d2}$  represent the total capacitance between the spirals and conductive Si substrate (including both BCB and

Fig. 3. Schematic of the proposed equivalent circuit model of the fabricated elevated inductors.

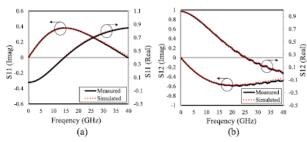

Fig. 4. Measured versus modeled (a) S11 and (b) S21 for a 3-turn spiralelevated inductor on BCB.

air dielectrics in series), and  $R_{\rm sub}$  and  $C_{\rm sub}$  are the substrate parameters. The circuit model was verified by the excellent agreement between modeled and measured S-parameters up to 40 GHz, as shown in Fig. 4.

# IV. MEASUREMENT RESULTS

On-wafer measurements of small-signal S-parameters were performed from 0.1 to 67 GHz. The system was calibrated to the probe tips using off-wafer line-reflect-reflect-match calibration. The measured S-parameters were then converted to Y-parameters, which were subsequently used to calculate the inductance and Q-factor of the fabricated devices [9].

To show the challenges involved in the design of highperformance inductors using SE-CPW technology, three different inductor technologies were realized: shielded-elevated inductors where ground planes were patterned on BCB underneath the elevated spiral loops, inductors fabricated directly on the BCB, and elevated inductors on BCB.

As shown in Fig 5, for the 3-turn inductors, the shielded-elevated inductor achieved the lowest performance, where a Q-factor of as poor as 4 at 17 GHz along with an  $f_{\rm SRF}$  of 34 GHz were measured. This could be because the conductive ground plane allows an image current to flow and the negative mutual coupling between the spiral plane and the ground plane reduces the inductance [10]. Using the patterned ground shield instead of solid ground shield can improve inductor performance, but it is limited to lower frequency range [11]. Q-factor and  $f_{\rm SRF}$  were further improved to 15 at 23 and 55 GHz, respectively, when fabricating the inductors directly on the BCB. Having the spiral loops elevated in air

Fig. 5. Comparison of the measured results of the fabricated MMIC inductors versus frequency. (a) Quality-factor. (b) Inductance.

TABLE I

EXTRACTED PARAMETERS FOR THE EQUIVALENT CIRCUIT IN FIG. 2

AND MEASURED Q-FACTOR AND fSRF OF THE INDUCTORS

| Parameter                         | N = 3       | N = 4 | N = 5 | N = 6 |  |  |

|-----------------------------------|-------------|-------|-------|-------|--|--|

| L <sub>Prime</sub> (nH)           | 0.815       | 1.517 | 2.677 | 4.304 |  |  |

| $L_s$ (nH)                        | 0.104       | 0.464 | 0.689 | 1.19  |  |  |

| $R_s(\Omega)$                     | 3.73        | 7.53  | 9.6   | 12.5  |  |  |

| $R(\Omega)$                       | 7.5         | 9.1   | 11.58 | 16.28 |  |  |

| C <sub>dI</sub> (fF)              | 18          | 19.5  | 24.7  | 30.06 |  |  |

| $C_{d2}(fF)$                      | 18.8        | 20.82 | 26.02 | 31.26 |  |  |

| $C_P$ (fF)                        | 2           | 3.4   | 6.8   | 14.4  |  |  |

| $R_{sub1}/R_{sub2}$ (K $\Omega$ ) | 15.8 / 13.3 |       |       |       |  |  |

| $C_{sub1}/C_{sub2}$ (fF)          | 2           |       |       |       |  |  |

| $f_{SRF}(GHz)$                    | 59          | 42    | 28    | 15    |  |  |

| Q-Factor (Peak)                   | 22          | 18    | 15    | 10    |  |  |

increased the Q-factor by 57% (Q=22 at 24 GHz and  $f_{\rm SRF}=59$  GHz) due to reduced substrate parasitics. However, inductors achieved lower performance at frequencies below X-band due to a finite conductor thickness of 2  $\mu$ m, where conductor losses are dominant [6]. This could be enormously improved by having thicker conductor metals (by increasing electroplating time during fabrication process). However, at higher frequency range, improvement to inductor performance by increasing the physical conductor thickness is limited by the saturation of the series resistance [12]. Therefore, this technique will not be effective in the millimeter-frequency range.

To further investigate the performance/loss mechanism of the best performing elevated inductors on BCB, inductors with various turns ( $N=3,\,4,\,5,\,$  and 6) were fabricated and modeled. The model parameters (indicated in Table I) are

determined using the S-parameters fitting technique. As shown in Table I, increasing N results in an increase in self-inductance due to the addition of the new conductors, and corresponding increase in the total mutual inductance of the device, resulting in the increase of the inductance value ( $L_{\rm Prime}$ ). However, as the inductor periphery increases,  $C_{d1}$  and  $C_{d2}$  and R will be dramatically increased, resulting in degradation of the Q-factor and  $f_{\rm SRF}$  [as shown in the results of the 6-turn inductors indicated in Fig. 5(a)].

### V. Conclusion

High-Q on-chip inductors employing elevated traces and a BCB interface layer have been realized on GaN-on-LR Si to reduce substrate coupling effects. Inductors with inductance varying from 0.81 to 4.3 nH were designed, fabricated, and characterized based on the extracted small-signal model. A peak Q-factor of 22 at 24 GHz and  $f_{\rm SRF}$  of 59 GHz was achieved for 0.81-nH inductors. The fabricated MMIC inductors offer a promising technology platform and can be integrated with RF GaN-HEMTs on LR Si for the realization of high-performance MMIC circuits for millimeter-wave applications.

#### REFERENCES

- [1] Y. P. Hong, K. Mukai, H. Gheidi, S. Shinjo, and P. M. Asbeck, "High efficiency GaN switching converter IC with bootstrap driver for envelope tracking applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Seattle, WA, USA, Jun. 2013, pp. 353–356.

- [2] M. Sudow et al., "An AlGaN/GaN HEMT-based microstrip MMIC process for advanced transceiver design," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 8, pp. 1827–1833, Aug. 2008.

- [3] L.-H. Lu, G. E. Ponchak, P. Bhattacharya, and L. P. B. Kateh, "High-Q X-band and K-band micromachined spiral inductors for use in Sibased integrated circuits," in *Topical Meetings Silicon Monolithic Integr.* Circuits RF Syst. Dig. Papers, Garmisch, Germany, 2000, pp. 108–112.

- [4] J. M. Yook, D. Kim, and J. C. Kim, "High-performance RF inductors and capacitors using the reverse trench structure of silicon," *IEEE Microw.* Wireless Compon. Lett., vol. 25, no. 11, pp. 709–711, Nov. 2015.

- [5] N. Li et al., "High-Q inductors on locally semi-insulated Si substrate by helium-3 bombardment for RF CMOS integrated circuits," *IEEE Trans. Electron Devices*, vol. 62, no. 4, pp. 1269–1275, Apr. 2015.

- [6] A. Eblabla, B. Benakaprasad, X. Li, D. J. Wallis, I. Guiney, and K. Elgaid, "Low-loss MMICs viable transmission media for GaN-on-low resistivity silicon technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 1, pp. 10–12, Jan. 2017.

- [7] A. Eblabla, X. Li, I. Thayne, D. J. Wallis, I. Guiney, and K. Elgaid, "High performance GaN high electron mobility transistors on low resistivity silicon for X-band applications," *IEEE Electron Device Lett.*, vol. 36, no. 9, pp. 899–901, Sep. 2015.

- [8] A. Eblabla, D. J. Wallis, I. Guiney, and K. Elgaid, "Novel shielded coplanar waveguides on GaN-on-low resistivity Si substrates for MMIC applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 7, pp. 427–429, Jul. 2015.

- [9] S. Chander, K. Bansal, S. Gupta, and M. Gupta, "Design and analysis of spiral circular inductors for GaN based low noise amplifier (MMICs)," in Proc. Int. Conf. Microw., Opt. Commun. Eng. (ICMOCE), Bhubaneswar, India, 2015, pp. 292–294.

- [10] C. P. Yue and S. S. Wong, "On-chip spiral inductors with patterned ground shields for Si-based RF ICs," in *Proc. Symp. VLSI Circuits*, 1997, pp. 85–86.

- [11] V. Zhurbenko, Advanced Microwave Circuits and Systems. Rijeka, Croatia: InTech. 2010, p. 291.

- [12] C. P. Yue and S. S. Wong, "Physical modeling of spiral inductors on silicon," *IEEE Trans. Electron Devices*, vol. 47, no. 3, pp. 560–568, Mar. 2000.