# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/112083/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Han, Yu, Li, Qiang and Lau, Kei May 2016. Monolithic integration of tunnel diode based inverters on exact (001) Si substrates. IEEE Electron Device Letters 37 (6), pp. 717-720. 10.1109/LED.2016.2552219

Publishers page: http://dx.doi.org/10.1109/LED.2016.2552219

### Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

## Monolithic Integration of Tunnel Diode Based Inverters on Exact (001) Si Substrates

Yu Han, Qiang Li, member, IEEE, and Kei May Lau, Fellow, IEEE

Abstract— Monolithic integration of tunnel diode based inverters on exact (001) Si substrates for future high speed, low power and compact digital circuits is demonstrated. A two-state inverter was fabricated using a forward biased fin-array tunnel diode as drive and a reverse biased counterpart as load. On-chip operation and reduced fabrication complexity were achieved by exploiting the resistive characteristic of the reverse-biased tunnel diodes and the pre-defined patterns on the Si substrate.

Index Terms— Tunnel diode, monolithic integration, inverter, digital circuits.

#### I. INTRODUCTION

he application of tunnel diodes in digital circuits has long been recognized for advantages such as picosecond switching speed, reduced device counts per circuit function and low power consumption [1-3]. The folded I-V characteristic empowered by quantum mechanical tunneling has been utilized to fabricate ultra-high speed and compact circuits [4]. A simple series connection of a tunnel diode with a resistor or transistor can produce a circuit with double and even multi-stable states [5]. The inverter characteristic of tunnel diodes when connected with a load resistor is an inseparable part in multi-value logic design such as multiplexers [5], multi-valued adders [6], and mask programmable multi-valued logic gate [7]. III-V based tunnel diodes usually exhibit enhanced performance due to reduced tunneling mass and direct bandgap as compared with their Si based counterparts. Both silicon and III-V based tunnel diode digital circuits have been fabricated on their respective substrates with off-chip resistive components [8-10]. However integration of III-V based digital circuits on conventional (001) Si substrates has not been explored.

Previously we have reported the fabrication and characterization of GaAs-InGaAs-GaAs tunnel diodes utilizing nano-scale fin-arrays grown on V-grooved Si by metal-organic chemical vapor deposition (MOCVD) [11]. Here, we present the monolithic integration of two-state inverters on exact (001) Si using the fabricated fin-array tunnel didoes with varying peak current densities. Off-chip components are completely eliminated by connecting the tunneling junctions with partially-etched GaAs fin-arrays. Compared with other tunnel diode based digital circuits, the tunnel diode based inverter

Manuscript received 2016; revised xxx. This work was supported by grants (Nos. 614313 and ITS/320/14) from the Research Grants Council of Hong Kong. The review of this letter was arranged by Editor xx.

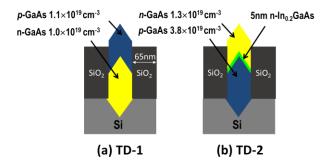

Fig. 1. Schematic of (a) TD-1 with a heavily doped p-GaAs/n-GaAs junction. (b) TD-2 with InGaAs insertion layer and reversed growth structure.

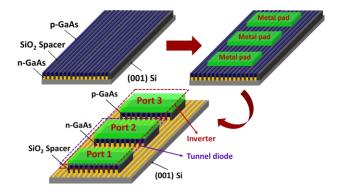

Fig. 2. Schematic and process flow of tunnel diodes and monolithically integrated inverters.

presented here features extremely simple fabrication procedures with one-step photolithography and a subsequent wet etching process. Such simplified integration scheme ensures identical metal-semiconductor interfaces for all contact electrodes and eliminates potential surface damage from otherwise subsequent processing.

#### II. DEVICE STRUCTURE AND FABRICATION

Two tunnel diode samples (TD-1 and TD-2) with fin-width of 65 nm were prepared on patterned (001) Si substrates using the same method detailed in [11], [12]. Fig. 1 depicts schematics of two different diode epitaxial structure designs. The p- and n-electrode of TD-2 was in reverse of TD-1, with an InGaAs middle layer. Electron and hole densities were calibrated through Hall measurements of n- and p-type GaAs thin films grown on planar semi-insulating GaAs substrates, respectively. Identical growth parameters were used for the growth of n- and p-regions of the tunnel diodes. The tunnel diodes and inverters were fabricated simultaneously using the process described in Fig. 2. Contact electrodes were formed by e-beam evaporation

Y. Han, Q. Li, and K.M. Lau are with the Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Kowloon, Hong Kong. (E-mail: eekmlau@ust.hk).

and a subsequent lift-off process. We chose Pt/Au stack to contact top p-GaAs fin-arrays in TD-1 and Ni/Ge/Au stack to contact top n-GaAs fin-arrays in TD-2. Using the patterned metal pads as a self-aligned mask, mesa etching (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 3:1:50) was performed to expose the underlying n-GaAs fin-arrays in TD-1 and p-GaAs fin-arrays in TD-2. After rinsing in DI water and blow-dry by N<sub>2</sub> gun, the devices were ready for measurement.

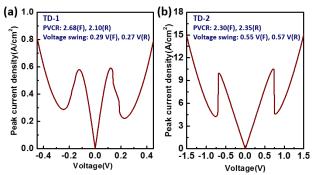

Fig. 3. Current-voltage characteristic of (a) TD-1 and (b) TD-2. (Note: F: forward bias, R: reverse bias).

#### III. RESULTS AND DISCUSSION

The current-voltage (IV) characteristics were measured by probing on Port 1 and Port 2 in Fig. 2. Fig. 3 shows I-V curves measured from devices with a metal-pad dimension of 100×100 μm<sup>2</sup>. Negative differential resistance (NDR) is clearly observed at room temperature. Unlike typical tunnel diodes with NDR only under forward bias, symmetric IV curves are obtained from our devices. Each tunnel diode is composed of two PN junctions connected in series. At either forward or reverse bias, one junction would be forward biased while the other is reverse biased. The kinks in the NDR region of TD-1 (Fig. 3(a)) indicate internal oscillation, commonly observed in the measurement of tunnel diodes [13]. A sharp transition in the NDR region accompanied by a large peak voltage (0.71 V) is observed in TD-2 (Fig. 3(b)), suggesting the presence of a large series resistance. Transmission line measurement (TLM) reveals a much larger contact resistance of 45 Ω·mm in TD-2 compared to TD-1 (8.6  $\Omega$ ·mm). At forward bias, the peak to valley current ratios (PVCR) are 2.68 and 2.30 for TD-1 and TD-2, respectively. TD-2 exhibits an order higher peak current density of 10.5 A/cm<sup>2</sup> (normalized to the area of the (111) GaAs surface), with an increased voltage swing of 0.55 V. At reverse bias, both TD-1 and TD-2 show characteristics comparable to forward bias. It is noted that higher PVCR (5.08 for TD-1 and 3.57 for TD-2) has been measured from devices with a dimension of  $40\times40 \,\mu\text{m}^2$ .

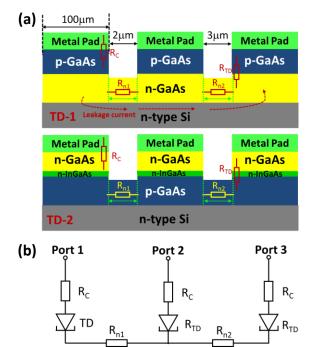

Tunnel diodes with a dimension of  $100\times100~\mu\text{m}^2$  were used to fabricate inverters for ease of measurement. Fig. 4(a) shows the cross-section view of an inverter along the direction of the fin-arrays. Three tunneling junctions are aligned in the V-grooved trenches and electrically connected by the partially etched GaAs fins. The distance between the tunneling junctions varies from 2  $\mu$ m to hundreds of microns to obtain various load values. The equivalent circuit of the inverter is depicted in Fig. 4(b).  $R_C$  refers to the contact resistance between the metal and GaAs fin-arrays, which was determined by TLM measurement.

$R_{TD}$  is the equivalent resistance of the reversely biased tunnel diodes and can be obtained by fitting the slope of the tunnel diode IV curve near the origin.  $R_{n1}$  and  $R_{n2}$  represent the resistive value of the GaAs fins connecting the tunneling junctions, which were calculated by measuring the peak voltage shift when varying the probing pad spacing. Table I summarizes the parasitic resistances corresponding to the specific dimensions in Fig. 4(a). It should be noted that medium-doped n-type Si substrates were used in this work. Leakage current through the Si substrate is mitigated by the reversed growth structure in TD-2 as compared to TD-1.

Fig. 4. (a) Cross section of the inverter along the direction of the GaAs fin-arrays. (b) Equivalent circuit of the inverter.

$\label{table I} TABLE~I$  Comparison of the Parasitic Resistance of TD-1 and TD-2

|      | $R_c(\Omega)$ | $R_{n1}(\Omega)$ | $R_{n2}(\Omega)$ | $R_{TD}(\Omega)$ |

|------|---------------|------------------|------------------|------------------|

| TD-1 | 86            | 37               | 56               | 1.2k             |

| TD-2 | 450           | 8                | 12               | 10               |

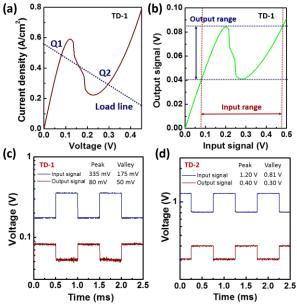

The basic principle of the inverter is illustrated in Fig. 5(a). Two stable states Q1 and Q2 can be achieved by connecting a load resistor with a tunnel diode. The tunnel diode at Port 1 serves as drive while the load resistor is the sum of R<sub>n2</sub>, R<sub>TD</sub> and R<sub>C</sub> at Port 3. Voltage sweep from 0 V to 0.5 V was applied on Port-1, with Port-3 grounded. The output signal was measured from Port-2. From an inverter built on TD-1, we measured the output and input signal characteristic curve as shown in Fig. 5(b). The "N-shape" IV-curve plotted with the load line clearly illustrates the inverter characteristic, with the increase of input signal accompanied by output signal decrease. The input voltage range is determined as 80 to 480 mV and the output voltage range is from 40 to 84 mV. For inverter based on TD-2, voltage sweep from 0 V to 1.5 V was applied on Port-1 to accommodate the NDR region, with Port-3 grounded. The input voltage range is measured as 0.43 to 1.49 V and output voltage range is from 0.21 to 0.42 V. Using a function generator as signal source and an oscilloscope to capture output signal, the recorded input and output waveforms of TD-1 are shown in Fig. 5(c), exhibiting inverter characteristic. The input signal features 335 mV peak and 175 mV valley while the output signal exhibits 80 mV peak and 50 mV valley. Same measurement has also been performed with the inverter based on TD-2. Inverter characteristic is clearly observed with 1.20 V peak and 0.81 V valley for the input signal and 0.4 V peak and 0.3 V valley for the output signal. The improved input/output signal range is mainly due to the higher current density of TD-2. The visible noise of the output signal should be due to the initial noise from the function generator.

Fig. 5. (a) Basic principle of the tunnel diode based inverter. (b) Output signal and input signal characteristic of inverters based on TD-1. (c) Output and input square waveform characteristic of inverters based on TD-1. (d) Output and input square waveform characteristic of inverters based on TD-2.

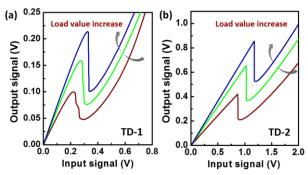

Fig. 6. (a) Output and input signal characteristic with varying load values of inverters based on (a) TD-1 (b) TD-2.

The input/output signal range increases with larger load resistance, as illustrated by the measured results from an inverter based on TD-1 in Fig. 6(a). Similar trend can also be observed from inverter based on TD-2, as evidenced by Fig. 6(b). Larger input/output signal ranges can improve signal to noise margin in actual use. Alternatively, both the input and output signal range can be tuned using a transistor as the load. Given recent progress in the integration of InGaAs FinFETs [14] and Gate-All-Around nanowire transistors [15] on Si using the aspect ratio trapping (ART) approach, co-integration of III-V

tunnel diode based inverters and transistors onto a common Si platform would be promising for circuit speed enhancement and power reduction.

#### IV. CONCLUSION

In conclusion, a two-state inverter was monolithically integrated onto exact (001) Si substrates using GaAs/InGaAs fin-array tunnel didoes as drive and load. On-chip bistable operation was demonstrated with a simple fabrication process. These results show potential for future high speed, low power consumption and compact tunnel diode based memory and multi-valued digital circuits.

#### ACKNOWLEDGMENT

The authors would like to thank SEMATECH for providing the initial patterned Si substrates and the NFF and MCPF of HKUST for technical support. Helpful discussions with H.X. Jiang, C. Liu, Y.T. Wan and B. Shi are also appreciated.

#### REFERENCES

- P. Mazumder, S. Kulkarni, M. Bhattacharya, J. P. Sun, and G. I. Haddad, "Digital circuit applications of resonant tunneling devices," Proc. IEEE, vol. 86, pp. 664–686, Apr. 1998. DOI: 10.1109/5.663544

- [2] J. P. A. van der Wagt, "Tunneling based SRAM," Proc. IEEE, vol. 87, pp. 571–595, 1999. DOI: <u>10.1109/5.752516</u>

- [3] A. Seabaugh, X. Deng, T. Blake, B. Brar, T. Broekaert, R. Lake, F. Morris, and G. Frazier, "Transistors and tunnel diodes for analog/mixedsignal circuits and embedded memory," in Int. Elect. Dev. Meeting Tech. Dig., 1998, pp. 429–432. DOI: 10.1109/IEDM.1998.746390

- [4] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," IEEE Trans. Electron Devices, vol. 36, pp. 2065-2082, Oct. 1989. DOI: 10.1109/16.40888

- [5] H.-L. E. Chan, S. Mohan, W. L. Chen, P. Mazumder, and G. I. Haddad, "Ultrafast, compact multiple-valued multiplexers using quantum electronic devices," in Proc. Government Microcircuit Applications Conf., San Diego, CA, 1994, pp. 115–118. DOI: <u>10.1109/4.508262</u>

- [6] L. J. Micheel, "Heterojunction bipolar technology for emittercoupled multiple-valued logic in gigahertz adders and multipliers," in *Proc. 22nd Int. Symp. Multiple-Valued Logic*, Sendai, Japan, 1992, pp. 18–26. DOI: 10.1109/ISMVL.1992.186773

- [7] H. Chan, M. Bhattacharya, and P. Mazumder, "Mask programmable multiple-valued logic gate using negative differential resistance devices," Proc. Inst. Electr. Eng., vol. 143, no. 5, pp. 289–294, Oct. 1996. DOI: 10.1049/ip-cds:19960571

- [8] N. Jin, S-Y. Chung, R.M. Heyns, P.R. Berger, R. Yu, P. E. Thompson, S. L. Rommel, "Tri-state logic using vertically integrated Si-SiGe resonant interband tunneling diodes with double NDR," *IEEE Electron Device Lett.*, vol. 25, no. 9, pp. 646-648, Sep. 2004. DOI: 10.1109/LED.2004.833845

- [9] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," IEEE Trans. Electron Devices, vol. 36, pp. 2065–2082, Oct. 1989. DOI: 10.1109/16.40888

- [10] N. Jin, S-Y. Chung, R. Yu, R.M. Heyns, P.R. Berger, P. E. Thompson, "The effect of spacer thicknesses on si-based resonant interband tunneling diode performance and their application to low-power tunneling diode SRAM circuits," *IEEE Trans. on Electron Devices*, vol. 53, no. 9, pp.2243-2249, Sep.2006. DOI: 10.1109/TED.2006.879678

- [11] Q. Li, Y. Han, X. Lu, Lau, K.M. Lau, "GaAs-InGaAs-GaAs Fin-Array Tunnel Diodes on (001) Si Substrates with Room-Temperature Peak-to-Valley Current Ratio of 5.4," *IEEE Electron Device Lett.*, vol.37, no.1, pp.24-27, Jan. 2016. DOI: 10.1109/LED.2015.2499603

- [12] Q. Li, K. W. Ng, and K. M. Lau, "Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001)

- silicon," Appl. Phys. Lett., vol. 106, no. 7, pp. 072105-1-072105-4, Feb,

- 2015. DOI: 10.1063/1.4913432

[13] M. Bao and K. L. Wang, "Accurately measuring current–voltage characteristics of tunnel diodes," IEEE Trans. Electron Devices, vol. 53, no. 10, pp. 2564–2586, Oct. 2006. DOI: 10.1109/TED.2006.882281

- [14] N. Waldron, C. Merckling, W. Guo, P. Ong, L. Teugels, S. Ansar, D. Tsvetanova, F. Sebaai, D.H. van Dorp, A Milenin, D. Lin, L. Nyns, J. Mitard, A Pourghaderi, B. Douhard, O. Richard, H. Bender, G. Boccardi, M. Caymax, M. Heyns, W. Vandervorst, K. Barla, N. Collaert and AV-Y. Thean, "An InGaAs/InP quantum well FinFet using the replacement fin process integrated in an RMG flow on 300 mm Si substrates," in Symp. VLSI Technol. Dig. Tech. Papers (VLSIT), Jun. 2014, pp. 32-33. DOI: 10.1109/VLSIT.2014.6894349

- [15] N. Waldron, C. Merckling, L. Teugels, P. Ong, S.A.U. Ibrahim, F. Sebaai, A. Pourghaderi, K. Barla, N. Collaert, A. Thean, "InGaAs gate-all-around nanowire devices on 300 mm Si substrates," IEEE Electron Device Lett., vol. 35, no. 11, pp. 1097–1099, Nov. 2014. DOI: 10.1109/LED.2014.2359579