**ORCA – Online Research @ Cardiff**

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/121919/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Alt, Alexander, Hirshy, Hassan, Jiang, Sheng, Lee, Kean Boon, Casbon, Michael, Chen, Peng, Houston, Peter, Tasker, Paul and Lees, Jonathan 2019. Analysis of gain variation with changing supply voltages in GaN HEMTs for envelope tracking power amplifiers. IEEE Transactions on Microwave Theory and Techniques 67 (7), pp. 2495-2504. 10.1109/TMTT.2019.2916404

Publishers page: http://dx.doi.org/10.1109/TMTT.2019.2916404

Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# Analysis of Gain Variation With Changing Supply Voltages in GaN HEMTs for Envelope Tracking Power Amplifiers

Alexander Alt, Student Member, IEEE, Hassan Hirshy, Member, IEEE, Sheng Jiang, Kean Boon Lee, Michael Casbon, Member, IEEE, Peng Chen, Member, IEEE, Peter A. Houston, Member, IEEE, Paul J. Tasker, Fellow, IEEE and Jonathan Lees

Abstract-Envelope tracking (ET) is a promising power amplifier (PA) architecture for current and future communications systems, that uses dynamic modulation of the supply voltage to provide high efficiency and potentially very wide bandwidth over a large dynamic range of output power. The dynamic nature of the supply voltage can lead to a problematic variation in transistor gain however, particularly in GaN HEMTs. This paper describes and analyses this behaviour and the detrimental effect it can have on ET PAs. Contributing factors and origins of gain variation are described in detail along with how, for the first time, meaningful comparisons can be made between different devices. Using these guidelines, gain variation is shown to be a widespread issue effecting most GaN HEMTs presented in literature. To allow an analysis of the intrinsic device behaviour, an extended transistor model is developed that takes the effect of gate and source field plates into account. This model is refined using measurement data and used to demonstrate the fact that the parasitic gate-drain capacitance  $(C_{GD})$  is the main contributor to the small-signal gain variation; a significant part of the overall gain variation. Based on this knowledge, possible strategies to reduce gain variation at the transistor technology level are proposed, allowing the optimisation of GaN HEMTs specifically for ET PAs. One identified strategy involves reducing the length of the gate field plate, and is shown to be a viable approach to reduce the gain variation in GaN HEMTs, albeit at an increased RF/dc dispersion.

*Index Terms*—Broadband, envelope tracking, HEMTs, power amplifiers, transistor technology.

#### I. INTRODUCTION

ODERN wireless communication standards utilise signals with high peak to average power ratio (PAPR) and increasing bandwidth to accommodate the growing demand

Manuscript received 15.11.2018; revised 06.03.2019; accepted 12.04.2019. This paper is an expanded version of the paper 'Comparing FET Technologies in Terms of Their Suitability for Broadband Envelope Tracking Power Amplifiers' that was presented at the International Workshop on Nonlinear Microwave and Millimetre-Wave Circuits (INMMiC), Brive-la-Gaillarde, France, July 5-6, 2018. This work was supported by the Engineering and Physical Science Research Council (EPSRC) in the context of the research project EP/N016408/1.

Alexander Alt, Michael Casbon, Peng Chen, Paul J. Tasker and Jonathan Lees are with the Centre for High Frequency Engineering (CHFE), School of Engineering, Cardiff University, Cardiff, UK. (e-mail: {alta, casbonma, chenp10, tasker, leesj2} @cardiff.ac.uk ).

Hassan Hirshy was with Cardiff University, Cardiff, UK. He is now with the Compound Semiconductor Applications Catapult, Cardiff, UK. (Hassan.hirshy@csa.catapult.org.uk)

Sheng Jiang, Kean Boon Lee and Peter A. Houston are with Department of Electronic and Electrical Engineering, University of Sheffield, Sheffield, UK. (e-mail: {sjiang5, kboon.lee, p.a.houston} @sheffield.ac.uk.

for high data rates. This, in turn, increases the demands placed upon the power amplifier (PA) as it is still expected to operate linearly and at high efficiency over a wide dynamic range. To achieve these goals, PA architectures such as Envelope Tracking (ET), Doherty and out-phasing have been, and continue to be developed [1]-[3]. In ET architectures, the power amplifier is kept in an efficient state of operation by modulating its supply voltage using a dynamic power supply. As a result of this, the transistor is not operated at a fixed supply voltage as in a conventional PA, but over a range of supply voltages. The implications of this have been explored [4], [5] where transistor technologies are compared in terms of suitability for ET. One issue that has been identified is the variation of the transistor's gain, both small-signal and large signal, with a changing supply voltage. Although GaN HEMTs are generally accepted as one of the most promising transistor technologies for broadband power amplifiers in most established and emerging communication frequency bands, it has been shown [5] that, depending on the technology, they can exhibit different and significant degrees of gain variation. While [5] compares device technologies and mentions a wide range of gain variation in different devices, this paper will focus on the characterisation, impact and origins of gain variation itself. For clarity, while a transistor's gain depends on many factors, such as applied voltages, temperature and bias, for this paper, the term gain variation is used to describe only the supply voltage dependent gain variation.

Section II describes gain variation, ways to characterise it and comparisons of gain variation in literature. In Section III, the impact of gain variation on ET PAs will be discussed, and its physical origin will be analysed in Section IV. Based on this analysis, the possibility to optimise GaN HEMTs for ET PAs will be considered in Section V.

Unless specified otherwise, the measurements presented in this paper are of a GaN-on-Si HEMT with a gate length (L<sub>g</sub>) of 0.25  $\mu$ m, a gate width of 250  $\mu$ m, a barrier thickness of 30 nm. The drain-source separation is 7  $\mu$ m and the gate-source separation is 2  $\mu$ m. The power density is 6 W/mm and it has gate and source field plates. All load-pull and large signal measurements are conducted statically, using CW excitation, at device die level, in a probe station at 1 GHz and in a class F environment with second and third harmonic impedances controlled by an active load-pull system. The S-parameter, IV and  $g_m$  measurements are all conducted statically.

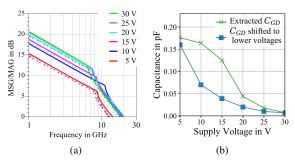

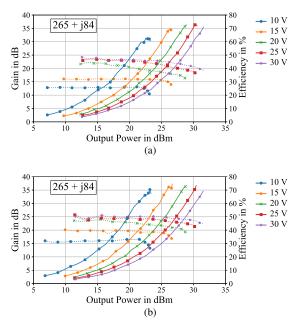

Fig. 1. Measured gain (dotted lines) and power added efficiency (solid lines) over output power characteristics of a GaN HEMT for different supply voltages and with a different fundamental load impedances: (a)  $\underline{Z}_1 = 121 + j*51 \Omega$  and (b)  $\underline{Z}_2 = 265 + j*84 \Omega$

## II. GAIN VARIATION

In an ideal transistor, the gain is independent of the supply voltage  $V_{\rm D}$ . It has been shown that this is necessary to achieve ideal envelope tracking where a change in supply voltage does not change the PA's behaviour, other than to increase efficiency [4]. In real transistors however, the gain does change with the supply voltage, the degree of which depending upon transistor type and technology [6]. To be able to evaluate the effect of gain variation, gain variation itself has to be defined and measurable, and there are multiple challenges in doing this. As gain variation changes with load impedance, gate bias and the input match, these challenges need to be discussed in more detail.

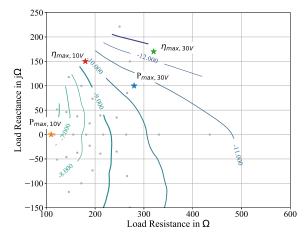

The first challenge in characterising gain variation is its dependence on the load impedance, as demonstrated in Fig. 1. At these two different load impedances, the gain variation changes significantly. This becomes even more problematic when looking at a wider range of load impedances, see Fig. 2. The figure shows that the gain variation due to a supply voltage change is between 6 and 13 dB for a GaN HEMT device depending on the load impedance. As the impedances for highest output power and highest efficiency are not the same, the designer has to choose. Usually, the targeted impedance is between the two maxima, providing a reasonable trade-off between power and efficiency. The gain variation at this choice of  $Z_{opt}$  is therefore considered to be the relevant. This stipulation leads to two further issues however. Firstly, it makes characterising gain variation subjective, as the trade-off between power and efficiency depends on the system requirements and is ultimately subject to design choice. Secondly, despite being an effect that is entirely observable in small-signal measurements, true gain variation can only be evaluated comprehensively in conjunction with large signal

Fig. 2. Contours showing the difference in gain in dB between supply voltages of 30 V and of 10 V of a GaN-on-Si HEMT at 1 GHz. Grey dots represent measured impedances, stars show the impedances for maximum efficiency and power at 10 V and 30 V. All measurements conducted under CW excitation, gain averaged over power levels

measurements that provide power and efficiency information under representative operational conditions. This is further illustrated in Fig. 1(a) and Fig. 1(b), where the gain variation is compared for two load impedances,  $\underline{Z}_1 = 122 + j \times 51 \Omega$  (the point of the lowest gain variation) and  $\underline{Z}_2 = 265 + j \times 84 \Omega$ (an impedance offering a good trade off between efficiency and output power). The figures show that the gain variation, output power and efficiency achieved for  $\underline{Z}_1$  and  $\underline{Z}_2$  differ significantly, emphasising the necessity of large signal measurements.

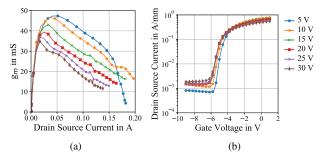

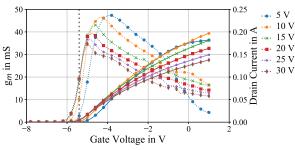

Additionally, quiescent current and  $g_m$  also depend on the supply voltage, as shown in Fig. 3(a). This leads to a change in the threshold voltage and thus a change in conduction angle and ultimately the class of operation for a PA, when the gate voltage remains fixed. As both class AB and class C have a non-linear gain [7], [8], this will lead to a gain that changes with input power. This can be observed in the gain curves in Fig. 1, where the gain can be seen to slowly drop for supply voltages of 20 V, 25 V and 30 V, stays nearly constant up to the compression point for the 15 V case and, for the 10 V case, increases with increasing input power, and then drops once compression is reached. As this AM/AM behaviour would not be clearly discernible in small-signal measurements, it reinforces the fact that large signal measurements are required

Fig. 3. Measured static transconductance and transfer characteristics; (a)  $g_m$  vs.  $I_D$  and (b)  $I_D$  vs  $V_{GS}$  of a GaN HEMT for different supply voltages

Fig. 4. Measured S<sub>11</sub> of a GaN HEMT for different supply voltages and increasing input powers for a load impedance of  $\underline{Z}_2 = 265 + j^* 84 \Omega$

for full characterisation of gain variation under representative conditions.

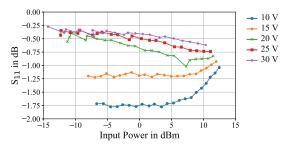

A third challenge in characterising gain variation is the impact of the transistor input impedance. In a typical transistor measurement, gain variation is typically shown as either the variation in transducer gain or power gain. If the transistor input impedance is constant, the two parameters will vary in the same way with the difference between transducer gain and available gain remaining constant. As CGS changes with  $V_{\rm DS}$  [9], [10] and with  $V_{\rm GS}$  [10], the input impedance of the transistor can be expected to change with both supply voltage and input power, see Fig. 4. These measurements show that the input impedance for different values of  $V_{DS}$ is significantly different at low and high input powers, and that this difference decreases with increasing drive level where the input impedances begin to converge. The change in input impedance with supply voltage and input power therefore means that the difference between power gain and transducer gain changes.

The last issue considered here is the fact that the variation depends on the supply voltage range. In Fig. 1(a), the gain can be seen to drop by 1.5 dB when reducing the supply voltage from 30 V to 20 V. When reduced further, the gain drops dramatically. In ET, the desired supply voltage range depends on the PAPR of the modulation used. Preferably, the transistor would be able to operate over a voltage range that is a few dB higher than the PAPR of the target signal to ensure the PA can operate efficiently most of them time.

To enable a meaningful comparison in spite of all of the above-mentioned issues, a set of guidelines is proposed for gain variation characterisation. The transistor needs to be:

- 1) Matched to an impedance that provides a good trade-off between power and efficiency

- Biased for flat gain at the lowest considered supply voltage, gain compared at 1 dB compression for all supply voltages

- Matched on the input for PAs, in which case transducer gain should be compared, whereas in load-pull measurements the power gain should be compared

This list with its partially subjective criteria demonstrates that evaluating gain variation is not a straightforward and simple task. However, based on these criteria, the gain variation of a number of GaN HEMTs described in literature is evaluated to establish its prevalence. This comparison is based on the established criteria, and assumes that the ET PAs presented in literature are matched for a trade-off between power and efficiency. Table I compares a wide range of different technology manufacturers and shows that most devices exhibit strong gain variation, demonstrating that gain variation is a wide spread phenomena for a wide variety of devices. As the different devices are measured over different voltage ranges, the voltage range needs to be considered carefully for a meaningful comparison.

Voltage normalised Gain Variation =

$$\frac{\text{Gain Variation (dB)}}{\text{Voltage Range (dB)}}$$

(1)

Equation (1) shows a straight forward way of achieving this. The closer the values of the voltage normalised gain variation are to zero, the lower the impact of supply voltage on gain in the chosen voltage range.

# III. IMPACT ON ENVELOPE TRACKING PAS

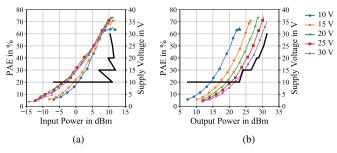

While gain variation is not trivial to characterise and compare, it's effects and the impact they have are more easily described. In PAs, gain manifests itself obviously in two measured characteristics, power added efficiency (PAE) and the AM/AM distortion. It has been shown that high gain variation reduces a transistor's usable supply voltage range [11], [17], limiting its usefulness within an ET application for high PAPR signals. Gain has a direct effect on PAE as shown in (2)

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} = \frac{P_{out}}{P_{dc}} \cdot \left(1 - \frac{1}{G}\right)$$

(2)

where G is the linear transducer gain. With G in the denominator, a low gain will clearly limit the PAE of the PA. If the gain drops with the applied supply voltage in envelope tracking PAs, the PAE will decrease for lower supply voltages. This is particularly relevant for ET PAs for modern communication standards with associated high PAPR signals, where the probability of the signal being of low magnitude and the supply voltage being low as a consequence, is high. This means that to achieve a high PAE for an ET PA over the whole output power range, a reasonable gain at all supply voltages is essential. The maximum frequency at which the transistor can be used with an acceptable efficiency is thus reduced by gain variation to a degree dependent on the targeted supply voltage range and the behaviour of the gain variation over that range.

Another impact of gain variation is an increase in AM/AM distortion when the supply voltage is modulated. As envelope tracking reduces the supply voltage at lower output powers to increase the efficiency of the PA, it places the transistor into an operational environment where its gain is reduced. If, for example, the degree of compression the PA is driven into is kept below 3 dB, any gain variation of more than 3 dB will appear as AM/AM distortion. A small amount of gain variation can be beneficial in reducing AM/AM distortion if the PA is operated in a slightly compressed state [6].

Gain variation is also the source of problems that do not impact the PA itself, but the ET PA as a whole by restricting the possible shaping functions. Shaping functions relate the applied dynamic supply voltage to the instantaneous magnitude of the modulated input envelope [18]. The most common shaping functions [2] all depend on the transistor's behaviour being insensitive to a change in supply voltage

| Transistor / Process | Technology | Voltage Range     | Gain Variation | Voltage normalised Gain Variation | Reference             |

|----------------------|------------|-------------------|----------------|-----------------------------------|-----------------------|

| Wolfspeed CGH40010F  | GaN-on-SiC | 16 - 28 V, 5 dB   | 4 dB           | 0.8                               | [6]                   |

| _ " _                | - " -      | 10 - 28 V, 9 dB   | 7 dB           | 0.78                              | [11]                  |

| MACOM NPT1012        | GaN-on-Si  | 14 - 28 V, 6 dB   | 2 dB           | 0.33                              | [12]                  |

| MACOM NPTB00004      | - " -      | 12 - 28 V, 7 dB   | 2 dB           | 0.29                              | [13]                  |

| FBH                  | GaN-on-SiC | 7.5 - 40 V, 15 dB | 7.5 dB         | 0.5                               | [14]                  |

| Qorvo                | GaN-on-SiC | 10 - 20 V, 6 dB   | 8 dB           | 1.3                               | [15]                  |

| RFMD/Qorvo RF3934    | GaN        | 15 - 60 V, 12 dB  | 4 dB           | 0.33                              | [16]                  |

| This work            | GaN-on-Si  | 10 - 30 V, 10 dB  | 7-9 dB         | 0.7-0.9                           | Fig. 1(b), Fig. 17(b) |

TABLE I

COMPARISON OF GAIN VARIATION IN GAN HEMTS

[4] and typically track the point of highest efficiency, or attempt to trade-off efficiency and linearity [11], [18] and result in a trajectory of supply voltage versus input power or input voltage magnitude [2], [19]. If the gain varies strongly, the input power necessary for high efficiency operation can become decoupled from, and almost independent of the supply voltage. To demonstrate this, PAE is plotted vs. input power in Fig. 5(a), as opposed to the usual way of plotting of PAE vs. output power, where the effect is not visible, see Fig. 5(b). Fig. 5 also shows the supply voltage profile in solid black lines, that yields the maximum PAE, both as a function of input and output power. The profile shown in Fig. 5 would usually be the foundation for a shaping function. As the measurements were conducted using only a limited number of discrete static supply voltages, the resulting resolution in the required voltage profile is very coarse, but sufficiently detailed to identify the required trend. In Fig. 5(b), where the required drain voltage for maximum efficiency is plotted vs. output power, the shaping function follows the familiar trend presented in literature [2], [11], [19]. When plotted vs. input power however, the shaping function in Fig. 5(a) is very different; remaining at a low supply voltages for most of the dynamic range and then rises sharply, close to the maximum input power, as shown in [17, Fig. 4]. This is completely due to the gain variation in the measured device, and shows that the maximum efficiency at different output power levels is achieved by fixing the input power and varying the supply voltage.

In this case, interestingly, the ET PA would be a hybrid structure, operating between ET and envelope elimination and

Fig. 5. Measured power added efficiencies for different supply voltages and the supply voltage trajectory giving the maximum PAE (solid black, symbolless lines), (a) over input power and (b) over output power

restoration (EER); varying the input power at a fixed supply voltage to control the output power in the low power region, and then varying the supply voltage at a fixed input power to control the output power in the high power region. This operation as an EER PA increases the accuracy requirements of the output voltage generated by the dynamic power supply, since the supply voltage is now the decisive factor in controlling the output power magnitude, and not the input power.

The measurements were conducted in a static and CW environment. Using static measurements to extrapolate dynamic operation has been shown to be a good starting point for predicting behaviour [11], [15], but can be limited, especially for GaN HEMT devices exhibiting trapping behaviour and thermal memory. In such devices, behaviour can be expected to change during dynamic, modulated operation [14], [20], [21], further impacting the gain variation. In order to understand the fundamental mechanisms behind gain variation, in this paper, the analysis will be conducted using exclusively static measurements.

## IV. ON THE ORIGIN OF SMALL-SIGNAL GAIN VARIATION

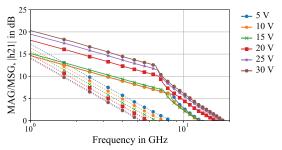

As discussed in Section II, gain variation has more than one source, and can be caused by a number of things, including input mismatch, gate bias point variation and the supply voltage dependence of the transistors small-signal gain. To limit the number of variables during analysis, smallsignal measurements are conducted where both the input impedance and the gate bias point are held constant. Under these measurement conditions, gain variation can be observed, even at low drive levels, as shown in Fig. 1, it follows that this is an effect that should be present in small-signal measurements. To focus on small-signal measurements alone however means that, in addition to the input mismatch and gate bias point variation, some large signal effects such as thermal and trapping memory effects may be neglected. The smallsignal S-parameter measurements conducted over a range of supply voltages however, do demonstrate that small-signal modelling with a static response main current source can be useful in identifying major contributors to overall gain variation. The transistor was biased at a quiescent drain current of 60 mA which was maintained for all supply voltages. At this bias point, the  $g_{\rm m}$  slightly increases with decreasing supply voltage, see Fig. 3. From the measured S-parameters, current gain, maximum stable gain and maximum available gain are

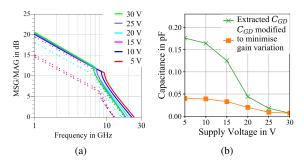

extracted. Fig. 6 shows that the maximum stable gain drops by around 6 dB and  $f_{max}$ , defined as the frequency where MSG reaches 0 dB, drops by 30% from 18.2 GHz to 12.7 GHz when reducing the supply voltage from 30 V to 5 V. It also shows that the gain does not reduce linearly; the MAG/MSG curves for 5 V, 10 V and 15 V are close to identical. The biggest drop in MAG/MSG happens between 20 V and 15 V. This demonstrates that small-signal analysis can be used to describe a significant contributor to the gain variation as described in Section II. While the power gain increases with supply voltage, the current gain decreases resulting in  $f_{\rm T}$  decreasing by about 35% from 8.2 GHz to 5.2 GHz.

The small-signal gain variation is observable in the frequency range up to 8 GHz where the maximum available gain is not defined due to the stability factor K being less than unity [22]. Therefore, the analysis can be conducted using the maximum stable gain with its simpler definition (4).

$$G_{\rm MSG} = \frac{|S_{21}|}{|S_{12}|} \tag{3}$$

$G_{\rm MSG}$  only considers gain and isolation, allowing the simplification of the problem. By applying the conversions in [23], this can be rewritten as

$$G_{\rm MSG} = \frac{|Y_{21}|}{|Y_{12}|} \tag{4}$$

From [24] the two parameters  $|Y_{21}|$  and  $|Y_{12}|$  are known to be associated with  $Z_{GD}$  and  $g_m$  in an intrinsic transistor. In the more complex transistor model using series and shunt capacitors, the  $G_{MSG}$  is influenced by additional elements, but as all the non-linear elements, except for  $R_S$  and  $R_D$ are intrinsic to the transistor, the model is suitable to be used to establish the origin of small-signal gain variation. The measurements in Fig. 6 show a large change in  $G_{MSG}$ between 20 V and 15 V, which means that at least one of these parameters needs to change significantly over the same range. To establish the behaviour over a range of  $V_{DD}$ ,  $C_{GD}$ and  $g_m$  values need to be extracted for the different voltages used.

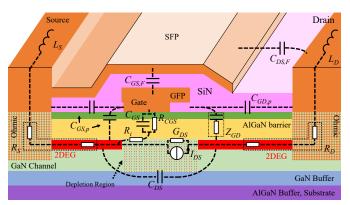

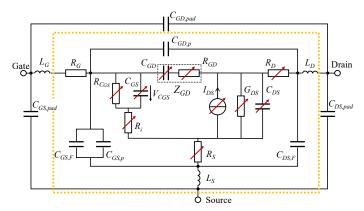

To model AlGaN/GaN HEMTs that use both gate and source field plates [27] to mitigate trapping effects, smallsignal circuit models need to accommodate this complexity if they are to be useful in describing the transistor properly [28]. In the case of the transistor measured for this paper, both gate and source field plates are present, see Fig. 7. In this case,

Fig. 6. Measured extrinsic maximum stable gain/maximum available gain (MSG/MAG) (solid lines) and current gain |h21| (dotted lines) of a GaN HEMT for different supply voltages

Fig. 7. Schematic of an AlGaN/GaN HEMT including gate and source field plate. Elements based on [25], [26]

Fig. 8. Small-signal equivalent circuit of a HEMT with gate and source field plate, elements visible in Fig. 7 are enclosed in the dotted rectangle, non-linear components that change with applied voltages are marked with an arrow

the commonly used small-signal equivalent circuit model [26] needs to be extended, combining the topologies for transistors with field plates in [28] resulting in the model shown in Fig. 8.

In order to extract values from measurement data, the "cold", i.e. at  $V_D = 0$  V, open and short S-parameters are measured in addition to the measurements for different supply voltages shown earlier. The extrinsic parameters are fitted to the passive "cold"-FET measurement data, supplemented with the other measurements, in a similar way to the approaches used in [29]-[31]. By incorporating as much measurement data as possible and basing the initial values on the device geometry, the risk of non-physical values was mitigated. Transconductance  $g_m$  has been measured, see Fig. 3 and  $R_s$ and  $R_{\rm D}$  were estimated from the sheet resistance and the port separations. As the measurements were conducted under isothermal and iso-current conditions, the non-linearities of the source resistance  $R_{\rm S}$  [32], [33] can be neglected. As the drain voltage changes the length of the depletion region [25],  $R_{\rm D}$ also changes with supply voltage. The resulting values were iteratively fitted until simulation and measurement lined up sufficiently. Fig. 8 uses red arrows to show which values are constant for all measurements and which change with supply voltage. S-parameter simulation results based on the model are close to the measurements for all extreme cases; forward and reverse biased at  $V_D = 0$  V, as well as at the lowest and highest supply voltage of  $V_D = 10$  V and  $V_D = 30$  V,

Fig. 9. Comparison of modelled (crosses, light colours) and measured (circles, dark colours) extrinsic device S-parameters from 0.1 GHz to 30 GHz for (a)  $V_D = 0$  V, forward biased, (b)  $V_D = 0$  V, pinched off, (c) operation at  $V_D = 5$  V,  $I_D = 60$  mA and (d) operation at  $V_D = 30$  V,  $I_D = 60$  mA

Fig. 10. Measured static transfer characteristic  $g_m$  versus  $V_{GS}$  (dotted) and drain current  $I_D$  (solid) of a GaN HEMT for different supply voltages and selected bias point for large signal measurements (dotted line, vertical)

respectively, see Fig. 9.

#### A. Role of the transconductance $g_m$

From Fig. 3, we know that  $g_m$  has little dispersion for low currents and diverges as soon as the current reaches 10 mA. For higher currents, the  $g_m$  curves diverge significantly for different supply voltages, with  $g_m$  decreasing for increasing supply voltages, reaching peak  $g_m$  earlier and at lower values. This decrease in  $g_m$  can be attributed to self-heating of the transistor and the associated effects on the channel [34]. For higher drain currents,  $g_m$  drops at approximately the same rate for all supply voltages. In typical PAs, the gate voltage is constant. As in this case, the pinch-off voltage changes with supply voltage, the drain current curve and thus  $g_m$  shift negatively with increasing supply voltage, see Fig. 10.

The bias point for the large signal measurements in the previous figures (1,2,4,5) has been chosen to give a somewhat flat gain at the lowest supply voltage,  $V_{GG} = -5.4$  V. Fig. 10 shows that in this case, the  $g_m$  values are grouped closely

between 15 V and 30 V. The measurements show therefore that the gain changes significantly, see Fig. 1, while  $g_m$  stays close to constant. This demonstrates that  $g_m$  can be ruled out as the main contributor to the gain variation observed in the low power range of the large signal measurements. As power levels increase, the gate voltage moves into regions where  $g_m$  is significantly larger for lower supply voltages, see Fig. 10. In this region, the gain variation slightly reduces as the transistor is first moving towards class B and then entering soft compression.

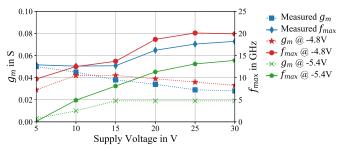

Fig. 10 shows the relationship between gate bias and  $g_{\rm m}$ for the measured GaN HEMT. The measurement based model is fully parametrised and can be used to adjust  $g_{\rm m}$ , allowing exploration of different bias points in the simulation. To explore this further, model predictions at two gate bias voltages are compared with measurements at a constant drain current of 60 mA, and are shown in Fig. 11: Firstly, a gate bias voltage of  $V_{GG} = -4.8$  V where the  $g_m$  values are close together for V > 10 V. This bias point is chosen to minimise the variation of  $g_{\rm m}$  to determine whether a reduced variation in  $g_{\rm m}$  reduces the variation in  $f_{\text{max}}$ . Secondly, the bias point  $V_{\text{GG}} = -5.4 \text{ V}$ was chosen as it emulates the bias conditions used for the large signal measurement. The simulation results show that in the case of  $V_{GG}$  = -4.8 V,  $f_{max}$  changes dramatically despite the relatively small variation in  $g_{\rm m}$ . At  $V_{\rm GG}$  = -5.4 V, the bias point corresponding to the large signal measurement,  $g_{\rm m}$  is close to constant from 15 V to 30 V, whereas  $f_{\rm max}$ doubles over the same voltage range. The simulation results demonstrate that, while the gate bias voltage can be used to change  $f_{\text{max}}$ , it has a limited influence on the variation of  $f_{\text{max}}$ . Even the large change from -5.4 V to the bias point of the measurement at around -4.2 V only leads to small changes in the variation of overall  $f_{\text{max}}$  for drain voltages above 10 V; while the  $f_{\text{max}}$  trajectory can be moved up and down by the gate bias, it's supply voltage dependent behaviour stays constant. Interestingly, this shows that the source of the smallsignal gain variation is to be found elsewhere, and not in the supply voltage dependence of  $g_{\rm m}$ .

# B. Role of the feedback capacitance $C_{GD}$

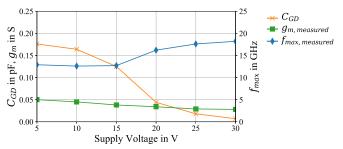

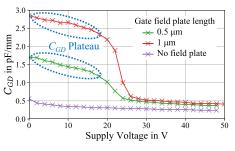

Using the same extraction process that resulted in the data shown in Fig. 9 and the measurements with a constant drain current of  $I_D = 60$  mA, the supply voltage dependent values for  $C_{\rm GD}$  can be obtained, as shown in Fig. 12. The feedback capacitance  $C_{\rm GD}$  increases significantly when the

Fig. 11. Comparison of  $f_{\text{max}}$  and  $g_{\text{m}}$  of the measurement with constant drain current and the simulation for two gate bias voltages, -4.8 V and -5.4 V

Fig. 12. Extracted gate-drain capacitance  $C_{\text{GD}}$  and measured transconductance  $g_{\text{m}}$  and maximum oscillation frequency  $f_{\text{max}}$  versus supply voltage

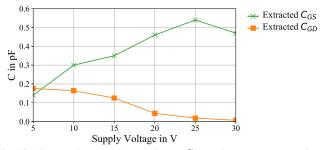

Fig. 13. Extracted gate drain capacitance  $C_{\rm GD}$  and gate source capacitance  $C_{\rm GS}$  versus supply voltage

supply voltage is reduced, its value changes most dramatically between 15 V and 20 V, which is consistent with the drop in gain. The drop in  $f_{\text{max}}$  is mitigated by the increasing  $g_{\text{m}}$  so that it stays almost constant between 5 V and 15 V. This indicates that  $C_{\text{GD}}$  is a major contributor to small-signal gain variation and thus a contributor to overall gain variation.

By using the same small-signal model of the transistor, it is possible to manipulate  $C_{GD}$  in order to explore the effect, and to verify the assumption that  $C_{GD}$  is one of the main contributors to small-signal gain variation. To demonstrate this, the supply voltage dependent behaviour of  $C_{GD}$  is artificially modified while all other parameters of the model are left unchanged, including  $g_m$  which is kept identical to the measured  $q_{\rm m}$ . This purely theoretical approach allows something impossible in reality, namely the adjustment of individual parameters that are not adjustable in isolation in real devices where  $C_{GD}$  and  $C_{GS}$  are closely interrelated, with one increasing while the other decreases, see Fig. 13, which is consistent with the behaviour reported in literature [9], [35]. Clearly, this artificial adjustment of one value in a system with many interdependent variables will lead to results that need to be treated with care and are only valid over a certain range. In this case, the most interesting parameter is the gain, particularly the MSG, in the region up to 6 GHz, where the ET PA will be used. From (4), the impact of  $C_{GS}$  on the MSG is known to be small, therefore a change in  $C_{GD}$  with a static  $C_{GS}$ will yield a sufficient approximation for the MSG while the values obtained for the MAG and  $f_{max}$  will not be meaningful as they depend on  $C_{GS}$ .

This approach allows the exploration of the impact of different shapes of the  $C_{GD}$  profile. One obvious shape is the one needed for minimal small-signal gain variation with supply voltage, as shown in Fig. 14(a). The second  $C_{GD}$

Fig. 14. Comparison of extracted  $C_{GD}$  and  $C_{GD}$  modified for minimum smallsignal gain variation: (a) Simulated MSG/MAG in dB for extracted (dotted line) and modified (solid line) for different supply voltages and (b) comparison of the two  $C_{GD}$  shapes versus supply voltage

Fig. 15. Comparison of extracted  $C_{GD}$  and  $C_{GD}$  modified to represent a  $C_{GD}$  curve shifted to start increasing at lower voltages: (a) Simulated MSG/MAG in dB for extracted (dotted line) and modified (solid line) for different supply voltages and (b) comparison of the two  $C_{GD}$  shapes versus supply voltage

profile represents a  $C_{\rm GD}$  which exhibits changes similar to the original case, but starting at a lower supply voltage, see Fig. 15. This leads to a gain that decreases with supply voltage but more gradually than in the original case. This behaviour is representative of the transistors with low gain variation shown in table I. The ability to change the small-signal gain variation by independently and exclusively changing  $C_{\rm GD}$ further demonstrates that  $C_{\rm GD}$  is the leading source of the observed small-signal gain variation in GaN HEMTs.

Using TCAD, a semiconductor device modelling tool, the behaviour of  $C_{GD}$  versus supply voltage is simulated. The simulation results of a GaN HEMT with and without gate field plates shows that the gate field plate is the cause for the plateauing of  $C_{GD}$  in GaN HEMTs, see Fig. 16. This is also reported in literature; gate field plates lead to a plateau in  $C_{GD}$ versus supply voltage in [25], compared to HEMT devices with no field plates [35] which do not show the same plateau behaviour. The authors of [25] separate the change in  $C_{GD}$  into two ranges [25]; the first where the depletion region changes exclusively laterally with  $C_{GD}$  increasing close to linearly, and the second where the depletion region additionally changes vertically, increasing the carrier concentration and thus leading to a significant increase in  $C_{GD}$ . From the presented analysis and simulation results, it is clear that this increase is a major cause of small-signal gain variation with supply voltage.

Fig. 16. TCAD simulation results of  $C_{\rm GD}$  of a GaN HEMT with a gate field plate length of 1  $\mu$ m, 0.5  $\mu$ m and with no gate field plate versus supply voltage at  $V_{\rm GS}$  = -5 V,  $C_{\rm GD}$  plateau is labelled in blue

#### V. OPTIMISATION OF GAN HEMTS FOR ET PAS

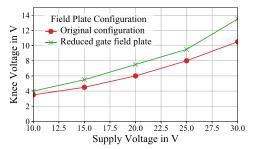

One major source of gain variation, has been shown to be the gate field plate, but as field plates are crucial in reducing RF/dc dispersion [27], [36], removing them does not appear to be an option. RF/dc dispersion, or knee-walkout, is the general term given to differences between static or slowly pulsed dc-IV characteristics and their dynamic equivalents that are revealed during large signal CW RF excitation or high frequency pulsed dc-IV. This phenomena occurs as a result of trapping effects that lead to an increase of the, now dynamic, on-resistance. In RF PAs, this effect limits achievable RF performance, and is discernible as the knee region expanding with increasing supply voltage. This increase in RF/dc dispersion leads to reduced efficiency, power and linearity and is therefore undesirable [27], [36]. Reducing the dimension of the field plate will increase the RF/dc dispersion [27] but reduce the variation of  $C_{GD}$  as demonstrated in the TCAD simulations in Fig. 16. To verify this assumption, two GaN-on-Si HEMTs, identical in all parameters but the length of the gate field plate, are fabricated, measured and compared under the identical bias, drive and harmonic load conditions, see Fig. 17. The measurements show that while power levels and efficiencies are comparable, the behaviour of the gain changes, particularly as the supply voltages decrease. The gain at 10 V and 15 V increase by 2 dB to 3 dB over the full power range, reducing the gain variation as defined in Section II by 2 dB. This increase in gain for low supply voltages also shows in the PAE, the maximum PAE at 10 V increased by about 5%. As expected, this comes at the cost of increased RF/dc dispersion, see Fig. 18, as the electric field increases and, with it, trapping effects. The knee voltage is higher for all supply voltages and increases more with increasing supply voltage. While this does not significantly effect the efficiency measurements for higher supply voltages, the linearity will be impacted by the increased knee region interaction, the degree of which will be determined in future research. For modern communications standards with high peak-to-average power ratios, ET PAs will tend to operate at lower supply voltages anyway, so a higher RF/dc dispersion may be preferable to high gain variation: the two can be traded-off depending on the application.

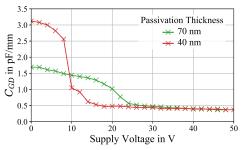

Another factor in reducing gain variation is the thickness of the passivation between gate field plate and the barrier layer. The voltage of transition to the  $C_{GD}$  plateau is determined

Fig. 17. Measured gain (dotted lines) and power added efficiency (solid lines) versus output power characteristics of two GaN HEMTs for different supply voltages with the same fundamental load impedance of  $\underline{Z}_2 = 265 + j^* 84 \Omega$ : (a) original field plate configuration, corresponding to the orange curve in Fig. 16 and (b) reduced length of the gate field plate, corresponding to the the green curve in Fig. 16.

Fig. 18. Measured RF/dc dispersion versus supply voltage for the original field plate configuration and an device with a reduced gate field plate

by the pinch-off voltage at which the channel under the field plate is depleted. By reducing the thickness of passivation under the field plate and hence the pinch-off voltage, the voltage at which  $C_{\text{GD}}$  starts to increase can be moved to a lower supply voltage albeit the penalty of larger  $C_{\text{GD}}$  in the plateau as shown in Fig. 19. This demonstrates a practical

Fig. 19. TCAD simulation showing the behaviour of  $C_{\text{GD}}$  for a constant gate field plate configuration and different SiNx passivation thicknesses between field plate and barrier versus supply voltage at  $V_{\text{GS}} = -5$  V

approach where modifying the passivation thickness can be used to move the  $C_{\text{GD}}$  plateau towards lower supply voltages to reduce the impact on ET PA performance.

# VI. CONCLUSION

Supply voltage dependent gain variation has been discussed and analysed in terms of characterisation, prevalence in literature and impact on ET PAs. The difficulty in comparing gain variation of different devices is addressed by introducing guidelines that allows robust and meaningful comparison and characterisation of the gain variation of GaN HEMTs. The discussion has also established that gain variation is an issue for linearity, linearisability and shaping functions in ET PAs and that, while being a wide spread phenomena, it is not an inherent characteristic of GaN HEMTs. Using small-signal measurements to extract and fit the parameters of an extended model incorporating both gate and source field plates, the origin of the small-signal gain variation has been identified to be mainly the result of the variation of the gate-drain capacitance  $C_{GD}$  with supply voltage due to the presence of gate field plates. Different approaches to reducing the impact of the supply voltage dependent gain variation have been proposed and one of them has been verified. This shows that while gain variation is an issue in many GaN HEMTs on the market, it can be addressed with at device level, allowing devices to be optimised for use within ET PA architectures.

## REFERENCES

- Z. Popović, "Amping Up the PA for 5G: Efficient GaN Power Amplifiers with Dynamic Supplies," *IEEE Microwave*, vol. 18, no. 3, pp. 137–149, May 2017.

- [2] B. Kim *et al.*, "Push the Envelope: Design Concepts for Envelope-Tracking Power Amplifiers," *IEEE Microwave*, vol. 14, no. 3, pp. 68– 81, May 2013.

- [3] R. Quaglia, M. D. Greene, M. J. Poulton, and S. C. Cripps, "Design and characterization of a 1.7-2.7 GHz quasi-MMIC Doherty power amplifier," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2017, pp. 771–773.

- [4] E. McCune, *Dynamic Power Supply Transmitters*. Cambridge University Press, 2015, Cambridge Books Online.

- [5] A. Alt et al., "Comparing FET Technologies in Terms of Their Suitability for Broadband Envelope Tracking Power Amplifiers," in Proc. Int. Workshop Integr. Nonlinear Microw. Millim.-Wave Circuits, Jul. 2018, pp. 1–3.

- [6] Z. Yusoff *et al.*, "The benefit of GaN characteristics over LDMOS for linearity improvement using drain modulation in power amplifier system," in *Proc. Int. Workshop Integr. Nonlinear Microw. Millim.-Wave Circuits*, Apr. 2011, pp. 1–4.

- [7] L. C. Nunes, P. M. Cabral, and J. C. Pedro, "AM/AM and AM/PM Distortion Generation Mechanisms in Si LDMOS and GaN HEMT Based RF Power Amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 4, pp. 799–809, Apr. 2014.

- [8] S. Cripps, *RF Power Amplifiers for Wireless Communications*, ser. Artech House microwave library. Artech House, 2006.

- [9] P. J. Tasker and B. Hughes, "Importance of source and drain resistance to the maximum  $f_T$  of millimeter-wave MODFETs," *IEEE Electron Device Lett.*, vol. 10, no. 7, pp. 291–293, Jul. 1989.

- [10] G. Callet *et al.*, "A new nonlinear HEMT model for AlGaN/GaN switch applications," *EUMA Int. J. Microw. Wireless Tech.*, vol. 2, no. 3-4, pp. 283–291, 2010.

- [11] M. Olavsbråten, D. Gecan, M. R. Duffy, G. Lasser, and Z. Popovic, "Efficiency enhancement and linearization of GaN PAs using reducedbandwidth supply modulation," in *Proc. Eur. Microw. Conf.*, Oct. 2017, pp. 456–459.

- [12] MaCOM, Ed., NPT1012 Datasheet, 2013.

- [13] M. Mercanti, A. Cidronali, S. Maurri, and G. Manes, "HEMT GaAs/GaN power amplifiers architecture with discrete dynamic voltage bias control in envelope tracking RF transmitter for W-CDMA signals," in *Proc. IEEE Topical Conf. Power Amplifi.*, Jan. 2011, pp. 9–12.

- [14] N. Wolff, W. Heinrich, and O. Bengtsson, "Challenges in the design of wideband GaN-HEMT based class-G RF-power amplifiers," in *Proc. German Microw. Conf.*, Mar. 2016, pp. 189–192.

- [15] G. Lasser, M. Duffy, J. Vance, and Z. Popović, "Discrete-level envelope tracking for broadband noise-like signals," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2017, pp. 1942–1945.

- [16] A. Cidronali, N. Giovannelli, T. Vlasits, R. Hernaman, and G. Manes, "A 240W dual-band 870 and 2140 MHz Envelope Tracking GaN PA designed by a probability distribution conscious approach," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2011, pp. 1–4.

- [17] Z. Popović, "GaN power amplifiers with supply modulation," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2015, pp. 1–4.

- [18] Z. Mokhti, J. Lees, P. Tasker, and C. Cassan, "Investigating the linearity versus efficiency tradeoff of different power amplifier modes in an envelope tracking architecture," in *Proc. Eur. Microw. Integr. Circuits Conf.*, Sep. 2015, pp. 357–360.

- [19] A. K. Kwan, M. Younes, O. Hammi, M. Helaoui, and F. M. Ghannouchi, "Linearization of a Highly Nonlinear Envelope Tracking Power Amplifier Targeting Maximum Efficiency," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 1, pp. 82–84, Jan. 2017.

- [20] C. Florian *et al.*, "A Prepulsing Technique for the Characterization of GaN Power Amplifiers With Dynamic Supply Under Controlled Thermal and Trapping States," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 12, pp. 5046–5062, Dec. 2017.

- [21] S. Hiura and R. Ishikawa, "Electrothermal Transient Analysis of GaN Power Amplifier With Dynamic Drain Voltage Biasing," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 11, pp. 1019–1021, Nov. 2017.

- [22] D. Pozar, Microwave Engineering, 4th Edition. Wiley, 2011.

- [23] D. A. Frickey, "Conversions between S, Z, Y, H, ABCD, and T parameters which are valid for complex source and load impedances," *IEEE Trans. Microw. Theory Techn.*, vol. 42, no. 2, pp. 205–211, Feb. 1994.

- [24] B. Hughes and P. J. Tasker, "Bias dependence of the MODFET intrinsic model elements values at microwave frequencies," *IEEE Trans. Electron Devices*, vol. 36, no. 10, pp. 2267–2273, Oct. 1989.

- [25] D. Cucak *et al.*, "Physics-Based Analytical Model for Input, Output, and Reverse Capacitance of a GaN HEMT With the Field-Plate Structure," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2189–2202, Mar. 2017.

- [26] C. A. Liechti, "Microwave Field-Effect Transistors 1976," IEEE Trans. Microw. Theory Techn., vol. 24, no. 6, pp. 279–300, Jun. 1976.

- [27] N. Ronchi *et al.*, "Optimization of the source field-plate design for low dynamic RDS-ON dispersion of AlGaN/GaN MIS-HEMTs," *Physica status solidi* (a), vol. 214, no. 3, p. 1 600 601, 2017.

- [28] R. Coffie, "Field plate models applied to manufacturability and for RF Analysis," in *Proc. CS MANTECH*, 2015, pp. 279–282.

- [29] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microw. Theory Techn.*, vol. 36, no. 7, pp. 1151–1159, Jul. 1988.

- [30] N. Rorsman, M. Garcia, C. Karlsson, and H. Zirath, "Accurate smallsignal modeling of HFET's for millimeter-wave applications," *IEEE Trans. Microw. Theory Techn.*, vol. 44, no. 3, pp. 432–437, Mar. 1996.

- [31] A. Jarndal and G. Kompa, "A new small-signal modeling approach applied to GaN devices," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 11, pp. 3440–3448, Nov. 2005.

- [32] M. Thorsell *et al.*, "Thermal Study of the High-Frequency Noise in GaN HEMTs," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 1, pp. 19–26, Jan. 2009.

- [33] R. J. Trew *et al.*, "Nonlinear source resistance in high-voltage microwave AlGaN/GaN HFETs," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 5, pp. 2061–2067, May 2006.

- [34] A. Bellakhdar, A. Telia, L. Semra, and A. Soltani, "The thermal effect on the output conductance in AlGaN/GaN HEMT's," in 2012 24th International Conference on Microelectronics (ICM), Dec. 2012, pp. 1–4.

- [35] A. Jarndal and G. Kompa, "A new small signal model parameter extraction method applied to GaN devices," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2005, 4 pp.–.

- [36] C. Roff et al., "Detailed Analysis of DC-RF Dispersion in Al-GaN/GaN HFETs using Waveform Measurements," in Proc. Eur. Microw. Integr. Circuits Conf., Sep. 2006, pp. 43–45.

Alexander Alt received a B.Eng. degree in Information Technology from the University of Applied Science in Kaiserslautern in 2011, a BEng (Hons) degree in Electrical and Electronic Engineering from the University of East London in 2012 and, in 2017, a MSc degree in Wireless & Microwave Communication Engineering from Cardiff University where he is now working towards a PhD in the centre for high frequency engineering.

He was a RF R&D Engineer with TRUMPF Huettinger from 2012 to 2015. His research interests

include high efficiency broadband power amplifiers, particularly envelope tracking PAs, RF power converters and device characterisation and optimisation.

**Hassan Hirshy** (M' 15) received his PhD degree in electronic engineering from Cardiff University in year 2008.

He worked as a research associate and project manager at the Manufacturing Engineering Centre at Cardiff University where he was involved in micro and nano fabrication. He then worked as Research fellow at the Centre for High Frequency Engineering at Cardiff University where research focused on device technology development and circuit design of III-V RF devices. He is currently working at the

Compound Semiconductor Applications Catapult as Senior RF Engineer. He is responsible for RF device modelling and PDK development.

**Sheng Jiang** received the B.Sc.(Eng.) degree in electrical engineering from the East China University of Science and Technology, Shanghai, China, in 2011, and the M.Sc. (Eng.) and Ph.D. degree in electronic and electrical engineering from the University of Sheffield, Sheffield, U.K., in 2013 and 2017, respectively.

He is currently a research associate with the department of electronic and electrical engineering, the University of Sheffield. His research interests include the design, fabrication and characterisation

of GaN-based devices and integrated circuits for high-power high-frequency applications.

**Kean Boon Lee** received the Ph.D. degree in electronic engineering from the University of Sheffield, Sheffield, U.K., in 2010.

He is currently a Lecturer with the University of Sheffield, Sheffield, U.K. His current research interests include wide bandgap semiconductors and high-voltage/high-speed GaN HEMT technologies.

Michael A. Casbon received the PhD degree in electronic engineering from Cardiff University in 2018.

He is currently a researcher and technology translator at Cardiff University, specialising in pulsed active harmonic load-pull systems for investigating charge trapping in new semiconductor processes.

**Peng Chen** (S'15-M'17) received the B.E. degree in communication engineering and M.E. degree in electronic engineering from the Harbin Institute of Technology, Harbin, China, in 2010 and 2012, and the Ph.D. degree in electronic engineering from University College Dublin, Dublin, Ireland, in 2016.

Since 2017, he has been a research associate with Centre for High Frequency Engineering, Cardiff University. His current research interests include nonlinear device modeling and optimization algorithms applied to power amplifier design.

**Peter A. Houston** (M'92) received the B.Sc. degree (Hons.) in physics and the Ph.D. degree in physics from Strathclyde University, Glasgow, U.K., in 1972 and 1975, respectively.

He is currently a Professor of electronic devices with a specific research interest in the design and fabrication of GaN-based HEMTs for power switching applications.

**Paul J. Tasker** received the B.Sc. degree in physics and electronics, and the PhD. degree in electronic engineering from Leeds University, Leeds, UK, in 1979 and 1983, respectively.

From 1984 to 1990, he was a Research Associate with Cornell University, Ithaca, NY, where he was involved in the early development of HFET transistors. From 1990 to 1995, he was a Senior Researcher and Manager with the Fraunhofer Institute for Applied Solid State Physics (IAF), Freiburg, Germany, where he directed for the development

of millimeter wave GaAs MMICs. In 1995, he joined Cardiff University, UK., as a Professor, establishing the Centre for High Frequency Engineering which is now recognised internationally for its pioneering work in developing waveform engineering concepts and their application to microwave and millimetre-wave power amplifier design.

He was recently involved in the strategic development of the South Wales Compound Semiconductor (CS) Cluster, the establishment of the Compound Semiconductor Centre (CSC), the CS Catapult and the EPSRC "Future Compound Semiconductor Manufacturing Hub". He is a regular speaker at international conferences and he has contributed to over 200 journal and conference publications.

Prof. Tasker was awarded the honour of Distinguished Microwave Lecturer by the IEEE MTT society (2008 - 2010).

Jonathan Lees received the M.Sc. and PhD. degrees in electronic engineering from Cardiff University, UK in 2002 and 2006, respectively. He is currently a Senior Lecturer with Cardiff University. His key research areas are linear-efficient PA design and characterization with a specific interest in the design and optimization of high-efficiency power amplifiers. His work in this area culminated in the first published GaN Doherty amplifier.

His more recent research areas are the development of novel high-power, broadband time-domain

measurement and load-pull techniques, as well as investigation into RF properties of materials, microwave heating, and novel applications of microwave engineering.