# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/127587/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Benakaprasad, Bhavana, Eblabla, Abdalla M., Li, Xu, Crawford, Kevin G. and Elgaid, Khaled 2020. Optimization of ohmic contact for AlGaN/ GaN HEMT on low resistivity silicon. IEEE Transactions on Electron Devices 63 (3), pp. 863-868. 10.1109/TED.2020.2968186

Publishers page: http://dx.doi.org/10.1109/TED.2020.2968186

# Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# Optimization of ohmic contact for AlGaN/ GaN HEMT on low resistivity silicon

Bhavana Benakaprasad, Abdalla M Eblabla, Xu Li, Kevin G Crawford and Khaled Elgaid, Senior Member, IEEE

Abstract— In this study, we report the optimisation of ohmic contact formation on AlGaN/GaN on low resistivity silicon. To achieve this, a strategy of uneven AlGaN / GaN was introduced through patterned etching of the substrate under the contact. Various pattern designs (holes, horizontal lines, vertical lines, grid) and varied etch depth (above and below the 2-dimensional electron gas) were investigated. Further, a study of planar and non-planar ohmic metallisation was investigated. Compared to a traditional fabrication strategy, we observed a reduced contact resistance from 0.35  $\Omega$ .mm to 0.27  $\Omega$ .mm by employing a grid etching approach with a "below channel" etch depth and non-planar ohmic metallisation. In general, measurements of "below channel" test structures exhibited improved contact resistance compared to "above channel" in both planar and non-planar ohmic metallisation.

Index Terms— AlGaN/GaN High Electron Mobility Transistors (HEMTs), annealing temperatures, above and below 2DEG channel etching, contacts, contact resistance, contact roughness, GaN HEMTs, GaN on Low Resistivity Silicon, metal morphology, ohmic contacts, patterned etching, planar and non-planar ohmic surfaces, recessed ohmic contacts.

### I. INTRODUCTION

Wide band gap materials such as gallium nitride (GaN) are well suited for high-power, and high-frequency electronic devices over their silicon counterparts. This is

due to a large bandgap ( $E_g \sim 3.42~eV$ ), high critical electric field ( $E_e \sim 3.3~MV/cm$ ), high electron saturation velocity ( $v_{sat} \sim 2.7 \times 10^7~cm/s$ ) and high carrier mobility ( $\mu_n \sim 2000~cm^2/s$ ) of the two-dimensional electron gas (2DEG) channel formed by an AlGaN/ GaN interface. The ability to grow defect-free GaN on large silicon wafers also makes this technology more economic, while maintaining high performance [1]. However, one the many factors that limits the performance of GaN HEMTs is the requirement of low ohmic resistance, smooth surface morphology, and thermal stability for high-temperature performance [2]. This paper reports on the optimisation of ohmic contact formation on GaN-on-low resistivity (LR) Si substrate.

Several approaches have been adopted to try reduce access resistance to an AlGaN/ GaN interface. Ti/Al based metal schemes like Ti/Al/Ni/Au, Ti/Al/Mo/Au, Ta/Ti/Al/Ni/Au, Ti/Al/Ta/Au and Ti/Al/Ti/TiN annealed at elevated temperatures have been successfully demonstrated to reduce contact resistance [3] [4] [5] [6] [7]. Recess of the barrier layer at the drain and source has also proven to be successful [8] [9]. Regrowth of N-type GaN is so far the most effective way to reduce ohmic contact resistance, however the procedure is currently cost prohibitive and adds significant complexity to the fabrication process. N-type doping in the source and drain is also effective but requires extremely high anneal temperatures of the ohmic contacts compared to conventional schemes and can be similarly expensive.

In this paper, characteristics of contact resistance are studied by creating an uneven AlGaN/ GaN interface (barrier recess) through etching different patterns into the substrate. Two different etch depths were considered in this experiment; above and below the 2DEG channel, and different etch patterns, holes,

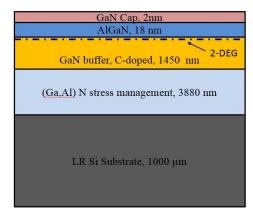

Fig. 1. Schematic of the AlGaN/GaN HEMT on the LR Si (111) silicon

B. Benakaprasad, A. Eblabla, and K. Elgaid are with School, of Engineering, University of Cardiff, Cardiff, CF24 3AA, U.K (e-mail: BenakaprasadB@cardiff.ac.uk, ElgaidK@cardiff.ac.uk)

EblablaA@cardiff.ac.uk,

X. Li is with School of Engineering, University of Glasgow, Glasgow, G12 8LP, U.K. (e-mail: Xu.Li@glasgow.ac.uk)

K.G. Crawford is with U.S. Army Research laboratory, Adelphi MD, USA (e-mail: k.g.crawf@gmail.com)

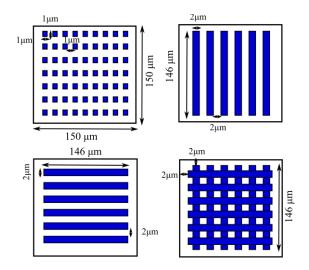

Fig. 2. Etching patterns of uneven AlGaN/GaN structures used in this experiment

vertical lines, horizontal lines and a grid. Further, differences in resistance for planar and non-planar ohmic contact for above channel etch formation was measured. This is the first time such an experiment has been reported for GaN-on-LR Si.

### II. EXPERIMENTAL

The Epitaxial layer structure used in this paper is as shown in the Fig. 1. Growth of AlGaN/GaN was done on a 1 mm thick silicon substrate by metal organic chemical vapour deposition (MOCVD). This process starts with the growth of a GaN stress management layer of 3880 nm followed by a carbon doped buffer layer of 1450 nm and the formation of an 18 nm Al<sub>x</sub>Ga<sub>1-x</sub>N (X=0.26) and 2 nm GaN cap layer. A sheet resistance of 475.4  $\Omega/\Box$ , carrier density of 7.41  $\times$   $10^{12}$  cm $^{-2}$  and mobility of 1770 cm $^{2}$ /V-s was obtained through Hall measurement of van der Pauw (VDP) structures.

|               |               |                                   |                 |                                                 |       |       |                                              | <u> </u>                                |

|---------------|---------------|-----------------------------------|-----------------|-------------------------------------------------|-------|-------|----------------------------------------------|-----------------------------------------|

| Sample<br>set | Etch<br>depth | Etch pattern                      | Metal<br>filled | AFM Roughness by annealed temperatures (RMS nm) |       |       |                                              | Cross-section schematic                 |

| 500           |               |                                   |                 | 790°C                                           | 810°C | 830°C | 850°C                                        |                                         |

| Set I         | N/A           | No etch<br>(control<br>structure) | N/A             | 75.4                                            | 88.9  | 92    | 101                                          | Ti/Al/Ni/Au  AlGaN                      |

|               | 8 nm          | Holes                             | Ti              | 64.2                                            | 91.8  | 68.7  | 65.5                                         | GaN 2-DEG Ti fill, 8 nm etch            |

|               |               | Horizontal                        |                 | 73.7                                            | 92.5  | 91    | 103                                          |                                         |

|               |               | Vertical                          |                 | 69.3                                            | 85.4  | 100   | 98.6                                         |                                         |

|               |               | Grid                              |                 | 70.7                                            | 86.2  | 93    | 95.8                                         |                                         |

| Set II        | N/A           | No etch<br>(control<br>structure) | N/A             | N/A                                             |       |       |                                              | Ti/Al/Ni/Au  Ti/Al/Ni/Au  Ti fill 50 pm |

|               | 50 nm         | Holes                             | Ti              | 88.7                                            | 97.2  | 97    | 106                                          | Ti fill, 50 nm etch                     |

|               |               | Horizontal                        |                 | 87.6                                            | 84.9  | 95.2  | 103                                          | etcii                                   |

|               |               | Vertical                          |                 | 93.9                                            | 94.6  | 101   | 101                                          | LR Si Substrate                         |

|               |               | Grid                              |                 | 94.8                                            | 101   | 104   | 115                                          |                                         |

| Set III       | N/A           | No etch<br>(control<br>structure) | N/A             | 81                                              | 97.5  | 103   | 112                                          | TI/AI/NI/Au  TI/AI/NI/Au  Ohmic fill,   |

|               | 8 nm          | Holes                             | Ti/Al/Ni/<br>Au | 61.3                                            | 72.4  | 82.9  | 73.4                                         | 2-DEG Onmic IIII,<br>8nm etch           |

|               |               | Horizontal                        |                 | 87                                              | 105   | 80.6  | 100                                          | LR Si Substrate                         |

|               |               | Vertical                          |                 | 91.2                                            | 108   | 102   | 105                                          |                                         |

|               |               | Grid                              |                 | 69.4                                            | 88.1  | 79.3  | 71.1                                         |                                         |

| Set IV        | N/A           | No etch<br>(control<br>structure) | N/A N/A         |                                                 |       |       | Ti/Al/Ni/Au  Ti/Al/Ni/Au  AlGan  Ohmic fill, |                                         |

|               | 50 nm         | Holes                             | Ti/Al/Ni/<br>Au | 56.7                                            | 61.9  | 87.6  | 110                                          | GaN Onm etch                            |

|               |               | Horizontal                        |                 | 82.3                                            | 99.1  | 105   | 105                                          |                                         |

|               |               | Vertical                          |                 | 102                                             | 106   | 70.4  | 103                                          | LR Si Substrate                         |

|               |               | Grid                              |                 | 92.5                                            | 92.2  | 88.7  | 108                                          |                                         |

Table. 1. Summary of samples used in this study. Each set has varied etch depth, metallization and contact roughness. An illustrative cross section of the ohmic contact is provided for each set.

Fig. 2 shows the different etching patterns investigated. First is a hole pattern consisting of  $1 \times 1$  µm holes with 1 µm separation. Second is a horizontal line pattern of size  $2 \times 146$ μm lines separated by 2 μm. Next is a vertical line etch pattern of the same geometry perpendicular to the direction of current flow and lastly a combination of horizontal and vertical etching to form a grid pattern. Additionally, a control contact with no etching was included for comparison purposes. Contact resistance of each approach was determined using the Transmission Line Measurement (TLM) method. Table 1 shows the sample sets prepared for this experiment, each set has four samples for different annealing temperatures (790, 810, 830, 850 °C) and in total 16 samples were fabricated. Each sample had the four etch patterns, as mentioned above, with a control of no etch pattern and two VDP structures for Hall measurements. All the samples were processed together and taken from the same wafer to mitigate parameter dispersion. Set I and set III were tested for above 2DEG channel etching and set II and IV for below 2DEG channel etching. Also, experiments were designed to compare between a planar and non-planar ohmic surface. Planar ohmic pads (Set I and II) were fabricated by filling the etched trenches under the ohmic contact with Ti metal with the thickness depending on the etch depth. Whereas, for the non-planar contacts (Set III and IV) there was no additional deposition of Ti metal to fill the trenches, resulting in an uneven metal surface on top of the contact. An ohmic metal stack of Ti/Al/Ni/Au (20/120/40/50 nm) was used. This is illustrated by cross-section schematic of each contact formation type in Table 1.

### III. FABRICATION

All fabrication was done using e-beam lithography and samples were prepared in parallel with each other. Samples in set I and III were etched using SiCl<sub>4</sub> in an Oxford Instruments PlasmaLab system 100 RIE with RF power of 200 W for above channel etching and samples in set II and IV for below channel etching. Etch depths of 8 nm and 50 nm were achieved respectively and was verified using Atomic Force Microscopy (AFM). For deposition of Ti into the trenches of set I and II, a lithography step was designed for Ti metal lift-off process using electron-beam evaporation. The thickness of the Ti filled in the etched area was matched to the depth measured by AFM to produce a planar surface. AFM and optical analysis during the fabrication process verified the resist profile matched that of the etch and no gaps were observed. For samples without additional Ti deposition (set III and IV), both etching and ohmic metallization were carried out in a single lithography step, producing a non-planar surface. Ohmic metals were deposited using electron-beam evaporation and all sets of samples were metallised at the same time. Isolation of the TLM's was achieved via a mesa etch around the test structures, using inductively coupled plasma (ICP) and Cl<sub>2</sub>/Ar chemistry. Lastly, the ohmic contacts were annealed under vacuum using Rapid Thermal Annealing (RTA) at four different temperatures of 790, 810, 830, 850°C for 30 secs.

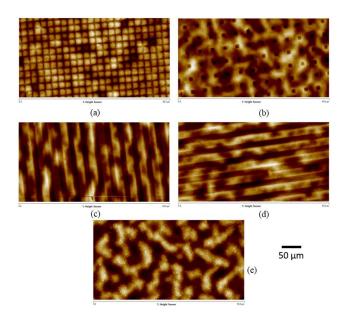

Fig. 3.  $50 \, \mu m$  AFM scans of non-planar ohmic surface (a) holes (b) grid (c) vertical (d) horizontal (e) no etch

Fig. 3 shows AFM scans for each etch pattern after metallisation for non-planar contacts. The roughness values of all four temperatures annealed for each pattern and etch depth along with control sample are presented in the 6<sup>th</sup> column of Table 1. Samples annealed were rougher (50 nm-110 nm) than the other pattern etching studies (19 nm - 43 nm) [10]. This might be due to the etching of the AlGaN interface or use of Ti/Al/Ni/Au ohmic metal stack. Further, there was no clear difference in roughness between planar and non-planar ohmic surfaces, most likely due to the metal re-flow in non-planar structures. Roughness increased with annealing temperature for all samples, as could be expected. The roughness of annealed Ti/Al/Ni/Au ohmic metal stack is often reported to be much higher than a Ti/Al/Mo/Au or Ti/Al/Ti/Au due to the Ni-Al alloy aggregation in some areas [11].

# IV. RESULTS AND DISCUSSION

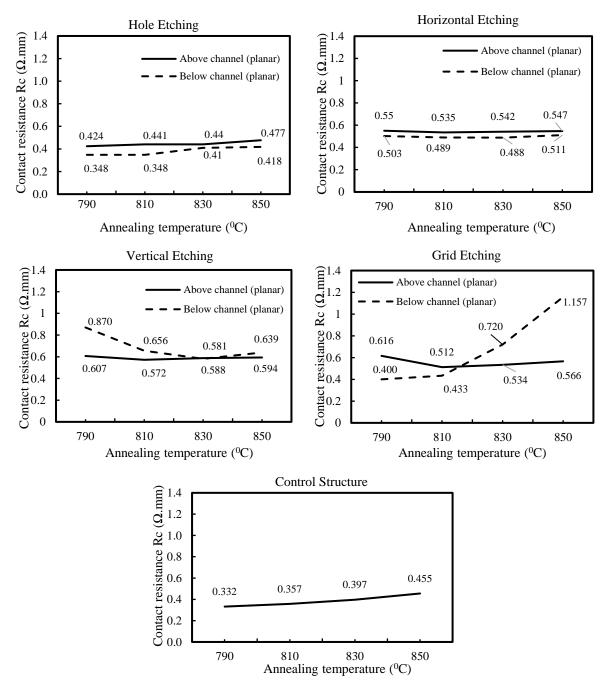

Fig. 4 shows the measurement of contact resistance with annealing temperature for different etch depths, etch patterns, planar contacts and the control design. Above channel etching is represented by a black solid line, and below channel etching is represented by black dashed line. Above channel etching showed greater contact resistance (0.424 - 0.616  $\Omega$ .mm) in general compared to below channel etching (0.348 - 1.157  $\Omega$ .mm), except in the grid and vertical etch pattern designs. Below channel etching for both vertical and grid patterns showed some unusual behaviour. For vertical etching there was a sudden dip in the contact resistance at 8100 C and for grid etching there was a sudden rise in contact resistance at 810° C. These anomalies might be due to ohmic roughness or impurities in GaN which contribute towards contact resistance. Comparing all above channel etching, the hole pattern exhibited a lower contact resistance in general (0.424 - 0.477  $\Omega$ .mm) compared to horizontal (0.535 - 0.555  $\Omega$ .mm), vertical (0.572 - $0.607 \Omega$ .mm) and grid etching patterns (0.512 - 0.616  $\Omega$ .mm). For below channel etching patterns, hole etching exhibited

Fig. 4. Plots of planar ohmic contact resistance vs annealing temperatures

lower contact resistance (0.348-0.418  $\Omega$ .mm) in general compared to horizontal (0.488-0.511  $\Omega$ .mm), vertical (0.581-0.870  $\Omega$ .mm), and grid (0.4 - 1.157  $\Omega$ .mm). Comparing this to the control sample, a contact resistance of 0.332 - 0.455  $\Omega$ .mm was achieved, which showed better performance than above or below etching with planar ohmic surfaces.

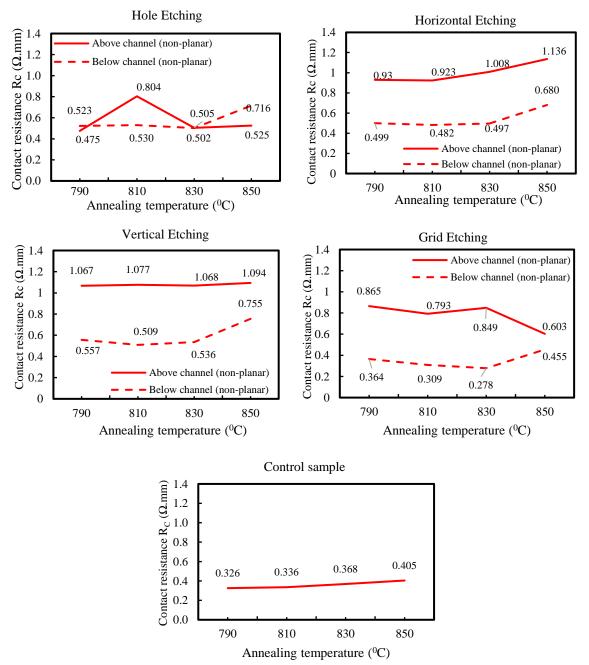

Fig. 5 shows the measurement of contact resistance with annealing for the non-planar samples. Above channel etching is represented by a red solid line and data of below etching is represented by a red dashed line. Above channel etching showed higher ohmic contact resistance (0.475 - 1.136  $\Omega$ .mm) compared to below channel for non-planar ohmic surfaces (0.278 - 0.755  $\Omega$ .mm). Comparing to other above channel

etching, hole etching (0.475 - 0.804  $\Omega$ .mm) performed better in general than horizontal etching (0.93 - 1.136  $\Omega$ .mm), vertical (1.077 - 1.094  $\Omega$ .mm) and grid etching (0.603 - 0.865  $\Omega$ .mm), despite the unusual spike at 810°C. Below channel etching with a grid design (0.278-0.455  $\Omega$ .mm) performed better than hole (0.502 - 0.716  $\Omega$ .mm), horizontal (0.482 - 0.68  $\Omega$ .mm) and vertical etching (0.509 - 0.755  $\Omega$ .mm). Relating these results to the control sample, an average contact resistance of 0.35 to 0.41  $\Omega$ .mm was achieved. A contact resistance of 0.27  $\Omega$ .mm was observed for a grid patterned ohmic contact employing below channel etching and an anneal temperature of 830°C. By comparison, the lowest contact resistance measured for TLM's without etching was 0.32  $\Omega$ .mm, annealed at 790°C. Since the

Fig. 5. Plots of non-planar ohmic contact resistance vs annealing temperatures

annealing temperature only differed by  $20^{0}$ C, it is possible that a contact resistance of less than 0.27  $\Omega$ .mm was achieved between the annealing temperatures of 810 and 850 $^{0}$  C.

The concept of an irregular AlGaN layer underneath the ohmic metal was proposed to reduce contact resistance lower than the limit found in control structures. First, patterned etching removes the irregular surface oxide layers and the pollutants by etching process which attributes to the lowering the contact resistance [12]. Second, patterned AlGaN increases 2DEG concentration by creating fringes near the edges of the etched AlGaN and high-density 2DEG located just outside these regions [13] [14]. Third, due to more side wall area the Ti will react with AlGaN to form TiN (which has lower work function than Ti), facilitating direct carrier transport between

metal and 2DEG [15]. The improved tunneling effect through N vacancies can be explained by the following equations:

$$R_c = \left(\frac{\partial J}{\partial V}\right)^{-1} \bigg|_{V=0} \Omega. cm^2$$

, where

$$J_t \propto \exp\left(\frac{-e\phi_{Bn}}{E_{00}}\right) \tag{2}$$

$$E_{00} = \frac{e\hbar}{2} \sqrt{\frac{N_d}{\varepsilon_s m_n^*}} \tag{3}$$

Through plasma etching, N vacancies are created at the surface of AlGaN [10] [14], which increases the donor doping concentration N<sub>d</sub> and electric field E<sub>00</sub>, Equation 3. Thus, increasing the tunnel current Jt and reducing the contact resistance R<sub>C</sub>, Equation 1 & 2. In the above channel etch, the electron tunneling between the ohmic metal and channel is low due to the thick barrier underneath, contributing to higher contact resistance. Non-planar surface ohmics demonstrate this behavior whereas in planar surface ohmics this is improved, which may be due to the extra filling of Ti in the trenches which could have reduced the barrier height. This shows the importance of Ti thickness with respect to the AlGaN thickness. In below channel etching, we find that non-planar ohmic surface performed much better than the planar surface, extra filling of Ti metal in the etched area did not show any significant improvement in the contact resistance. Previous some research [9] [14] has shown etching below the 2DEG channel, in the case of a single recess ohmic contact, to exhibit high contact resistance. Even though the barrier height is low, the absence of 2DEG channel underneath the contact limits carrier tunneling to a smaller region around the sidewall of the recessed barrier. Other work [16] [15] has shown, etching below the channel enhances ohmic performance. This difference is reportedly due to the sidewall angle, metal coverage and metallization. In our case, several small areas are etched under the contacts and thus tunneling is likely to occur around the sidewall of each etched region, achieving lower contact resistance. Overall, the below channel etch pattern with increased sidewall area exhibited lower contact resistance. When comparing the grid pattern to others tested, it is also possible the improvement in contact resistance observed is due to increased sidewall area in the transfer length region of the contact alone. This method of pre-etching the substrate prior to metallization is simple and non-invasive.

### V. CONCLUSION

In this paper, we have investigated the optimization of ohmic contact formation on GaN on low resistivity silicon through patterned etching of the AlGaN/ GaN substrate at two different etch depths and four annealing temperatures. A grid pattern etched below the 2DEG channel produced the lowest ohmic contact resistance observed (0.27  $\Omega$ .mm). Using a grid pattern produces increased exposed sidewall area and is most likely the cause of reduced contact resistance. Below channel etching also exhibited lower contact resistance compared to above channel etching. Further, use of extra Ti metal in the etched trenches to produce a planar surface showed reduction in contact resistance for above channel etching, but not for below channel etching. These results indicate etching beneath contacts can be a relatively simple method to reduce contact resistance, which will benefit RF and power devices based on GaN on low resistivity silicon. While devices in this study were produced using e-beam lithography, such etching can be easily achieved with photolithography also. Further optimization of etch pattern design could yield even greater improvements, such as a tapered profile to maximize sidewall area.

### ACKNOWLEDGMENT

The authors wish to thank staff at the James Watt Nanofabrication Centre for their assistance with this work. This work was supported by the Engineering and Physical Sciences Research Council under grants EP/N014820/2 and EP/P006973/1.

### REFERENCES

- [1] S. S. H. Hsu, C.-W. Tsou, Y.-W. Lian and Y.-S. Lin, "GaN-on-Silicon Devices and Technologies for RF and Microwave Applications," in *Radio-Frequency Integrated Technology (RFIT), 2016 IEEE International Symposium on*, Taipei, Taiwan, 24-26 Aug. 2016.

- [2] V. Kumar, L. Zhou, D. Selvanathan and I. Adesida, "Thermally-stable low-resistance Ti/Al/Mo/Au multilayer ohmic contacts on n-GaN," *Journal of Applied Physics*, vol. 92, no. 3, pp. 1712-1714, 2002.

- [3] R. Gong, J. Wang, S. Liu, Z. Dong, M. Yu, C. P. Wen, Y. Cai and B. Zhang, "Analysis of surface roughness in Ti/Al/Ni/Au Ohmic contact to AlGaN/GaN high electron mobility transistors," *Applied Physics Letters*, vol. 97, no. 6, pp. 10-13, 2010.

- [4] L. Wang, F. M. Mohammed and I. Adesida, "Differences in the reaction kinetics and contact formation mechanisms of annealed TiAlMoAu Ohmic contacts on n-GaN and AlGaNGaN epilayers," *Journal of Applied Physics*, vol. 101, no. 1, pp. 013702, 2007.

- [5] K. H. Kim, "Investigation of Ta/Ti/Al/Ni/Au ohmic contact to AlGaN/GaN heterostructure field-effect transistor," JVST B -Microelectronics and Nanometer Structures, vol. 23, no. 1, pp. 322, 2005.

- [6] C. Wang, S.-J. Cho and N.-Y. Kim, "Optimization of Ohmic Contact Metallization Process for AlGaN/GaN High Electron Mobility Transistor," *Transactions on Electrical and Electronic Materials*, vol. 14, no. 1, pp. 32-35, 2013.

- [7] H. Sun, M. Liu, P. Liu, X. Lin, J. Chen, M. Wang and D. Chen, "Optimization of Au-Free Ohmic Contact Based on the Gate-First Double-Metal AlGaN/GaN MIS-HEMTs and SBDs Process," *IEEE Transactions on Electron Devices*, vol. 65, no. 2, pp. 622-628, 2018.

- [8] K. Han, "AlGaN / GaN Heterostructures to reduce annealing Employing hole-array recess of barrier layer of AlGaN / GaN Heterostructures to reduce annealing Temperature of Ohmic contact," Semiconductor Science and Technology Paper, vol. 32, no. 10, 2017.

- [9] M. Hajlasz, J. J. T. M. Donkers, S. J. Sque, S. B. S. Heil, D. J. Gravesteijn, F. J. R. Rietveld and J. Schmitz, "Characterization of recessed Ohmic contacts to AlGaN/GaN," in *Microelectronic Test Structures (ICMTS)*, 2015 International Conference on, Tempe, AZ, USA, 2015.

- [10] W. Chong, Z. Meng-Di, H. Yun-Long, Z. Xue-Feng, W. Xiao-Xiao, M. Wei, M. Xiao-Hua, Z. Jin-Cheng and H. Yue, "Optimization of ohmic contact for AlGaNGaN HEMT by introducing patterned etching in ohmic area," *Solid-State Electronics*, vol. 129, pp. 114-119, 2017.

- [11] W. Macherzynski, A. Stafiniak, B. Paszkiewicz, J. Gryglewicz and R. Paszkiewicz, "Microanalysis of the Ti/Al and Ti/Al/Mo/Au ohmic contacts metallization to AlGaN/GaN heterostructures," *Physica Status Solidi A*, vol. 213, no. 5, pp. 1145-1149, 2016.

- [12] D. Buttari, A. Chini, G. Meneghesso, E. Zanoni, B. Moran, S. Heikman, N. Q. Zhang, L. Shen, R. Coffie, S. P. DenBaars and U. K. Mishra, "Systematic characterization of Cl2 reactive ion etching for improved ohmics in AlGaN/GaN HEMTs," *IEEE Electron Device Letters*, vol. 23, no. 2, pp. 76-78, 2002.

- [13] Y. Takei, M. Kamiya, K. Tsutsu, W. Saito, K. Kakushima, H. Wakabayashi, Y. Kataoka and H. Iwai, "Reduction of contact resistance on AlGaN/GaN HEMT structures introducing uneven AlGaN layers," *Physica Status Solidi A*, vol. 212, no. 5, pp. 1104-1109, 2015.

- [14] C. Wang, Y. He, X. Zheng, M. Zhao, M. Mi, X. Li, W. Mao, X. Ma and Y. Hao, "Low ohmic-contact resistance in AlGaN/GaN high electron mobility transistors with holes etching in ohmic region," *Electronics Letters*, vol. 51, no. 25, pp. 2145-2147, 2015.

- [15] L. Wang, D.-H. Kim and I. Adesida, "Direct contact mechanism of Ohmic metallization to AlGaN/GaN heterostructures via Ohmic area recess etching," *Applied Physics Letters*, vol. 95, pp. 172107, 2009.

- [16] Y.-K. Lin, J. Bergsten, H. Leong, A. Malmros, J.-T. Chen, D.-Y. Chen, O. Kordina, H. Zirath, E. Y. Chang and N. Rorsman, "A versatile low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs," Semiconductor Science and Technology, vol. 095019, no. 9, pp. 33, 2018.

- [17] J. Zhang, S. Huang, Q. Bao, X. Wang, K. Wei, Y. Zheng, Y. Li, C. Zhao, X. Liu, Q. Zhou, W. Chen and BoZhang, "Mechanism of Ti/Al/Ti/W Au-free ohmic contacts to AlGaN/GaN heterostructures via pre-ohmic recess etching and low temperature annealing," *Applied Physics Letters*, vol. 107, no. 26, pp. 262109, 2015.

Bhavana Benakaprasad received the B.Eng. degree in Electronics and Communication Engineering from VTU, Mysore, India, in 2012, and the M.Sc. degree in Electronics Design from the University of Glasgow, Glasgow, U.K., in 2014, where she is currently working towards the Ph.D. Degree in Electrical and Electronics

Engineering in University of Glasgow, U.K.

Her research interests include design and fabrication of terahetz antennas, active and passive RF devices, and characterisation of microwave and millimeter wave components.

Abdalla Mohamed Eblabla received the B.Sc. degree in Communication Engineering from Misurata University, Misurata, Libya, in 2008, and the M.Sc. degree in Electrical and Electronics Engineering from the University of Glasgow, Glasgow, U.K., in 2012, and Ph.D. degree in Electrical and Electronics Engineering from

University of Glasgow, U.K., in 2017. He is curently working as a post doctorate in Cardiff University.

**Xu Li** received the B.Sc. degree in physical chemistry from Central South University, Changsha, China, in 1981, the M.Sc. degree in Metallurgical Chemistry from the Changsha Institute of Mining and Metallurgy, Changsha, in 1986, and the Ph.D. degree in applied chemistry from the University of Strathclyde, Glasgow, U.K., in 1997.

Since 2004, he has been with the University of Glasgow, Glasgow.

Kevin G Crawford received a B.Sc. and M.Sc. degree in Computer Engineering from Glasgow Caledonian University and the University of Glasgow, Scotland, UK, in 2011 and 2012 respectively. He was awarded a PhD degree in Electronics and Electrical Engineering from The University of Glasgow in 2017 and

has been with the U.S. Army Research Laboratory, SEDD division, Adelphi MD, USA, since 2018.

using GaN technology.

Khaled Elgaid received the B.Sc. degree from the University of Evansville, Evansville, IN, USA, the M.Sc. degree from the University of Cincinnati, Cincinnati, OH, USA, and the Ph.D. degree from the University of Glasgow, Glasgow, U.K. He is a Professor in Cardiff University, where presently leading a high frequency devices and integrated circuits research team

His current research interests include the design and realization of compound semiconductor microwave, millimeter-wave, and terahertz monolithic integrated circuits using state-of-the-art inhouse nanotechnology facilities. These activities utilize different compound semiconductors platforms including GaN and GaAs. The group enhances its research activities with further integration including on chip antennas at submillimeter-wave and terahertz frequencies. His research activities are funded by government agencies and world leading industrial organizations in the area of high-speed wireless communications, radar, imaging, and sensors applications.