# **Cardiff University**

# **Technology Development for Nanoscale InSb**

### Quantum Split-Gate Structures

Author SHAWKAT JUBAIR Supervisor Dr. P.D. BUCKLE

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

in the

Condensed Matter and Photonics Group Cardiff School of Physics and Astronomy

22<sup>nd</sup> July 2019

"Study hard what interests you the most in the most undisciplined,

irreverent and original manner possible."

– Richard Feynman

# ABSTRACT

In this project some of the challenges of novel InSb based semiconducting material are investigated. Various features of electron transport in low dimensional semiconductors were studied for AlInSb/InSb quantum well (QW) two-dimensional electron gas (2DEG) heterostructures with an emphasis placed on realising one-dimensional systems (which exhibit quantum phenomena where the conductance takes on a discrete 'step-like' nature).

This material allows us to take advantage of very extreme material parameters such as light effective mass, the lowest binary material band gap, the highest electron mobility at room temperature, and an extremely large effective g-factor (with associated spin orbit coupling). However, this material still has significant challenges due to the large mismatch between the substrate GaAs and the QW, which produces threading dislocations that lead to limitations in mobility.

Surface roughness has been investigated as a result of shallow etching for Ohmic contact deposition on the AlInSb/InSb wafer. Both dry and wet techniques have been investigated, and their effect on the electron transport as a function of roughness, primarily using Transmission Length Measurement (TLM). In addition, the Ohmic contact resistivity was investigated as a function of depth over a wide range of temperatures to extract an effective contact barrier. The contact potential barrier was found to have a strong effect at low temperatures, which leads to a non-linear I-V characteristic.

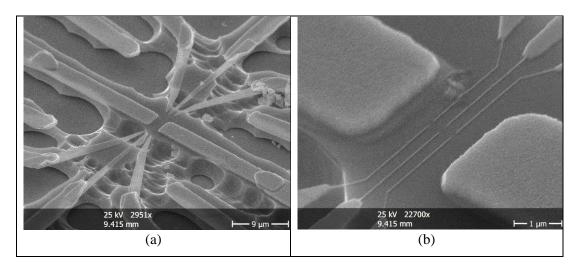

Finally, this thesis studied different designs of nanoscale split gate structures that were fabricated on this state of the art InSb QW 2DEG material. This material was grown by collaborators at Sheffield University at the National Centre for III-V technologies. The devices were fabricated at Cardiff using photo-lithography and nanoscale electron beam lithography (EBL) using recipes tailored to this material.

# **DEDICATION**

I dedicate this work to my parents; Ismael and Zainab, to my brothers; Qaiser, Khalid, Nashaat, Osama and Naseem, to my wife; Sally, and to my children; Teeba, Zainab, AbdurRahman and Alleen, who are a constant source of motivation, and who inspire me to strive to be the best person I could possibly be. I could not have taken this opportunity if they had not helped me through the early stages of my education with patience and encouragement.

# ACKNOWLEDGEMENTS

First and foremost, I gratefully acknowledge the help and support of my supervisor, Dr. Phil Buckle for his continuous guidance throughout experimental work and in the writing up this thesis. His constant support, motivation and encouragement has been invaluable throughout my research. I would like to thank him, not only for widening my research acumen but also for inspiring conversation about professional as well as personal development. I have been very fortunate to be supervised by such a dedicated scholar.

A special thank you goes to Dr. Craig Alford for his help with expertise and availability in dealing with equipment-related issues, as well as for his knowledge and worthy comments. My sincere thanks also go to my colleagues in the Condensed Matter and Photonics group: Dr. Dave, Dr. George, Dr. Fadwa, Dr. Chris and Tom for their assistance with many discussions and coding help.

I would also like to thank the cleanroom staff at Cardiff University (Dr. Angela, Saleem, Hugh, Sam, Dr. Connie) for their tremendous assistance in training, technical discussions and technical issues.

I would like to express my gratitude to the Ministry of Higher Education and Scientific Research in coordination with the Iraqi Attaché in London, as well as Engineering and Physical Research Council (EPSRC), who funded this project.

v

## PUBLICATIONS AND CONFERENCE PRESENTATION

### PUBLICATION

- Effect of wet and dry etching on metal-semiconductor contact resistivity for InSb QW 2DEG using TLM technique. (To be submitted to Physica E)

- 2. Effect of wet and dry etching on metal-semiconductor contact roughness. (in preparation)

- 3. Quantization conductance of InSb QW 2DEG and its limitations. (in preparation)

### **Conference Presentation and Poster**

- S I Jubair, P D Buckle. 'Fabrication of InSb Nanoscale Split-Gate Structures' Cardiff University (5<sup>th</sup> July 2016).

- S I Jubair, P D Buckle, C Allford, C McIndo. 'InSb QW Contact Characterization and Development for Nanoscale Devices' Swansea university (CAPS19), 11<sup>th</sup> July 2019.

## **TABLE OF CONTENTS**

| DECLARATION AND STATEMENTSi                                  |

|--------------------------------------------------------------|

| ABSTRACT iii                                                 |

| DEDICATIONiv                                                 |

| ACKNOWLEDGEMENTSv                                            |

| Conference Presentation and Postervi<br>TABLE OF CONTENTSvii |

| LIST OF FIGURESx                                             |

| LIST OF TABLES                                               |

| LIST OF ABBREVIATIONSxxi                                     |

| Chapter 11                                                   |

| Introduction1                                                |

| 1.1 Motivation1                                              |

| 1.2 Thesis Outline                                           |

| 1.3 Bibliography5                                            |

| Chapter 29                                                   |

| 2.1 Introduction                                             |

| 2.2 Quantum Well                                             |

| 2.2.1 The Finite Quantum Well10                              |

| 2.2.2 Density of States                                      |

| 2.3 Electron Transport                                       |

| 2.3.1 Two-dimensional Electron Gas17                         |

| 2.3.2 Ballistic Transport17                                  |

| 2.3.3 Quantized Conductance                                  |

| 2.4                            | Metal–Semiconductor Contact                     | 21 |

|--------------------------------|-------------------------------------------------|----|

| 2.4                            | .1 Ohmic Contacts                               | 21 |

| 2.4.2 Transmission Line Model2 |                                                 |    |

| 2.5                            | Scattering                                      | 29 |

| 2.6                            | Bibliography                                    | 31 |

| Chapter                        | 3                                               |    |

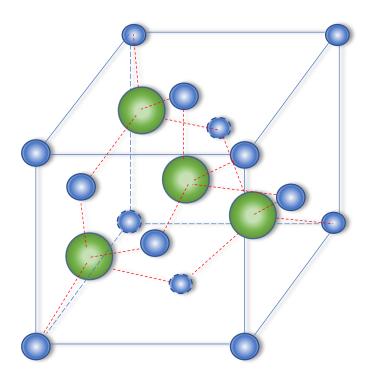

| 3.1                            | Indium Antimonide Semiconductor Heterostructure |    |

| 3.1                            | .1 Crystal Structure                            | 37 |

| 3.1                            |                                                 |    |

| 3.1                            | .3 Molecular Beam Epitaxy                       | 41 |

| 3.2                            | Device Design                                   | 42 |

| 3.2                            | .1 Split Gate Devices                           | 42 |

| 3.2                            | .2 TLM Device Design                            | 48 |

| 3.3                            | Device Fabrication                              | 50 |

| 3.4                            | Techniques                                      | 52 |

| 3.4                            | .1 Lithography (Photo and EBL)                  | 52 |

| 3.5                            | Sample Cleaning                                 | 55 |

| 3.6                            | Wet Chemical Etching                            | 56 |

| 3.7                            | Plasma Ashing Technique                         | 57 |

| 3.8                            | Wafer Surface Characterisation Techniques       | 58 |

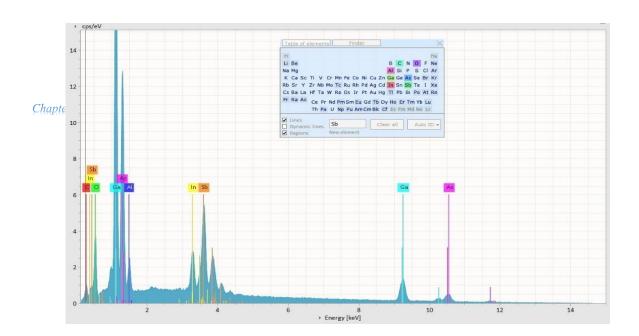

| 3.8                            | .1 Energy Dispersive X-ray Spectroscopy (EDX)   | 58 |

| 3.8                            | .2 Atomic Force Microscopy                      | 60 |

| 3.9                            | Device Characterisation                         | 61 |

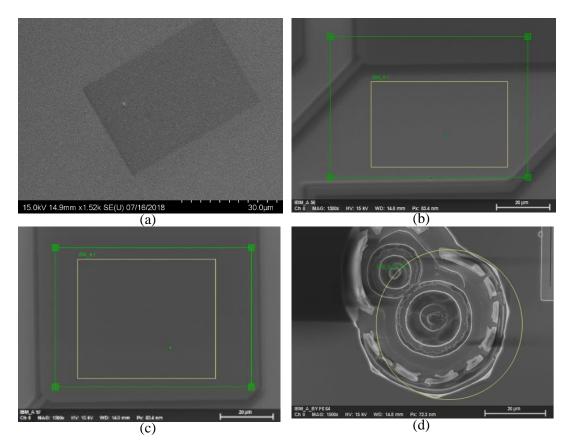

| 3.9                            | .1 Scanning Electron Microscope                 | 61 |

| 3.9                            | .2 Room Temperature I-V Measurements            | 62 |

| 3.10                           | Packaging and Wire Bonding                      | 63 |

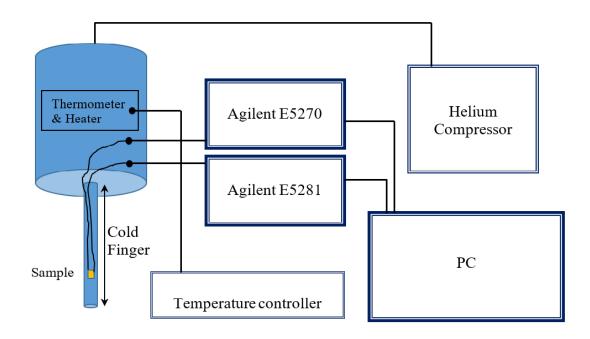

| 3.11                           | Low Temperature Measurement                     | 63 |

| 3.12                           | Conclusion                                      | 65 |

| 3.13                           | Bibliography                                    | 65 |

| Chapter                        | 4                                               | 69 |

| 4.1                            | Introduction                                    | 69 |

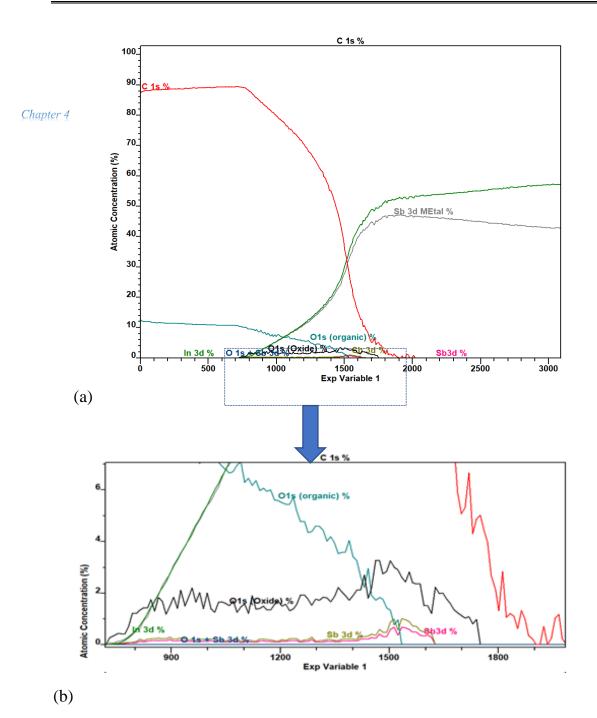

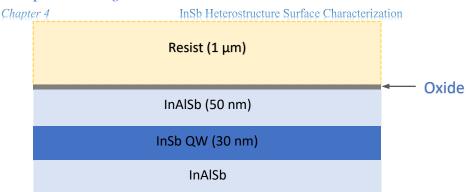

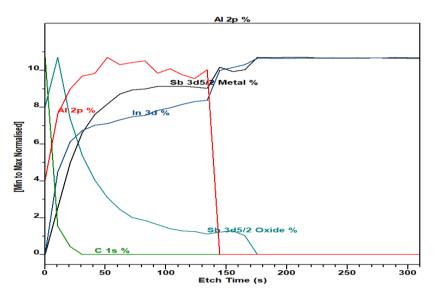

| 4.2                            | Surface Oxide Characterisation                  | 70 |

| 4.3     | Surface    | Roughness Characterization                  | 74  |

|---------|------------|---------------------------------------------|-----|

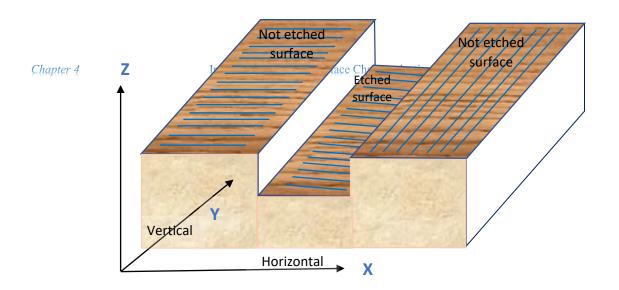

| 4.3     | .1 Pris    | tine wafer Roughness at zero and 90° degree | 78  |

| 4.3     | .2 Citr    | ic Acid Etching for the AlInSb/InSb wafer   |     |

| 4.3     | .3 Ion     | Beam Milling for the AlInSb/InSb wafer      | 91  |

| 4.4     | Conclus    | sion                                        | 100 |

| 4.5     | Bibliog    | raphy                                       | 101 |

| Chapter | 5          |                                             |     |

| 5.1     | Introdu    | ction                                       | 105 |

| 5.2     | Total R    | esistance                                   | 106 |

| 5.3     | Temper     | ature Dependence of the Contact Resistivity | 112 |

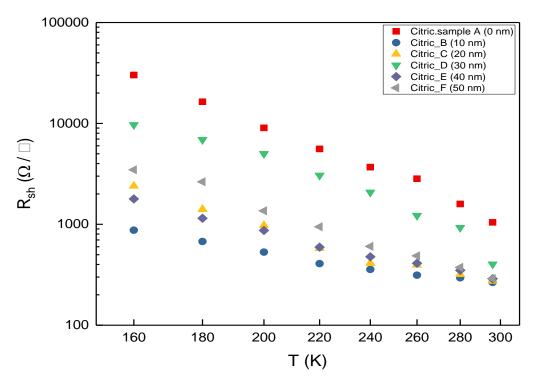

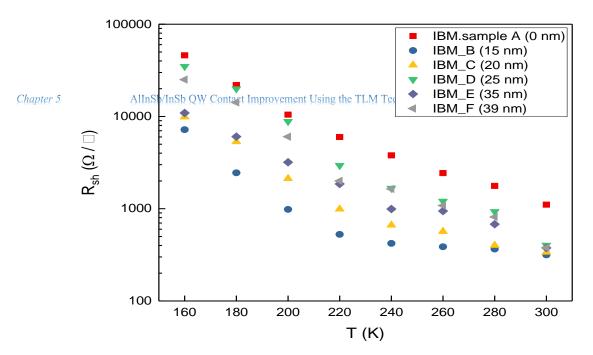

| 5.4     | Temper     | ature Dependence of the Sheet Resistivity   | 115 |

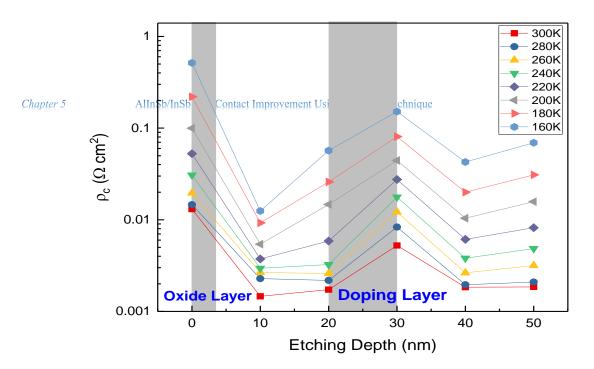

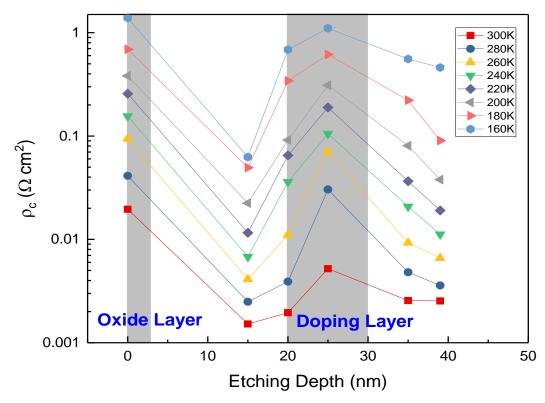

| 5.5     | Etching    | Depth Dependence Contact Resistivity        | 118 |

| 5.6     | Conclus    | sion                                        | 121 |

| 5.7     | Bibliog    | raphy                                       | 121 |

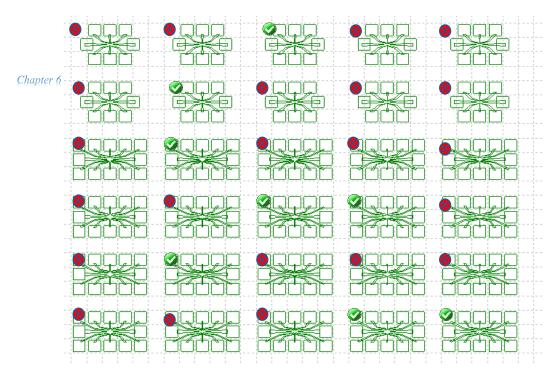

| Chapter | 6          |                                             | 126 |

| 6.1     | Introdu    | ction                                       | 126 |

| 6.2     | InSb 2D    | DEG Quantized Conductance                   |     |

| 6.3     | Limitati   | ions of Conductance Quantization            | 141 |

| 6.4     | Conclus    | sion                                        | 143 |

| 6.5     | Bibliog    | raphy                                       | 144 |

| Chapter | 7          |                                             |     |

| 7.1     | Conclus    | sions                                       | 149 |

| 7.2     | Future     | work                                        | 151 |

| 7.3     | Bibliog    | raphy                                       |     |

| Append  | x          |                                             |     |

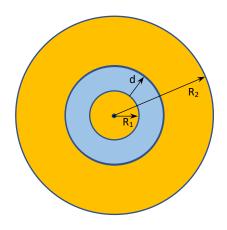

| A.1 (   | Circular S | Structure (CTLM)                            | 154 |

|         |            | phy                                         |     |

## LIST OF FIGURES

| Figure 2. 1: A schematic energy-band diagram of a QW as a function of confinement          |

|--------------------------------------------------------------------------------------------|

| direction, when E1, E2, E3 are the bound states in the finite quantum well as a function   |

| of the wave vector                                                                         |

|                                                                                            |

| Figure 2. 2: Barrier wave vector as a function of well wave vector, when the left-hand     |

| side of equation (2-15) is plotted as a solid line and the right-hand side is plotted as a |

| set of dashed lines                                                                        |

| <i>Figure 2. 3: Reciprocal lattice of a cubic lattice in 3D (a) and 2D (b).</i> 15         |

| Figure 2. 4: InSb density of states (DOS) in 3D (a) using equation (2-25) and 2D QW        |

| (b) using equation (2-27) with quantised energy levels                                     |

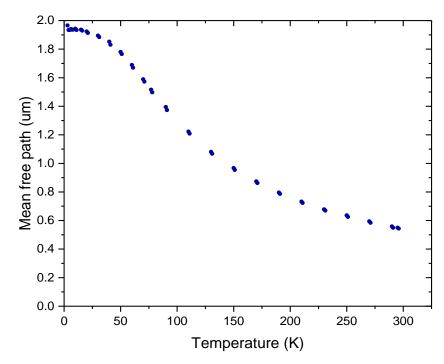

| Figure 2. 5: Temperature dependence of the mean free path of InSb wafer (SF1258)           |

| as measured by the Hall effect                                                             |

| Figure 2. 6: Schematic band structure of a metal-semiconductor junction before and         |

| after contact for Schottky and Ohmic cases22                                               |

| Figure 2. 7: Schematic diagram of the conduction mechanisms for different barrier          |

| widths: (a) wide barrier, (b) intermediate barrier width, and (c) thin barrier. The case   |

| of thermal activation and then subsequent tunnelling is sometimes referred to as a         |

| field emission mechanism25                                                                 |

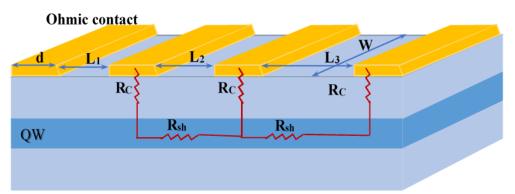

| Figure 2. 8: A Schematic 3D representation of a typical transmission line model            |

| (TLM) device configuration showing the contributing contact resistance $(R_C)$ and the     |

| effect of sheet resistance (R <sub>s</sub> )                                               |

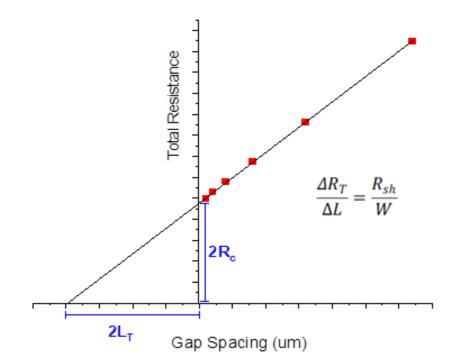

| Figure 2. 9: A sketch of a typical plot of total resistance as a function of gap spacing   |

| between the planar Ohmic contacts in a TLM measurement                                     |

| Figure 2. 10: A typical transport model of mobility (lines) using the relaxation time      |

| approximation, and measured data (symbols) versus temperature from [47]31                  |

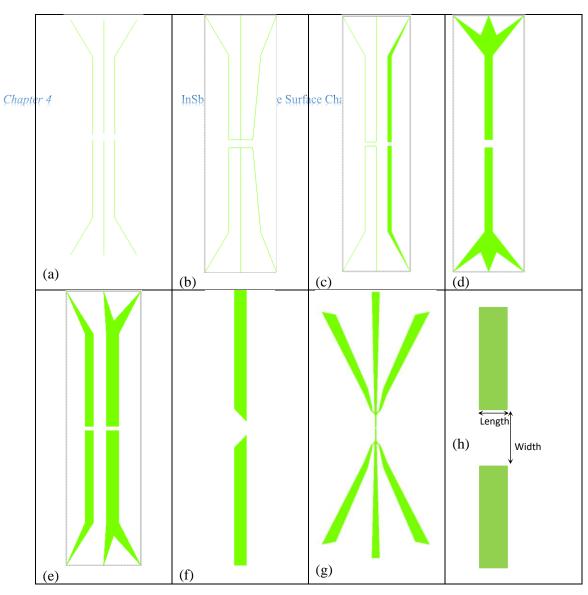

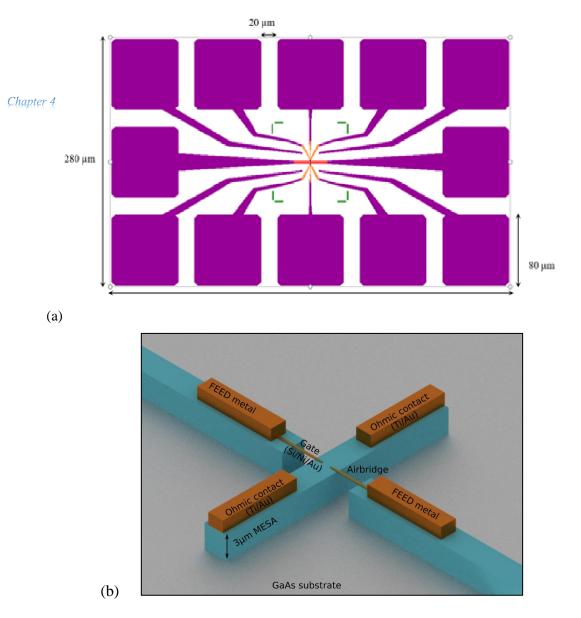

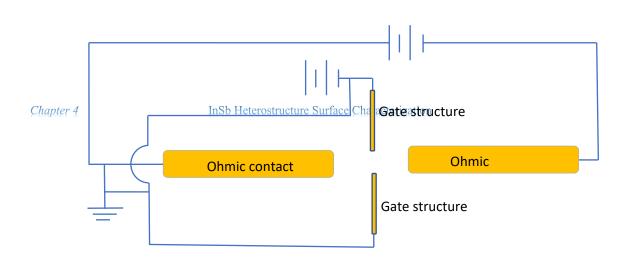

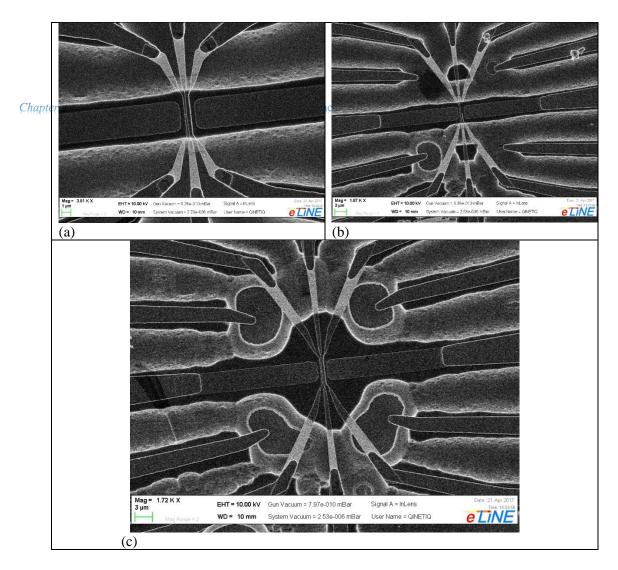

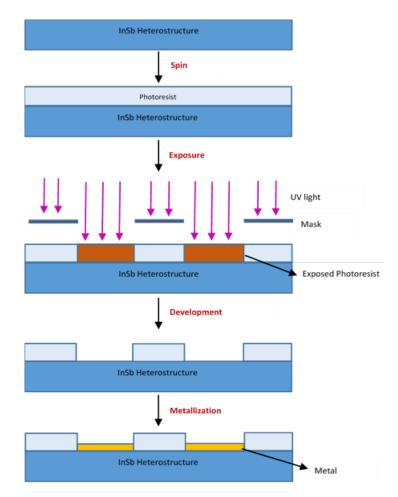

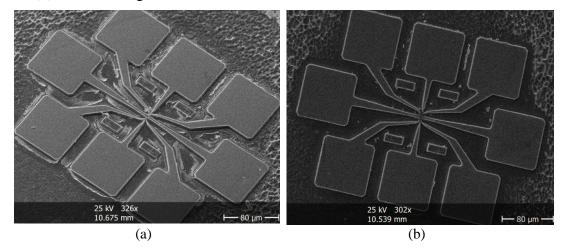

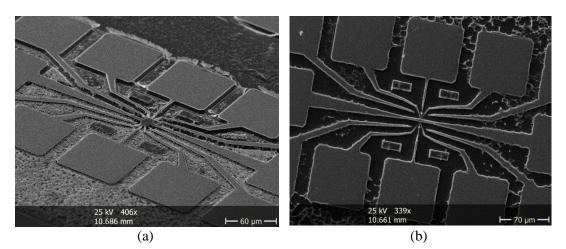

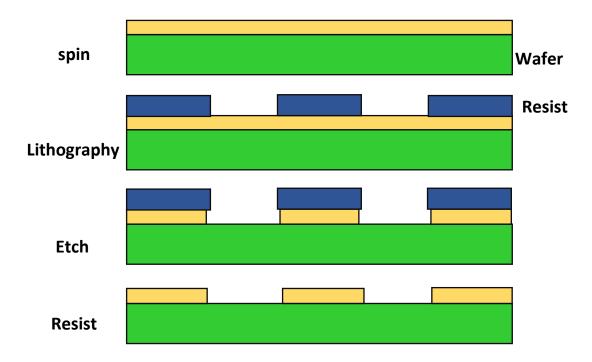

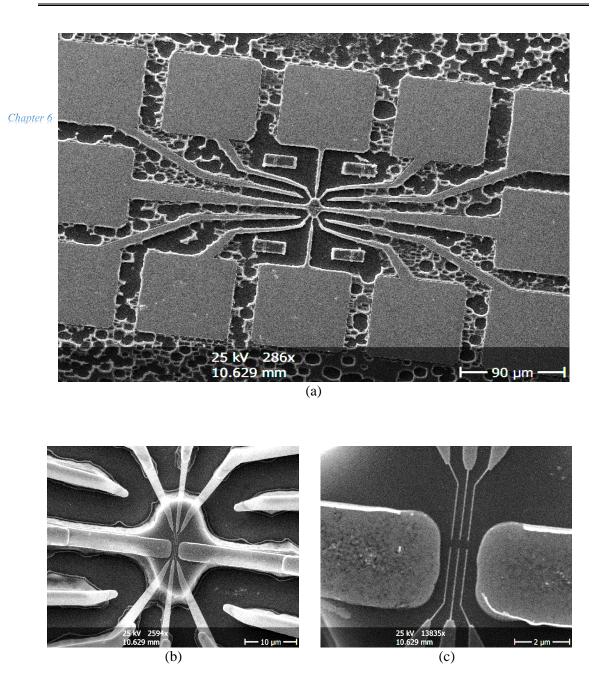

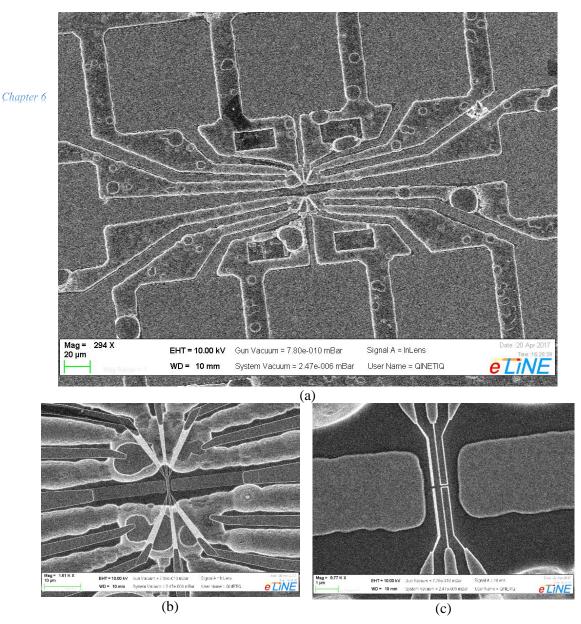

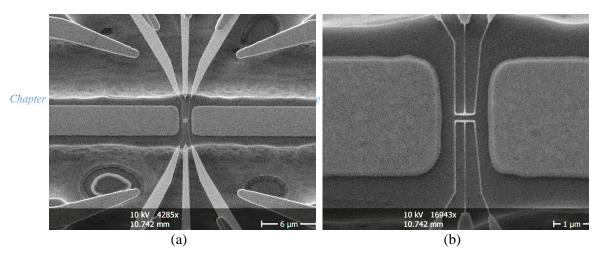

Figure 3. 7: Circuit of split gate device measurement. The source-drain for two Ohmic contacts and one channel for both gates is shown, with a common earth contact. ...48

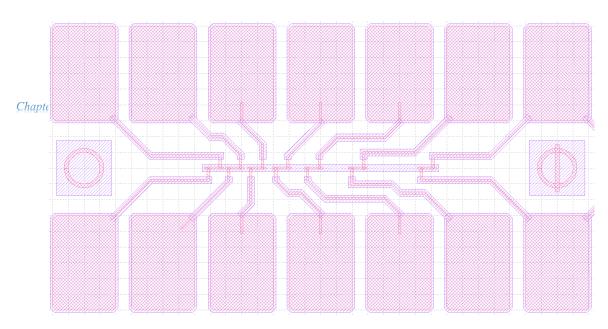

Figure 3.8: Whole TLM device design containing Ohmic pads in the middle connected to feed metal and bond pads. This also shows the active MESA area in the centre. 49

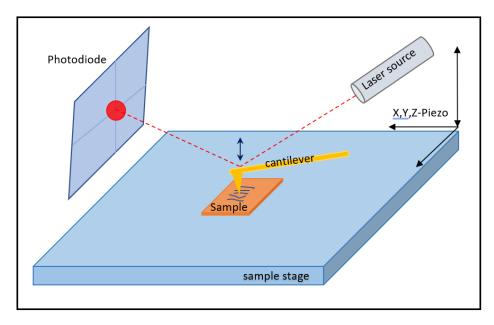

Figure 3.17: Principle of operation of the atomic force microscope, including cantilever moving up and down, photodetector with red spot and laser source......61

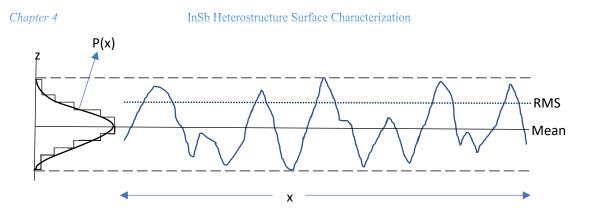

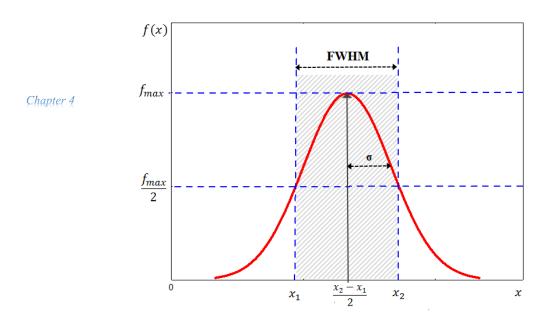

Figure 4. 6: Relationship between the standard deviation  $\sigma$  and the full width at halfmaximum (FWHM) of Gaussian distribution (frequencies of roughnesses)......77

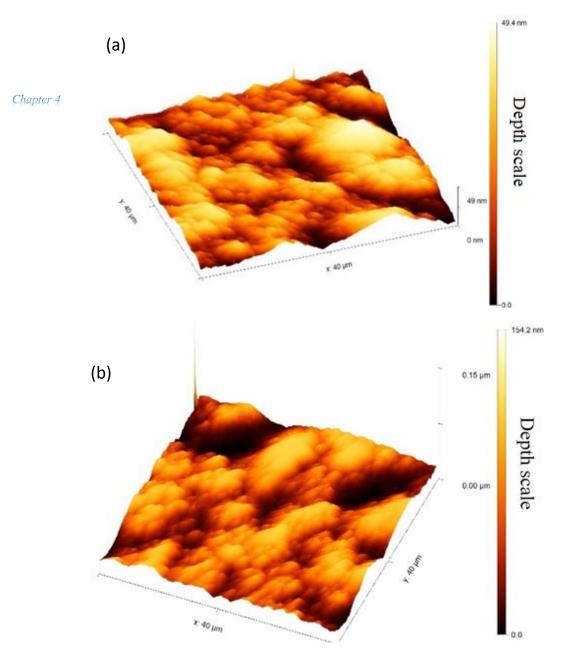

| Figure 4. 8: AFM images of AlInSb/InSb wafer in three-dimensional profile; (a) at |

|-----------------------------------------------------------------------------------|

| zero degrees on the wafer, and (b) at 90-degrees, the AFM tip measurement of the  |

| same area                                                                         |

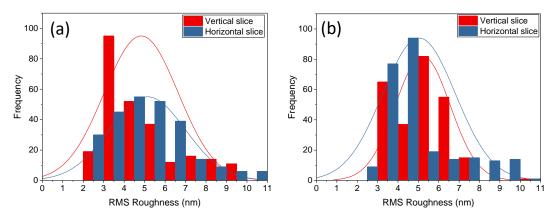

*Figure 4. 9: Histogram of the pristine sample in vertical and horizontal slices with; (a) zero degrees and, (b) 90-degrees AFM tip direction measuring......80*

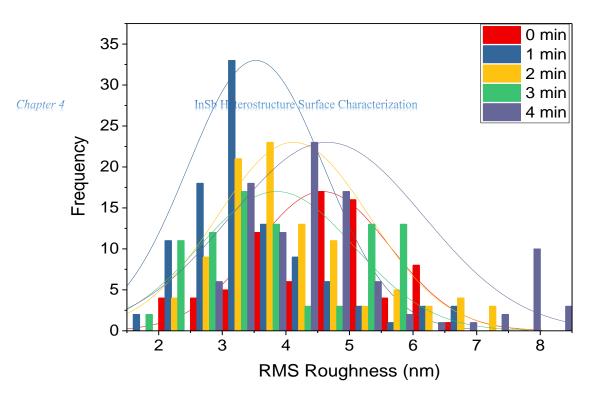

Figure 4. 15: Histogram for citric acid etched samples as a function of RMSRoughness in horizontal axis.86

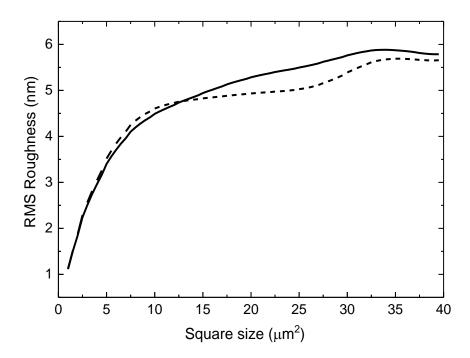

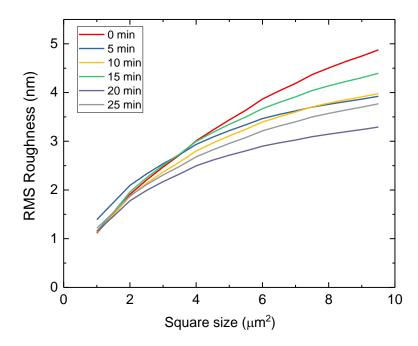

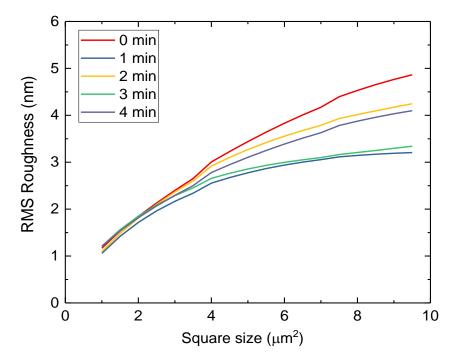

| Figure 4. 20: RMS Roughness as a function of square size for the citric acid etched   |

|---------------------------------------------------------------------------------------|

| samples                                                                               |

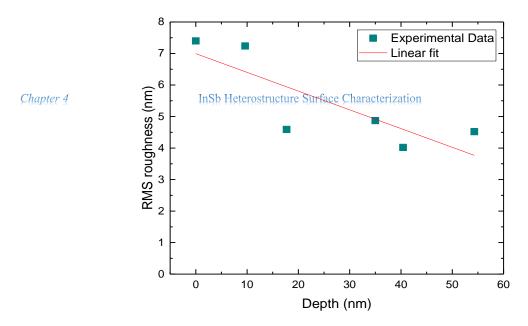

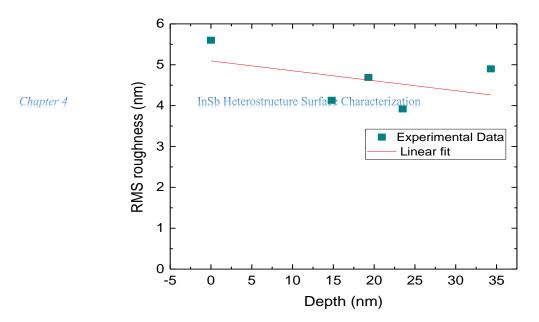

| Figure 4. 21: RMS roughness for full trench area by Citric acid versus depth91        |

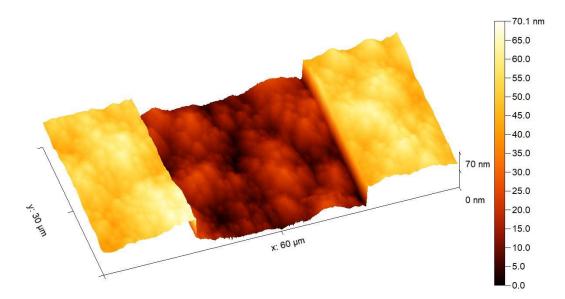

| Figure 4. 22: AFM image in three-dimensional profile for the etched AlInSb/InSb       |

| wafer by means of IBM technique92                                                     |

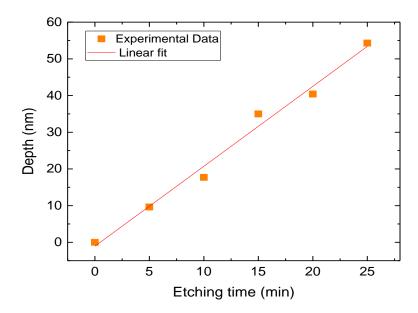

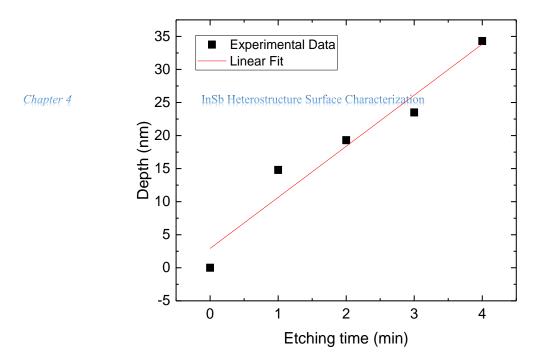

| Figure 4. 23: Ion Beam Etching depth as a function of time                            |

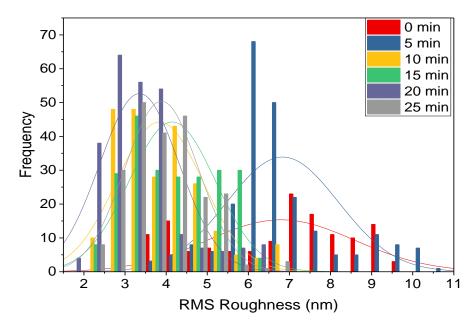

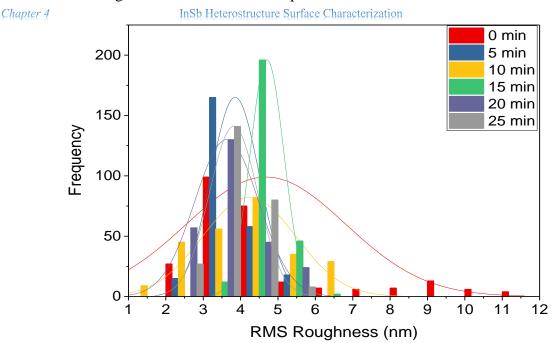

| Figure 4. 24: Histogram for IBM etched samples as a function of RMS roughness in      |

| the vertical axis                                                                     |

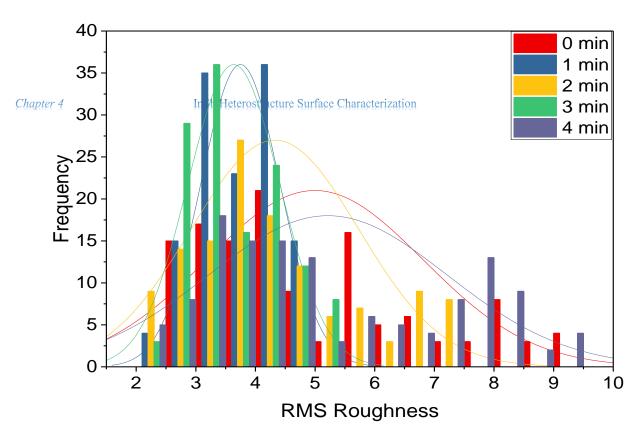

| Figure 4. 25: Histogram for IBM etched samples as a function of RMS roughness in      |

| the horizontal axis                                                                   |

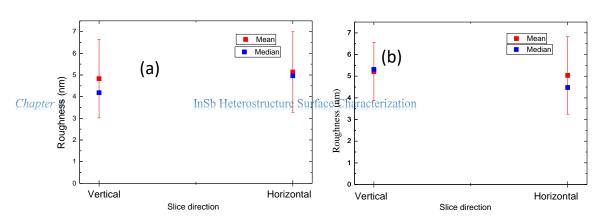

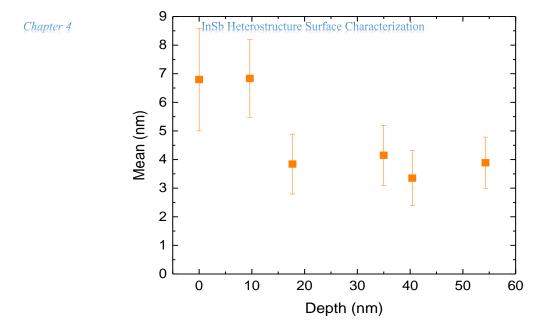

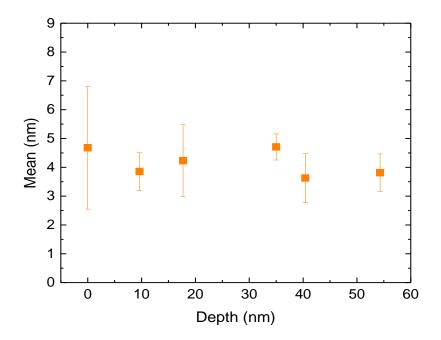

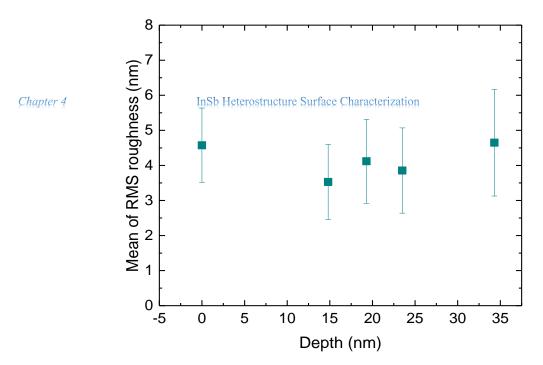

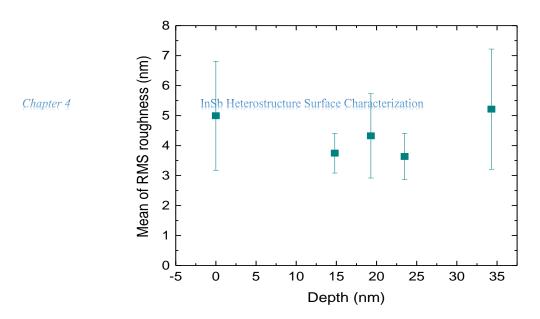

| Figure 4. 26: Mean and standard deviation bars for IBM etched samples in the vertical |

| axis as a function of etching depth96                                                 |

| Figure 4. 27: Mean and standard deviation bars for IBM etched samples in the          |

| horizontal axis as a function of etching depth97                                      |

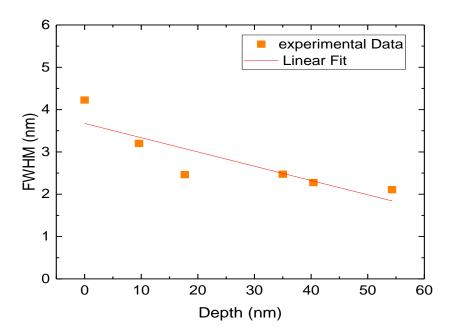

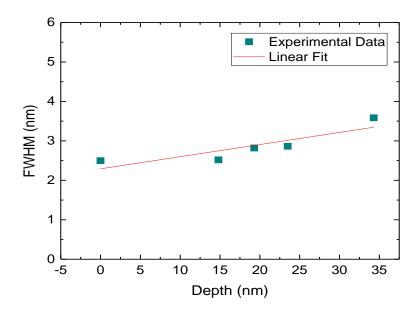

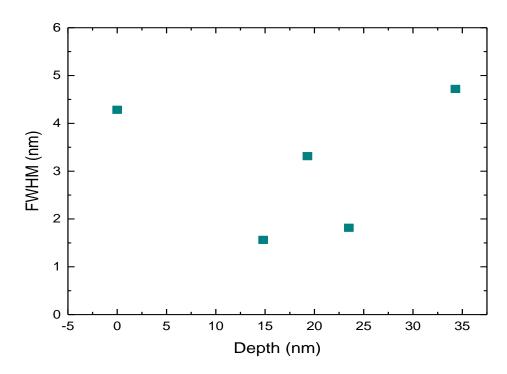

| Figure 4. 28: Full Width at Half maximum value for IBM etched samples in the vertical |

| axis as a function of etching depth97                                                 |

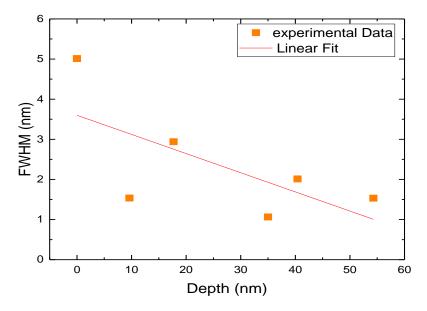

| Figure 4. 29: Full Width at Half maximum value for IBM etched samples in the          |

| horizontal axis as a function of etching depth                                        |

| Figure 4. 30: Square area average RMS roughness for only IBM etched areas99           |

| Figure 4. 31: RMS roughness for full trench area by IBM versus depth100               |

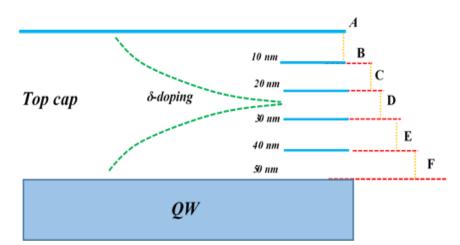

| Figure 5. 1: AlInSb/ InSb wafer etching depth using citric acid for samples A–F106    |

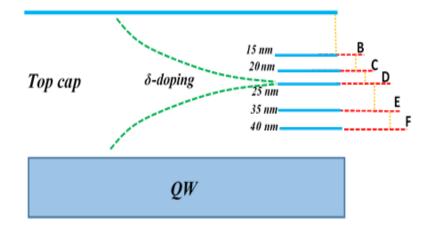

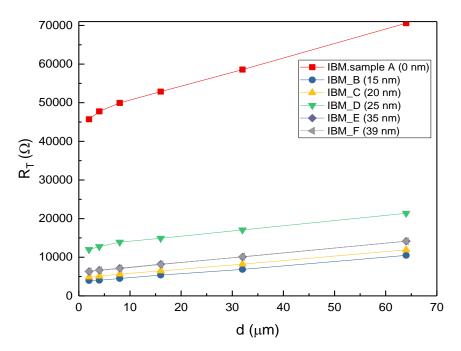

| Figure 5. 2: AlInSb/ InSb wafer etching depth using IBM for samples A–F107            |

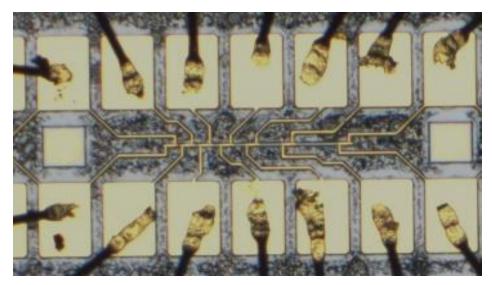

| Figure 5. 3: LTLM device with gold wires connected to FEED pads measuring             |

| resistance for 2–64 µm distances                                                      |

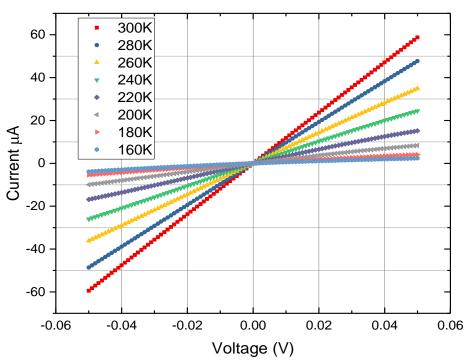

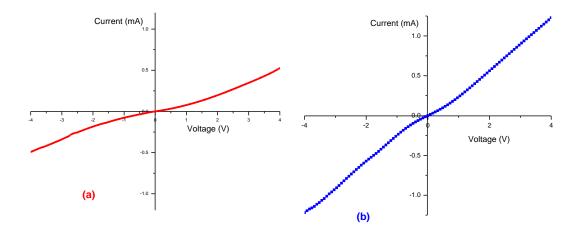

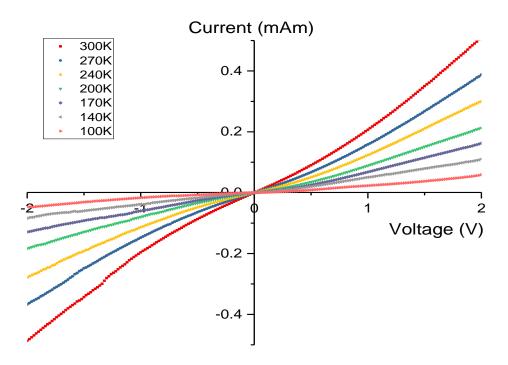

| Figure 5. 4: I–V characteristics of LTLM | contacts for InSb 2DEG over a range of |

|------------------------------------------|----------------------------------------|

| temperatures                             |                                        |

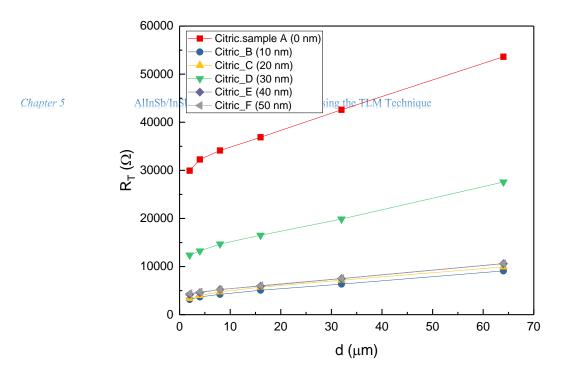

| Figure 5. 5: Total resistance of contacts of LTLM device versus distance with different |

|-----------------------------------------------------------------------------------------|

| citric etching depths at room temperature using SF1258 wafer110                         |

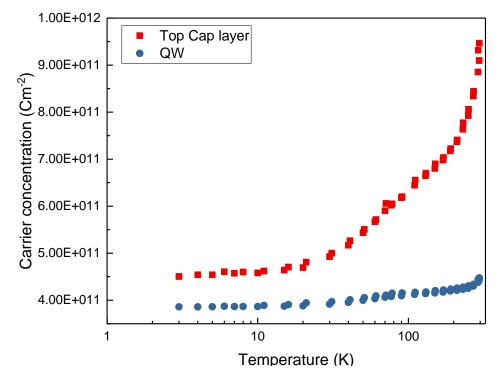

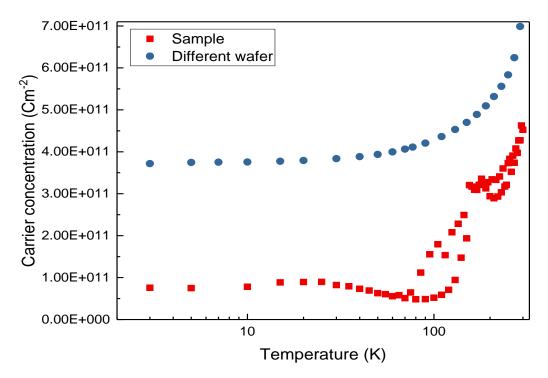

Figure 5. 7: Carrier concentration in the top cap layer and QW of AlInSb/InSb wafer, measured by the Hall technique using bar device in ratio 1/5 dimension......111

| Figure 5. 8: A semilog contact resistivity | versus temperature for contacts etched by |

|--------------------------------------------|-------------------------------------------|

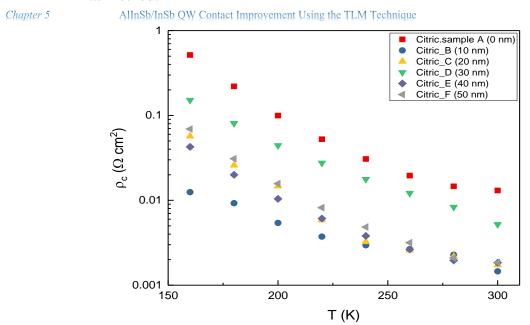

| citric acid over a range of depth          |                                           |

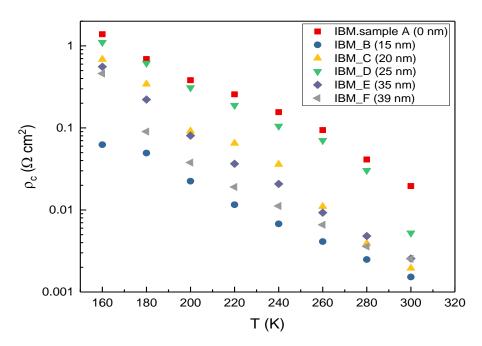

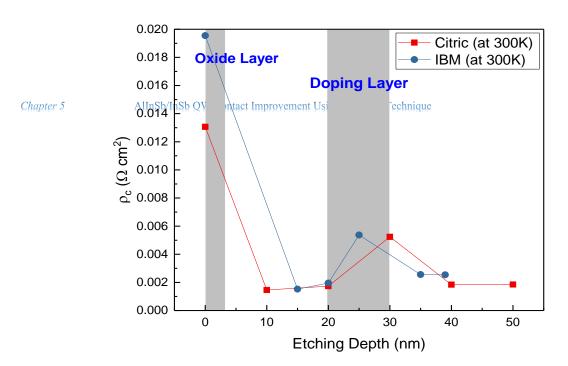

Figure 5. 15: Contact resistivity as a function of citric acid and IBM etching depth into top cap layer (AlInSb) at 300K. This curves hapoe is important and shows a

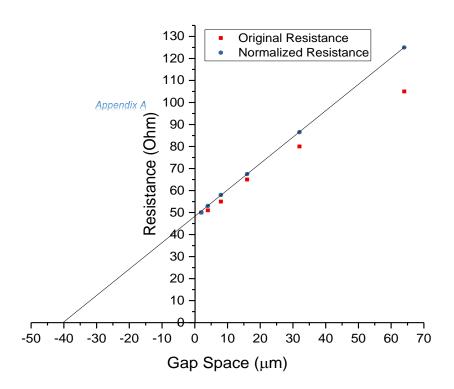

| Figure A. 2: The resistance for circular structure ver | rsus gap spacing before and after |

|--------------------------------------------------------|-----------------------------------|

| applying the correction factors.                       |                                   |

# LIST OF TABLES

| Table 1.1: Fundamental properties of some semiconductor materials, including direct    |

|----------------------------------------------------------------------------------------|

| energy band gap $E_g$ , electron effective mass $m^*$ , electron g-factor and electron |

| <i>mobility at 300K [11][15][17][29].</i>                                              |

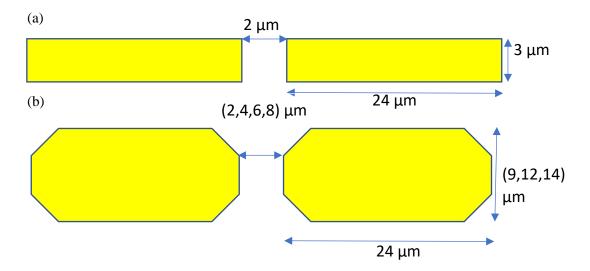

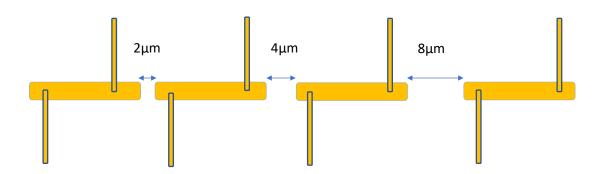

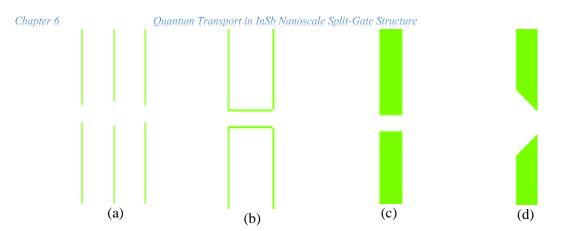

| Table 3.1: Loop split gates dimensions                                                 |

| Table 3.2: Line and solid split gate dimensions                                        |

| Table 3.3: Triangle solid gate dimensions.    45                                       |

| Table 3.4: The variety of width and length for the Ohmic contact pad TLM design.49     |

| Table 6.1: The used wafer including names, carrier density and electron mobility at    |

| 3K measurements                                                                        |

# LIST OF ABBREVIATIONS

| MBE   | Molecular Beam Epitaxy               |

|-------|--------------------------------------|

| QW    | Quantum Well                         |

| 2DEG  | 2-Dimensional Electron Gas           |

| DOS   | Density of States                    |

| TLM   | Transmission Line Model              |

| LTLM  | Linear Transmission Line Model       |

| IFRS  | Interface Roughness Scattering       |

| XPS   | X-ray photoelectron spectroscopy     |

| EDX   | Energy Dispersive X-ray Spectroscopy |

| AFM   | Atomic Force Microscopy              |

| EBL   | Electron Beam Lithography            |

| SEM   | Scanning Electron Microscopy         |

| PMMA  | Poly (Methyl MethAcrylate)           |

| IBM   | Ion Beam Milling                     |

| FWHM  | Full Width at Half Maximum           |

| RMS   | Root Mean Square                     |

| TDs   | Threading Dislocations               |

| TEM   | Transmission Electron Microscope     |

| RTA   | Rapid Thermal Annealing              |

| I-V   | Current Voltage                      |

| FE    | Field Emission                       |

| I-V-T | Current Voltage Temperature          |

| MS    | Metal Semiconductor                  |

| TE    | Thermionic Emission                  |

| TFE   | Thermionic Field Emission            |

# Chapter 1

Chapter 1

Introduction

### Introduction

### 1.1 Motivation

The semiconducting properties of indium antimonide (InSb) first became known in the early 1950s [1]–[4]. Numerous scientific investigations have since been performed on this material. However, even after 60 years of research, the growth of InSb crystals and their characterisation continues to evoke keen interest due to their innovative properties and their novel technological applications in areas such as thermal imaging and more recently nanoscale electronic devices [5]–[7].

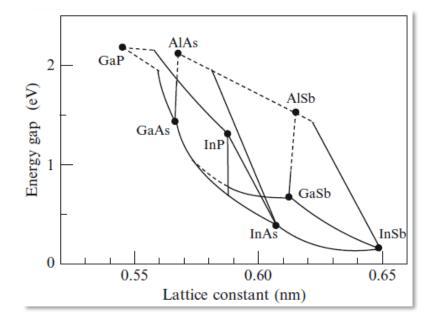

Nanoscale quantum devices have attracted attention over recent years, and they have yielded some landmark fundamental studies of electronic states in matter, as well as potential applications in metrology and single electron sensing in quantum computing qubit implementations. A high-quality InSb quantum well (QW) two-dimensional electron gas (2DEG) is highly desired because of its unique and extreme properties compared to all other binary III-V compound semiconductors, having the narrowest band gap, lightest electron effective mass, largest Landé g-factor and highest intrinsic electron mobility amongst the currently known binary III-V compounds. These novel properties allow for a wide range of potential applications in nanoscale electronics and optoelectronics. This means that InSb QWs are an interesting material for fabricating high-speed and low power devices, spintronic devices, magnetic field sensors, middleto-long wavelength photon detectors, and so on [8]-[13]. Table 1.1 shows some of the fundamental properties of the intrinsic semiconductors Si and Ge, as well as III-V compound semiconductor materials. InSb is a direct bandgap semiconductor with energy band gap  $(E_g)=0.235$  eV at low temperature because of its conventional negative temperature coefficient. The energy gap decreases to about 0.22 eV and 0.18 eV at 77K and room temperature, respectively [14]–[16].

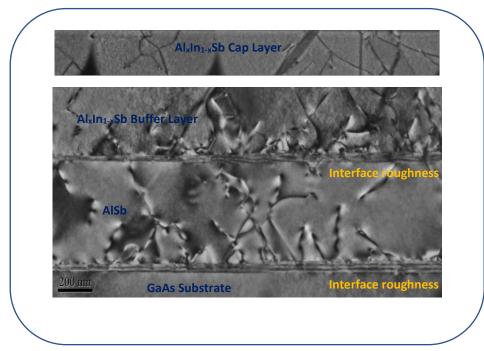

InSb's mobility (µ<sub>e</sub> =78000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) is the highest reported electron mobility at room temperature in comparison to any compound semiconductor. It has been reported to have mobilities in excess of (200000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) at 1.8K in two-dimensional electron *Chapter 1* gas (2DEG) channels [17]–[20], which is respectable, but still low in comparison to other materials, such as GaAs. This is due primarily to threading dislocations coming from lattice mismatch of the 2DEG and the substrate.

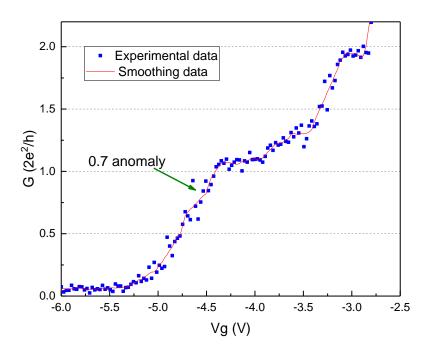

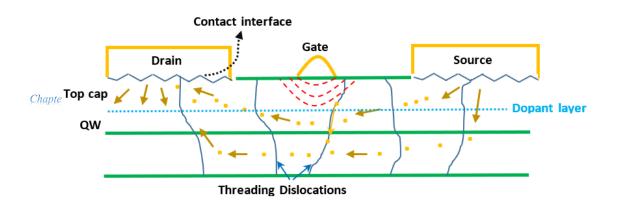

InSb exhibits the lightest electron effective mass (m\*= $0.014m_e$ ) at room temperature. The corresponding high-mobility possible allows for low power consumption devices to be realized [21]. Moreover, it can exhibit effects of quantisation phenomenon at higher temperatures than other materials, (following the Landauer equation [22]). Furthermore, the large *g*-factor makes its electron spin interaction extremely strong. This makes it an ideal material to study spin phenomenon and also facilitates potential exploitation in spintronics and quantum information control [23]–[25]. One of the aspects of potential qubit structures is the successful implementation of flexible surface gated split gate structures for charge sensing (in any spin to charge conversion scheme). Consequently, there is high potential in studying quantized conductance in this material system, and further investigation into the well-known 0.7 conductance anomaly in such a rich spin system may well yield interesting physics. Additionally, the realisation of a superconducting top gate offers the possibility of investigating Majorana physics [26] [27], as a result of the high g-factor.

Despite the apparent advantages of this materials system, significant challenges exist with the basic technology. In particular, ohmic contact technology is frequently inconsistent and with poor contact resistance. It is not well understood what causes this. Standard III-V NiGe:Ni:Au alloyed contacts will not work with this material due to thermal budgets (typical crystal growth temperatures are lower than traditional 385°C contact anneal temperatures. As a result of the variety of applications, there is a high-demand for accurate measurements to evaluate and optimize the contact resistance and specific contact resistance of metal/semiconductor contacts that limit device performance [28].

Table 1.1: Fundamental properties of some semiconductor materials, including direct energy band gap  $E_g$ , electron effective mass  $m^*$ , electron g-factor and electron mobility at 300K [11][15][17][29].

| Chapter <u>1</u> |        |          | Introduction       |                                                 |          |                                |

|------------------|--------|----------|--------------------|-------------------------------------------------|----------|--------------------------------|

|                  | System | Material | $E_g(\Gamma)$ (eV) | <b>m</b> <sup>*</sup> ( <b>m</b> <sub>0</sub> ) | g-Factor | $\mu_{e} (cm^{2}V^{-1}s^{-1})$ |

|                  | IV     | Si       | 1.2                | 0.190                                           | 1.9      | 1450                           |

|                  |        | Ge       | 0.80               | 0.081                                           | 1.6      | 3900                           |

|                  | III-V  | GaAs     | 1.42               | 0.064                                           | -0.4     | 8000                           |

|                  |        | InAs     | 0.35               | 0.023                                           | -15.6    | 33000                          |

|                  |        | InSb     | 0.18               | 0.014                                           | -50.6    | 78000                          |

Despite these impressive features of InSb, many challenges remain. InSb QW growth on GaAs substrates with a large mismatch is an engineering challenge due to the significant strain in the crystal layers. This leads to the inevitable creation of high densities of dislocations, which adversely impact the mobility of the material and significantly degrade the performance of the device (such as gate leakage). This issue has led to a significant effort to eliminate the density of defects using for example super lattice layers, buffer layers, dislocations filtering, and decreasing the surface roughness to release the strain between the layers and improve the material's mobility [26][30]–[37]. Whilst not entirely solving the problems of mismatch, these improvements of the InSb material mobility have encouraged further investigations and applications, such as in high sensitivity magnetic field sensors, high frequency electronics and quantum computer technology [38]. Therefore, quantum devices that utilize the ballistic transport of the carriers will be very attractive for this purpose [39].

### 1.2 Thesis Outline

This research was performed at Cardiff University and it focused on characterising InSb QW 2DEG material, developing metal-semiconductor gate and Ohmic contact technology, and studying electron transport mechanisms and ballistic electron transport in InSb QW 2DEG split gate structures. This thesis is structured as follows.

Chapter 2 describes the physical concepts of the QW and low-dimensional electronic confinement in semiconductor heterostructure systems, specifically for aluminium indium antimonide/indium antimonide (AlInSb/InSb). The ballistic transport mechanism in 2DEG leading to quantisation conductance by using surface split gate

structures is then described. The electron transport mechanisms through metalsemiconductor (Ohmic) contacts are discussed using the "Transmission Line Model" (TLM) measurement technique.

#### Chapter 1

#### Introduction

Chapter 3 gives an overview of the structure of an InSb crystal, and in the case of the samples studied here, the epitaxial layers and its bandgap engineering, along with a description of the wafer fabrication and characterisation techniques. The split gate and TLM devices designs are described in detail, together with the techniques that were used in the fabrication process. Moreover, the sample packaging, wiring, electrical measurement techniques and variable low temperature set up are also described.

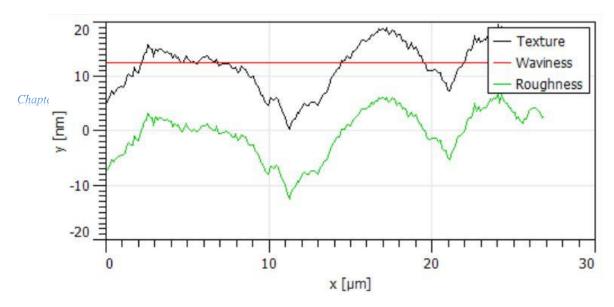

Chapter 4 describes the experimental study of the wafer surface roughness of AlInSb/InSb for a pristine sample and for a variety of surface etched samples. Wet and dry etching techniques are used to etch the Ohmic contact area over a range of depths into the QW layer and comparisons are made. An atomic force microscope (AFM) is used to create surface topography images of etched areas, which were then analysed mathematically using Python code.

Chapter 5 investigates metal-semiconductor contact resistance, sheet resistance and contact resistivity as a function of etching depth, with variable temperatures related to electron transport mechanisms, using the TLM technique.

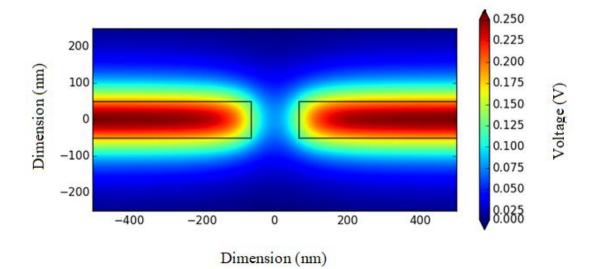

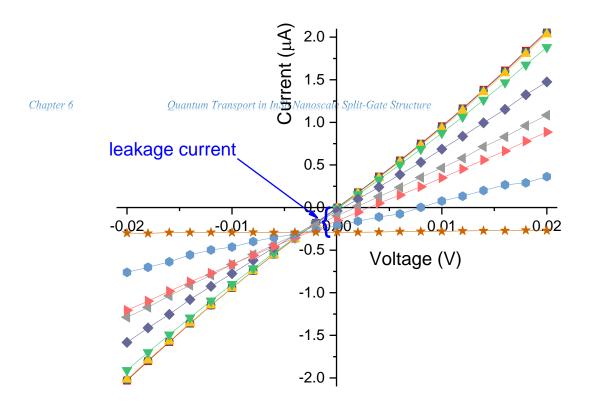

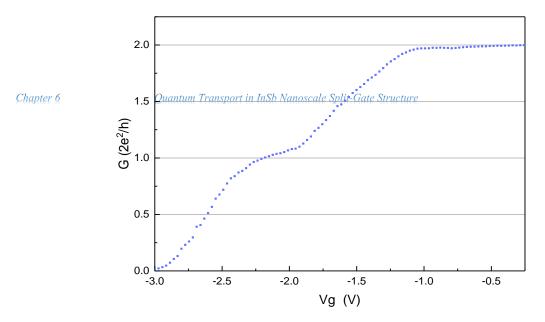

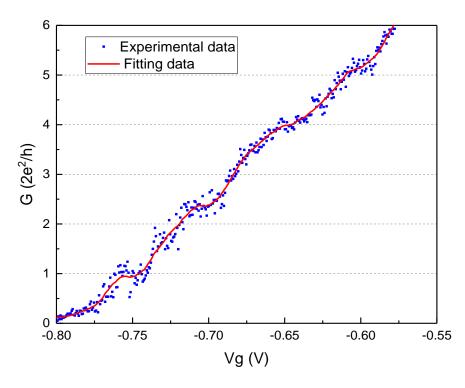

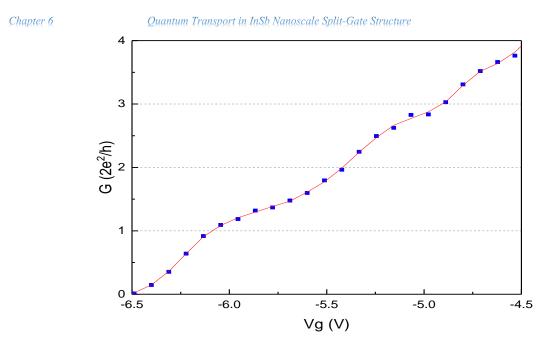

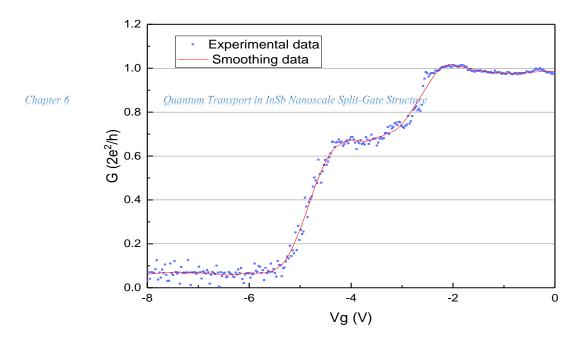

Chapter 6 looks at different designs of surface metal gates and studies the transport that results in quantum conductance. The quantisation conductance is achieved by applying a source-drain voltage via Ohmic contacts and DC voltage on the top gate to increase the resistance, resulting in conductance steps. The results for a range of device designs at low temperature (2.7K) are given here.

Chapter 7 summarises the results from the research undertaken in this thesis, and it briefly discusses future possible research areas.

Appendix is included at the end of the thesis in which relevant addition details are provided for the simulations that were performed. Appendix A includes the theory concepts of an additional kind of TLM, which is a "circular" or "bullseye" CTLM.

### **1.3** Bibliography

[1] M. Tanenbaum and J. P. Maita, "Hall effect and conductivity of InSb single crystals," *Phys. Rev.*, vol. 91, no. 4, pp. 1009–1010, 1953.

- [2] R. G. Bregkenridge, R. F. Bliint, W. R. Hosr, H. P. R. Feederiesz, J. H. Bzceer, and W. Oseinszv, "Electrical and Optical Properties of Intermetallic Compounds. I. Indium Antimonide," *Phys. Rev.*, vol. 96, no. 3, pp. 571–575, 1954.

- [3] D. Long, "Effect of pressure on the electrical properties of indium antimonide," *Phys. Rev.*, vol. 99, no. 2, pp. 388–390, 1955.

- [4] H. Fritzsche and K. Lark-Hqrovitz, "Electrical Properties of p-Type Indium Antimonide at Low Temperatures," *Phys. Rev.*, vol. 99, no. 2, pp. 400–405, 1955.

- [5] A. Rogalski and K. Chrzanowski, "Infrared Devices And Techniques," *OPTO-ELECTRONICS Rev.*, vol. 10, no. 2, pp. 111–136, 2002.

- [6] T. Ashley *et al.*, "Epitaxial InSb for elevated temperature operation of large IR focal plane arrays," *Infrared Technol. Appl. XXIX*, vol. 5074, pp. 95–102, 2003.

- [7] D. A. Huckridge *et al.*, "Albion camera: a high-performance infrared imaging system," *Infrared Technol. Appl. XXX*, vol. 5406, no. 44, pp. 163–169, 2004.

- [8] D. Bimberg, *Semiconductor Nanostructure*. 2008.

- [9] Y. Wang *et al.*, "Bonding and diffusion of nitrogen in the InSbN alloys fabricated by two-step ion implantation," *Appl. Phys. Lett.*, vol. 101, no. 2, pp. 0–4, 2012.

- [10] Y. J. Jin, D. H. Zhang, X. Z. Chen, and X. H. Tang, "Sb antisite defects in InSb epilayers prepared by metalorganic chemical vapor deposition," *J. Cryst. Growth*, vol. 318, no. 1, pp. 356–359, 2011.

- [11] Y. J. Jin, X. H. Tang, J. H. Teng, and D. H. Zhang, "Optical properties and bonding behaviors of InSbN alloys grown by metal-organic chemical vapor deposition," J. Cryst. Growth, vol. 416, pp. 12–16, 2015.

- [12] S. R. Jost, V. F. Meikleham, and T. H. Myers, "InSb: A key material for IR detector applications," *Mater. Res. Soc.*, vol. 90, pp. 429–435, 1987.

- [13] I. Žutić, J. Fabian, and S. Das Sarma, "Spintronics Fundamentals and applications.pdf," *Rev. Mod. Phys.*, vol. 76, no. 2, pp. 323–410, 2004.

- [14] I. Vurgaftman, J. R. Meyer, and L. R. Ram-Mohan, "Band parameters for III-V compound semiconductors and their alloys," *J. Appl. Phys.*, vol. 89, no. 11 I, pp. 5815–5875, 2001.

- [15] P. Y. Liu and J. C. Maan, "Optical properties of InSb between 300 and 700 K.

I. Temperature dependence of the energy gap," *Phys. Rev. B*, vol. 47, no. 24, pp. 16274–16278, 1993.

- [16] C. Lárez and C. Rincón, "Temperature dependence of the fundamental energy gap in InSb," *Mater. Lett.*, vol. 24, no. 4, pp<sub>at</sub>21<sub>t</sub>1<sub>Tt</sub>213, 1995.

- [17] W. Yi *et al.*, "Gate-tunable high mobility remote-doped InSb/In1-x Alx Sb quantum well heterostructures," *Appl. Phys. Lett.*, vol. 106, no. 14, p. 142103, 2015.

- [18] O. J. Pooley *et al.*, "Quantum well mobility and the effect of gate dielectrics in remote doped InSb-AlxIn1-xSb heterostructures," *Semicond. Sci. Technol*, vol. 25, pp. 1–7, 2010.

- [19] J. M. S. Orr *et al.*, "Electronic transport in modulation-doped InSb quantum well heterostructures," *Phys. Rev. B*, vol. 77, no. 165334, pp. 1–7, 2008.

- [20] F. Qu *et al.*, "Quantized conductance and Large g-Factor Anisotropy in InSb Quantum Point Contacts," *Nano Lett.*, vol. 16, pp. 7509–7513, 2016.

- [21] L. and B. O. Madelung, U. Rössler, M. Schulz, *Group III Condensed matter: Group IV Elements, IV-IV and III-V Compounds. Part b - Electronic, Transport, Optical and Other Properties.* Springer, 2002.

- [22] D. K. Ferry and S. M. Goodnick, *Transport in Nanostructures*. Cambridge University Press, 1997.

- [23] J. W. G. Van Den Berg *et al.*, "Fast spin-orbit qubit in an indium antimonide nanowire," *Phys. Rev. Lett.*, vol. 110, no. 6, pp. 1–5, 2013.

- [24] R. Li, J. Q. You, C. P. Sun, and F. Nori, "Controlling a nanowire spin-orbit qubit via electric-dipole spin resonance," *Phys. Rev. Lett.*, vol. 111, no. 8, pp. 1–5, 2013.

- [25] D. D. Awschalom, L. C. Bassett, A. S. Dzurak, E. L. Hu, and J. R. Petta, "Quantum Spintronics: Engineering and Manipulatin Atom-Like Spins in Semiconductors," *Science (80-.).*, vol. 339, pp. 1174–1179, 2013.

- [26] Z. Lei *et al.*, "Quantum transport in high-quality shallow InSb quantum wells," no. April, pp. 2–5, 2019.

- [27] V. Mourik, K. Zuo, S. M. Frolov, S. R. Plissard, E. P. A. M. Bakkers, and L. P. Kouwenhoven, "Signatures of Majorana Fermions in Topological Superconductor Nanowires," *Science (80-. ).*, vol. 336, pp. 1003–1008, 2012.

- [28] J. H. Klootwijk and C. E. Timmering, "Merits and limitations of circular TLM structures for contact resistance determination for novel III-V HBTs," *Proc. IEEE 2004 Int. Conf. Microelectron. Test Struct.*, vol. 17, pp. 247–252, 2004.

- [29] J. Low, M. Kreider, D. Pulsifer, A. Jones, and T. Gilani, "Band Gap Energy in Silicon," *Am. J. Undergrad. Res.*, vol. 7, no. 1, pp. 27–31, 2008.

- [30] C. A. Lehner *et al.*, "Limiting scattering processes in high-mobility InSb quantum wells grown on GaSb buffer systems," *Phys. Rev. Mater.* 2, vol. 2, no. 054601, pp. 1–12, 2018.

- Chapter [31] Y. Shi, D. Gosselink, K. Gharavi, J. Baugh, and Z. R. Wasilewski, "Optimization of metamorphic buffers for MBE growth of high quality AlInSb / InSb quantum structures : Suppression of hillock formation," J. Cryst. Growth, vol. 477, pp. 7–11, 2017.

- [32] X. Zhao *et al.*, "Effect of InSb/In0.9Al0.1Sb superlattice buffer layer on the structural and electronic properties of InSb films," *J. Cryst. Growth*, vol. 470, pp. 1–7, 2017.

- [33] S. Fujikawa, T. Taketsuru, D. Tsuji, T. Maeda, and H. I. Fujishiro, "Improved electron transport properties of InSb quantum well structure using stepped buffer layer for strain reduction," *J. Cryst. Growth*, vol. 425, pp. 64–69, 2015.

- [34] M. Y. Chernov *et al.*, "InSb/InAs/InGa(Al)As/GaAs(001) metamorphic nanoheterostructures grown by MBE and emitting beyond 3 μm," *J. Cryst. Growth*, vol. 477, pp. 97–99, 2017.

- [35] B. W. Jia, K. H. Tan, W. K. Loke, S. Wicaksono, and S. F. Yoon, "Formation of periodic interfacial misfit dislocation array at the InSb/GaAs interface via surface anion exchange," *J. Appl. Phys.*, vol. 120, no. 3, 2016.

- [36] T. D. Mishima, M. Edirisooriya, N. Goel, and M. B. Santos, "Dislocation filtering by AlxIn1-xSb/Al yIn1-y Sb interfaces for InSb-based devices grown on GaAs (001) substrates," *Appl. Phys. Lett.*, vol. 88, no. 19, pp. 10–13, 2006.

- [37] A. A. Podpirka, M. E. Twigg, J. G. Tischler, R. Magno, and B. R. Bennett, "Step graded buffer for (110) InSb quantum wells grown by molecular beam epitaxy," *J. Cryst. Growth*, vol. 404, pp. 122–129, 2014.

- [38] Ö. Gül *et al.*, "Hard Superconducting Gap in InSb Nanowires," *Nano Lett.*, vol. 17, no. 4, pp. 2690–2696, 2017.

- [39] D. K. Ferry, S. M. Goodnick, and J. Bird, *Transport in Nanostructures*, Second Edi. Cambridge University Press, 2009.

Chapter 4

# Chapter 2

Chapter 4

InSb Heterostructure Surface Characterization

### Theory and Background

### 2.1 Introduction

Semiconductor materials that consist of two or more elements from the periodic table are known as compound semiconductors and they include binary compounds such as indium antimonide (InSb) and ternary alloys such as aluminium indium antimonide (AIInSb). Compound semiconductors that are derived of elements from group three and five of the periodic table are generally known as III–V semiconductors. Whilst it is not used widely, InSb has attractive semiconducting properties and this has led to interest in its uses in many electronic, optoelectronic and electromagnetic devices. This material can be grown by the molecular beam epitaxy (MBE) technique that can achieve high-quality semiconductor crystal growth and enables the growth of, for example, heterostructures and quantum wells (QWs) to be engineered. These dimensions possible for growth enables carrier quantisation effects to be achieved in real semiconductor devices.

InSb nanostructures may allow us to more easily study *ballistic transport* in QWs due to the large mean free path of electrons (as a result of the light electron effective mass). For devices this can result in electrons flow from the filled states one side of a device to flow to empty states without scattering. Consequently, this material should exhibit clear one-dimensional conductance quantization, an important mesoscopic phenomenon. However, in practice, the immature technology of things like the metal–semiconductor contact (Ohmic contact) plays a vital role in overall device performance and can dominate any observable effects.

This chapter begins with an overview of the basic principles of Ohmic contact formation, and the transmission line model technique will then be used to introduce the determination of specific contact resistance, which is the most important property

of Ohmic contacts, as well as the sheet resistance of the InSb QW samples used. Finally, electron scattering mechanisms will be introduced that have influence on the electron mobility, ballistic transport and ultimately observable conductance *Chapter 4* quantization. InSb Heterostructure Surface Characterization

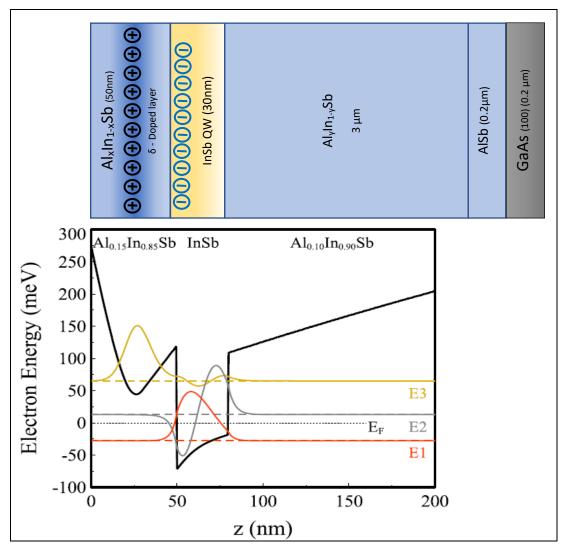

### 2.2 Quantum Well

A QW is a series of semiconductor layers grown with a sandwich-like structure with a large difference in energy between the conduction bands of the bottom and top layers and the sandwiched intermediate layer. The electronic properties of InSb and AlInSb materials are well-suited to QW architecture [1]. Hence, the QW cladding layers (AlInSb layers (top and bottom) are thick or the conduction bands potential on both sides are sufficiently high, such that the electron tunnelling out can be considered negligible and the electrons will be confined in the growth direction (conventionally the z direction) and are free to move in the x and y plane of the QW [2]. The electronic states under this confinement are then quantised to a discrete number of energy levels, which are given by solutions of Schrödinger's equation.

The confining potentials in QW heterostructure devices are due to the band offsets (which will be discussed in more detail in Chapter 3) at the interfaces in double-junction QWs [2].

### 2.2.1 The Finite Quantum Well

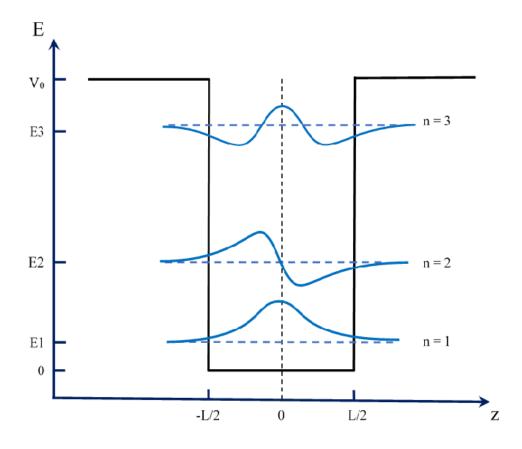

The finite QW is sketched in *Figure 2*. *1*, which explains the band diagram of an ideal QW with a finite potential barrier of height  $V_o$  at each interface such that.

$$V_{o} = \begin{cases} V_{o} & z < -\frac{L}{2} \\ 0 & -\frac{L}{2} \le z \le \frac{L}{2} \\ V_{o} & z > \frac{L}{2} \end{cases}$$

(2-1)

The states are described by the time-independent Schrödinger equation: [3][4]

$$-\frac{\hbar^2}{2m_*}\frac{d^2\Psi(z)}{dz^2} = E \Psi(z) \quad \text{(within the QW)}$$

$$-\frac{\hbar^2}{2m_*}\frac{d^2\Psi(z)}{dz^2} + V_0\Psi(z) = E \Psi(z) \quad \text{(within the barrier regions)}$$

(2-2)

(2-3)

ChapteA finite number of states are confined in this region, which are labelled with a quantum number n:  $m^*$  is the particle effective mass, E is the energy and  $\Psi(z)$  is the particle wavefunction.

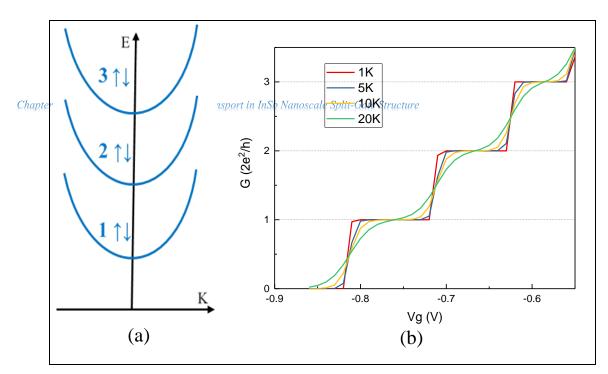

*Figure 2. 1:* A schematic energy-band diagram of a QW as a function of confinement direction, when E1, E2, E3 are the bound states in the finite quantum well as a function of the wave vector.

According to quantum theory, the wavefunction is non-zero at the barrier interface, which has to be considered with the solution of the following equation. Therefore, the wavefunctions within the QW can be written:

$$\Psi_w(z) = Asinknz \tag{2-4}$$

$$\Psi_w(z) = Bcosknz \tag{2-5}$$

for even and odd values of n. The wavefunction in the barrier region can be written in the form

Chapter 4

### InSb Heterostruc $\Psi_{b}(z)$ r $f= C \partial \overline{\Pi} k^{2}$ cterization

(2-6)

where, A, B and C are constants. The states of the system can be described by two parameters: a quantum number n to indicate the energy level for the *z*-direction, and a wave vector k to specify the free motion in the x, y plane. The wavevector is

$$k_n = \left[\frac{2m_w^* E}{\hbar^2}\right]^{1/2}$$

(2-7)

Whereas, the wave vector value in the barrier region is

$$k_{z} = \left[\frac{2m_{b}^{*}(V_{o} - E)}{\hbar^{2}}\right]^{1/2}$$

(2-8)

where  $m_w^*$  and  $m_b^*$  denote the effective mass of the QW and the barrier material, respectively [5][6].

Using boundary conditions, by equating  $\Psi$  in the well and the barrier, considering z = +L/2 at the interface:

$$B\cos\left(\frac{k_nL}{2}\right) = Ce^{\left(-\frac{kL}{2}\right)}$$

(2-9)

and equating the derivatives gives:

$$-kAsin\left(\frac{k_nL}{2}\right) = -kCe^{\left(-\frac{kL}{2}\right)}$$

(2-10)

By dividing equation (2-9) equation (2-10) then gives:

$$-\frac{1}{k_n} Cot\left(\frac{k_n L}{2}\right) = -\frac{1}{k}$$

(2-11)

$$\therefore k_n \tan\left(\frac{k_n L}{2}\right) - k = 0 \tag{2-12}$$

Following through the same analysis as above gives the equation to be solved for the odd parity eigen energies also (but odd parity states would require the choice of wave function in the well region as a sine wave). This results in:

$$k_n \cot\left(\frac{k_n L}{2}\right) + k = 0 \tag{2-13}$$

Since both  $k_n$  and k are functions of the energy E, then equations (2-12) and (2-13) are also functions of E. These two equations can be solved numerically or graphically [6].

The wave vectors and decay constants in equations (2-12) and (2-13) normalized to obtain dimensionless values,  $v = k_n L/2$  and u = kL/2 yielding

Chapter 4

$$\mathbf{u}_{S} = \mathbf{v}_{erostructure Surface Characterization}^{\text{tan } v} (even parity)$$

(2-14)

This expression can be written in terms of the variable v by making further substitution  $u_0^2 = v^2 + u^2$  such that:

$$\sqrt{u_0^2 - v^2} = v \begin{cases} \tan v & (even parity) \\ -\cot v & (odd parity) \end{cases}$$

(2-15)

So,  $u_0$  value can be found by substituting in the definitions of  $u, v, k_n$  and k:

$$u_0^2 = v^2 + u^2 = \frac{L^2}{4} (K_n^2 + k^2)$$

(2-16)

$$=\frac{2m^{*}L^{2}}{4\hbar^{2}}\left(E+V-E\right)$$

(2-17)

$$=\frac{m^*L^2V}{2\hbar^2} \tag{2-18}$$

Therefore, the  $u_0$  value contains all the structural information including effective mass, barrier height and well width for the finite well system.

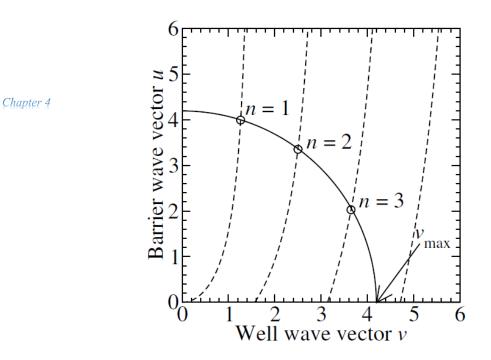

Plotting barrier wave vector u as a function of well wave vector v and the intersections (drawn as open circles) show the wave vectors of the bound states and the maximum possible wave vector in the well is denoted as  $v_{max}$ .

Figure 2. 2: Barrier wave vector as a function of well wave vector, when the lefthand side of equation (2-15) is plotted as a solid line and the right-hand side is plotted as a set of dashed lines.

Thus, each crossing point is a unique solution of  $k_n$  value and therefore unique value of energy as plotted in *Figure 2. 1*.

$$E_n = \frac{\hbar^2 k_n^2}{2m^*}$$

(2-19)

#### 2.2.2 Density of States

The density of states is defined as the density of allowed energy states per unit volume/area/length depending on dimensionality. Electron states in structures are obtained by solving the wave equation for the potential distribution in the structure by using the bulk physical constants and by applying the so-called effective mass approximation, under which the electron energy can be written as follows:

$$E = \frac{\hbar^2 k^2}{2m^*} = \frac{\hbar^2 k_{x,y,z}^2}{2m^*}$$

(2-20)

and the solution of the electron wavefunction satisfies Schrödinger's equation and is of the form:

$$\psi_k(r) = U_k(r)e^{ik.r} \tag{2-21}$$

where r = (x, y, z),  $U_k(r)$  is a periodic function (Bloch function) and exp(ik.r) is a plane wave. Chapter 4 InSb Heterostructure Surface Characterization

Due to the periodicity of the lattice, the probability of finding an electron in one position is also periodic and, therefore, the wavevector will be:

$$k_x = \frac{2\pi n_{x,y,z}}{L} \tag{2-22}$$

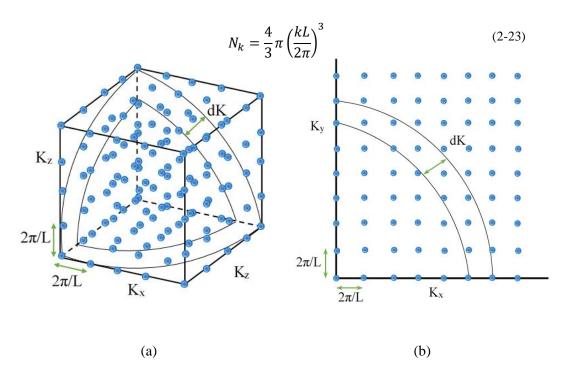

where  $n_{x,y,z}$  are integers. *Figure 2. 3* shows that an allowed state in the lattice exists in a k-space volume  $(2\pi/L)^3$ , so the total number of states up to the wavevector k is given by:

Figure 2. 3: Reciprocal lattice of a cubic lattice in 3D (a) and 2D (b).

Therefore, the density of states considering the spin degeneracy (spin up and spin down), such that:

$$g_{3D}(E) = 2dN_k = \frac{L^3 k^2}{\pi^2} dk$$

(2-74)

By differentiating Equation 2-11, the density of states within an energy range E+dE, is then given by:

$$g_{3D}(E)dE = \frac{1}{2\pi^2\hbar^3} (2m^*)^{3/2} E^{1/2} dE$$

(2-25)

The density of states of a two-dimensional (2D) system is a similar calculation in method as for three dimensions. However, the electrons are now confined in the *z*-*Chapter 4* direction and the volume  $(2\pi/L)^2$  of the single energy state is considered in twodimensional k-space (a circle), which results in:

$$g_{2D}(E)dE = \frac{m^*}{\pi\hbar^2} dE$$

(2-26)

This shows that the density of states in two-dimensions does not depend on the energy. Consequently, a considerable number of states are available at the lowest energy, unlike the 3D case which builds parabolically. The total density of states has to be modified by taking into account the confinement energies in the QW and can be written as

$$g_{2D}(E)dE = \frac{m^*}{\pi\hbar^2} \sum_{i} \Theta(E - E_i) dE$$

(2-27)

where  $\Theta(E - E_i)$  is the Heaviside step function centred on the sub-band edge  $E_i$ , (this takes the value of zero if  $E < E_i$  and one if  $E \ge E_i$ , where  $E_i$  is the energy of the *i*<sup>th</sup> level within the QW [2][7]–[11]).

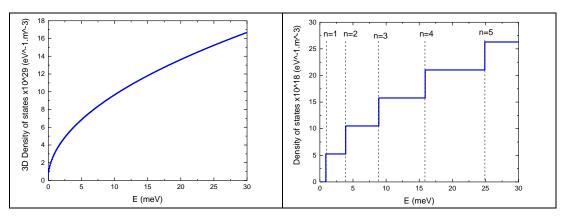

Figure 2. 4: InSb density of states (DOS) in 3D (a) using equation (2-25) and 2D QW(b) using equation (2-27) with quantised energy levels.

*Figure 2. 4* compares the density of states (DOS) of InSb as a function of energy in 2D and 3D. The number of available states in 3D is dependent on  $E^{1/2}$ , whereas the quantization of the electron states in the 2D QW cause the DOS to become invariant with energy and increases in a step-wise way with the increasing number of sub-bands.

## 2.3 Electron Transport

### 2.3.1 Two-dimensional Electron Gas InSb Heterostructure Surface Characterization

Electron transport studies in narrow-gap semiconductors have recently attracted considerable attention because the confinement in a DEG provides a tool to create system with high-electronic mobility. It also permits electrons with a large mean free path to travel up to micrometres before scattering. Control of the mobility has important applications, such as in a magnetic sensor and ballistic transport [12][13].

One of the most significant developments in semiconductors from the point of view of physics and device development is the realisation of 2D structures, which means that electrons are trapped in a narrow potential well that restricts their motion in one dimension and modifies their available states to discrete energy levels. If the separation between these energy levels is large enough, then an electron will appear to be confined in the ground state of this potential well. The result for many electrons is a 2D electron gas (2DEG) [14]. The energy of an electron in a 2DEG according to solutions of Schrödinger's equation is

$$E = \frac{\hbar^2 k^2}{2m^*} = \frac{\hbar^2 (k_x^2 + k_y^2)}{2m^*}$$

(2-28)

### 2.3.2 Ballistic Transport

Semiconductor nanostructures are unique in offering the possibility to study quantum transport in an artificial potential landscape. Ballistic conduction is the transport of charge carriers in the active region of a 'device', which has negligible electrical resistance caused by scattering. Transport is described purely by Newton's second law in this scenario. Transport is confined to the conduction band above the Fermi energy where the energy states are not fully occupied. The transport properties can be tailored by geometric variations in the same way as tailoring the transmission properties of light in a waveguide [15]–[17].

If there is no barrier to transport, the current flows through the active region as a number of electrons (per unit time) from the source contact. If a barrier is present however a proportion of the injected electrons are reflected back into the source contact and a fraction are transmitted across the barrier (which can take place by quantum tunnelling or by thermal activation say). Note that the charge fluctuations near the barriers may substantially affect the potential near the barriers and so modify *Chapter 4* band structure. The transmission is then controlled by the quantization of conductance (for instance in split gates and quantum point contact devices that result from the discreteness of the number of electron wave energies [15][16][18]. The ballistic transport of an electron can be determined by the mean free path equation [19]:

$$\lambda = \frac{\hbar\sqrt{2\pi}}{e} \cdot \sqrt{n} \cdot \mu \tag{2-29}$$

where  $\mu$  is the electron mobility. The ballistic transport for an InSb QW can be calculated as a function of temperature, from electron concentration (*n*) and mobility ( $\mu$ ) of a two-dimensional electron gas (2DEG). An example measurement of mean free path (deduced from Hall measurement) for a typical InSb 2DEG is shown in *Figure 2.5*.

Figure 2. 5: Temperature dependence of the mean free path of InSb wafer (SF1258) as measured by the Hall effect.

### 2.3.3 Quantized Conductance

The one-dimensional conductance quantization phenomenon is probably one of the most important phenomena exhibited by mesoscopic conductors [18]. This *Chapter A* phenomenon depends on the significance of the Landauer formula, which plays a central role in the study of ballistic transport because it expresses the conductance in terms of a Fermi level property of a system, such as a mesoscopic size system. Quantum tunnelling across a potential well produces a quantization of the conductance, as given by the Landauer formula [15][16]:

$$G = \left(\frac{e^2}{h}\right)T\tag{2-30}$$

where *T* is the electron transmission probability, *e* is electron charge and *h* is Planck's constant. This phenomenon was independently discovered by Van Wees et al. [20] and Wharam et al. [21] in the form of a sequence of steps in the conductance of a point contact using a GaAs 2DEG. These steps are nearly integer multiples of  $2e^2/h$  ( $\approx 13$  K $\Omega^{-1}$ ). The principle of this effect relies on the fact that each 1D sub-band in the constriction contributes  $2e^2/h$  to the conductance. Therefore, the conductance G is quantized and can be written in the form of [15]:

$$G = \left(\frac{2e^2}{h}\right)N\tag{2-31}$$

where *N* is the number of modes or channels participating in the conduction process. These elegant set of experiments and results were revealed by using very-highmobility 2DEGs that formed at the interface between GaAs QW and the doped top cap (AlGaAs) layer. The conductance was measured between two reservoirs (*Ohmic contacts*) where electrons may travel ballistically between at low temperatures. A pair of surface metal gate electrodes are imposed on the top of the heterostructure material to create a *nanoscale constriction* between the two parts of the 2DEG by applying a negative potential on these electrodes, which repels the electrons and subsequently changes the current flow in the QW. These electrodes are electrically isolated from the 2DEG and form a short one-dimensional channel with allowed modes of propagation between the two parts of the broad-area electron gas depending on constriction size. The transmission coefficient is either 0 or 1, depending on whether the sub-band (mode channel) energy lies above or below the Fermi energy. The arrangement of subbands, Fermi energy and the bandgap of InSb structure are depicted in chapter 3. Essentially, the gate bias is varied and the number of channels below the Fermi level is changed as the saddle potential between the gates is raised or lowered. Thus, in the case of a sufficiently large negative gate bias, all of the channels are pinched off and *Chapter 4* conductance drops to zero. A simulation of the quantization conductance steps for InSb at a variety of temperatures are displayed in chapter 6. These results represent a very dramatic verification of the Landauer formula and ballistic transport in mesoscopic systems [16][18][22].

The degree of the plateaus 'flatness' and 'sharpness' varies among devices of identical design, indicating that the detailed shape of the electrostatic potential defining the constriction is significant. Whereas, there are many uncontrolled factors that affect this shape, such as changes in the gate geometry, variations in the Fermi level pinning at the QW, surface or at the interface with the gate metal, doping homogeneity in the heterostructure material and trapping of charge in deep levels in the top cap layer [15].

To model the quantization conductance electron energies in 2DEG of InSb heterostructure, the energy that corresponds to the  $n^{th}$  level is given by:

$$E_n = \frac{\hbar^2 k_n^2}{2m^*} = \frac{\hbar^2}{2m^*} \left(\frac{n\pi}{d}\right)^2$$

(2-32)

where  $m^*$  is effective mass and d is the electron path confined with QW [3]. While, the Fermi energy is giving by:

$$E_F = \frac{\hbar^2 \pi \, n_{2D}}{m^*} \tag{2-33}$$

where  $n_{2D}$  is the carrier density. Therefore, the quantized conductance of electrons in the case of many (*n*) channels is given by the Landauer equation [23]–[25]:

$$G = \frac{2e^2}{h} T \sum_{n}^{\infty} \left( \frac{1}{EXP\left[\frac{-(E_F - E_n)}{KT}\right] + 1} \right)$$

(2-34)

where *T* denotes the transmission probability of a single electron in the QW.

# 2.4 Metal–Semiconductor Contact

#### **2.4.1** Ohmic Contacts InSb Heterostruct

4 InSb Heterostructure Surface Characterization

The metal–semiconductor contact system can either be rectifying such as a Schottky barrier or of broadly linear resistance which is known as an Ohmic contact. This in general depends on the material properties, preparation and characterisation of the contact which have major efforts in device fabrication. Therefore, the metal–semiconductor contact system can be defined as an *Ohmic contact* if has an insignificant junction resistance comparative to the entire resistance of the semiconductor device when the charge carriers flow in either direction without presenting any resistance at the interface. Low Ohmic contact resistance and the quality of Ohmic contacts are important and play a vital role in determining the performance limitations and reliability of many semiconductor devices [26], in particular devices like split gate structures. It is essential to understand the physical nature of Ohmic contacts and pave a way to determine some important basic quantities, such as specific contact resistance, the electron transmission length and the corresponding sheet resistance for the active material.

Essentially, a good Ohmic contact current-voltage characteristic displays a linear relationship and is symmetric with respect to the origin (if a potential barrier does not exist in between the semiconductor and the metal). Consequently, the contact resistance depends on parameters such as the contact size and geometry, the interface between the metal and the semiconductor, the regions immediately below and above the interface, and the uniformity of current within the contacted area [26]–[28].

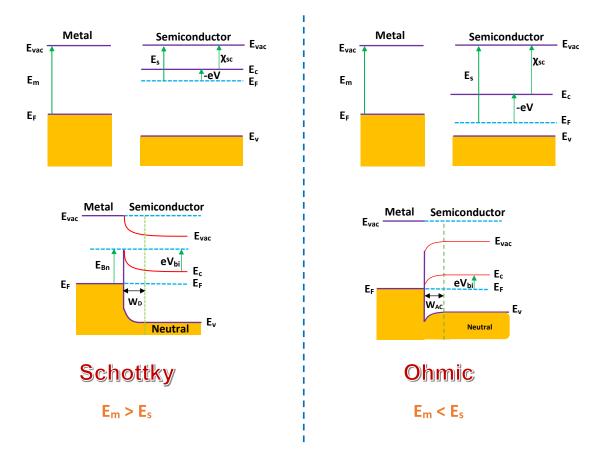

Fabrication of Ohmic contacts relies on several theoretical and experimental concepts. The metal–semiconductor system is presented in *Figure 2. 6*, in two cases: Schottky and Ohmic cases, which depend upon the work functions for the metal and the semiconductor [28].

After the metal and semiconductor are brought into contact the charge carriers flow through the metal–semiconductor contact in either direction without any resistance (in theory). However, in practice, a potential barrier is formed at the interface. Fundamentally, the barrier arises from the difference in the metal and semiconductor work functions. If the work function of the semiconductor is lower than that of the metal and Em > Es, then electrons will flow from the semiconductor to the metal until the Fermi levels in both materials reach equilibrium. The barrier height is then given *Chapter 4* by the band bending at the semiconductor surface *Characterization* by the band bending in the theory of barrier formation:

$$E_{Bn} = E_m - \chi_{sc} \tag{2-35}$$

where  $\chi_{sc}$  is the electron affinity of the semiconductor and  $W_m$  describes the barrier for electron flow from the metal to the semiconductor. For the reverse flow of electrons, from the semiconductor into the metal, the barrier will be

$$eV_{bi} = E_{Bn} - (E_C - E_F)$$

(2-36)

where the quantity  $V_{bi}$  denotes the diffusion potential, and  $E_C$  and  $E_F$  are the lower conduction band and the Fermi level, respectively [26].

Figure 2. 6: Schematic band structure of a metal-semiconductor junction before and after contact for Schottky and Ohmic cases.

$W_D$  and  $W_{AC}$  denote the width of the depletion and accumulation layers, respectively,  $E_{Bn}$  denotes the Schottky barrier height, and  $V_{bi}$  denotes the built-in voltage (here  $V_{bi}$ > 0). Whereas, in the case where the work function of the semiconductor is higher in *Chapter 4* energy than that of the metal, Em < Es electrons will flow from the metal to the semiconductor until the Fermi levels in both materials equilibrate. This results in band bending at the semiconductor surface. This is an Ohmic contact. However, experimentally fabricating Ohmic contacts can be more of an art than a science, and every laboratory has its own tailored recipe using particular metals or alloy systems, deposition methods, and heat treatments. All of these recipes depend on one or more of the following three principles [29]:

- Depending on the Schottky–Mott (2-35), the contact behaves as an Ohmic with negative barrier height if the work function of the metal is less than that of the n-type semiconductor or greater than the work function of the p-type semiconductor, which allow carriers to transfer from the metal to the semiconductor.

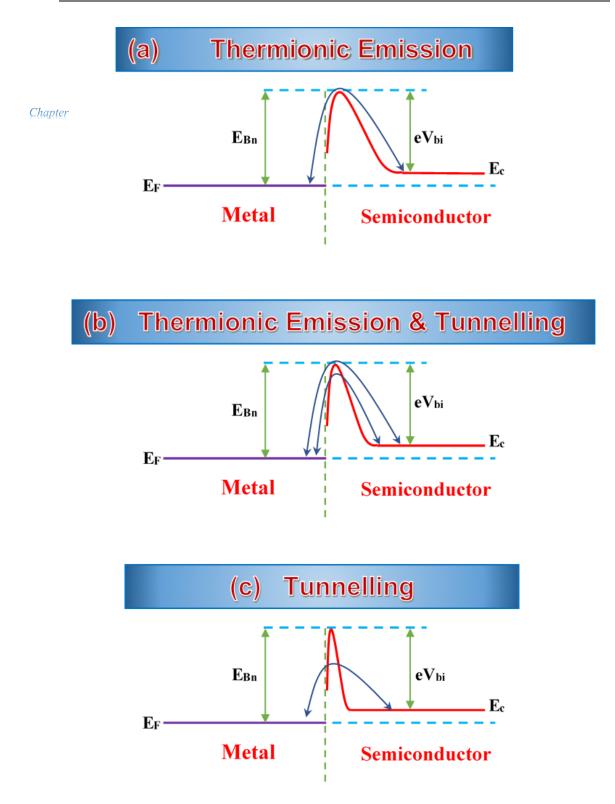

- 2. A very heavy doping with a thin layer into the semiconductor immediately adjacent to the metal to obtain a very thin depletion region that allows electron transportation to take place with very low resistance contact at zero bias (transparent Schottky). *Figure 2.* 7 explains the tunnelling electron transport through a thin barrier and both tunnelling electron and thermionic emission through a medium, whereas it is only thermionic in the case of a wide barrier, depending on the electron energy for both mechanisms.

- 3. Damaging the semiconductor surface by, for instance using ion beam milling technique, which forms crystal defects that act as efficient recombination centres. Consequently, the high density of these centres, means that the recombination in the depilation region will become the dominant conduction mechanism, causing an essential drop of contact resistance.

The current transport in a metal–semiconductor contact system has been studied by Schottky and Mott, who proposed models known as the diffusion theory and the thermionic transport theory [26]. Current transport in metal–semiconductor contact results from majority carriers, in contrast to p-n junctions, where the minority carriers are responsible. The mechanisms of current transport are [29][30]:

1. Emission of electrons from the semiconductor over the top of the barrier into the metal which depends on the barrier height and the thermal energy of an electron which must have a sufficiently high energy to overcome the potential barrier. The barrier *Chapter 4* width should also be significantly less than the mean free path of the electron in the semiconductor;

2. Quantum mechanical tunnelling of electrons from the semiconductor through the barrier into available states in the metal;

3. Recombination of electrons and holes in the depletion region; and

4. Recombination of electrons and holes in the neutral region ("hole injection").

These mechanisms are depicted in *Figure 2*. 7:

Figure 2. 7: Schematic diagram of the conduction mechanisms for different barrier widths: (a) wide barrier, (b) intermediate barrier width, and (c) thin barrier. The case of thermal activation and then subsequent tunnelling is sometimes referred to as a field emission mechanism.

### 2.4.2 Transmission Line Model

The Transmission Line Model (TLM) is one of the most common methods for *Chapte*quantitatively determining<sub>11</sub>the performance of ADM is contacts and assessing the intrinsic sheet resistance of the semiconductor material. This model has been widely used to extract the metal–semiconductor barrier resistance, in a form known as the specific contact resistance  $\rho_c$  (ohm-cm<sup>-2</sup>), which is the most important property of Ohmic contacts [31]. The specific contact resistance is due to the potential barrier at the metal–semiconductor interface [32].

A TLM was originally proposed by Shockley [33] and it offered a convenient method for determining  $\rho_c$  for planar Ohmic contacts and experimentally by measuring the total resistance  $R_T$  between two contacts (of length *d* and width *W* separated by a space *L*). The total resistance can be plotted as a function of *L* and several other useful quantities can be obtained, including contact resistance *Rc*, transmission length of the electrons ( $L_T$ ) and sheet resistance ( $R_{sh}$ ) [34]–[38]. *Figure 2*. 8 shows a schematic diagram of a typical TLM device, depicting the Ohmic contacts on the surface, distances ( $L_1$ ,  $L_2$ ,  $L_3$ ), to a first approximation the contact resistances and the sheet resistances in the material.

TLM measurements can be carried out using a four-point probe technique or the Van der Pauw method. This technique uses two outer probes to pass the current (I) flow under and through the interface and two inner probes to measure the potential difference (V) determining the sheet resistance of the semiconductor.

Figure 2. 8: A Schematic 3D representation of a typical transmission line model (TLM) device configuration showing the contributing contact resistance ( $R_c$ ) and the effect of sheet resistance ( $R_s$ ).

Therefore, this measures the resistance that is given by Ohm's law:

$$R = \frac{V}{I} \tag{2-37}$$

Chapter 4 InSb Heterostructure Surface Characterization where R is the resistance. But this resistance is the total resistance, so  $R_T$  should be included, as in the following equation:

$$R_T = 2R_m + 2R_C + R_{semi} \tag{2-38}$$

where  $R_m$  is the resistance due to the contact metal,  $R_c$  is the metal–semiconductor interface of the single contact and  $R_{semi}$  is the usual semiconductor material resistance. However, in most situations, the resistivity of  $R_m$  is low compared to the others and, therefore, can be neglected. In addition,  $R_{semi}$  in a homogeneous material is given by:

$$R_{semi} = R_{sh} \left(\frac{L}{W}\right) \tag{2-39}$$

where  $R_{sh}$  is the semiconductor sheet resistance, L is the nominal length between contacts and W is the width of the contact, resulting in:

$$R_T = 2R_C + R_{sh}\left(\frac{L}{W}\right) \tag{2-40}$$

### 2.4.2.1 Linear Structure (LTLM)

The simplest and most used configuration of TLM is a linear array of Ohmic contacts, all of which are the same size but placed on the semiconductor surface at a variety of distances (L1 < L2 < L3 < ... < Ln). This configuration is often referred to as the linear transmission line method (LTLM) due to the linear arrangement of the Ohmic contacts. *Figure 2. 8* gives a schematic depiction of the LTLM configuration, which is in general isolated by mesa etching to restrict the current to flow only across the distances *Ln* and to prevent current spreading.

The LTLM configuration can be described by the following equations, when the total resistances  $R_{T1}$  and  $R_{T2}$  correspond to the contact separations  $L_1$  and  $L_2$ , respectively:

$$R_{T1} = 2R_C + R_{sh} \left(\frac{L_1}{W}\right) \tag{2-41}$$

$$R_{T2} = 2R_C + R_{sh} \left(\frac{L_2}{W}\right) \tag{2-42}$$

The contact resistance  $R_c$  can be calculated by measuring the total resistances  $R_{T1}$  and  $Chapter R_{T2}$ , and can be obtained by: interestructure Surface Characterization

$$R_C = \frac{(R_{T2}L_1 - R_{T1}L_2)}{2(L_1 - L_2)} \tag{2-43}$$

By plotting the total resistance as a function of the distance between several pairs of the planar contacts,  $R_c$  is determined by a linear extrapolation of the experimental points to L=0, which is shown in *Figure 2*. 9. Note that the probe metal's resistance is assumed to be negligible in this case of a four-point probe measurement technique. Whereas, the  $R_{sh}$  value can be calculated by the following formula:

$$\frac{\Delta R_T}{\Delta L} = \frac{R_{sh}}{w} \tag{2-44}$$

The transmission length can be extrapolated on the x-axis when  $R_T$  is at zero from the  $R_T$ -L trend.

*Figure 2. 9:* A sketch of a typical plot of total resistance as a function of gap spacing between the planar Ohmic contacts in a TLM measurement.

### 2.5 Scattering

Electron transport in a heterostructure semiconductor in the QW scatters by interaction *Chaptewith* the following excitations uppolar phonons, the doping layer and QW interface roughness. The average of these mechanisms decreases the electron mobility by scattering events. The total electron mobility and the average mobility can be found by using Matthinessen's rule, which can be written as [12][13];

$$\mu = \frac{e < \tau >}{m *}$$

(2-45)

$$\frac{1}{\mu} = \frac{1}{\mu_{ac}} + \frac{1}{\mu_{po}} + \frac{1}{\mu_{bg}} + \frac{1}{\mu_{rii}} + \frac{1}{\mu_{int}}$$

(2-46)

where  $\mu$  is the total mobility, *e* is the electron charge,  $m^*$  is electron effective mass,  $\mu$  is average mobility,  $\mu_{ac}$  is the acoustic mobility,  $\mu_{po}$  is the polar phonon mobility,  $\mu_{bg}$  is the background mobility,  $\mu_{rii}$  is the remote ionised impurities mobility and  $\mu_{int}$  is the interface roughness mobility.

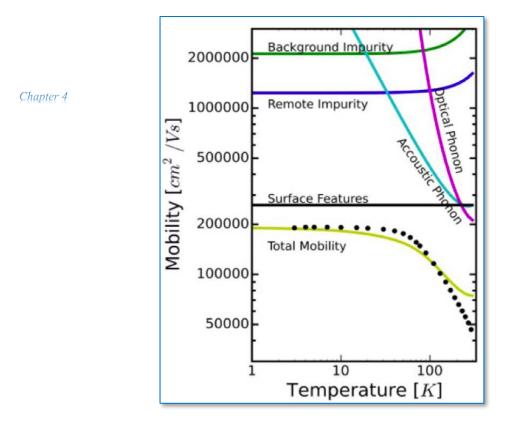

Electrons can be scattered in an *inelastic* or *elastic* process, depending upon the collision transfer kinetic energy between the particles. For inelastic processes, there are acoustic and optical phonon scattering. The former plays a more effective role than the latter as temperature decreases. Therefore, at low temperatures, the optical phonon population in the crystal starts to vanish. Only at temperatures above 50 K do the effects of phonon scattering start to play a role. At temperatures approaching 300 K, the mobility is dominated by polar optical phonon scattering [39]. *Figure 2. 10* shows these types of scattering contributions and electron mobility in InSb QW as a function of temperature.

Whereas, for elastic processes, electrons can be scattered by ionised impurities or scattering from interface roughness. Both of these scattering events can even be effective and dominant at low temperatures, which is found to be independent of temperature in this regime. In addition, crystal dislocations can contain charge centres and thus act as scattering centres [17]. Nevertheless, even with a large spacer between dopant and QW in modulation-doped QWs, a heavy doping will raise the scattering rate [14][40]. The primary reason for the decrease of mobility with increasing doping level is the increasing role of remote ionised impurity scattering. At high-doping

levels, this can become more important at room temperature than phonon scattering [17][41].

The background density of neutral impurities is usually very small when compared with ionised impurities with a thin spacer layer thickness. However, when the thickness of the spacer layer is relatively large, the effect of remote ionised impurities is reduced and the background neutral impurity scattering becomes more important [42]. The net mobility in the AlInSb/InSb system increases with decreasing temperature due to impurities scattering.

Where surface roughness is one of the major scattering mechanisms, the low temperature mobility of 2D electrons in these layers is limited by the surface roughness scattering [43]. The effect of interface roughness on electron transport in semiconducting materials depends on the quality of the interfaces, which limits the electron mobility [44]. Interface roughness scattering has a very strong effect on electron mobility with the quantum width and becomes significant when L < 25nm in InSb QW [14][40][42]. Thus, the interface roughness scattering (IFRS) rate in narrow QW is high. Whereas, in wide QW width, the large mobility values indicate that scattering only comes from background impurities, which is small compared to the effect of (IFRS) in narrower wells. There are also some limitations for relative very wide thicknesses. For instance, nucleation of misfit dislocations in the QW layer due to the partial strain relaxation coming from lattice mismatch between QW and bottom layer. Moreover, the onset of intersub-band scattering is likely to come into play as the wells become wider. Therefore, there is a strong dependence on the well width and the optimum thickness of the QW, which should be checked for a particular material [45][46]. Therefore, roughness at the QW edge interfaces causes the energy of the confined states to change as the width of the confinement changes [39]. Furthermore, due to the narrow bandgap of InSb, the nonparabolicity effect with scattering can be strong.

*Figure 2. 10:* A typical transport model of mobility (lines) using the relaxation time approximation, and measured data (symbols) versus temperature from [47].

Furthermore, structural defects, micro-twins and threading dislocations contribute to carrier scattering and decrease the mobility in the QWs, which is related to the defects density that arises from lattice mismatch with the substrate and growth process [47]–[50]. *Figure 2. 10* explains the electron mobility versus temperature for InSb and the scattering types.

## 2.6 Bibliography

- [1] D. V. Keith Barnham, *Low-Dimensional semiconductor structures Fundamentals and device applications*. Cambridge University Press, 2001.

- [2] B. R. Nag, *Physics of quantum well devices*. 2002.

- [3] M. Fox, *Optical Properties of Solids*, Second Edi. 2010.

- [4] D. K. Ferry and M. G. Stephen, *transport in Nanostructures*. Cambridge: Cambridge University Press, 1997.

- [5] D. J. Griffiths, *Introduction to Quantum Mechanics*, Second Edi. 2005.

- [6] P. Harrison and A. Valavanis, *Quantum Wells, Wires and Dots*, Fourth Edi. John Wiley & Sons, Ltd, 2016.

- Chapte[7] C. Jacoboni, *Theory of Electron Transfort in Semiconductors*. Springer Series, 2010.

- [8] K. Hess, Advanced theory of semiconductor devices. 2000.

- [9] S. Bandyopadhyay, *Physics of Nanostructured Solid State Devices*. Springer New York Dordrecht Heidelberg London, 2012.

- [10] A. Moliton, *Solid-State Physics for Electronics*. 2010.

- [11] G. Iadonisi, G. Cantele, and M. L. Chiofalo, *Introduction to Solid State Physics* and Crystalline Nanostructures. 2014.

- [12] P. J. Price, "Two-Dimensional Electron Transport in Semiconductor Layers. I. Phonon Scattering," *Ann. Phys. (N. Y).*, vol. 133, pp. 217–239, 1981.

- [13] PeterY.Yu, Fundamentals of Semiconductors Physics and Materials Properties, Fourth Edi. springer, 2010.

- [14] H. Sakaki, T. Noda, K. Hirakawa, M. Tanaka, and T. Matsusue, "Interface roughness scattering in GaAs/AlAs quantum wells," *Appl. Phys. Lett.*, vol. 51, no. 7, 1987.

- [15] C. W. J. Beenakker and H. van Houten, "Quantum Transport in Semiconductor Nanostructures," *Solid State Phys. - Adv. Res. Appl.*, vol. 44, no. C, pp. 1–111, 1991.

- [16] D. K. and S. M. G. Ferry, *Transport in Nanostructures*. Cambridge University Press, 1997.

- [17] M. Grundmann, *The Physics of Semiconductors An Introduction Including Nanophysics and Applications*, Second Edi. Springer, 2010.

- [18] D. K. Ferry, S. M. Goodnick, and J. Bird, *Transport in Nanostructures*, Second Edi. Cambridge University Press, 2009.

- [19] Y. Hirayama, T. Saku, S. Tarucha, and Y. Horikoshi, "Ballistic electron transport in macroscopic four-terminal square structures with high mobility," *Appl. Phys. Lett.*, vol. 58, no. 23, pp. 2672–2674, 1991.

- [20] B. J. Van Wees *et al.*, "Quantized conductance of point contacts in a twodimensional electron gas," *Phys. Rev. Lett.*, vol. 60, no. 9, pp. 848–850, 1988.

- [21] D. A. Wharam *et al.*, "One-dimensional transport and the quantisation of the ballistic resistance," *J. Phys. C Solid State Phys.*, vol. 21, no. 8, pp. L209–L214, 1988.

- [22] Y. V Nazarov and Y. M. Blanter, *Quantum Transport. Introduction to Nanoscience*. Cambridge University Press, 2009.

- [23] R. Landauer, "Spatial Variation of Currents and Fields Due to Localized Scatterers in Metallic Conduction," *IBM J. Res. Dev.*, vol. 1, no. 3, pp. 223–

231, 1957.

[24] M. Bttiker, Y. Imry, R. Landauer, and S. Pinhas, "Generalized many-channel conductance formula with application to small rings," *Phys. Rev. B*, vol. 31, no. 10, pp. 6207–6215, 1985.

*er 4* InSb Heterostructure Surface Characterization

Chapter 4

- [25] R. F. Pierret, "Advanced Semiconductor Fundamentals," *Book*, vol. 121, no. 7, p. 221, 1987.

- [26] S. S. Cohen and S. G. Gildenblat, VLSI Electronics Microstructure Science Metal-Semiconductor Contacts and Devices, Volume 13. ACADEMIC PRESS, INC, 1986.

- [27] S. M. Sze and Kwok K. Ng, *Physics of Semiconductor Devices*, Third Edit. JOHN WILEY & SONS, 2007.

- [28] L. N. H. Badih El-Kareh, *Silicon Analog Components*. Springer New York Heidelberg Dordrecht London, 2015.

- [29] Rhoderick, E H and R. H. Williams, *Metal-Semiconductor Contacts*, Second Edi. OXFORD University Press, 1988.

- [30] S. Tiwari, *Compound Semiconductor Device Physics*. ACADEMIC PRESS, Harcourt Brace Jovanovich, 1992.