# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/132374/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Zhao, Xibei, Chen, Lixu, Li, Gen, Xu, Jianzhong and Yuan, Jinsha 2022. Coordination method for DC fault current suppression and clearance in DC grids. CSEE Journal of Power and Energy Systems 8 (5), pp. 1438-1447. 10.17775/CSEEJPES.2019.03160

Publishers page: http://dx.doi.org/10.17775/CSEEJPES.2019.03160

# Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# Coordination Method for DC Fault Current Suppression and Clearance in DC Grids

Xibei zhao, Lixu Chen, Gen Li, Jianzhong Xu, Jinsha Yuan

Abstract—The modular multilevel converter (MMC) based DC grid is considered as a future solution for bulk renewable energy integration and transmission. However, the high probability of DC faults and their rapid propagation speed are the main challenges of the development of DC grids. Existing research mainly focuses on the DC fault clearance methods, while the fault current suppression methods are still under researched. Additionally, the coordination method of fault current suppression and clearance needs to be optimized. In this paper, the technical characteristics of the current suppression methods are studied, based on which the coordinated methods of fault current suppression and clearance are proposed. At last, a cost comparison of these methods is presented. The research results show that the proposed strategies can reduce the cost of the protection equipment.

Index Terms—DC fault, DC grid, fault current limiter (FCL); DC circuit breaker.

#### I. INTRODUCTION

HIGH voltage direct-current (HVDC) system based on modular multilevel converters (MMCs) is a potential solution for future renewable energy integration and DC grid interconnection [1-3]. DC grids based on power electronics devices feature their controllability and flexibility. However, semiconductor devices are easily damaged, especially when they suffer large DC fault currents. Therefore, fast and reliable DC fault clearance methods are crucial for the widespread application of DC grids.

DC circuit breakers (DCCBs) have been recognized as essential equipment protecting DC grids from DC faults [4-5]. However, installing numerous DCCBs in a DC grid with multiple transmission lines may lead to an extensive capital cost. To reduce the investment, a lot of research focuses on the low-cost DCCB topologies using fewer semiconductors [6]. Moreover, the electric stress on DCCBs may be extremely high during the current interrupting process, which is also a challenge for the deployment of DCCBs [7-8]. Although some DCCBs have been installed in real projects [9-10], more work

can be carried out to mature their reliability.

The MMC with fault current clearing capability is an alternative way to deal with DC faults [11] in which steady-state operation and fault clearance are incorporated. For instance, clamping sub-modules (SMs) [12] or auxiliary branches [13] are used in some of these converters to create zero voltages on DC buses. Then, the faulty line can be isolated by the mechanical switches installed along with transmission lines. As one converter may have multiple outwards DC lines, it's blocking can handle the fault in any of these lines. Therefore, the MMC based protection may be optional for MTDC grids with complex DC link interconnections [14]. However, such protection schemes may lead to temporary power cuts of the MMCs, and therefore, may threat the stable integration of renewable energy sources. Thus, more attention should be paid to this area.

Different from the DC fault clearance methods, research on the DC fault current suppression methods is limited. DC reactors have been widely deployed in DC systems to limit the rapid increase of fault currents. However, their applications may result in system instability under normal conditions [15]. MMCs can act to prevent the rapid increase of the fault current by reducing their DC output voltage. However, this approach may also cause the power outage problem similar to the converter based fault clearing methods. Fault current limiters (FCLs), which can suppress fault currents by inserting additional resistors or reactors [16], maybe a potential fault protection equipment for DC grids. A solid self-adaptive FCL based on an external DC voltage source has been developed in [17]. However, the external DC source may limit its flexible applications. In [18], a thyristor-based hybrid FCL which inserts a reactor during the current commutation process has been proposed, but the reliability of the FCL is questionable. Therefore, more research is required concerning FCLs.

The coordination of the fault current suppression and clearance schemes is another perspective in research, which mainly focuses on the fault current reduction and helps the DCCB operation. By triggering all MMC SMs, the converter can generate an active inner short-circuit. In this case, the fault current cannot feed from the AC side to the DC side [19]. However, this method may threaten the safety of the converters and their connected AC systems due to the created short-circuit. The assembled FCL with DCCB proposed in [20] can realize both current suppression and clearance process. The DC reactor is bypassed to reduce the energy dissipation in the DCCB. The research results show that a proper coordination method can achieve a fast and cheap solution for DC fault protection, but more optional methods are still needed.

In this paper, two novel coordination methods are proposed for DC fault current suppression and clearance. The soft current

This paragraph of the first footnote will contain the date on which you submitted your paper for review. This work was supported by National Key R&D Program 2018YFB0904600 and National Natural Science Foundation of China under grant 51777072.

X. Zhao, L. Chen, J. Xu (Corresponding author, E-mail: xujianzhong@ncepu.edu.cn), J. Yuan are with the State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources, North China Electric Power University, Beijing China.

G. Li is with the School of Engineering, Cardiff University, Cardiff, UK.

suppression (SCS) control is suitable for MMCs, which can self-adapt the fault current suppression and recovery. In this scheme, the remote converters will also participate in the current suppression. The coordination method of FCL and DCCB is also discussed, in which the FCL SMs are inserted sequentially before the DCCB is blocked. The coordination method for backup protection is discussed as well. Finally, economic discussion is presented.

Following Section I, the technical characteristics of the MMC, FCL, and DCCB during the fault suppression and clearance are analyzed in Section II. The coordination methods based on different devices are described in Section III followed by a detailed comparison in Section IV. Economy evaluation of different coordination methods is given in Section V. Finally, conclusions are presented in Section VI.

# II. TECHNICAL CHARACTERISTICS OF FAULT CURRENT SUPPRESSION AND CLEARANCE EQUIPMENT

MMC, FCL and DCCB are three building blocks for a DC grid. Their controllability and characteristics of current suppression are discussed as follows.

# A. Fault Current Suppression Method of MMC

MMC is designed for power conversion and exhibits limited fault current tolerant operation capability. As the MMC performs as a current source during a fault, preventing SMs from discharging is a potential approach to reduce fault currents and therefore, protect the DC grid.

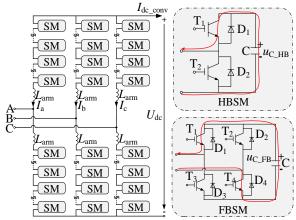

The topology of an MMC is illustrated in Fig. 1. Each arm consists of half-bridge SMs (HBSMs) or full-bridge SMs (FBSMs) or mixed HBSMs and FBSMs. The SM capacitors will start to discharge and the fault current will flow through  $T_1$  of HBSMs or  $T_1$  and  $T_4$  of FBSMs when a DC fault occurs.

Fig. 1 Schematic diagram of an MMC.

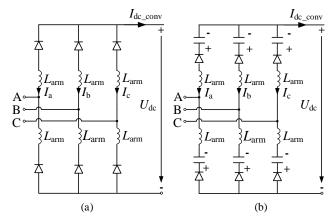

Blocking the converter is an effective way to interrupt the discharge path of the SM capacitor to prevent the fault current increasing. For HB-MMC, the converter becomes a three-phase diode rectifier. AC side currents will feed into the fault point through the uncontrollable diode bridge, as shown in Fig. 2 (a). For FB-MMC, the FBSMs will only be charged after blocking. Thus, the fault current will diminish fast until the sum voltage of the FBSMs equals to the peak AC line-to-line voltage.

Fig. 2. Equivalent circuits of blocked (a) HB-MMC; (b) FB-MMC.

For a hybrid MMC, which consists of mixed HBSMs and FBSMs, the converter's controllability is enhanced thanks to the deployment of FBSMs. The fault-ride-through (FRT) control proposed in [11] can interrupt the fault current by controlling the converter output voltage to zero. However, it can only be used in hybrid MMCs. In this paper, an SCS control which suits for both HB-MMC or hybrid MMC is proposed without involving more investment.

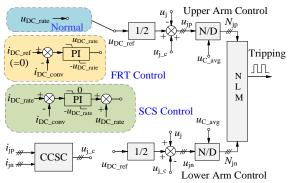

The MMC arm controllers are shown in Fig. 3.  $u_{DC\_ref}$  is the voltage reference for the sum voltage of upper and lower arms.  $u_j$  is the AC voltage of phase j, which is obtained from the AC vector control.  $u_{j\_c}$  is the compensation voltage generated from the circulating current suppression controller (CCSC) [22],  $u_{C\_avg}$  is the average capacitor voltage,  $u_{jp}$  and  $u_{jn}$  are the modulation voltages of each arm.  $N_{jp}$  and  $N_{jn}$  are the calculated numbers of inserted SMs in each arm, respectively. The nearest level modulation (NLM) [23] is used for IGBT switching.

The  $u_{\rm DC}$  ref can be obtained from three channels:

- 1) Normal state rating voltage: During normal operation, a constant value of  $u_{DC\_rate}$  will be the input of the arm controller which will regulate the sum voltage of the upper and lower arms to the rated DC voltage.

- 2) FRT control: The FRT control can be applied to the hybrid MMC. In case of a DC fault, the active power control of the hybrid MMC will switch to regulate its average capacitor voltage, and the FRT control is used to control the DC current to follow the zero-current reference. In this way, the converter active power is controlled by the FRT channel.

- 3) The proposed SCS control: The SCS control can be applied on HB-MMC or FB-MMC, which can limit the fault current by temporally reducing the inserted number of SMs. The SCS control is implemented by a feedforward control on the normal rated DC voltage. The current feedforward control is used to control the real-time converter DC current  $i_{DC\_conv}$  does not exceed the rated DC current  $i_{DC\_rate}$ . If  $i_{DC\_conv}$  is higher than  $i_{DC\_rate}$ , the feedforward control will output a negative value to reduce the DC voltage.

Fig. 3 MMC arm controller.

To ensure the current feedforward control will not disturb the system under normal state,  $i_{DC\_rate}$  is set as the rated DC current under the maximum power.  $i_{DC\_conv}$  is the measured current. Thus,  $i_{DC\_conv}$  will always be lower than or equal to  $i_{DC\_rate}$ . Then the current feedforward control will not disturb  $u_{DC\_rate}$  under normal state. If there is a continuous severe fault, the PI controller will gradually reach the lower limit of  $-u_{DC\_rate}$ , then  $u_{DC\_ref}$  will equal to zero. The  $u_{jp}$  will still have a small value due to the difference between  $u_j$  and  $u_{j\_c}$ . However, this state is very close to the blocking scheme.

In contrast to the blocking or the FRT method, the SCS method doesn't base on the fault detection signal. It is a self-adapting current limiting method. The blocking or the FRT method both will decrease the DC voltage suddenly. However, the SCS control will reduce the DC voltage gradually after detecting the fault. Moreover, it will recover automatically when the overcurrent disappears. The blocking or FRT control both will lose the active power transmission capability completely. However, the SCS only reduces the converter power transmission, which will cause less disturbance to the AC system. Moreover, this method can be applied to multiple converters to limit the fault current, so it is also suitable for a coordinated fault current suppression.

# B. Fault Current Suppression Method of FCL

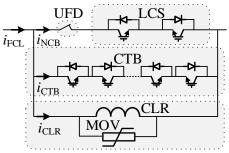

The main function of an FCL is to suppress the fast increasing of the fault current. Some existing research focuses on superconductor based FCLs (SFCLs). However, the SFCL may have limited controllability due to lack of semiconductor switches. A hybrid FCL can achieve a flexible controllability during a fault. Therefore, a coordination method with DCCBs is worth studying.

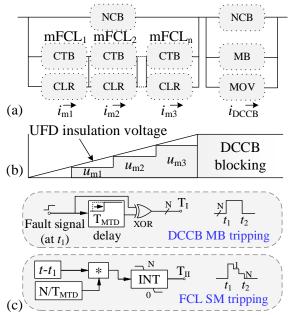

As shown in Fig. 4, the hybrid FCL consists of a normal current branch (NCB), a current transfer branch (CTB), and a current limiting reactor (CLR). The NCB consists of a load commutation switch (LCS) and an ultra-fast disconnector (UFD), which is similar to the hybrid DCCB in [24]. Under normal conditions, the load current flows through the NCB and will be transferred to the CTB once the FCL is triggered. IGBTs of the CTB will be turned off when the UFD operates successfully. Then, the fault current is forced to the CLR. The MOV is used to prevent the voltage spike on the CLR.

Fig. 4 Diagram of the FCL.

The FCL can be implemented in different forms. However, the very basic concept is to raise the inductance in the fault circuit. Compared with the resistance type FCL, the inductance type FCL does not require continuous energy dissipation on its resistance, which benefits for its lightweight design. Therefore, the inductance type FCL is usually chosen. Compared with passive CLRs, the active FCL can insert additional inductor to the fault circuit. It may be an option to assist the passive CLR and DCCB in the future.

# C. Fault Current Suppression Method of DCCB

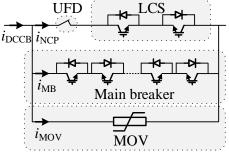

The basic function of DCCB is to cut off DC fault current and isolate the faulty line. In this way, the healthy part of the DC grid can keep running. The structure of a hybrid DCCB is shown in Fig. 5. It consists of an NCB, a main breaker (MB) and an energy dissipation branch which only employs MOVs. The basic principle of the DCCB has been discussed in [24]. The fault current is forced to be dissipated in the MOVs. Then the faulted line can be isolated.

Fig. 5 Diagram of the hybrid DCCB.

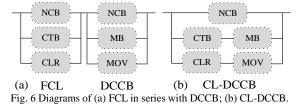

A current-limiting DCCB (CL-DCCB) benefits from the low voltage and current stress on the DCCB. However, the structure of the CL-DCCB is more like an FCL in series with a DCCB. As shown in Fig. 6, the FCL and DCCB can be installed in series or they can share one NCB to build a CL-DCCB.

The FCL and DCCB in series will involve more cost on the NCB, but it can provide some benefits regarding easy

manufacturing and installation, while the CL-DCCB integrates the FCL and DCCB to achieve a lower cost and less power losses. As the CL-DCCB shares one NCB, the failure of NCB will affect two parts of the CL-DCCB. The series FCL and DCCB have their corresponding NCB. Therefore, if one NCB fails, the other one will not be affected, which can be used in backup protection.

Moreover, if their difference is negligible in the real project, the effects of the two configurations can be the same in the simulation. In the rest of this paper, the discussion is based on that FCL and DCCB are in series for simplicity.

# III. COORDINATION METHOD FOR FAULT CURRENT SUPPRESSION AND CLEARANCE

Since a DC fault can severely strike power electronics devices, a fault clearance method must be able to handle tough situations. Then the cost of certain equipment may be significantly increased. A proper coordination design for fault current suppression and clearance can reduce the demand for single equipment and the fault stress can be shared.

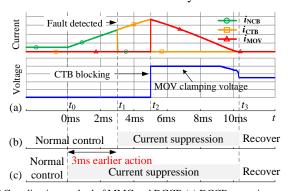

# A. Coordination Method of MMC and DCCB

As the capacitor is a fault current source, a capacitor fault current suppression method will significantly reduce the demand for DCCBs. The converter-based fault current suppression method has a detection delay when a fault occurs. The converter will act synchronously with the hybrid DCCB. As shown in Fig. 7 (a), the classical operation process of a hybrid DCCB involves a 2 ms delay between fault detection and CTB blocking. The converter will have 2 ms to limit the fault current before the DCCB is blocked. Then the fault will be isolated by the DCCB. As shown in Fig. 7 (b), the converter will switch to the fault current suppression mode during fault detection and the fault will be cleared by the DCCB.

Fig. 7 Coordination method of MMC and DCCB (a) DCCB operation sequence; (b) Converter current suppression based on fault detection; (c) SCS process.

As the fault current increases, the SCS control will be automatically activated. Thus, the detection time delay is unnecessary. As shown in Fig. 7 (c), the SCS may have 5 ms before the DCCB blocking. Moreover, the SCS method will enable a lower initial current in the MB, which will reduce the MB overcurrent.

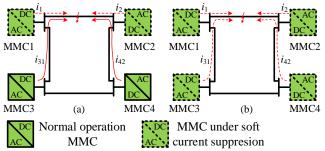

In a DC gird, the SCS may coordinate among converters. Although remote converters may only contribute a small part of the DC fault current, the current suppression achieved by these converters still helps lower the fault current. As shown in Fig. 8

(a), the near fault converters will reduce the DC output voltage during the fault. As a result, the main portion  $(i_1 \& i_2)$  of the fault current is reduced. However, the capacitor discharging of the remote converters are still growing. If SCS is applied to all converters, the reduction of  $i_{31} \& i_{42}$  can also contribute to a smaller fault current, as shown in Fig. 8 (b).

Fig. 8 Schematic diagrams of (a) single converter current suppression; (b) coordination converter current suppression.

#### B. Coordination Method of FCL and DCCB

The FCL and DCCB operation depends on the fault signal detection before being triggered. To ensure that the FCL operates earlier than the DCCB, the FCL is separated into N (=3) SMs and triggered consequently during the UFD operation, see Fig. 9(a). The NCBs within the FCL and DCCB are triggered at the same time. However, the DCCB still needs a 2 ms delay before the MB is blocked. The UFD separation can be seen as a linear process and therefore, the voltage withstand over the UFD will be gradually established. Therefore, the FCL SMs can be sequentially triggered during this time [25-28]. The voltage across the FCL must be lower than the isolation voltage of the UFD. When the UFD is fully separated, the DCCB will act to isolate the fault, see Fig. 9(b).

Fig. 9 Diagrams of (a) modular FCL in series with the DCCB; (b) step tripping FCL coordination with the DCCB; (c) control diagram for DCCB and FCL.

The control diagram for DCCB MB and FCL SMs are provided in Fig. 9(c):

- 1) DCCB: All MB IGBTs share the same blocking signal  $T_{\rm I}$ . They will be conducted after receiving the fault signal at  $t_{\rm I}$ , and will be blocked when the UFD is successfully separated after the mechanical time delay ( $T_{\rm MTD}$ ) at  $t_{\rm 2}$ . This is achieved by XORing the step fault signal and its delay.

- 2) FCL: T<sub>II</sub> is the number of inserted FCL SMs, which is calculated by evaluating the contact insulation voltage of the UFD, then round down through the limiter. In this mode, the FCL SMs are blocked sequentially during the UFD separation process and fully inserted after t<sub>2</sub>.

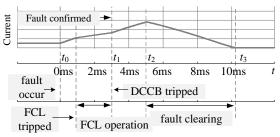

With the assistance of the FCL, the peak fault current is reduced and the demand for DCCB is also decreased. Apart from the above method, there is one more potential method for FCL and DCCB coordination. Since the DCCB operation sequence cannot be stopped, the tripping signal usually waits for a certain confirmation of the DC fault for approximately 3 ms in real applications. The DC grid can trip the FCL with a small disturbance signal and also trip the DCCB with a certain fault signal. Thus, the detection time delay of the FCL is reduced and a better current suppression performance can be achieved. As shown in Fig. 10, the system will undergo a current suppression and clearance process, where the DCCB tripping signal is applied only after the fault is confirmed (3 ms). The FCL tripping signal is applied based on a small disturbance signal (1 ms). The fault current will keep rising between the period of the insertion of FCL and DCCB blocking (3-5 ms).

Fig. 10 Time sequence of tripping the FCL in advance.

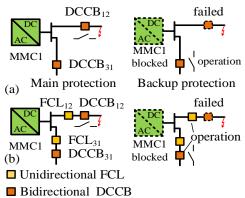

#### C. Direction Configuration of FCL and DCCB

The DCCB is usually designed as bidirectional equipment. The positive direction is used for the main protection of its transmission lines, while the backup protection is realized by the reverse direction of the near DCCBs which installed at the same station, see Fig. 11(a). Unidirectional DCCBs at the remote end of the adjacent lines can also be used in the backup protection, but the far electrical distance between the DCCB and the fault point may limit the speed and sensitivity of the proposed scheme. As the near backup protection can receive the failure signal of the faulty line DCCB in time [29]-[30], the coordination backup protection in this paper is also designed as a near protection, as shown in Fig. 11(b).

Fig. 11 Main and backup protection principles for (a) DCCB; (b) FCL in series with DCCB.

Two reasons determine that a unidirectional FCL is adequate for the current suppression: 1) The fault current mainly comes from the near converters and only a small part comes from the remote converters. Thus, the required capacity of DCCB backup protection is much smaller than that of the main protection. 2) According to the N-1 principle, the FCL on the faulty line will continue its operation. Therefore, the fault current is suppressed and the backup protection can operate successfully, see Fig. 11(b).

In this way, the direction configuration of the FCL and DCCB is based on bidirectional DCCB and unidirectional FCL. Thus, the investment can be minimized without sacrificing the capability of current suppression and clearance.

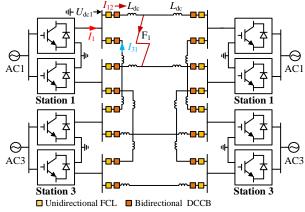

# IV. CASE STUDY

The proposed current suppression methods are validated in the Zhangbei four-terminal DC grid, as shown in Fig. 12. The converter control modes and system parameters are listed in the Appendix. Each line of the DC grid employs an FCL in series with a DCCB. A pole-to-pole metal fault  $F_1$  is set at the line terminal. To verify the performance of the proposed schemes under the most severe condition, a 3 ms fault detection delay is used based on the real project design [31], which can be shorter in real operation.

Fig. 12. Four-terminal DC grid.

#### A. Fault Current Suppression of MMC

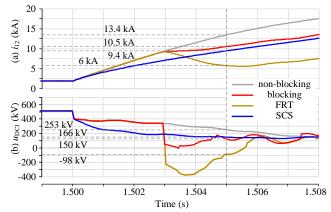

The MMC fault current suppression is verified under different methods. As shown in Fig. 13, the MMC is blocked or

the FRT control acts 3 ms later after the fault. The SCS control will be activated shortly after the fault. The DC bus voltage  $u_{\rm DC1}$  is also shown in Fig. 13.

Fig. 13 Comparison of converter current suppression methods.

The fault occurs at t = 1.505 s, the non-blocking discharging current of the DC grid reaches 13.4 kA in 5 ms. If the converter is blocked at t = 1.503 s, the fault current becomes 10.5 kA at t = 1.505 s. The hybrid converter using the FRT control can regulate  $i_1$  to zero. Therefore, the fault current at is 6 kA at t =1.505 s, which is much less than other cases. However, hybrid MMC's higher capital cost compared to HB-MMC is its demerit. As the MMC controls its DC current via the DC voltage,  $u_{DC1}$  has a significant influence on the DC current. The DC voltages are also marked in Fig. 13(b). The DC voltages of fault detection based methods exhibit a sudden drop when the current suppression methods are activated. However, the SCS control doesn't disturb the converter suddenly and the current is still effectively suppressed. The FRT method can generate negative voltage to quickly suppress the fault current. However, others can only limit the DC current by reducing the DC voltage. The DC voltage under the SCS control is 166 kV at t = 1.505 s, which is slightly higher than the blocking method. It means that the SCS control can achieve better performance without more cost on the FRT method.

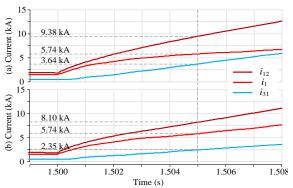

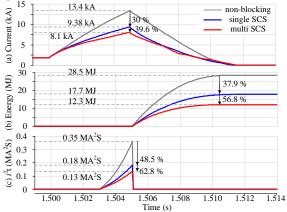

The coordination SCS control is also verified in the test system. The SCS control is applied to all terminals. Current of the single converter SCS method is also shown in Fig. 14 (a) for comparison. As  $i_1$  is limited by the SCS control of station 1, the fault current from remote stations increase due to the reduced voltage  $u_{\rm DC1}$ . The fault currents in the near and remote fault stations will reach the same level at  $t=1.508~\rm s$ . The coordination SCS control is able to suppress the overcurrent in every station, as shown in Fig. 14(b). The fault current  $i_{31}$  from the remote station is also reduced and the total fault current  $i_{12}$  reduces to 8.1 kA.

Fig. 14 Comparison of (a) single terminal SCS and (b) multi-terminal SCS.

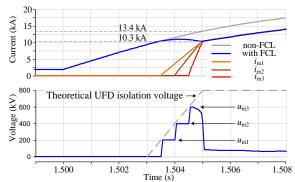

# B. Fault Current Suppression of FCL

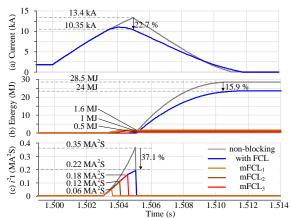

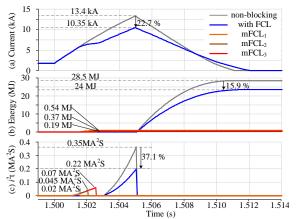

The fault current suppression using the FCL is verified based on the method illustrated in Fig. 9. The FCL consists of three SMs. Each MOV has a protection voltage of 200 kV. The three SMs are triggered every 0.5 ms once the fault is detected. To make sure the FCL is completely inserted within 5 ms, the inductance of the three SMs has been set as 30, 20 and 10 mH. The current and voltage of the FCL are shown in Fig. 15.

Fig. 15 Fault current suppression capability of the FCL.

Compared with the non-FCL scheme, the FCL can limit the fault current to 10.35 kA in 5 ms, which is 23 % lower than the free discharging current. All FCL SMs can be completely inserted within 5 ms and the voltage across the FCL doesn't exceed the safe margin. Compared with the SCS control, the effectiveness of the FCL is slightly lower due to the limited operation time. However, since it is a strict N-1 method, only the faulty line is influenced during this process.

# C. Coordination Control of MMC and DCCB

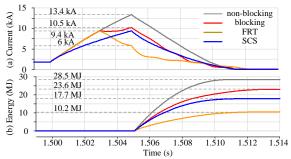

The fault interruption performance under different MMC current suppression methods is shown in Fig. 16, including the energy dissipation of DCCBs. The fault current increasing process is the same as shown in Fig. 13.

The methods of the blocking, SCS and FRT control all contribute to assist the fault interruption of DCCBs. The FRT control has the lowest dissipation energy of 10.2 MJ followed by the SCS control which has a lower converter cost.

Fig. 16 Fault interruption performance under different MMC control.

The SCS control is also compared with the multi converter SCS control with the consideration of three factors: 1) fault current level; 2) MOV dissipation energy; 3)  $i^2t$  of DCCB IGBT. As shown in Fig. 17, the coordination method of the SCS can largely reduce the demand of DCCBs.

Fig. 17 Coordination of MMC SCS and DCCB.

As shown in Fig. 17, the dissipated energy and  $i^2t$  of non-blocking MMC is 28.5 MJ and 0.35 MA<sup>2</sup>S. If SCS control is applied to a single converter, the energy dissipation on the MOV is reduced to 17.7 MJ with a reduced  $i^2t$  of 0.18 MA<sup>2</sup>S. The performance is further improved to 16 MJ and 0.13 MA<sup>2</sup>S in case of employing the SCS control to all stations.

Comparing to the results in Fig. 16, the energy dissipation and  $i^2t$  reduce more than the fault current reduction. It is because both of them are determined by  $i^2$  wherein a small reduction of the fault current can largely reduce the burden of DCCBs and therefore, reduce the capital cost.

# D. Coordination Control of FCL and DCCB

With the assistance of the FCL, the requirement of DCCBs can be reduced. At the same time, the increased investment on the FCL should be considered. The current, MOV energy and  $i^2t$  of the FCL and DCCB are shown in Fig. 18. The MOV energy of the DCCB is reduced to 24 MJ with the help of FCL, while the three modules of the FCL absorb 1.6, 1 and 0.5 MJ, respectively. The  $i^2t$  of the DCCB IGBT is 0.22 MA<sup>2</sup>S, while FCL's  $i^2t$  is 0.18, 0.12 and 0.6 MA<sup>2</sup>S, respectively.

Compared with the SCS control, the effect of the FCL is limited due to the limited action time of the FCL. The SCS can achieve a better current suppression within 5 ms. However, the converter operation is affected. The FCL method is a strict N-1 method, which helps the operation of DCCBs. The burden of DCCBs is further reduced in the case of using the pre-activating

Fig. 18 FCL coordination with DCCB.

method of the FCL. As shown in Fig. 18, the FCL will limit the fault current to 10.35 kA within 5 ms, which is similar to the case shown in Fig. 17. However, the thermal effect and energy dissipation of the FCL is reduced significantly.

Fig. 19 FCL coordination with DCCB in advance

#### V. INVESTMENT AND PERFORMANCE ANALYSIS

The IGBT and MOV occupy the main cost a DCCB. Therefore, the cost calculation is based on the demand of IGBT and MOV under different scenarios.

# A. DCCB Requirement of MMC Current Suppression Method

Assuming all IGBTs have the same voltage level, then the IGBT cost is proportional to the current capacity. Therefore, it is assumed that the reduction of  $i^2t$  contributes to the proportional reduction of the cost. In Table I, the four fault current suppression methods are compared with the non-blocking method.

TABLE I DCCB REQUIREMEN

| DCCB REQUIREMENT |                       |         |           |         |

|------------------|-----------------------|---------|-----------|---------|

| Items            | IGBT i <sup>2</sup> t | Reduced | MOV       | Reduced |

|                  | /MA <sup>2</sup> S    | by      | energy/MJ | by      |

| Non-blocking     | 0.35                  | 0 %     | 28.5      | 0 %     |

| blocking         | 0.22                  | 37 %    | 25.8      | 10 %    |

| FRT              | 0.072                 | 79 %    | 10.1      | 64 %    |

| Single SCS       | 0.17                  | 51 %    | 17.7      | 38 %    |

| Multi-SCS        | 0.13                  | 62 %    | 12.3      | 56 %    |

It is observed from Table I that the SCS control methods are optimal solutions to reduce the DCCB requirement without using FBSMs. The single SCS control can reduce the

requirement of IGBT by 51 % and 38 % of the MOV. The multi-SCS control can reduce 62% and 56 % of the requirement of the IGBT and MOV. Although the FRT control can achieve the largest reduction of the requirement of DCCBs, it sacrifices the high converter capital cost. The hybrid converter will further increase the cost. Thus, SCS control is much more appropriated.

# B. Requirement Calculation of FCL with DCCB

Compared with the converter current suppression method, the FCL may have a limited effect due to its limited operation time. However, this method is still worth studying, because it only isolates the faulty line without expanding the faulty area. Different from the MMC current suppression method, the FCL can reduce the cost of DCCB. However, its own cost should be calculated as well. The IGBT thermal effect requirement and the MOV dissipation energy are calculated in Table II.

TABLE II FCL AND DCCB REQUIREMENT

|                     | 1 CE AND DCCD REQUIREMENT |         |                       |         |

|---------------------|---------------------------|---------|-----------------------|---------|

| Items               | IGBT i <sup>2</sup> t     | Reduced | MOV energy            | Reduced |

|                     | $/MA^2S$                  | by      | /MJ                   | by      |

| Non-                | 0.35                      | 0 %     | 28.5                  | 0 %     |

| blocking            |                           |         |                       |         |

|                     | FCL <sub>1</sub> 0.06     | -       | FCL <sub>1</sub> 0.5  | 5 %     |

| DCCB<br>with FCL    | FCL <sub>2</sub> 0.12     | -       | FCL <sub>2</sub> 1    |         |

|                     | FCL <sub>3</sub> 0.18     | -       | FCL <sub>3</sub> 1.6  |         |

|                     | DCCB 0.22                 | 37 %    | DCCB 24               |         |

| with FCL in advance | FCL <sub>1</sub> 0.02     | -       | FCL <sub>1</sub> 0.19 | 12 %    |

|                     | FCL <sub>2</sub> 0.045    | -       | FCL <sub>2</sub> 0.37 |         |

|                     | FCL <sub>3</sub> 0.07     | -       | FCL <sub>3</sub> 0.54 |         |

|                     | DCCB 0.22                 | 37 %    | DCCB 24               |         |

As seen from Table II that the FCL can assist the DCCB to reduce the IGBT requirement by 37 %. A slight requirement reduction of the MOV is also achieved. This is similar to the blocking scenario. The MOV dissipation energy can be simply added in the calculation. However, the requirements for IGBTs should be calculated based on its voltage level. In this paper, the voltage of each FCL module is 200 kV, while the DCCB is an 800 kV bi-directional module. The IGBT cost is calculated by considering the thermal effect requirement and the voltage level (see Table III).

TABLE III IGBT REQUIREMENT

| IGBT REQUIREMENT               |                        |         |                        |            |

|--------------------------------|------------------------|---------|------------------------|------------|

| Items                          | IGBT i <sup>2</sup> t  | Voltage | IGBT cost              | Reduced by |

|                                | /MA <sup>2</sup> S     | /kV     | /MA <sup>2</sup> S• kV |            |

| Non-                           | 0.35                   | 1600    | 560                    | 0 %        |

| blocking                       |                        |         |                        |            |

|                                | FCL <sub>1</sub> 0.06  | 200     | 424                    | 24 %       |

| DCCB                           | FCL <sub>2</sub> 0.12  | 200     |                        |            |

| with FCL                       | FCL <sub>3</sub> 0.18  | 200     |                        |            |

|                                | DCCB 0.22              | 1600    |                        |            |

|                                | FCL <sub>1</sub> 0.02  | 200     | 379                    | 32 %       |

| DCCB<br>with FCL<br>in advance | FCL <sub>2</sub> 0.045 | 200     |                        |            |

|                                | FCL <sub>3</sub> 0.07  | 200     |                        |            |

|                                | DCCB 0.22              | 1600    |                        |            |

Thus, the FCL can help the DCCB to reduce the IGBT cost by 24 %. 32 % of the IGBT cost can be reduced if the FCL is inserted in advance.

Compared with the converter current suppression method, the effect of the FCL is between the converter blocking and non-blocking method, which indicates that the converter method is the most effective way to limit the fault current. Although the FCL fault current suppression method is not as effective as the converter method, it strictly follows the N-1 principle and it is still cheaper than only using DCCB.

# VI. CONCLUSIONS

DC fault current suppression methods for protecting MTDC grids are discussed in this paper. The fault current suppression effect of the converter and FCL is analyzed and the coordination method for fault current suppression with DCCB is proposed:

- 1) The proposed converter SCS method is suitable for multi-SCS control without relying on communication. Compared with other methods, the SCS has the best fault current suppression effect without increasing the converter investment. Moreover, its fault current suppression process is much smoother than others.

- 2) An FCL topology is proposed. The fault current is suppressed by inserting an additional CLR. The FCL working principle and its coordination method with DCCBs are discussed. The FCL can sequentially insert the CLR during the operation process of the UFD.

- 3) The cost evaluation shows that both the converter fault current suppression methods and FCL can reduce the capital cost. The converter fault current suppression methods have a better current suppression effect because they can directly reduce the capacitor discharging. The FCL is also able to limit the fault current, but its additional cost may partly reduce the benefit of using DCCBs.

It can be concluded through the comparison of the two fault current suppression methods that the converter SCS method exhibits a better current suppression effect and the cost of the DCCB is significantly reduced. The effectiveness of the FCL in the fault current suppression and cost reduction is not as good as that of the converter-based methods, but the FCL current suppression method strictly follows the N-1 principle. Therefore, the FCL may be more suitable to a DC grid.

In addition to converters, FCL and DCCB, DC-DC converters and power flow controllers (PFCs) may also be installed in a DC grid. The DC-DC converter usually has the SM-scalable controllability like MMCs. Therefore, the above devices can be considered to have an as similar fault current suppression effect as MMCs. The CFC usually controls the steady-state power flow of the DC grid and it is not required for high voltage withstanding capability. For this reason, it has not been discussed in this paper.

# **Appendix**

The DC grid model is based on the four-terminal Zhangbei project [31]. Parameters and control strategies of the four stations are given in Table A1 and Table A2.

TABLE A1

PARAMETERS OF MMCS

| Items                | Station1&2 | Station 3&4 |

|----------------------|------------|-------------|

| AC voltage           | 230 kV     | 500 kV      |

| Transformer Capacity | 1700 MW    | 3400 MW     |

| Transformer Leakage  | 0.1 pu     | 0.15 pu     |

| Arm Inductance       | 0.06 H     | 0.1 H       |

| SM Number            | 250        | 250         |

| SM Capacitance       | 7500 μF    | 15000 μF    |

| CLR Inductance       | 150 mH     | 150 mH      |

TABLE A2

MMC CONTROL STRATEGIES

| Station1 | active power   | P <sub>N</sub> =1500 MW        |

|----------|----------------|--------------------------------|

|          | reactive power | $Q_{\rm N}=150~{\rm Myar}$     |

| Station2 | active power   | $P_{\rm N} = 1500 \; {\rm MW}$ |

|          | reactive power | $Q_{\rm N}=150~{\rm Myar}$     |

| Station3 | active power   | $P_{\rm N} = 3000  {\rm MW}$   |

|          | reactive power | $Q_{\rm N}=300~{\rm Myar}$     |

| Station4 | DC voltage     | $U_{\rm DC}=\pm 500~{\rm kV}$  |

|          | reactive power | $Q_{\rm N}$ =300 Mvar          |

#### REFERENCES

- [1] T. An, X Zhou, C Han Y Wu, Z He, H Pang and G Tang, "A DC grid benchmark model for studies of interconnection of power systems," CSEE Journal of Power and Energy Systems, vol.1, no.4, pp.101-109, Dec. 2015.

- [2] T. An, G. Tang, and W. Wang, "Research and application on multi-terminal and DC grids based on VSC-HVDC technology in China," IET High Voltage vol.2, no.1, pp.1-10, 2017.

- [3] Juan Manuel Carrasco et al., "Power-Electronic System for the Grid Integration of Renewable Energy Sources: A Survey," IEEE Trans. Industrial Electronics, vol. 53, no.4, pp. 1002-1016, Aug. 2006.

- [4] W. Grieshaber et al., "Development and Test of a 120kV direct current circuit breaker," CIGRE Session', Paris, France, Aug. 2014, pp. 1–11.

- [5] A. Jamshidi Far and D. Jovcic, "Design, Modeling and Control of Hybrid DC Circuit Breaker Based on Fast Thyristors," IEEE Transactions on Power Delivery, vol. 33, no. 2, pp. 919-927, April 2018.

- [6] C. Li, J. Liang and S. Wang, "Interlink Hybrid DC Circuit Breaker," in IEEE Transactions on Industrial Electronics, vol. 65, no. 11, pp. 8677-8686, Nov. 2018.

- [7] K. Sano and M. Takasaki, "A Surgeless Solid-State DC Circuit Breaker for Voltage-Source-Converter-Based HVDC Systems," IEEE Transactions on Industry Applications, vol. 50, no. 4, pp. 2690-2699, July-Aug. 2014.

- [8] X. Han, W. Sima, M. Yang, L. Li, T. Yuan and Y. Si, "Transient Characteristics Under Ground and Short-Circuit Faults in a ±500 kV MMC-Based HVDC System with Hybrid DC Circuit Breakers," in IEEE Transactions on Power Delivery, vol. 33, no. 3, pp. 1378-1387, June 2018

- [9] W. Zhou X. Wei S. Zhang et al., "Development and test of a 200kV full-bridge based hybrid HVDC breaker," 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), Geneva, 2015, pp. 1-7.

- [10] X. Li, Z. Yuan, J. Fu, Y. Wang, T. Liu and Z. Zhu, "Nanao multi-terminal VSC-HVDC project for integrating large-scale wind generation," 2014 IEEE PES General Meeting Conference & Exposition, National Harbor, MD, 2014, pp. 1-5

- [11] W. Lin, D. Jovcic, S. Nguefeu and H. Saad, "Full-Bridge MMC Converter Optimal Design to HVDC Operational Requirements," in IEEE Transactions on Power Delivery, vol. 31, no. 3, pp. 1342-1350, June 2016.

- [12] S. Wenig, M. Goertz, C. Hirsching, M. Suriyah and T. Leibfried, "On Full-Bridge Bipolar MMC-HVDC Control and Protection for Transient Fault and Interaction Studies," in IEEE Transactions on Power Delivery, vol. 33, no. 6, pp. 2864-2873, Dec. 2018.

- [13] S. Li J. Xu Y. Lu et al., "An Auxiliary DC Circuit Breaker Utilizing an Augmented MMC," in IEEE Transactions on Power Delivery, vol. 34, no. 2, pp. 561-571, April 2019.

- [14] J. Xu, X. Zhao, H. Jing, J. Liang and C. Zhao, "DC Fault Current Clearance at the Source-side of HVDC Grid Using Hybrid MMC," in IEEE Transactions on Power Delivery.

- [15] C. Xiying, D. M. Sheng, L. Xiang, S. Yunting, M. Shiying and G. Feng, "Research on the DC access grid security and stability analysis," 2013 2nd International Symposium on Instrumentation and Measurement, Sensor Network and Automation (IMSNA), Toronto, ON, 2013, pp. 942-946.

- [16] B. Li, J. He, Y. Li, W. Wen and B. Li, "A Novel Current-Commutation-Based FCL for the Flexible DC Grid," in IEEE Transactions on Power Electronics, vol. 35, no. 1, pp. 591-606, Jan. 2020.

- [17] B. Li, J. He, Y. Li and R. Li, "A Novel Solid-State Circuit Breaker with Self-Adapt Fault Current Limiting Capability for LVDC Distribution Network," in IEEE Transactions on Power Electronics, vol. 34, no. 4, pp. 3516-3529, April 2019.

- [18] J. Xu, X. Zhao, N. Han, J. Liang and C. Zhao, "A Thyristor-Based DC Fault Current Limiter with Inductor Inserting Bypassing Capability," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 7, no. 3, pp. 1748-1757, Sept. 2019.

- [19] S. Wang, C. Li, O. D. Adeuyi, G. Li, C. E. Ugalde-Loo and J. Liang, "Coordination of MMCs With Hybrid DC Circuit Breakers for HVDC Grid Protection," in IEEE Transactions on Power Delivery, vol. 34, no. 1, pp. 11-22, Feb. 2019.

- [20] J. He, B. Li and Y. Li, "Analysis of the fault current limiting requirement and design of the bridge-type FCL in the multi-terminal DC grid," in IET Power Electronics, vol. 11, no. 6, pp. 968-976, 29 5 2018.

- [21] J. Yang, J. E. Fletcher and J. O'Reilly, "Short-Circuit and Ground Fault Analyses and Location in VSC-Based DC Network Cables," in IEEE Transactions on Industrial Electronics, vol. 59, no. 10, pp. 3827-3837, Oct. 2012.

- [22] Q. Tu, Z. Xu, and L. Xu, "Reduced Switching-Frequency Modulation and Circulating Current Suppression for Modular Multilevel Converters," IEEE Trans. Power Del., vol. 26, no. 3, pp. 2009-2017, July 2011.

- [23] J. Wang, H. Ma and Z. Bai, "A Submodule Fault Ride-Through Strategy for Modular Multilevel Converters with Nearest Level Modulation," *IEEE Trans Power Electronics*, vol. 33, no. 2, pp. 1597-1608, Feb. 2018

- [24] A. Hassanpoor, J. Häfner and B. Jacobson, "Technical Assessment of Load Commutation Switch in Hybrid HVDC Breaker," IEEE Trans. Power Electron., vol.30, no.10, pp.5393-5400, Oct. 2015.

- [25] Y. Song, J Sun, M Saeedifard, S Ji, L Zhu, and L Graber., "Reducing the Fault-Transient Magnitudes in Multiterminal HVdc Grids by Sequential Tripping of Hybrid Circuit Breaker Modules," IEEE Trans. Ind. Electron, vol. 66, no. 9, pp. 7290-7299, Sept. 2019.

- [26] M. H. Hedayati and D. Jovcic, "Reducing Peak Current and Energy Dissipation in Hybrid HVDC CBs Using Disconnector Voltage Control," IEEE Trans. on Power Deliv, vol. 33, no. 4, pp. 2030-2038, Aug. 2018.

- [27] M. Zaja, A. Razi-Kazemi, D. Jovcic, "A Detailed Electro-Dynamic Model of an Ultra-Fast Disconnector Including the Failure Mode," High Voltage. 8 pp. (early access)

- [28] D. Jovcic, "Fast Commutation of DC Current into a Capacitor Using Moving Contacts," in IEEE Transactions on Power Delivery, vol. 35, no. 2, pp. 639-646, April 2020.

- [29] G. Chaffey and T. C. Green, "Directional current breaking capacity requirements for HVDC circuit breakers," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 5371-5377.

- [30] J. Sun, M. Saeedifard and A. P. S. Meliopoulos, "Backup Protection of Multi-Terminal HVDC Grids Based on Quickest Change Detection," *IEEE Transactions on Power Delivery*, vol. 34, no. 1, pp. 177-187, Feb. 2019

- [31] G Tang, H. Pang and X. Wei, "Research on Key Technology and Equipment for Zhangbei 500kV DC Grid," 2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia), Niigata, 2018, pp. 2343-2351

**Xibei Zhao** was born in Hebei, China. He received the B.S degree from Chongqing University (CQU) in 2015, currently he is a Ph.D. student in North China Electric Power University (NCEPU) from 2017. From Aug 2019 to Oct 2020, he is a joint Ph.D. student at Cardiff University. His research interests include HVdc grid operation and protection.

**Lixu Chen** received the B.S. degree in Electrical Engineering and its Automation from North China Electric Power University, Baoding, China, in 2019. He is currently working toward the M.S. degree at North China Electric Power University, Beijing, China.

His current research interests are mainly on flexible DC grid and its DC fault current suppression and clearance.

Gen Li (M'18) received the B.Eng. degree in Electrical Engineering and its Automation from Northeast Electric Power University, Jilin, China, in 2011, the M.Sc. degree in Power Engineering from Nanyang Technological University, Singapore, in 2013 and the Ph.D. degree in Electrical Engineering from Cardiff University, Cardiff, U.K., in 2018.

From 2013 to 2016, he was a Marie Curie Early Stage Research Fellow funded by the European Union's

MEDOW project. He has been a Visiting Researcher at China Electric Power Research Institute and Global Energy Interconnection Research Institute, Beijing, China, at Elia, Brussels, Belgium and at Toshiba International (Europe), London, U.K. He has been a Research Associate at the School of Engineering, Cardiff University since 2017. His research interests include control and protection of HVDC and MVDC technologies, power electronics, reliability modelling and evaluation of power electronics systems.

Dr. Li is a Chartered Engineering in the U.K. He is an Associate Editor of the CSEE Journal of Power and Energy Systems. He is an Editorial board member of CIGRE ELECTRA. His Ph.D. thesis received the First CIGRE Thesis Award in 2018.

Jianzhong Xu (M'14) was born in Shanxi, China. He received the B.S. and Ph.D. degrees fromNorth China Electric Power University (NCEPU), Beijing, China, in 2009 and 2014, respectively. From 2012 to 2013 and 2016 to 2017, he was, respectively, a joint Ph.D. student and Postdoctoral Fellow with the University of Manitoba. He is currently an Associate Professor with the State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources, NCEPU. He is

now working on the high-speed electromagnetic transient modeling, control, and protection of MMC-HVdc and dc grid.

JINSHA YUAN received the M.E. degree in theoretical electrical engineering and the Ph.D. degree in electrical engineering and its automation from North China Electric Power College, Baoding, China, in 1987 and 1992, respectively. He is currently a Professor and a Ph.D. Supervisor with North China Electric Power University, Baoding. His research interests include intelligent information processing technology, wireless communication, and electromagnetic field numerical

calculation method and application.