## **ORCA - Online Research @ Cardiff**

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/134724/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Wang, Yibo, Wang, Peng, Cai, Guowei, Liu, Chuang, Guo, Dongbo, Zhang, Hanwen, Zhu, Bingda and Li, Gen 2021. An improved bipolar-type AC-AC converter topology based on non-differential dual-buck PWM AC choppers. IEEE Transactions on Power Electronics 36 (4), pp. 4052-4065. 10.1109/TPEL.2020.3022026

Publishers page: http://dx.doi.org/10.1109/TPEL.2020.3022026

#### Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# An Improved Bipolar-Type AC-AC Converter Topology Based on Non-Differential Dual-Buck PWM AC Choppers

Yibo Wang, Student Member, IEEE, Peng Wang, Guowei Cai, Chuang Liu, Member, IEEE, Dongbo Guo, Hanwen Zhang, Bingda Zhu, and Gen Li, Member, IEEE

Abstract—A novel single-phase pulse width modulation (PWM) direct ac-ac converter based on two-level non-differential dual-buck ac chopper legs with inverting and non-inverting operations is first proposed in this paper. It has the ability to resolve both voltage sag and swell problems at the same time when used as distributed flexible voltage conditioner (DFVC). Compared to the traditional ac-ac converter, it has much enhanced system reliability thanks to no shoot-through problems even when all switches of each ac chopper legs are turned on, and therefore, the PWM dead-time is not needed leading to improving the utilization of the duty cycles. Only half of the switches in the proposed converter are switched at high frequency during a switching period at most, which significantly reduces the total switching loss. In particularly, the converter has two greatest advantages that it retains the common sharing ground of the input and output and has the same buck/boost operation process for non-inverting and inverting modes. In order to fully testify the performance of the proposed converter, a 500W experimental prototype is built and tested at different conditions.

Index Terms—AC-AC converter, bipolar voltage gain, non-differential AC chopper, voltage sag and swell, buck/boost operation process.

#### I. INTRODUCTION

THE parameters of electrical energy, such as supply voltage amplitude, has a great influence on both the operation of the power grid and the use of the load side [1]. With the continuous access of distributed generation, the voltage quality becomes worse. Among the many power quality problems, the sag and swell in supply voltage are the main problems. Voltage sag and swell will do a great deal of harm to the end-user, especially from the viewpoint of the sensitive loads such as hospitals, data centers, etc. In the case of big plants and

Manuscript received May 29, 2019; revised July 11, 2019, August 22, 2019, April 19, 2020 and July 16, 2020; accepted August 21, 2020. This work was supported in part by the National Natural Science Foundation of China under Grant 51877035. Recommended for publication by Associate Editor Yaow-Ming Chen. (*Corresponding author: Chuang Liu.*)

Y. Wang, G. Cai, C. Liu, D. Guo, H. Zhang and B. Zhu are with Key Laboratory of Modern Power System Simulation and Control & Renewable Energy Technology, Ministry of Education (Northeast Electric Power University), Jilin 132012, China (e-mail: 469682939@qq.com; cai4806439@126.com; victoliuchuang@163.com; 837271373@qq.com; 1025499953@qq.com; 674467193@qq.com).

P. Wang is with the State Grid Jurong Power Supply Company of Jiangsu Electric Power Company, Zhenjiang 212000, China (e-mail: 215900691@qq.com).

G. Li is with the Cardiff University, Cardiff CF24 3AA, U.K. (e-mail: LiG9@cardiff.ac.uk).

factories, voltage sags and swells may cause financial losses [2].

In order to fully mitigate unwanted effects of supply voltage, mainly voltage sags and swells, various types of devices have been developed in recent literature. These devices are primarily referred to as voltage sag/sell compensators [3]-[4], ac voltage regulators [5], ac stabilizers [6], ac voltage sag supporters [7], voltage conditioners [8], dynamic voltage restorers (DVR) [9]-[12], distributed flexible voltage conditioner (DFVC) [13], etc. Either of these devices can be designed with a voltage source inverter (VSI) or a direct PWM ac-ac converter. AC voltage compensator based on VSI can be divided into two main types. One of the types is adopting dc-ac converters, which requires independent external energy storage systems such as batteries, capacitors, super magnetic energy storage, and so on. This feature determines that it is not capable of compensating deep and long-duration voltage sags or swells, and its magnitude and ride-through capability depend on the size and capacity of the storage systems [14]. Therefore, ac voltage compensator adopted dc-ac converters is not suitable for high power applications. The other ac voltage compensator based on ac-dc-ac converters does not need to use external energy storage systems, but it adds one ac-dc power processing stage with bulky DC link. These facts will reduce the efficiency of the whole systems and add to the maintenance burden. If the ac voltage compensator implements the direct ac-ac converters, the DC-link will be saved, the whole systems will be improved, and no external energy storage systems will be required, the devices volume and cost also will be reduced. Specially, the direct ac-ac converters are more attractive in applications where only need to maintain the grid voltage amplitude without changing phase shift and frequency at the same time. Under this motivation, the direct ac-ac converter is to be studied continuously [15]-[16].

The simplest and most basic ac-ac converters including buck, boost, buck-boost topologies, etc. These converters inherit the merits of simple structure, uncomplicated control, and high conversion efficiency, but they have common commutation problems due to using ac switches [17]-[18]. To overcome commutation problems, RC buffer circuit and the soft commutation strategies are the two commonly used methods. However, these two methods have some shortcomings, such as the commutation strategy cannot guarantee the zero-crossing reliable commutation, and the output voltage waveforms are distorted because energy is dissipated in the RC snubber circuits. Recently, a novel single-phase PWM ac-ac converters solving commutation problem without using RC snubber circuits or soft commutation strategies is presented in [19]-[21].

These converters, while effectively solving the commutation problems, all suffer from a unipolar voltage gain range, which, in use of the grid-voltage compensation, restricts them to mitigate either voltage sag or swell but not both [22].

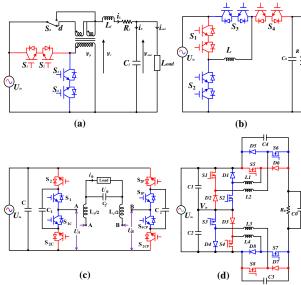

To overcome this constraint of ac-ac converter applications, a cost-effective ac voltage stabilizer based on ac-ac converters is proposed in [23], as shown in Fig. 1 (a). It can output bipolar voltage by adding a mechanical switch, but there are some shortcomings in mechanical switches such as slow response speed, voltage step change, etc. In [24], a Z-source PWM ac-ac converter is presented to achieve the bipolar voltage gain through an additional impedance network. However, the sharp rise and fall in its gain during the non-inverting buck operation are quite challenging for the controller. Another Z-source ac-ac converter is analyzed in [25], it is able to output bipolar voltage, but it requires a new commutation strategy to achieve safe commutation. The topology shown in Fig. 1(b) is a unified non-inverting and inverting PWM ac-ac converter capable of obtaining bipolar voltage gains [26]. But the converter may have commutation problems due to employing bidirectional switches, which decreases the reliability of the systems. Hence, it also needs to adopt a safe commutation strategy to address commutation problems [27]. Recently, a novel bipolar-type direct ac-ac converter is presented in [13], as shown in Fig. 2(c). This converter not only resolves the commutation problem, but also retains the common sharing ground of the input and output. Especially, the main advantage is that the converter has the same buck/boost operation process for non-inverting and inverting modes. However, it is necessary for this converter to set a dead-time to solve the shoot-through problems due to the two active switches in each legs of the converter, which reduces utilization of the duty cycles. A buck-boost ac-ac converters adopting switching cell structured and coupled inductor is proposed in [28], as shown in Fig. 1(d). This converter effectively solves the commutation problem and does not need to set dead-time. But it needs more numbers of passive components, which increases the volume of the devices in high-power applications. Moreover, similar to the converter proposed in [29]-[32], the converter has not the same buck/boost operation process for non-inverting and inverting modes and have not the common ground on input and output. In addition, a high-frequency isolated AC-AC converter with bipolar voltage gain is proposed in [33]-[34]. However, this converter has some drawbacks, such as a converter proposed in [34] needs to a safe-commutation strategy, which reduces its reliability.

To overcome above constraints, this paper investigates a novel single-phase ac-ac converter based on two-level non-differential dual-buck ac chopper legs with bipolar voltage gains. The DB-AC has the following advantages:

- 1) It can achieve continuous and bipolar voltage transfer without drastic changes and the combination of multiple PWM modulation modes increases the degree of freedom of control. It employs less passive devices, thus reducing footprint of the converter.

- 2) By adopting dual-buck ac chopper legs, it does not need to set dead-time, which increases the utilization of the equivalent pulse width-modulated voltage, and leads to output waveform distortions and less energy transfer. Partial free-wheeling

diodes can be chosen independently with fast reverse recovery features to minimize switching loss.

- 3) The limiting inductors of each ac choppers are replaced by separated inductors instead of coupled inductors, which effectively decreases the magnetic volume and improves the ability to deal with power density. The limiting inductors also contributes to the inductance of the output filter inductor, which is conducive to reducing volume of the output filters.

- 4) The common ground between the input and output ports is retained, the feature that output can reverse or maintain phase angle with input is supported well. Additionally, it has the same buck/boost operation process for non-inverting and inverting modes, which ensures the continuously average current supply to the output side without a high-value capacitor to supply power.

Fig. 1 Four types of bipolar AC-AC converters.

The paper is arranged as follows. The description of the proposed topology and PWM modulation principles are described in section II. Section III investigates the operation states of the ac-ac converter. Section IV discusses the design of the converter parameters. Experimental results illustrating the performance of the converter are presented in Section V. Finally, the conclusions are highlighted in Section VI.

## II. DESCRIPTION OF THE PROPOSED TOPOLOGY AND PMW MODULATION PRINCIPLES

#### A. Topology of the Proposed Converter

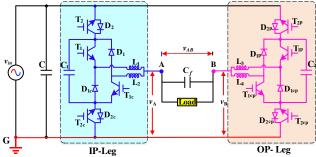

The novel bipolar-type dual-buck PWM AC-AC converter (DB-AC) proposed is expressed in Fig. 2. As shown in Fig. 2, the topology structure of the DB-AC is consisted of two dual-buck ac chopper legs with two separation inductors that are defined as IP-Leg (in-phase leg) and OP-Leg (out-of-phase leg) respectively, both of which are two-level non-differential ac choppers. Hence, the polarity of the output port voltage  $v_{AB}$  is determined by the voltage difference between the two legs, that is  $v_{AB}=v_A-v_B$ , where  $v_A$  and  $v_B$  are IP-Leg and OP-leg voltage respectively. Four insulated gate bipolar transistor (IGBT) that two of the IGBT contain antiparallel body diodes, and the other two do not contain, two fast recovery diodes, two inductors and one capacitor are contained in each leg, and the

connected relation of the components and parts is shown in Fig. 2. The diodes  $D_1$ ,  $D_{1c}$  and  $D_{1p}$ ,  $D_{1cp}$  in each leg are fast recovery diode, which validly relieves the problems of high loss and slow turn-off of bulk diode. On the other hand, in order to reduce the influence of the source voltage, an input capacitor is added at input side. Additionally, the two legs retain a common ground connection with the input side.

The proposed DB-AC can effectively deal with the problem commutation without bulky and lossy resistor-capacitor (RC) snubbers circuits or soft commutation strategies, which obviously improves the reliability of the systems. The bipolar output voltage can be ensured by IP-Leg and OP-leg voltage, and it is precisely because of the two controllable objects of the topology that the flexibility and diversity of the proposed DB-AC can be improved commendably. With the common sharing ground of the input and output, the feature that output can reverse or maintain phase angle with input is supported well. Meanwhile, no dead time is required, which increases the utilization of the equivalent pulse width-modulated voltage, and leads to output waveform distortions and less energy transfer. The particularly outstanding superiority is that the proposed DB-AC has the same buck or boost running process for non-inverting and inverting modes, so there is no need to design high-value capacitors to ensure that the average current of the outside continuously.

Fig. 2. Schematic of the proposed DB-AC.

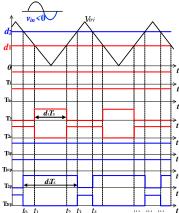

#### B. PWM Modulation Principles

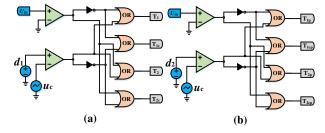

Fig. 3. PWM modulation principles.

The PWM modulation principle with zero vector coupling of the proposed DB-AC is shown in Fig. 3. A square wave signal is generated by a comparison of  $v_{in}$  and zero potential. Besides, the converter flexibility is improved with two duty cycles, where  $d_1$  and  $d_2$  are the duty cycles of IP-Leg and OP-Leg, respectively, and  $u_c$  is a triangular carrier with a scope value of 0 to 1. Compared with the interleaved PWM strategy used in [19], the proposed PWM strategies reduce partial circulation due to the absence of the mode in which all switches are turned

on simultaneously. Additionally, the proposed converter has the least number of switches to do high-frequency switching in a switching period through using the proposed PWM strategies, which further reduces the total switching loss and improves the efficiency of the converters. In order to further understand the DB-AC, the comparative analysis between it and previously published bipolar voltage gain ac-ac converters is shown in TABLE I.

#### III. OPERATION OF THE PROPOSED CONVERTER

According to the analysis of the PWM strategies mentioned above, the input voltage in the positive and negative half-wave has a direct effect on the working process of the converters. Considering the proposed topology is a novel bidirectional AC-AC converter and in order to analysis the working process of it in detail, the buck operation mode is clearly divided into in-phase and out-of-phase in TABLE II with the interrelation between input and output voltage.

According to the work pattern shown in TABLE II, the proposed DB-AC has a variety of operation modes. Regardless of the operating mode, the relationship between input voltage  $v_{in}$  and output voltage  $v_o$  is as follows.

$$v_0 = v_A - v_B = (d_1 - d_2)v_{in}$$

(1)

Where  $v_A$  and  $v_B$  are the output voltages of ports A and B, respectively,  $v_A=d_1v_{in}$  and  $v_B=d_2v_{in}$ .

Further, the formula (1) can be rewritten

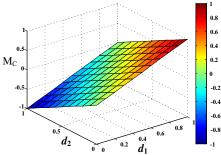

$$M_C = \frac{v_0}{v_{in}} = (d_1 - d_2) \tag{2}$$

Where  $M_C$  is defined as voltage gains of the DB-AC, it reflects the input-output relationship of the converter and it is determined by the duty cycles of the two legs.

The interrelation between  $M_C$  and  $(d_1, d_2)$  are presented in Fig. 4 and it is clear observed that the range of  $M_C$  is from -1 to 1. That is to say, the proposed DB-AC has the capability of bipolar voltage gains. Similar to the TABLE II above, the DB-AC is divided into in-phase operation state and out-of-phase operation state based on the voltage polarity between input and output. It should be pointed out that the converter has three modulation modes (Modes I, II, II), regardless of the output voltage and the input voltage in the same phase or the inverse phase, but modulation modes I and III are the special cases of modulation mode II. To avoid repeating description, the modulation mode II is taken as an example to analyze in detail in the operation process A and B of the proposed converter. Additionally, it is stipulated that the load current io flows from output ports A to output ports B in the positive direction, that is,  $i_0 > 0$ , and vice versa, the load current  $i_0$  in a negative direction. Because the operation process of the converter is different when the input voltage is different at different half-waves, in order to fully analyze the operation process of the converter, the positive half-wave of the input voltage is analyzed in detail in process A (A. OPERATION PROCESS IN IN-PHASE), and the negative half-wave of the input voltage is analyzed in detail in process B (B. OPERATION PROCESS IN OUT-OF-PHASE).

TABLE I

COMPARISON BETWEEN THE PROPOSED DB-AC AND PREVIOUSLY PUBLISHED BIPOLAR VOLTAGE GAIN AC-AC CONVERTERS

|                                          | DB-AC                        | Proposed in [26] (Fig. 1(b))                  | Proposed in [13]<br>(Fig. 1(c)) | Proposed in [28]<br>(Fig. 1(d))           | Proposed in [24]                      |

|------------------------------------------|------------------------------|-----------------------------------------------|---------------------------------|-------------------------------------------|---------------------------------------|

| Voltage gain                             | $d_1$ - $d_2$                | $2-1/d$ , $d_3/(d_3-1)$ , $(d_1-d_3)/(1-d_3)$ | $d_1$ - $d_2$                   | $d$ , $d_1/(d_1-1)$ , $2-1/d_2$           | (1-d)/(1-2d),(1-2d)/(1-d)             |

| Switches numbers                         | 8                            | 8                                             | 8                               | 8                                         | 2                                     |

| Passive devices                          | 4 inductors, 3 capacitors    | 1 inductor, 1 capacitor                       | 1 inductor, 3 capacitors        | 4 inductors, 5 capacitors                 | 3 inductors, 3 capacitors             |

| Ground sharing                           | Yes                          | Yes                                           | Yes                             | No                                        | No                                    |

| Dead time                                | No                           | Yes                                           | Yes                             | No                                        | No                                    |

| Reliable commutation                     | No commutation problem       | Need soft commutation strategies              | No commutation problem          | No commutation problem                    | An external snubber circuit is needed |

| Same inverting and non-inverting process | Yes                          | No                                            | Yes                             | Possible                                  | No                                    |

| Adopt bidirectional switches             | No                           | Yes                                           | No                              | No                                        | Yes                                   |

| Controllable degrees of freedom          | Two $(d_1 \text{ and } d_2)$ | One (d) or Two ( $d_1$ and $d_3$ )            | Two $(d_1 \text{ and } d_2)$    | One $(d \text{ or } d_1 \text{ or } d_2)$ | One (d)                               |

### TABLE II PARTITIONING TABLE OF WORK MODE

| $v_0$                               | Modulation modes | $d_1$                    | $d_2$                 |

|-------------------------------------|------------------|--------------------------|-----------------------|

|                                     | Mode I           | 0 <d<sub>1x&lt;1</d<sub> | 0                     |

| $v_0$ is in phase with $v_{in}$     | Mode II          | $0 < d_{1x} < 1$         | $0 < d_{2x} < d_{1x}$ |

| with $V_{in}$                       | Mode III         | 1                        | $0 < d_{2x} < 1$      |

| is out of phase                     | Mode I           | 0                        | $0 < d_{2x} < 1$      |

| $v_0$ is out of phase with $v_{in}$ | Mode II          | $0 < d_{1x} < d_{2x}$    | $0 < d_{2x} < 1$      |

| WIUI Vin                            | Mode III         | 0 <d<sub>1x&lt;1</d<sub> | 1                     |

Fig. 4 The relationship between  $M_C$  and  $(d_1, d_2)$ .

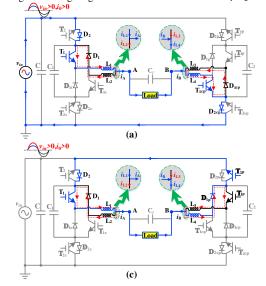

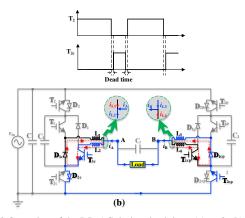

#### A. Operation Process in In-phase

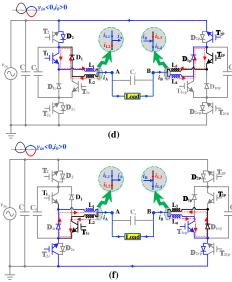

In this operation process  $M_C>0$ , and the output voltage  $v_o$  maintains the same phase as the input voltage  $v_{in}$ , and the two duty cycles of  $d_1$  and  $d_2$  range from 0 to 1 respectively, but  $d_1>d_2$ . At this modulation modes, the proposed converter has the maximum controllable degree of freedom. Further, in order to analyze in detail, the working process is discussed when the  $i_o>0$ ,  $i_o<0$ , and the input voltage is positive half-wave. At this point, the switches  $T_2$ ,  $T_{2c}$ ,  $T_{2p}$  and  $T_{2cp}$  are always ON,  $T_1$ ,  $T_{1c}$ ,  $T_{1p}$  and  $T_{1cp}$  are modulated in a PWM manner. The gate signal and operation with current flowing of the proposed DB-AC is shown in Fig. 5 and Fig. 6, respectively. Fig. 6 (a), (b), and (c) are employed to illustrate the working process of the proposed converter when  $i_o>0$ , and Fig. 6 (d), (e), and (f) are used to describe the working process of the converter when  $i_o<0$ .

Fig. 5 Gate signal generation of switches when  $1>d_1>d_2>0$ .

Fig. 6 The effective switching states of DB-AC under operation process A  $(1>d_1>d_2>0)$  and  $v_{in}>0$ .

#### State I $[t_0 \sim t_1]$

As shown in Fig. 6(a), in this state, the switches  $T_2$ ,  $T_{2c}$ ,  $T_{2p}$ ,  $T_{2cp}$ ,  $T_1$  and  $T_{1cp}$  are all turned on and the  $T_{1p}$ ,  $T_{1c}$  are turned off. At this time, the converter is in active state, and the voltage and current relationships are as follows:

$$v_{L_{sum}} = v_{in} - v_{o} \tag{3}$$

$$v_{L_{sum}} = v_{in} - v_{o}$$

$$L_{eq} \frac{di_{L1}}{dt} = 2L \frac{di_{L1}}{dt} = 2L \frac{di_{L4}}{dt} = (1 - d_{1} + d_{2})v_{in}$$

(4)

Where  $v_{Lsum}$  is the sum of voltages across all inductors, and it contains three parts:  $v_{L1}$ ,  $v_{L4}$ , L represent the inductance values of the separation inductors  $L_1 \sim L_4$ .

When the inductor current  $i_o < 0$ , the switches operate in the same order as when the inductor current  $i_0 > 0$ , but the diodes  $D_2$ and D<sub>2cp</sub> become reverse biased, and the diodes D<sub>1</sub>, D<sub>1cp</sub> become forward biased. Therefore, a current path shown in Fig. 6 (b) is formed. Since the inductance values of the four separate inductors are the same, the voltage and current relationships in the circuit at this time are the same as formulas (3) and (4). Consequently, the above relationship formulas are not repeated here.

#### State II $[t_1 \sim t_2]$

Fig. 6 (c) is adopted to describing state II of the converter, this moment, switches  $T_1,\,T_2,\,T_{2c},\,T_{1p},\,T_{2p}$  and  $T_{2cp}$  are ON, and other switches T<sub>1c</sub> and T<sub>1cp</sub> are OFF. Additionally, the body diodes  $D_1$  and the fast recovery diodes  $D_{1p}$  are forward biased. The current loop is shown in Fig. 6 (b), and the relationship of the voltage and current can be expressed as follows.

$$v_L = -v_o \tag{5}$$

$$L_{eq} \frac{di_{L1}}{dt} = 2L \frac{di_{L1}}{dt} = 2L \frac{di_{L4}}{dt} = (d_2 - d_1)v_{in}$$

(6)

Similarly, if the inductor current  $i_o < 0$  at this state, the diodes  $D_1$  and  $D_{2p}$  become forward biased, and the diodes  $D_2$ ,  $D_{1p}$ become reverse biased. Thus, the current flow loop is shown in Fig. 6 (d), and the relationship between voltage and current is similar to formulas (5) and (6).

#### State III $[t_2 \sim t_3]$

State III is similar to state I, therefore, Fig. 6 (a) can also be used to describe state III. The variation of output filter inductor current is the same as that of state I, so it is not repeated. Similarly, when the inductor current  $i_o < 0$ , the working process of the converter is the same as that of Fig. 6 (b).

#### **State IV** [*t*<sub>3</sub>~*t*<sub>4</sub>]

The converter is in state IV, when the switches  $T_{1c}$ ,  $T_2$ ,  $T_{2c}$ ,  $T_{1cp}$ ,  $T_{2p}$  and  $T_{2cp}$  are ON, and at the same time the switches  $T_1$ and T<sub>1p</sub> is OFF. State IV is described in Fig. 6 (e), the converter is in continuous flow state right now. The relationship between the voltage and current can be expressed as follows.

$$L_{eq} \frac{di_{L1}}{dt} = 2L \frac{di_{L1}}{dt} = 2L \frac{di_{L4}}{dt} = (d_1 - 1)v_{in}$$

(7)

Fig. 6 (f) can be employed to describe the working process of the proposed converter with inductor current  $i_0 < 0$  in state II. At this point, the diodes D<sub>1cp</sub> and D<sub>2c</sub> become forward biased, and the diodes D<sub>1c</sub>, D<sub>2cp</sub> become reverse biased, and the inductor current also decreases linearly. The relationship between voltage and current is also similar to formulas (7).

Combined with the analysis of the working process of the proposed converters and the PWM modulation strategies mentioned above, it can be seen that each legs of the converters has no state in which all switches are turned-on simultaneously, hence the circulating currents are also eliminated. Additionally, through the above analysis, we can see that the current flow direction on the four separated inductors is fixed regardless of the direction of the load current. Fig. 6 also shows that only two separated inductors ( $L_1$  and  $L_4$ ) or ( $L_2$  and  $L_3$ ) conduct the current ( $i_A$  and  $i_B$ ) at a time. At the same time, it can be seen that no matter in which state the converter works, the current always has a current loop, which effectively ensures the safe commutation of the proposed converter. The current relationship is as follows:

$$i_A = i_{L1} - i_{L2} = i_B = i_{L4} - i_{L3}$$

(8)

When the input voltage is in negative half-waves, the modulation principles and working process of the proposed converter are similar to the above analysis. Hence, in order to avoid repetition, this paper will not describe it again.

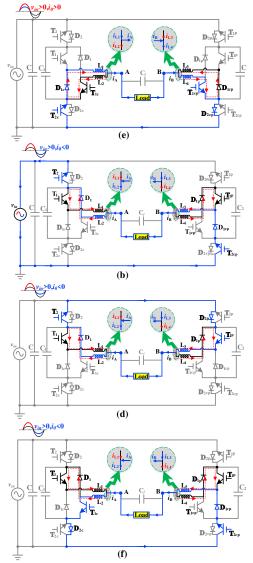

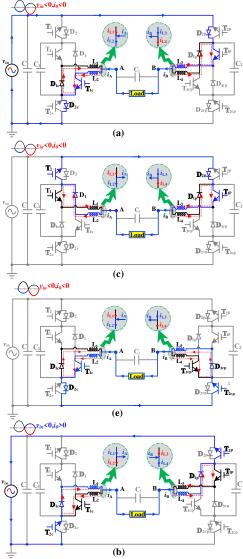

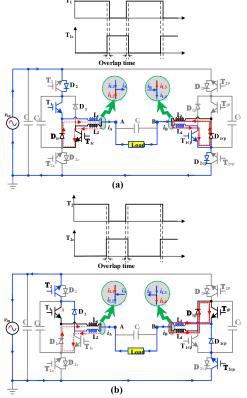

#### B. Operation Process in Out-of-phase

Similar to the above, when the output voltage  $v_o$  is out of phase with the input voltage  $v_{in}$ , the operation and analysis process is the same as that of the in-phase above. And limited to

length, the detailed analysis is not carried out in this paper and only shown the relevant information in Fig. 7 and Fig. 8. In order to increase the diversity of analysis, the working process diagram of the proposed converter is given when the input voltage is negative half-wave.

Fig. 7 Gate signal generation of switches when  $0 < d_1 < d_2 < 1$ , and  $v_{in} < 0$ .

Fig. 8 The effective switching states of DB-AC under operation process B  $(1>d_2>d_1>0)$  and  $v_m<0$ .

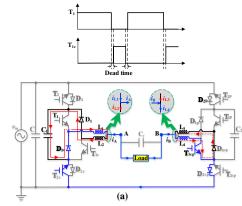

#### C. Dead Time and Overlap Time

Due to the delayed response of electronic circuits and semiconductor switching devices, the two switches with complementary signals may have the problem of dead-time and overlap-time in the operation of the converter. Taking the output voltage  $v_o$  is in phase with  $v_{in}$  and the converter adopts the modulation modes I as an example, the analysis will be carried out. In addition, this paper only takes the positive half-wave of input voltage as an example to carry on the analysis. At present, the switches  $T_2$ ,  $T_{2c}$ ,  $T_{1cp}$ ,  $T_{2p}$  and  $T_{2cp}$  are always ON, and  $T_{1p}$  is always OFF.

Ideally, the switches  $T_1$  and  $T_{1c}$  are modulated in a PWM manner, and the switches use complementary signals. However, due to the existence of dead time in the actual work of the converter, the switches  $T_1$  and  $T_{1c}$  are turned off in the dead-time, shown in Fig. 9. At present, the capacitor  $C_1$  or  $C_2$  bypass the separated inductors currents, shown in Fig. 9 (a) and (b). Similarly, there will also be overlap time in the actual work of the converter. The overlap time in which the switches  $T_1$  and  $T_{1c}$  are turned ON, shown in Fig. 10. The separated inductors limit the shoot-through current by providing a high impedance path at this time [35].

Fig. 9 Operation of the DB-AC during dead time. (a)  $i_0>0$ . (b)  $i_0<0$ .

Fig. 10 Operation of the DB-AC during dead time. (a)  $i_o > 0$ . (b)  $i_o < 0$ . Through the detailed analysis of the different working processes mentioned above, it can be seen that the converters mentioned in this paper can operate reliably under different working conditions and the proposed converter can guarantee the safe commutation without any other measures.

#### IV. DESIGN CONSIDERATION

Based on the above analysis, in this section, the guidelines of the parameter selection for the DB-AC are given. The known parameters: input voltage  $v_{in}$ =160-200V (50Hz) ac, range of voltage gain  $M_C$  is [-1, 1], output voltage  $v_o$ =80-120V (50Hz) ac, the rated power of the converter is  $P_o$ =500W, allowable current and voltage ripples  $k_i \le 20\%$  of  $i_L$  and  $k_V \le 20\%$  of  $v_o$  (or  $v_{in}$ ), and assuming that the minimum conversion efficiency of the proposed converter is 0.8.

#### A. Selecting of Switches

The two important bases for selecting the switches are the maximum current through the switches and the maximum voltage across the switch when it is open. In this topology, the maximum voltage across each switch is equal to the input peak voltage, that is  $v_{in.pk}$ =282.84V. The maximum current through the switches is given by the following equation:

$$I_{S.\text{max}} = \frac{v_0 i_0}{v_{in.\text{min}} \eta} = \frac{P_0}{v_{in.\text{min}} \eta} = \frac{500W}{80V} = 6.25A$$

(9)

Therefore, the switches used in proposed converter is initially selected as an IKW75T60 (600V/75A) and IGW50T60 (600V/50A) IGBT. As is well known, the higher the switching frequency is, the less the filters will be at a cost of more switching losses. But, considering the selected switches type, the switching frequency  $f_s$  is chosen as 18 kHz as a tradeoff. Additionally, diodes  $D_1$ ,  $D_{1c}$ ,  $D_{1p}$  and  $D_{1cp}$  choose fast recovery diodes, the type of which is RHRG6080.

#### B. Selecting of Separated Inductors

According to the above analysis, when the two duty cycles  $d_1$  and  $d_2$  of the converter are between 0 and 1, the converter has four working states in a switching period, of which two are active modes and two are continuous modes. Additionally, according to the different relationship of the two duty cycles, the relationship between the duration of the continuous current in two continuous current modes of the converter is obtained as follows.

If

$$d_1+d_2>1$$

,

then  $(1-d_1)T_S>d_2T_S$ .

Similarly, if  $d_1+d_2=1$ , then  $(1-d_1)T_S=d_2T_S$ ; If  $d_1+d_2<1$ , then  $(1-d_1)T_S>d_2T_S$ . Therefore, in order to ensure continuous-conduction mode (CCM) operation of the converter, the designed inductor must satisfy the continuity of the CCM under the different operation modes of the converter. Additionally, the maximum and minimum voltage gains of the converter can be determined according to the input and output voltages of the converter.

$$M_{C.\text{max}} = (d_{1x} - d_{2x})_{\text{max}} = \frac{v_{0.\text{max}}}{v_{in.\text{min}}} = \frac{120}{160} = 0.75$$

(10)

$$M_{C.min} = (d_{1x} - d_{2x})_{min} = \frac{v_{0.min}}{v_{in.max}} = \frac{80}{200} = 0.4$$

(11)

It can be seen from the above formula that different combinations can be realized through two duty cycles when the voltage gain  $M_C$  is guaranteed, which effectively improves the controllable freedom of the converter. It should be pointed out that during the design of the converter in this paper, we assume that the duty cycles  $d_{2,\text{min}}$ =0.1. Therefore, the maximum and minimum values of duty cycles  $d_1$  can be determined,  $d_{1,\text{max}}$ =0.85,  $d_{1,\text{min}}$ =0.5. The following is a discussion of inductor design under different operation conditions.

#### 1) When $d_1+d_2<1$

During one switching period  $T_s$ , there is

$$L_{eq} \frac{\Delta i_L}{\left(1 - d_1\right) T_S} = v_0 \tag{12}$$

In the formula above,  $\Delta i_L = 2k_iI_L$  and  $I_L$  represent current ripple and average value of  $i_L$ , respectively. For the converter, we can get formulas (13) and (14).

$$v_{in}i_{in}\eta = v_0i_0 \tag{13}$$

$$i_{in} = M_C I_L = (d_1 - d_2) I_L$$

(14)

Combining (2), (13) and (14), we can get the formula (15).

$$I_L = \frac{i_0}{\eta} \tag{15}$$

From (10), (12) and (15), equivalent inductor  $L_{eq}$  must be satisfied such that

$$L_{eq} \ge \frac{v_{0,\text{max}} \left(1 - d_{1,\text{max}}\right) \eta_{\text{min}}}{2k_i f_S i_{0,\text{min}}}$$

$$= \frac{120 \times \left(1 - 0.85\right) \times 0.8}{2 \times 0.2 \times 18 \times 10^3 \times \left(500 / 120\right)} = 0.48 mH$$

(16)

Therefore, the separated inductors used in paper is selected as  $L_1=L_2=L_3=L_4=L_{eq}/2=0.24m$ H.

#### 2) When $d_1+d_2>1$

The design principle of the inductor is similar to the above, so it is not discussed here. We can get the following formula for calculating separated inductors L.

$$L_{eq} \ge \frac{v_{0,\text{max}} d_{2,\text{min}} \eta_{\text{min}}}{2k_i f_s i_{0,\text{min}}}$$

$$= \frac{120 \times 0.1 \times 0.8}{2 \times 0.2 \times 18 \times 10^3 \times (500/120)} = 0.32mH$$

(17)

Therefore, the separated inductors used in paper is selected as  $L_1=L_2=L_3=L_4=L_{eq}/2=0.16m$ H.

In order to ensure the CCM of the converter under different conditions, the inductance value of the separated inductor is 0.3mH.

#### C. Selecting of Output Filter Capacitor $C_f$

During one  $T_s$ , the following equation is gained such that

$$\Delta v_0 = \frac{i_0 \Delta t}{C_f} = \frac{i_0 \left(\frac{d_1 - d_2}{2}\right) T_S}{C_f}$$

(18)

To limit the output voltage ripple, output filter capacitor  $C_f$  must satisfy the following:

$$C_{f} \ge \frac{i_{0,\text{max}} \left(d_{1} - d_{2}\right)_{\text{max}}}{k_{u} v_{0,\text{min}} f_{S}} = \frac{i_{0,\text{max}} M_{C,\text{max}}}{k_{u} v_{0,\text{min}} f_{S}}$$

$$= \frac{\left(500 / 80\right) \times 0.75}{0.2 \times 80 \times 18 \times 10^{3}} = 16.28 \mu F$$

(19)

The maximum voltage across  $C_f$  is  $\sqrt{2}v_{0,\text{max}} = 170$ , therefore,  $C_f$  is chosen as  $20\mu\text{F/}850\text{V}$ .

TABLE III

SPECIFICATION OF THE DB-AC EXPERIMENT

| Parameters                                    | Values            |

|-----------------------------------------------|-------------------|

| Peak Input voltage $v_{in}$                   | [160-200]/50Hz    |

| Voltage gains $M_c$                           | [-1 1]            |

| Output power $P_o$                            | 500W              |

| Switching frequency $f_c$                     | 18kHz             |

| Separated inductors $L_1 \sim L_4$            | 0.3 <i>m</i> H    |

| Capacitors $C$ , $C_1$ , $C_2$ , $C_f$        | $20\mu\mathrm{F}$ |

| IGBTs $T_1$ , $T_{1c}$ , $T_{1p}$ , $T_{1cp}$ | IGW50T60          |

| IGBTs $T_2$ , $T_{2c}$ , $T_{2p}$ , $T_{2cp}$ | IKW75T60          |

| Diodes                                        | RHRG6080          |

#### V. EXPERIMENTAL RESULTS OF THE DB-AC

#### A. Experimental Results of DB-AC

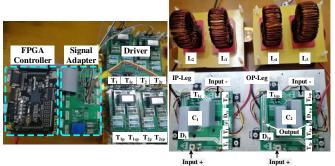

In order to verify the rationality and feasibility of the proposed AC-AC converter, a 500-W laboratory prototype of the DB-AC is fabricated and tested successfully. The photograph of the experimental setup is shown in Fig. 11, and the design specifications of the converter are offered in Table IV. For fully proving the performance and advantage of the proposed AC-AC converter, several different experiments were conducted specifically under the working scenarios shown in TABLE IV.

Fig. 11 Photograph of the experimental prototype.

#### TABLE IV EXPERIMENTAL SCENARIOS OF THE DB-AC

| Scenario number | $d_1$ | $d_2$ | Load                         | Operation process |

|-----------------|-------|-------|------------------------------|-------------------|

| Scenario I      | 0.85  | 0.25  | $R=20\Omega$                 | In-phase          |

| Scenario II     | 0.4   | 1     | $R=20\Omega, X_L=12.1\Omega$ | Out-of-phase      |

| Scenario III    | 0.6   | 0     | non-linear load              | In-phase          |

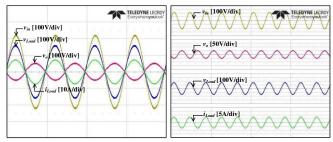

#### Scenario I

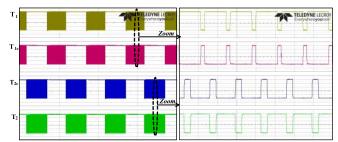

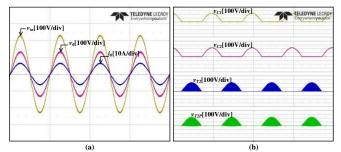

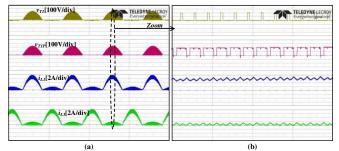

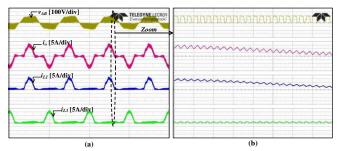

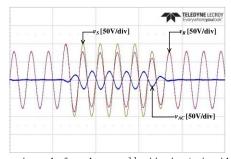

Fig. 12-15 show the results of Scenario I. Fig. 12 shows the four switches  $(T_1, T_{1C}, T_2, T_{2C})$  signals of DB-AC. It can be seen from the diagram that there are only two switches operating at high frequency on one leg in each half-wave period, and the other two switches are in the low-frequency and normally open state. On the other hand, the two complementary signals do not have any delay during the switching process, that is to say, the proposed AC-AC converter does not need to set dead-time during its operation, which is completely consistent with theoretical analysis. Fig. 13 (a) shows the waveforms of the input voltage  $v_{in}$ , output voltage  $v_o$ , and output current  $i_o$ . And Fig. 13 (b) shows the voltage waveforms of the capacitors  $C_1$ ,  $C_2$  and the voltage waveforms of the switches  $T_2$ ,  $T_{2P}$ . It can be seen that the voltage at both ends of switches and capacitors are half-wave voltage, and the maximum value is the peak value of input voltage  $v_{in}$ . The high frequency voltages  $v_A$ ,  $v_B$ ,  $v_{AB}$  and unfiltered current  $i_H$  waveforms are shown in Fig. 14(a). Fig. 14(b) also shows the zoomed waveforms of  $v_A$ ,  $v_B$ ,  $v_{AB}$  and  $i_H$ . As can be seen, unfiltered current  $i_H$  has four change process within one cycle. Fig. 15 shows the voltage waveforms of switches T<sub>1</sub>, T<sub>1P</sub> and current waveforms of separated inductors  $L_1, L_3$ . Similarly, Fig. 15 (b) shows the zoomed waveforms. The results waveforms prove that there is no excessive voltage and current surges in the converter during the Scenario I and the experimental results are in good agreement with the theoretical analysis results above.

Fig. 12 Switching signals of T<sub>1</sub>, T<sub>1C</sub>, T<sub>2</sub>, T<sub>2C</sub>. (Time: 20ms/div and 40μs/div).

Fig. 13 Experimental waveforms of the DB-AC under Scenario I with a pure resistive load (a) Waveforms of input voltage  $v_{in}$ , output voltage  $v_o$ , and output current  $i_o$  with 20ms/div. (b) Voltage waveforms of capacitors ( $C_1$ ,  $C_2$ ), and switches ( $T_2$ ,  $T_{2P}$ ) with 20ms/div.

Fig. 14 High frequency voltages  $v_A$ ,  $v_B$ ,  $v_{AB}$  and unfiltered current  $i_H$  waveforms (a) Time at 20ms. (b) Time at  $200\mu s$ .

Fig. 15 Voltage waveforms of switches  $T_1$ ,  $T_{1P}$ , current waveforms of limiting inductors  $L_1$ ,  $L_3$ . (a) Time at 20ms/div (b) Time at  $200\mu s/div$ .

#### Scenario II

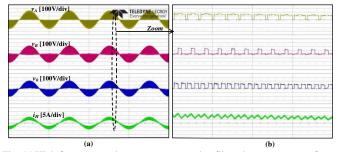

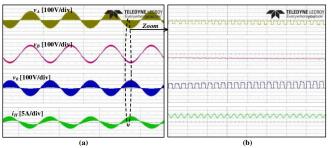

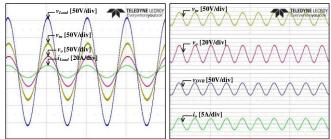

Fig. 16-18 show the results of Scenario II. Unlike Scenario I, in this case, the output voltage  $v_o$  is out of phase with the input voltage  $v_{in}$ . Besides, in order to distinguish the performance of the converter, the load type is selected for RL load and set the duty cycle  $d_2$  to 1. The specific analysis are as follows.

Fig. 16 (a) shows the input voltage  $v_{in}$ , the output voltage  $v_o$  and the output current  $i_o$ . As can be seen from the graph, the difference of phase angle between  $v_{in}$  and  $v_o$  is about 180°. Similar to Fig. 13 (b), the voltage waveforms of capacitors  $C_1$ ,  $C_2$  and switches  $T_2$ ,  $T_{2P}$  in this scenario is shown in Fig. 16 (b), and the  $v_{T2p}$  remains at zero level with the duty ratio  $d_2$  equals 1. It can be also seen in Fig. 17, the voltage  $v_B$  is presented in the

form of power frequency (50Hz). Besides, as compared to Scenario I, as shown in Fig. 18, the voltage of switch  $T_{1p}$  equals 0, and the separated inductors current  $i_{L1}$ ,  $i_{L3}$  only have two processes. In summary, the converter works well under Scenario II.

Fig. 16 Experimental waveforms of the DB-AC under Scenario II with *RL* load. (a) Waveforms of input voltage, output voltage, and output current with 50*ms*/div. (b) Voltage waveforms of capacitors (*C*<sub>1</sub>, *C*<sub>2</sub>), and switches (T<sub>2</sub>, T<sub>2P</sub>) with 20*ms*/div.

Fig. 17 High frequency voltages  $(v_A, v_B, v_{AB})$  and filter inductor current waveforms (a) Time at 20ms. (b) Time at 200 $\mu$ s.

Fig. 18 Voltage waveforms of switches ( $T_1$ ,  $T_{1P}$ ), current waveforms of limiting inductors ( $L_1$ ,  $L_3$ ). (a) Time at 20ms/div (b) Time at  $200\mu s/div$ .

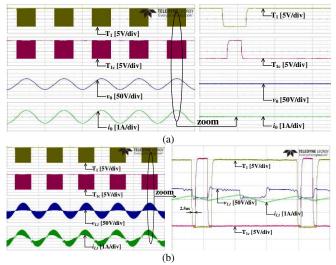

#### Scenario III

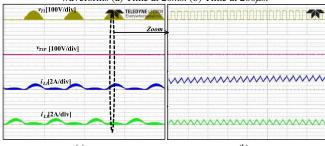

Fig. 19 and Fig. 20 show the experimental waveforms of the DB-AC under Scenario III with non-liner load. In this scenario, a single-phase uncontrollable rectifier bridge with capacitor filter and a pure resistive load is chosen as the non-linear load, which results in a large distortion of the voltage and current on the input AC side, as shown in Fig. 19(a). In addition, because the duty ratio  $d_2$  is equal to 0, the  $v_{T2p}$  is half of the input voltage waveform shown in Fig. 19(b). And the converter high frequency output voltage ( $v_{AB}$ ), the unfiltered current ( $i_H$ ) and two separated inductors currents ( $i_{L1}$ ,  $i_{L3}$ ) are shown in Fig. 20.

Fig. 21 and 22 are the experimental results of DB-AC with 2.5µs dead-time and overlap time respectively. From the experimental waveforms, it can be seen that the DB-AC proposed in this paper does not have the problem of commutation and shoot-through, and can run stably and reliably in dead-time and overlap time.

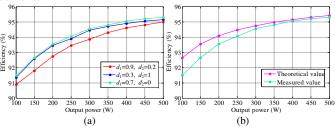

Fig. 23(a) shows the efficiency curves under a fixed pure resistive load (R=20 $\Omega$ ) with different duty ratio  $d_1$  and  $d_2$ ,

however, the voltage gain ( $M_C$ ) of the converter is all set as 0.7 under the three different scenarios. Fig. 23(b) shows the comparison between the measured value and the theoretical value with  $d_1$ =0.7,  $d_2$ =0. The theoretical value can be obtained by equation (20) and in order to simplify the calculation, we only analyze the power loss of the switches ( $T_1$ ,  $T_{1c}$ ,  $T_{1p}$ ,  $T_{1cp}$ ,  $T_2$ ,  $T_{2c}$ ,  $T_{2p}$ ,  $T_{2cp}$ ), body diodes ( $D_2$ ,  $D_{2c}$ ,  $D_{2p}$ ,  $D_{2cp}$ ), independent diodes ( $D_1$ ,  $D_{1c}$ ,  $D_{1p}$ ,  $D_{1cp}$ ) and inductors ( $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ ). The analysis process is obtained as follows:

$$\eta_{\text{Th}} = \frac{P_{\text{out}}}{P_{\text{in}}} \times 100\% = \frac{P_{\text{out}}}{P_{\text{out}} + P_{\text{loss}}} \times 100\%$$

(20)

Where  $\eta_{Th}$  is theoretical value of efficiency;  $P_{in}$ ,  $P_{out}$  and  $P_{loss}$  are the input power, output power and power loss of the converter within one power frequency cycle respectively.

Fig. 19 Voltage waveforms of switches  $(T_1, T_{1P})$ , current waveforms of limiting inductors  $(L_1, L_3)$ . (a) Time at 20ms/div (b) Time at  $200\mu s/div$ .

Fig. 20 Voltage waveforms of switches ( $T_1$ ,  $T_{1P}$ ), current waveforms of limiting inductors ( $L_1$ ,  $L_3$ ). (a) Time at 20ms/div (b) Time at  $200\mu s/div$ .

Fig. 21 The experimental results with 2.5  $\mu$ s dead times: (a) the switch signals of  $T_1$  and  $T_{1c}$ , the output voltage  $v_0$  and the output current  $i_0$ ; (b) the switch signals of  $T_1$  and  $T_{1c}$ , the voltage of inductor  $L_1v_{Li}$  and the current of inductor  $L_1$

Fig. 22 The experimental results with 2.5  $\mu$ s dead times: (a) the switch signals of  $T_1$  and  $T_{1c}$ , the output voltage  $v_0$  and the output current  $i_0$ ; (b) the switch signals of  $T_1$  and  $T_{1c}$ , the voltage of inductor  $L_I v_{LI}$  and the current of inductor  $L_I$

Then, the power loss can be calculated by (21):

$$\begin{split} P_{\text{loss}} &\approx P_{\text{IGBT-S}} + P_{\text{IGBT-CON}} + P_{\text{D-on}} \\ &+ P_{\text{D-off}} + P_{\text{D,turn-off}} + P_{\text{D,turn-off}} + P_{\text{inductor}} \end{split} \tag{21}$$

Where  $P_{\text{IGBT-S}}$  and  $P_{\text{IGBT-CON}}$  are the IGBT turn-on, turn-off and conduction loss respectively;  $P_{\text{D-on}}$ ,  $P_{\text{D-off}}$ ,  $P_{\text{D,turn-on}}$ ,  $P_{\text{D,turn-off}}$  and  $P_{\text{inductor}}$  are diode on state loss, diode off state loss, diode turn-on loss, diode turn-off loss and inductor loss, respectively.

$$P_{IGBT-S} = 0.02 \frac{f_s}{2} (E_{on} + E_{off}) \frac{I_{in}}{I_C} \frac{U_{in}}{U_{CC}} N$$

(22)

$$P_{\text{IGBT-CON}} = 0.01 \left[ \left( \frac{1}{4} d \cos \varphi V_{\text{CE(sat)}} I_{in} + \frac{2d \cos \varphi}{3\pi} r_{\text{CE}} I_{\text{in}}^{2} \right) + \left( \frac{1}{4} \cos \varphi V_{\text{CE(sat)}} I_{in} + \frac{2\cos \varphi}{3\pi} r_{\text{CE}} I_{\text{in}}^{2} \right) \right] N$$

(23)

Where  $E_{\rm on}$  is the turn-on loss;  $E_{\rm off}$  is the turn-off loss;  $f_{\rm s}$  is the switching frequency;  $V_{\rm CE(sat)}$  is saturation voltage drop;  $I_{\rm in}$  is the current (A) when the IGBT is in the on state; d is duty cycle; N is the number of IGBT.

The power loss of the body diodes  $(D_2, D_{2c}, D_{2p}, D_{2cp})$  are included. And the power loss of the independent diodes  $(D_1, D_{1c}, D_{1p}, D_{1cp})$  are calculated as follows:

$$P_{D-on} \approx 0.01 dV_F I_F n \tag{24}$$

$$P_{D-off} \approx 0.01 [(1-d)V_R I_R + V_R I_R] n$$

(25)

$$P_{D,turn-on} \approx 0.01 \times 0.5 V_{fp} I_{fp} t_{fp} f_s n$$

(26)

$$P_{D,turn-off} \approx 0.01 \times 0.5 V_{rp} I_{rp} t_b f_s n \tag{27}$$

Where  $t_{\rm fp}$  and  $t_{\rm b}$  are the turn-on and turn-off time of the independent diode respectively; n is the number of the independent diode; V and I are the corresponding voltage and current.

Fig. 23 Efficiency performance of DB-AC. (a) three scenarios. (b) comparison between the measured value and the theoretical value with  $d_1$ =0.7,  $d_2$ =0.

As can be seen from the figure, when the output power reaches 500W, the efficiency of the converter is over 95%. And the DB-AC will obtain higher efficiency in some cases with one duty cycle equals to 1 or 0. Because in the above two working conditions, the switching loss of the switches is smaller than other scenarios.

#### B. Application of Converter as DFVC

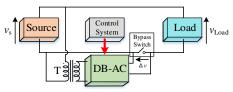

Fig. 24 The proposed DFVC.

From the above analysis, it can be seen that the DB-AC has the performance of output bipolar voltage. Therefore, as shown in Fig. 24, the DB-AC can be fully used as DFVC to address voltage swell and sag problems appeared in the power grid. And as the swell or sag of the power grid voltage appear, the bypass switch is turned off, the DB-AC operates in DFVC mode and provides compensation voltage for the system. Conversely, when the grid voltage is nominal voltage, the bypass switch is connected and the DFVC is in the bypass mode. As can be seen from Fig. 24, the relationship between the supply voltage  $v_s$ , load voltage  $v_{Load}$  and the compensation voltage  $\Delta v$  provided by DFVC is as follows.

$$v_R = v_S - v_{AC} \tag{28}$$

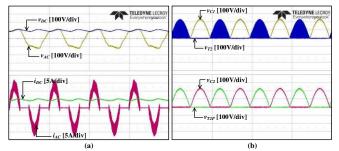

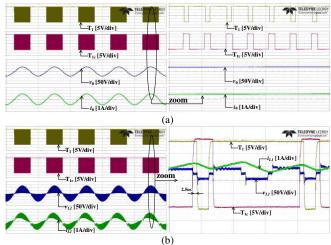

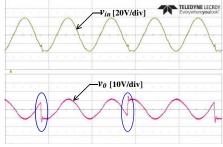

In order to verify the application of the proposed DB-AC as DFVC, two experiments were successfully implemented in the conditions of grid voltage swell and sag respectively, and the waveforms of experimental results are shown in Fig. 25 and Fig. 26. Due to the limitation of laboratory conditions, the standard voltage is set to 110Vrms. And that is to say, the load voltage  $v_{Load}$  should be maintained at 110Vrms by DFVC.

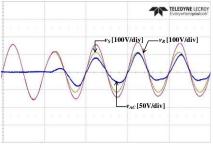

Voltage sag: Fig. 25 shows the experimental waveforms of the DFVC under voltage sag condition,  $v_s$ =60Vrms< $v_{std}$ =110 Vrms, and the grid voltage experiences approximately 45.45% voltage sag. At this point, the DFVC should be provided a 50V compensation voltage to maintain the load voltage  $v_{Load}$  at 110Vrms, and the proposed DB-AC works in non-inverting operation with the  $v_{AC}$  and  $v_S$  are in-phase.

Voltage swell: Fig. 26 shows the experimental waveforms of the DFVC under voltage swell condition,  $v_s$ =160Vrms> $v_{std}$ =110Vrms, and the grid voltage experiences approximately 45.45% voltage swell. In order to adjust the load voltage  $v_{Load}$  to the nominal voltage 110V, the DFVC should be provided a inverted 50V compensation voltage. As can be seen from the Fig .26, the supply voltage  $v_s$  and compensation voltage  $\Delta v$  are out-of-phase.

In order to prove more fully that the proposed converter can solve both voltage sag and swell problems. The waveforms of two dynamic experimental results are shown in Figs. 27 and 28. The experimental results show that the proposed converter can solve the voltage fluctuation problem well when it is used as DFVC. In addition, in order to prove the ability of the DB-AC to output bipolar voltage, the experimental results of DB-AC with transition from inverting to non-inverting operation shown in Fig. 29 is given.

In summary, when voltage swell or sag occur in the grid, the DFVC based on the proposed DB-AC works well, and it can provide a bipolar voltage.

Fig. 25 Experimental waveforms of the DB-AC used as DFVC ( $v_S$  is grid voltage,  $U_R$  represents load voltage,  $v_{AC}$  is the output voltage of the DB-AC).

Fig. 26 Experimental waveforms of the DB-AC used as DFVC ( $v_S$  is grid voltage,  $v_R$  represents load voltage,  $v_{AC}$  is the output voltage of the DB-AC).

Fig. 27 Dynamic results for voltage sag mitigation ( $v_s$  is grid voltage,  $v_R$  represents load voltage,  $v_{AC}$  is the output voltage of the DB-AC).

Fig. 28 Dynamic results for voltage swell mitigation ( $v_S$  is grid voltage,  $v_R$  represents load voltage,  $v_{AC}$  is the output voltage of the DB-AC).

Fig. 29 The experimental results of DB-AC with transition from inverting to non-inverting operation.

#### VI. CONCLUSION

In this paper, a novel bipolar-type ac-ac converter topology based on dual-buck PWM ac choppers is proposed. It can obtain bipolar output voltage gain, that is, an in-phase or out-of-phase output voltage with the input voltage can be obtained. Therefore, it has capability to compensate both voltage sag and swell when used in a DFVC. Especially, an advantage is that the proposed ac-ac converter has the same buck/boost operation process for non-inverting and inverting modes, which ensures the continuously average current supply to the low-voltage output side without a high-value capacitor to support power. Additionally, due to the common sharing ground of the input and output, the feature that output can reverse or maintain phase angle with input is supported well. By adopting two-level non-differential dual-buck ac chopper legs with two separation inductors, the proposed converter overcomes the commutation problem and improves the utilization of the duty cycles due to there is no dead-time. Partial free-wheeling diodes can be chosen independently with fast reverse recovery features to minimize switching loss. Finally, a detailed analysis of the proposed converter and DFVC has been presented and validated by experiment.

#### REFERENCES

- [1] J. Kaniewski, P. Szczesniak, M. Jarnut and G. Benysek, "Hybrid Voltage Sag/Swell Compensators: A Review of Hybrid AC/AC Converters," *IEEE Industrial Electronics Magazine*, vol. 9, no. 4, pp. 37-48, Dec. 2015.

- [2] A. Honrubia-Escribano, E. Gómez-Lázaro, A. Molina-García, and J. A. Fuentes, "Influence of voltage dips on industrial equipment: Analysis and assessment," *Electr. Power Energy Syst.*, vol. 41, no. 41, pp. 87-95, 2012.

- [3] E. Babaei and M. F. Kangarlu, "Sensitive load voltage compensation against voltage sags/swells and harmonics in the grid voltage and limit downstream fault currents using DVR," *Electric Power Syst. Res.*, vol. 83, pp. 80–90, 2012.

- [4] J. Kaniewski, Z. Fedyczak, and G. Benysek, "AC voltage sag/swell compensator based on three-phase hybrid transformer with buck-boost matrix-reactance chopper," *IEEE Trans. Ind. Electron.*, vol. 61, pp. 3835– 3846, Aug. 2014.

- [5] P. M. Garcia-Vite, F. Mancilla-David, and J. M. Ramirez, "Per-sequence vector-switching matrix converter modules for voltage regulation," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5411–5421, Dec. 2013.

- [6] J. C. C. Rodríguez, J. V. López, C. C. Olay, S. M. Fernández, R. V. García, and S. M. García, "Dual-tap chopping stabilizer with subcyclic AC soft switching," *IEEE Trans. Ind. Electron.*, vol. 57, no. 9, pp. 3060–3074, Sept. 2010.

- [7] S. Subramanian and M. K. Mishra, "Interphase AC-AC topology for voltage sag supporter," *IEEE Trans. Power Electron.*, vol. 25, no. 2, pp. 514–518, Feb. 2010.

- [8] E. Lefeuvre, T. Meyenard, and P. Viarouge, "Fast line voltage conditioners using a PWM AC chopper topology," in *Proc. European Conference on Power Electronics and Applications (EPE)*, 2001, pp. P.1-P.9, Graz, 2001

- [9] P. Kanjiyga, B. Singh, A. Chandra, and K. AllHaddad, "SRF theory revisited to control self-supported dynamic voltage restorer (DVR) for unbalanced and nonlinear loads," *IEEE Trans. Ind. Appl.*, vol. 49, no. 5, Sept./Oct. 2013.

- [10] A. Shabanpour and A. Reza Seifi, "A dynamic voltage restorer based on matrix converter with fuzzy controller," Adv. Electric Electron. Eng., vol. 10, no. 3, pp. 143–151, Sept. 2012.

- [11] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Compensation of voltage disturbances in distribution systems using single-phase dynamic voltage restorer," *Electric Power Syst. Res.*, vol. 80, pp. 1413–1420, 2010.

- [12] J. M. Lozano, J. M. Ramirez, and R. E. Correa, "A novel dynamic voltage restorer based on matrix converters," in *Proc. Modern Electric Power Systems (MEPS* 2010), Poland, Sept. 2010, pp. 20–22.

- [13] C. Liu, et al., "Novel Bipolar-Type Direct AC-AC Converter Topology based on Non-Differential AC Choppers," *IEEE Trans. Power Electron.*, doi: 10.1109/TPEL.2018.2890581.

- [14] S. Kim, H. Kim and H. Cha, "Dynamic Voltage Restorer Using Switching Cell Structured Multilevel AC–AC Converter," *IEEE Trans. Power Electron.*, vol. 32, no. 11, pp. 8406-8418, Nov. 2017.

- [15] S. Jothibasu and M. K. Mishra, "An improved direct AC–AC converter for voltage sag mitigation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 21–29, Jan. 2015.

- [16] S. Jothibasu and M. K. Mishra, "A control scheme for storageless DVR based on characterization of voltage sags," *IEEE Trans. Power Del.*, vol. 29, no. 5, pp. 2261–2269, Oct. 2014.

- [17] L. Li, J. Yang, and Q. Zhong, "Novel family of single-stage three-level AC choppers," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 504–511, Feb. 2011

- [18] A. A. Khan, H. Cha, and H. F. Ahmed, "An improved single-phase direct PWM inverting buck-boost AC-AC converter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 9, pp. 5384–5393, Sep. 2016.

- [19] H. Shin, H. Cha, H. Kim and D. Yoo, "Novel Single-Phase PWM AC–AC Converters Solving Commutation Problem Using Switching Cell Structure and Coupled Inductor," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2137-2147, April 2015.

- [20] A. A. Khan, H. Cha and H. Kim, "Magnetic Integration of Discrete-Coupled Inductors in Single-Phase Direct PWM AC–AC Converters," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2129-2138, March 2016.

- [21] A. A. Khan, H. Cha, H. F. Ahmed and H. Kim, "Elimination of Filter Inductor in Switching Cell AC–AC Converters Using Magnetic Integration," *IEEE Trans. Power Electron.*, vol. 31, no. 9, pp. 6317-6326, Sept. 2016.

- [22] Nan J, Kang D, Cui G. Research on Dynamic Voltage Restorer Based on Direct AC/AC Power Conversion," Transactions of China Electro technical Society., 2015, 30(11):71-77.

- [23] H. Liu, J. Wang and O. Kiselychnyk, "Mathematical Modeling and Control of a Cost Effective AC Voltage Stabilizer," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 8007-8016, Nov. 2016.

- [24] F. Xu Peng, Q. Zhao Ming, and P. Fang Zheng, "Single-phase Z-source PWM AC-AC converters," *IEEE Power Electron. Lett.*, vol. 3, no. 4, pp. 121–124, Dec. 2005.

- [25] Y. Tang, S. Xie, and C. Zhang, "Z-source AC–AC converters solving commutation problem," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2146–2154, Nov. 2007.

- [26] P. Li and Y. Hu, "Unified Non-Inverting and Inverting PWM AC–AC Converter With Versatile Modes of Operation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 2, pp. 1137-1147, Feb. 2017.

- [27] P. Li, Y. Wang, G. Philip Adam, D. Holliday, and B. W. Williams, "Three-phase AC–AC hexagonal chopper system with heterodyne modulation for power flow control enhancement," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5508–5521, Oct. 2015.

- [28] U. A. Khan, A. A. Khan, H. Cha, H. Kim, J. Kim and J. Baek, "Dual-Buck AC–AC Converter With Inverting and Non-Inverting Operations," *IEEE Trans. Power Electron.*, vol. 33, no. 11, pp. 9432-9443, Nov. 2018.

- [29] H. F. Ahmed, H. Cha, A. A. Khan and H. Kim, "A Novel Buck–Boost AC–AC Converter With Both Inverting and Non-inverting Operations and Without Commutation Problem," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4241-4251, June 2016.

- [30] A. A. Khan, H. Cha, J. Baek, J. Kim and J. Cho, "Cascaded Dual-Buck AC–AC Converter With Reduced Number of Inductors," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7509-7520, Oct. 2017.

- [31] A. A. Khan, H. Cha and H. Kim, "Three-Phase Three-Limb Coupled Inductor for Three-Phase Direct PWM AC–AC Converters Solving Commutation Problem," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 1, pp. 189-201, Jan. 2016.

- [32] A. A. Khan, H. Cha and H. F. Ahmed, "A New Reliable Three-Phase Buck-Boost AC–AC Converter," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 2, pp. 1000-1010, Feb. 2018.

- [33] H. F. Ahmed, H. Cha, A. A. Khan and H. Kim, "A Highly Reliable Single-Phase High-Frequency Isolated Double Step-Down AC–AC Converter With Both Noninverting and Inverting Operations," *IEEE Transactions on Industry Applications*, vol. 52, no. 6, pp. 4878-4887, Nov.-Dec. 2016.

- [34] H. F. Ahmed, H. Cha, A. A. Khan and H. Kim, "A Family of High-Frequency Isolated Single-Phase Z-Source AC–AC Converters

With Safe-Commutation Strategy," *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7522-7533, Nov. 2016.

[35] A. A. Khan, H. Cha and H. F. Ahmed, "High-Efficiency Single-Phase AC– AC Converters Without Commutation Problem", *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5655-5665, Aug. 2016.

Yibo Wang (S'19) was born in Shandong Province, China, in 1989. He received the B.S. and M.S. degrees in electrical engineering from Northeast Electric Power University, Jilin, China, in 2010 and 2016, respectively. He is currently working toward the Ph.D. degree in electrical engineering at Northeast Electric Power University, Jilin, China. His current

research interests include renewable energy integration into power networks, power systems and power quality.

Peng Wang was born in Anhui Province, China, in 1994. He received the B.S. and M.S. degrees from Northeast Electric Power University, Jilin, China, in 2016 and 2020. Currently, he is an engineer of State Grid Jurong Power Supply Company of Jiangsu Electric Power Company. His current research interests include direct PWM ac-ac converters, power quality, and the application of high-power electronic

conversion technology in renewable energy generation.

Guowei Cai was born in Jilin Province, China, in 1968. He received the B.S. and M.S. degrees from Northeast Electric Power University, Jilin, China, in 1990 and 1993, respectively, and the Ph.D. degree from Harbin Institute of Technology, Harbin, China, in 1999, all in electrical engineering. Since 2004, he has been a Professor in the school of Electrical Engineering, Northeast Electric Power

University. His current research interests include power system transient stability analysis, and smart grid with renewable power generation.

Chuang Liu (M'12) received the M.S. degree from Northeast Electric Power University, Jilin, China, in 2009, and the Ph.D. degree from Harbin Institute of Technology, Harbin, China, in 2013, both in electrical engineering. From 2010 to 2012, he was with the Future Energy Electronics Center, Virginia Polytechnic Institute and State university, Blacksburg, VA, USA, as a Visiting Ph.D. Student,

supported by the Chinese Scholarship Council.

In 2013, he became an Associate Professor in the school of Electrical Engineering, Northeast Electric Power University, where, since 2016, he has been a Professor. His research interests include power-electronics-based on ac and dc transformers for future hybrid ac-dc power grids, flexible operation and control of power grid based on ac-ac transformation, and power-electronics-based power system stability analysis and control.

Dongbo Guo was born in Shandong Province, China, in 1990. He received the B.S. degree from Northeast Electric Power University, Jilin, China, in 2016. He is currently working toward the M.S. degree in electrical engineering at Northeast Electric Power University, Jilin, China. His current research interests include flexible operation and control of power grid based on ac-ac conversion, direct

PWM ac-ac converters, and the application of high power electronic conversion technology in smart grid.

Hanwen Zhang was born in Jilin Province, China, in 1994. He received the B.S. degree from Northeast Electric Power University, Jilin, China, in 2017. He is currently working toward the M.S. degree in electrical engineering at Northeast Electric Power University, Jilin, China. His current research interests include power quality control in distribution

network, direct PWM ac-ac converters, and energy efficient intergrated conversion technology.

Bingda Zhu was born in Henan Province, China, in 1996. He received the B.S. degree from Northeast Electric Power University, Jilin, China, in 2018. He is currently working toward the M.S. and Ph.D degrees in electrical engineering at Northeast Electric Power University, Jilin, China. His current research interests include direct PWM ac-ac converters, control strategy, power quality

optimization in distribution network, and the application of high-power electronic conversion technology in smart grid.

Gen Li (M'18) received the B.Eng. degree in Electrical Engineering and its Automation from Northeast Electric Power University, Jilin, China, in 2011, the M.Sc. degree in Power Engineering from Nanyang Technological University, Singapore, in 2013 and the Ph.D. degree in Electrical Engineering from Cardiff University, Cardiff, U.K., in 2018.

From 2013 to 2016, he was a Marie Curie Early Stage Research Fellow funded by the European Union's MEDOW project. He has been a Visiting Researcher at China Electric Power Research Institute and Global Energy Interconnection Research Institute, Beijing, China, at Elia, Brussels, Belgium and at Toshiba International (Europe), London, U.K. He has been a Research Associate at the School of Engineering, Cardiff University since 2017. His research interests include control and protection of HVDC and MVDC technologies, power electronics, reliability modelling and evaluation of power electronics systems.