# Improved Grid Impedance Compensation for Phase-Locked Loop to Stabilize the Very-Weak-Grid Connection of VSIs

Chuanyue Li<sup>®</sup>, *Member, IEEE*, Wei Liu<sup>®</sup>, *Graduate Student Member, IEEE*, Jun Liang<sup>®</sup>, *Senior Member, IEEE*, Xiaolin Ding, and Liana M. Cipcigan, *Member, IEEE*

Abstract-Voltage source inverters (VSIs) with vector control based on phase-locked loop (PLL) suffer instability when connecting to a very weak AC grid (short circuit ratio (SCR)<1.3). The conventional inductive grid impedance compensation for the PLL by virtually reducing the grid impedance can stabilize this connection. However, the analysis in this paper indicates that its stabilization effectiveness is sensitive to grid impedance variance and, indeed, overcompensation causes the PLL instability. Therefore, in this paper, an improved grid impedance compensation for the PLL is proposed to achieve the same stabilization for very-weak-grid connection and possess a good tolerance of grid impedance variance and overcompensation. A comprehensive small-signal model of the VSI using the proposed PLL's grid impedance compensation is derived for stability analysis and parameter design. The time-domain simulation for this VSI is built to validate the stability analysis. Comparison studies for both proposed and conventional PLL's grid impedance compensation are conducted including the stability effectiveness, VSI performance and grid impedance variance.

*Index Terms*—PLL-based inverters, vector control, weak grids, stability analysis.

### I. INTRODUCTION

OLTAGE source inverters (VSIs) with PLL-based vector control are widely used for renewable energy integration. Those inverters locating far from the AC grid risk instability due to weak-grid connection [1], which is defined as short circuit ratio (SCR)<3 [2]. Oscillations caused by wind farm inverters connecting to weak grids have been observed in many regional

Manuscript received 6 February 2021; revised 11 June 2021 and 15 September 2021; accepted 18 December 2021. Date of publication 4 January 2022; date of current version 23 September 2022. This work was supported supported in part by the European Commission's Horizon 2020 Research and Innovation Programme (Marie Skodowska-Curie Actions) through the Project "Innovative Tools for Offshore Wind and DC Grids (InnoDC)," under Grant 765585, in part by U.K. National Grid Electricity Transmission, under Grant NIA\_NGTO044, and in part by the EPSRC "Sustainable urban power supply through intelligent control and enhanced restoration of AC/DC networks," under Grant EP/T021985/1. Paper no. TPWRD-00224-2021. (*Corresponding author: Wei Liu.*)

Chuanyue Li, Wei Liu, Jun Liang, and Liana M. Cipcigan are with the School of Engineering, Cardiff University, CF24 3AA Cardiff, U.K. (e-mail: chuanyue.li@outlook.com; liuw28@cardiff.ac.uk; liangj1@cardiff.ac.uk; CipciganLM@cardiff.ac.uk).

Xiaolin Ding is with National Grid, CV34 6DA Warwick, U.K. (e-mail: xiaolin.ding@nationalgrid.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPWRD.2021.3140024.

Digital Object Identifier 10.1109/TPWRD.2021.3140024

grids [3], such as Texa 4 Hz oscillations, West China 30 Hz oscillations and U.K. 8-9 Hz oscillations. This oscillation can further induce the torsional interaction with synchronization generators [4].

After extensive analysis for this weak-grid connection, it is found that PLL is critical to this VSI instability [5], especially interacting with high grid inductance. Besides, highly-coupled outer loop control [6] and fast-response inner loop control [7] could also cause the instability.

For stable connection to a mildly weak grid (SCR $\in$  [2 3]), many additional stabilization controls are added in the vector control. PLL dynamic compensation is an effective way, by applying in outer loop [8], inner loop [9] and voltage feedforward [10]. Reshaping the VSI impedance via a *q*-axis compensation can avoid the negative resistance behaviour with weak grid connection [11]. Based on the *LC* filter, a virtual inductance [12] is added in the vector control to emulate a *LCL* filter, which can also stabilize the weak-grid connection. However, for connecting to a weak grid such as SCR<2, these stabilization controls are not further validated.

Moreover, it is found that the VSI suffers a critical stability issue when connecting to a very weak grid (SCR<1.3) with rated power injection [13]. Even a great tuning effort is made for the PLL-based vector control, the rated power injection cannot be stabilized and the maximum injected power at SCR = 1 is around 0.7 p.u. [14].

Therefore, to stabilize the rated power injection when connecting to a very weak grid, many solutions have been proposed for the VSI, which can be categorized into two groups: gridforming control and improved PLL-based control.

Gird-forming control is proposed based on the power synchronization mechanism to effectively support a very weak grid with voltage and rated power. This Power synchronization mechanism can implemented via P [15] droop control or  $\omega - P$ droop control with the virtual swing equation of a synchronous generator [16]. Its ability to connect to a very weak grid is further enhanced via robust control design [17] and the transient stability analysis [18]. Although the power synchronization-controlled VSI works well with a weak grid, voltage conflict presents if a strong grid is connected [19], which may cause the VSI instability and sub-synchronous resonance [20].

PLL-based vector control can be improved via adding additional compensation to allow the very weak grid connection with

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

rated power injection. Outer loop compensation is an effective way to achieve the desired connection, many methods have been proposed including outer loop decoupling [6], AC voltage compensation [21]. Power compensation [22] by suppressing voltage impact on outer power loop can also effectively stabilize the very weak grid connection.

However, the above-mentioned methods are designed by using the small-signal dynamics of PLL, which increases the control complexity significantly.

The control complexity and stabilization effectiveness are well balanced by the grid impedance compensation in the PLL [23] [24] for the very-weak-grid connection. Only virtual negative impedance is added within the PLL to equivalently advance the synchronized point and strengthen the grid stiffness. Although [24] claims that virtually reducing the grid impedance with negative resistance and inductance helps to stabilize the VSI, its compensation is mainly inductive which  $R : Z_L = 1 : 5.6$ . More specifically, [23] only using inductive compensation stabilizes the VSI, which proves that the inductive compensation dominates the stabilization effectiveness.

However, in this paper, it is revealed that this inductive compensation highly relies on the information of grid impedance, leading to low tolerance of the grid impedance variance. Furthermore, if the overcompensation occurs because of grid impedance variance or being overestimated, the PLL is likely to lose stability.

In this paper, an improved grid impedance compensation for the PLL is proposed for avoiding above-mentioned drawbacks and stabilizing the very-weak-grid connection (SCR<1.3). Differing from the conventional inductive grid impedance compensation by virtually reducing the grid inductance [23], the proposed grid impedance compensation adopts a different mechanism of virtually increasing the grid resistance. Comparing to the conventional PLL's inductive grid impedance compensation, this proposed grid impedance compensation enables good tolerance of grid impedance variance and avoids the instability caused by the overcompensation.

The paper is outlined as follows: Section II introduces the instability mechanism caused by conventional PLL's inductive grid impedance compensation, and presents the feasibility of proposed PLL's grid impedance compensation via interaction analysis between the VSI and a weak AC grid. Section III presents the design of proposed grid impedance compensation for PLL within the VSI's control system, and a small-signal model of this PLL-based vector-controlled VSI using the proposed compensation is derived for parameter design. Section IV demonstrate comprehensive comparison studies between the conventional and proposed PLL's grid impedance compensation including stabilization effectiveness, overcompensation impact, VSI performance and grid impedance variance.

## II. MOTIVATION OF IMPROVING PLL'S GRID IMPEDANCE COMPENSATION

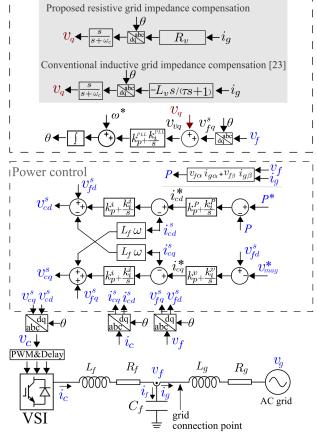

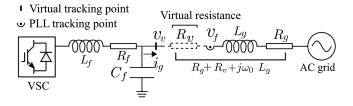

The studied VSI with power control based on the PLL is presented in Fig. 1. Besides the active power control at the Phase-locked loop with grid impedance compensation

Fig. 1. VSI system: a PLL-based vector-controlled VSI connecting to an AC grid.

outer loop, the voltage magnitude of the grid connection point is regulated at the q axis. Current control is necessarily placed in the inner loop to avoid overcurrent. The grid compensation is added in the PLL to adjust grid impedance value equivalently.

Conventional PLL's inductive grid impedance compensation [23] mainly uses virtual negative inductance to equivalently reduce the grid impedance, as shown in Fig. 1. It should be noted that conventional PLL's inductive grid impedance compensation via virtual inductance is a pure derivate, which may cause a significant impact on PLL when  $i_g$  varies. Therefore, to avoid this impact,  $-L_v s$  is added as  $-L_v s/(\tau s + 1)$  in the following analysis based on the guidance in [23], where  $\tau = 0.01$  ms.

In this section, the motivation of improving grid impedance compensation for the PLL is presented. Firstly, the mechanism of instability caused by the conventional inductive grid impedance compensation is explained and validated in time domain. Secondly, the impedance stability analysis method used in this paper is introduced. Thirdly, the impedance interaction between the VSI and the AC grid is assessed to reveal the stability mechanism by increasing the grid resistance, which is applied for the proposed PLL's grid impedance compensation in the next section.

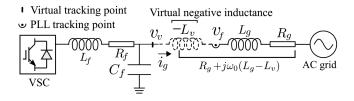

Fig. 2. Equivalent circuit using conventional inductive grid impedance compensation.

## A. Instability Caused by Conventional Inductive Grid Impedance Compensation

Conventional inductive grid impedance compensation for PLL was introduced by [23], which can effectively allow the very weak grid connection with rated power injection for VSIs. An equivalent circuit of the VSI system is presented in Fig. 2. By inserting the virtual negative inductance between the tracking point and AC grid, the tracking voltage becomes stiff as the grid impedance is reduced. However, if excessive compensation occurs, this negative inductance compensation will introduce right-plane poles in the PLL, which leads to the PLL instability. This instability mechanism is explained below.

After applying the grid impedance compensation, the tracking voltage becomes  $v_v$  as shown in Fig. 2, and the tracking voltage after abc - dq transformation for the PLL is presented below as the small-signal expression:

$$\widetilde{v}_{vq}^s = \widetilde{v}_{vq} - V_{vd}\widetilde{\theta} \tag{1}$$

where notation  $\sim$  means the small-signal disturbance, capital letter means the steady-state value, such as  $V_{vd}$ , superscript s represent the value after the abc - dq transformation.

$V_{vd}$  is calculated as below:

$$V_{vd} = V_{fd} + L_v \omega_0 \underbrace{I_{gq}}_{I_{qq} < 0} \tag{2}$$

Based on (1), the relation of PLL presented in Fig. 1 is summarized below:

$$\frac{1}{s} \times \left( k_p^{PLL} + \frac{k_i^{PLL}}{s} \right) \times \left( \tilde{v}_{vq} - V_{vd} \tilde{\theta} \right) = \tilde{\theta}$$

(3)

Rearranging (3) yields:

$$\frac{k_p^{PLL}s + k_i^{PLL}}{s^2 + V_{vd}k_p^{PLL}s + V_{vd}k_i^{PLL}}\widetilde{v}_{vq} = \widetilde{\theta}$$

(4)

Compensation ratio for virtual negative inductance is defined as below:

$$L_v = \alpha L_q \tag{5}$$

Excessive compensation, where  $\alpha > 1$ , may result in  $V_{vd} < 0$ in (2). Therefore, positive poles appear in  $1/(s^2 + V_{vd}k_p^{PLL}s + V_{vd}k_i^{PLL})$ , which cause the PLL instability.

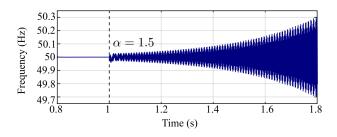

A time-domain test for the PLL with negative impedance grid compensation is presented by giving an excessive compensation ratio  $\alpha = 1.5$  with SCR = 2. The test case is based on the VSI system in Fig. 1, where power control is not included. Its

TABLE I Parameters of the VSI System

| Symbol                               | Parameter                                                    | Value                        |

|--------------------------------------|--------------------------------------------------------------|------------------------------|

|                                      | Circuit parameters of VSI system                             |                              |

| S                                    | Power rating                                                 | 1000 MVA                     |

| $V_g$                                | rms l-l AC grid voltage                                      | 320 kV                       |

| $L_{f}$                              | reactor inductance                                           | 0.15 p.u.                    |

| $R_f$                                | reactor resistance                                           | 0.05 p.u.                    |

| $C_f$                                | filter capacitance                                           | 0.067 p.u.                   |

| $v_{mag}^*$                          | d-axis voltage reference                                     | 1 p.u.                       |

| $P^*$                                | active power reference                                       | 1 p.u.                       |

| $T_{del}$                            | control delay and dead time of PWM                           | 5 µs                         |

| $\omega_0$                           | base frequency                                               | $2 \pi \times 50$            |

| SCR                                  | short-circuit ratio                                          | $1 (X_{L_g}:R_g=10)$         |

| $Z_g \left( R_g + j X_{L_g} \right)$ | grid impedance                                               | 0.01 + 0.995 j p.u.          |

|                                      | Power control                                                |                              |

| $\omega_c^i$                         | cut-off frequency of closed-loop current control             | 800 rad/s                    |

| $k_p^i \& k_i^i$                     | PI for current control                                       | 0.382&4                      |

| $k_p^P \& k_i^P$                     | PI for power control                                         | $0.1k_{p}^{i}\&0.1k_{i}^{i}$ |

| $k_p^v \& k_i^v$                     | PI for voltage control                                       | $0.1k_{p}^{i}\&0.1k_{i}^{i}$ |

|                                      | PLL and grid impedance compensation                          |                              |

| $\omega_c^{PLL}$                     | phase-locked loop cut-off frequency                          | 210 rad/s                    |

| $k_p^{PLL} \& k_i^{PLL}$             | PI for PLL                                                   | 420&44100                    |

| $\omega_c$                           | cut-off frequency of high-pass filter                        | 1000 rad/s                   |

| α                                    | gain of virtual inductance                                   | 0.8                          |

| β                                    | gain of virtual resistance and high-pass filter              | 0.1                          |

| $\omega_s$                           | cut-off frequency of virtual resistance and high-pass filter | 6.28 rad/s                   |

| $L_v$                                | inserted negative virtual inductance                         | $\alpha L_g$                 |

| $R_v$                                | inserted virtual resistance                                  | < 15                         |

${}^{0}\omega_{c}^{i}$  &  $\omega_{c}^{PLL}$  are calculated via their PI parameters based on [30] [31]

Fig. 3. Frequency tracked by the PLL with conventional inductive grid impedance compensation with SCR = 2.

Fig. 4. Equivalent circuit of the VSI system for stability analysis.

parameters are given in Table I. As shown in Fig. 3, when  $\alpha$  is changed to 1.5, the frequency tracked by PLL loses stability.

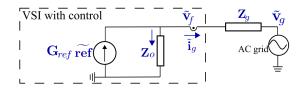

### B. Stability Analysis Method

To avoid the above-mentioned instability caused by the conventional inductive grid impedance compensation, the impedance stability analysis is introduced for further interaction analysis between the VSI and the ac grid. For impedance stability analysis, a Norton equivalent circuit (Fig. 4) of the VSI system needs to be derived [25] for assessing the stability.  $\mathbf{Z}_o$  is the total small-signal impedance of the VSI including the power control (inner and outer loops), PLL, abc - dq transformation, delay of PWM and control system, and LC filter, as shown in Fig. 1.  $\mathbf{Z}_g$  is

480

320

160 0

-160

-320

-480

-600

-400

200

Real (s<sup>-1</sup>)

(a)

Imaginary (Hz)

inductive

90°, 75°

0

-400

60° 45° 30°

0000000000

Real (s<sup>-1</sup>) (b)

200

resistive

0

$\mathbf{P} =$

0 100

$15^{\circ}$

Fig. 5. Impedance interaction analysis of the VSI with various grid impedance. (a) Increasing SCR. (b) Increasing the resistance at SCR = 1.

grid impedance known from  $R_g$  and  $L_g$ . The following relation is found based on Fig. 4:

$$(\mathbf{Z}_o + \mathbf{Z}_g)\widetilde{\mathbf{i}}_g = \mathbf{Z}_o \mathbf{G}_{ref} \widetilde{\mathbf{ref}} - \widetilde{\mathbf{v}}_g \tag{6}$$

Rearranging (6) with  $\mathbf{Y}_o$  yields:

$$\widetilde{\mathbf{i}}_g = (\mathbf{I} + \mathbf{Y}_o \mathbf{Z}_g)^{-1} (\mathbf{G}_{ref} \widetilde{\mathbf{ref}} - \mathbf{Y}_o \widetilde{\mathbf{v}}_g)$$

(7)

where  $\mathbf{Y}_o$  is the impedance of this VSI and  $\mathbf{Y}_o \mathbf{Z}_o = \mathbf{I}$ , the impedance ratio matrix is  $(\mathbf{I} + \mathbf{Y}_o \mathbf{Z}_g)^{-1}$ , and bold capital letter represents the matrix.

This impedance ratio is derived as a  $2 \times 2$  matrix in dq-frame, which is the key factor [25][26] to analyze the stability of VSI system.

Based on this  $2 \times 2$  impedance ratio matrix, the determinantbased method [27][28] is applied for stability analysis via only one pole map, as shown below:

$$(\mathbf{I} + \mathbf{Y}_o \mathbf{Z}_g)^{-1} = \operatorname{adj}(\mathbf{I} + \mathbf{Y}_o \mathbf{Z}_g) \underbrace{\operatorname{det}((\mathbf{I} + \mathbf{Y}_o \mathbf{Z}_g)^{-1})}_{\text{factor for stability analysis}}$$

(8)

## C. Impedance Interaction Analysis Between the VSI and a Weak AC Grid

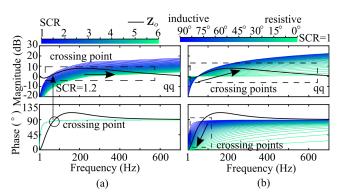

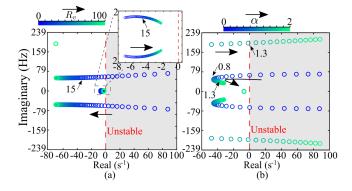

The small-signal impedance of PLL-based vector-controlled VSI is well derived in [5], which will not be presented in this paper. For a  $2 \times 2$  VSI impedance  $\mathbf{Z}_{o}$  in dq frame, it is reported that its qq element is critical for the impedance interaction analysis [5]. Therefore, only the qq element is presented. The bode plot of  $\mathbf{Z}_o$ 's qq element in terms of various SCR are shown in Fig. 5(a). The grid impedance is inductive with  $X_{L_q}$ : Rg =10:1. When the SCR is low, their magnitude crossing points are close to their phase crossing points, which makes the qq part of  $(\mathbf{Z}_o - \mathbf{Z}_g)$  close to 0. This indicates the VSI tends to be unstable. Increasing SCR pushes the magnitude crossing points far from their phase crossing points. Thus, the ultra-small qq element of  $(\mathbf{Z}_{o} - \mathbf{Z}_{a})$  is avoided. It is indicated that the VSI gets more stable with high SCRs. The pole map based on determinant-based stability analysis method also proves the findings, as shown in Fig. 6(a). The pole goes into the left plane and move far from x = 0 when increasing SCR.

The bode plot of  $\mathbf{Z}_o$ 's qq element with increasing grid resistance at SCR = 1 is shown in Fig. 5(b). When the grid impedance

0100-600

Fig. 7. Equivalent circuit of the proposed grid impedance compensation.

is highly inductive, the phase of  $\mathbf{Z}_o$  and the grid impedance are close at their magnitude crossing point, which results in instability, as shown in Fig. 6(a). With increasing grid resistance, their phases are significantly different at the magnitude crossing points. It is indicated that the VSI is more stable when the grid impedance is mainly resistive. The pole map of the VSI system also proves the finding, as shown in Fig. 6(b). With increasing resistance, the pole goes into the left pane and moves far from x = 0.

In sum, if a weak AC grid is connected to a PLL-based vectorcontrolled VSI, enhancing the grid resistance will effectively stabilize the connection.

## III. DESIGN OF PROPOSED GRID IMPEDANCE COMPENSATION FOR PLL

The previous analysis shows that grid resistance enhancement stabilizes the very-weak-grid connection (SCR=1) with rated power injection. Therefore, differing from the conventional inductive grid impedance compensation by virtually reducing the grid impedance, the proposed grid impedance compensation adopts a different mechanism of virtually increasing the grid resistance, as shown in Fig. 1. The equivalent circuit of the proposed grid impedance compensation is shown in Fig. 7, a virtual resistance is equivalently applied between the tracking point and the AC grid. The total equivalent grid resistance is increased as  $R_v + R_g$ . Comparing to conventional inductive grid impedance compensation, the virtual negative inductance is replaced, which avoids the instability caused by the overcompensation using virtual negative inductance.

Comparing to the original PLL, an additional  $v_q$  is added in the PLL for this compensation. At steady state, it is mandatory for a VSI to synchronize with the grid, which requires  $v_f$ being accurately tracked. Therefore,  $v_{vq} = v_{fq}$  is requested at steady state even the virtual resistance is applied. To avoid this steady-state error caused by  $v_q$ , a high-pass filter  $(s/(s + \omega_c))$  is added for the proposed resistive grid impedance compensation, as shown in Fig. 1.

## A. Small-Signal Impedance Model of Proposed Grid Impedance Compensation

The small-signal impedance model of PLL-based vectorcontrolled VSI using resistance grid compensation is derived for its parameter design and stability analysis. This impedance model represents the full VSI system shown in Fig. 1, which includes resistance grid compensation, power control (inner and outer loops), PLL, abc - dq transformation, delay of PWM and control system, and LC filter.

For the dq impedance derivation, the three-phase system is presented as the dq form, such as  $\mathbf{v}_c$ ,  $\mathbf{v}_f$ ,  $\mathbf{i}_c$ . The bold parameters stand for their dq matrix parameters such as  $\widetilde{\mathbf{v}_f} = \begin{bmatrix} \widetilde{v}_{fq} \\ \widetilde{v}_{fq} \end{bmatrix}$ . Notation  $\widetilde{}$  means the small-signal disturbance. The dq control is based on the synchronized dq frame, their parameters after abc - dq transformation are noted as  $\mathbf{v}_c^s \mathbf{v}_f^s \mathbf{i}_c^s$ . The dq-formed abc parameters are equal to their dq-synchronized parameters at steady state, but are different when a synchronized phase disturbance  $\widetilde{\theta}$  appears at the abc - dq transformation.

For example, abc - dq transformation of  $v_f$  is given below:

$$\begin{bmatrix} \widetilde{v}_{fd} + V_{fq}\widetilde{\theta} \\ \widetilde{v}_{fq} - V_{fd}\widetilde{\theta} \end{bmatrix} = \begin{bmatrix} \widetilde{v}_{fd}^s \\ \widetilde{v}_{fq}^s \end{bmatrix}$$

(9)

The phase disturbance  $\hat{\theta}$  comes from the PLL and grid resistance compensation, which is summarized below:

$$(\underbrace{R_v \times \frac{s}{s+\omega_c}}_{Z_v} \times \underbrace{\widetilde{i}_{gq}^s}_{\widetilde{i}_{gq}-I_{gd}\widetilde{\theta}} + \underbrace{\widetilde{v}_{fq}}_{\widetilde{v}_{fq}-V_{fd}\widetilde{\theta}}) \times \underbrace{PI_{pll}}_{k_p^{pll}+k_i^{pll}/s} \times \frac{1}{s} = \widetilde{\theta}$$

(10)

Rearranging (10) yields:

$$G_{pll}\tilde{v}_{fq} + Z_v G_{pll}\tilde{i}_{gq} = \tilde{\theta}$$

(11)

where  $G_{pll} = \frac{k_p^{pll} + k_i^{pll}/s}{s + (k_p^{pll} + k_i^{pll}/s)(V_{fd} + R_v s/(s + \omega_c)I_{gd})}$ Substituting  $\tilde{\theta}$  in (9) with (11) given:

$$\mathbf{G}_{fg}\widetilde{\mathbf{v}}_f + \mathbf{H}_{fg}\widetilde{\mathbf{i}}_g = \widetilde{\mathbf{v}}_f^s \tag{12}$$

where  $\mathbf{G}_{fg} = \begin{bmatrix} 1 & V_{fq}G_{pll} \\ 0 & 1 - V_{fd}G_{pll} \end{bmatrix}$ ,  $\mathbf{H}_{fg} = \begin{bmatrix} 0 & V_{fq}Z_vG_{pll} \\ 0 & -V_{fd}Z_vG_{pll} \end{bmatrix}$ .  $\widetilde{\mathbf{i}}^s$  and  $\widetilde{\mathbf{v}}^s$  are found based on a similar derivation:

$$\mathbf{v}_c^s$$

and  $\mathbf{v}_c^s$  are found based on a similar derivation:

$$\mathbf{i}_c + \mathbf{G}_{cf} \widetilde{\mathbf{v}}_f + \mathbf{H}_{cf} \mathbf{i}_g = \mathbf{i}_c^s \tag{13}$$

where

$$\mathbf{G}_{cf} = \begin{bmatrix} 0 & I_{cq}G_{pll} \\ 0 & -I_{cd}G_{pll} \end{bmatrix}, \mathbf{H}_{cf} = \begin{bmatrix} 0 & I_{cq}Z_vG_{pll} \\ 0 & -I_{cd}Z_vG_{pll} \end{bmatrix}.$$

$\widetilde{\mathbf{v}}_c^s + \mathbf{G}_{fc}\widetilde{\mathbf{v}}_f + \mathbf{H}_{fc}\widetilde{\mathbf{i}}_g = \widetilde{\mathbf{v}}_c$ (14)

where  $\mathbf{G}_{fc} = \begin{bmatrix} 0 & -V_{cq}G_{pll} \\ 0 & V_{cd}G_{pll} \end{bmatrix}$ ,  $\mathbf{H}_{fc} = \begin{bmatrix} 0 & -V_{cq}Z_vG_{pll} \\ 0 & V_{cd}Z_vG_{pll} \end{bmatrix}$

The linearization of the abc - dq transformation are clarified in (12) (13) (14).

The impedance of the VSI includes the control system and its LC filter. The control system, as shown in Fig. 1, is represented below:

$$\mathbf{PI}_{i}(\mathbf{PI}_{pv}(\widetilde{\mathbf{ref}} - [\widetilde{P} - \widetilde{v}_{fd}^{s}] - \widetilde{\mathbf{i}}_{c}^{s}) + \widetilde{\mathbf{v}}_{f}^{s} + \mathbf{G}_{dec}\widetilde{\mathbf{i}}_{c}^{s} = \widetilde{\mathbf{v}}_{c}^{s}$$

(15)

where  $\widetilde{\mathbf{ref}} = \begin{bmatrix} P^* \\ -v_{mag}^* \end{bmatrix}$ ,  $\mathbf{G}_{dec} = \begin{bmatrix} 0 & -L_f \omega_0 \\ L_f \omega_0 & 0 \end{bmatrix}$ ,  $\mathbf{PI}_i = \begin{bmatrix} k_p^p + k_i^p / s & 0 \\ 0 & k_p^p + k_i^i / s \end{bmatrix}$ ,  $\mathbf{PI}_{pv} = \begin{bmatrix} k_p^p + k_i^p / s & 0 \\ 0 & k_p^v + k_i^v / s \end{bmatrix}$ . The linearized active power in dq frame is shown below:

$\sim \sim \sim \sim \sim \sim$

$$P \approx 1.5 (I_{gd} \widetilde{v}_{fd} + V_{fd} i_{gd} + I_{gq} \widetilde{v}_{fq} + V_{fq} i_{gq}) \tag{16}$$

Substituting  $\widetilde{P}$  and  $\widetilde{v}_{fd}^s$  in (15) with (12) (16) yields:

$$\mathbf{PI}_{i}\mathbf{PI}_{pv}\widetilde{\mathbf{ref}} + \mathbf{G}_{rv}\widetilde{\mathbf{v}}_{f} + \mathbf{G}_{ri}\widetilde{\mathbf{i}}_{g} - \mathbf{PI}_{i}\widetilde{\mathbf{i}}_{c}^{s} + \widetilde{\mathbf{v}}_{f}^{s} + \mathbf{G}_{dec}\widetilde{\mathbf{i}}_{c}^{s} = \widetilde{\mathbf{v}}_{c}^{s}$$

(17)

where  $PI_{i} = k_{p}^{i} + k_{i}^{i}/s$ ,  $PI_{p} = k_{p}^{p} + k_{i}^{p}/s$ ,  $PI_{v} = k_{p}^{v} + k_{i}^{v}/s$ ,  $G_{vv} = \begin{bmatrix} -1.5PI_{p}I_{gd} & -1.5PI_{i}PI_{p}I_{gq} \\ PI_{i}PI_{v} & PI_{i}PI_{v}V_{fq}G_{pll} \end{bmatrix} \mathbf{G}_{ri} = \begin{bmatrix} -1.5PI_{i}PI_{p}V_{fq} \\ 0 & PI_{i}PI_{v}V_{fq}Z_{v}G_{pll} \end{bmatrix}$ .

Substituting  $\mathbf{i}_c^s$ ,  $\mathbf{\tilde{v}}_f^s$ , and  $\mathbf{\tilde{v}}_c^s$  in (17) with (12) (13) (14) and taking the time  $T_{del}$  including control delay and the dead time of PWM into account yields:

$$\mathbf{G}_{del}\{\mathbf{P}\mathbf{I}_{i}\mathbf{P}\mathbf{I}_{pv}\mathbf{ref} + [\mathbf{G}_{rv} + (\mathbf{G}_{dec} - \mathbf{P}\mathbf{I}_{i})\mathbf{G}_{cf} \\ + \mathbf{G}_{fg} + \mathbf{G}_{fc}]\widetilde{\mathbf{v}}_{f} + [\mathbf{G}_{ri} + (\mathbf{G}_{dec} - \mathbf{P}\mathbf{I}_{i})\mathbf{H}_{cf} \\ + \mathbf{H}_{fg} + \mathbf{H}_{fc}]\widetilde{\mathbf{i}}_{g} + (\mathbf{G}_{dec} - \mathbf{P}\mathbf{I}_{i})\widetilde{\mathbf{i}}_{c}\} = \widetilde{\mathbf{v}}_{c}$$

(18)

where  $\mathbf{G}_{del} = \begin{bmatrix} (1-0.5T_{del}s)/(1+0.5T_{del}s) & 0\\ 0 & (1-0.5T_{del}s)/(1+0.5T_{del}s) \end{bmatrix}$ . The voltage and current relation on the LC filter can be found

below:

$$\widetilde{\mathbf{v}}_c = \widetilde{\mathbf{v}}_f + \mathbf{Z}_f \mathbf{i}_c \tag{19}$$

$$\widetilde{\mathbf{i}}_c = \mathbf{Y}_c \widetilde{\mathbf{v}}_f + \widetilde{\mathbf{i}}_g \tag{20}$$

where  $\mathbf{Y}_{c} = \begin{bmatrix} C_{fs} & -\omega_{0}C_{f} \\ \omega_{0}C_{f} & C_{fs} \end{bmatrix}$ ,  $\mathbf{Z}_{f} = \begin{bmatrix} L_{fs} + R_{f} & -\omega_{0}L_{f} \\ \omega_{0}L_{f} & L_{fs} + R_{f} \end{bmatrix}$ . Substituting  $\mathbf{\widetilde{i}}_{c}$  in (19) with (20) yields:

$$\widetilde{\mathbf{v}}_c = \widetilde{\mathbf{v}}_f + \mathbf{Z}_f \mathbf{Y}_c \widetilde{\mathbf{v}}_f + \mathbf{Z}_f \widetilde{\mathbf{i}}_g \tag{21}$$

Substituting  $\tilde{\mathbf{i}}_c \tilde{\mathbf{v}}_c$  in (18) with (20) (21) yields:

$$\widetilde{\mathbf{v}}_{f} + \mathbf{Z}_{f} \mathbf{Y}_{c} \widetilde{\mathbf{v}}_{f} + \mathbf{Z}_{f} \widetilde{\mathbf{i}}_{g} = \mathbf{G}_{del} \mathbf{P} \mathbf{I}_{i} \mathbf{P} \mathbf{I}_{pv} \widetilde{\mathbf{ref}} + \mathbf{G}_{v} \widetilde{\mathbf{v}}_{f} + \mathbf{G}_{i} \widetilde{\mathbf{i}}_{g}$$

(22)

As shown in Fig. 4,  $\mathbf{G}_{ref}$  is the gain factor function of the VSI reference.  $\mathbf{G}_{ref}$  is the desired admittance of the VSI.  $\mathbf{Y}_o$  and  $\mathbf{G}_{ref}$  are defined via rearranging (22) based on Fig. 4:

$$\widetilde{\mathbf{i}}_{g} = \underbrace{(\mathbf{Z}_{f} - \mathbf{G}_{i})^{-1}(\mathbf{G}_{v} - \mathbf{Z}_{f}\mathbf{Y}_{c} - \mathbf{I})}_{-\mathbf{Y}_{o}} \widetilde{\mathbf{v}}_{f} + \underbrace{(\mathbf{Z}_{f} - \mathbf{G}_{i})^{-1}(\mathbf{G}_{del}\mathbf{P}\mathbf{I}_{i}\mathbf{P}\mathbf{I}_{pv})}_{\mathbf{G}_{ref}} \widetilde{\mathbf{ref}}$$

(23)

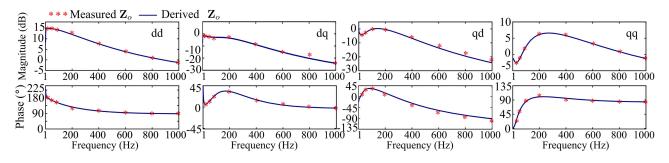

Fig. 8. Validation of derived VSI impedance  $\mathbf{Z}_o$  including the proposed grid impedance compensation within the PLL.

where  $\mathbf{G}_{v} = \mathbf{G}_{del}[\mathbf{G}_{rv} + (\mathbf{G}_{dec} - \mathbf{PI}_{i})\mathbf{G}_{cf} + \mathbf{G}_{fg} + \mathbf{G}_{fc} + (\mathbf{G}_{dec} - \mathbf{PI}_{i})\mathbf{Y}_{c}], \quad \mathbf{G}_{i} = \mathbf{G}_{del}[\mathbf{G}_{ri} + (\mathbf{G}_{dec} - \mathbf{PI}_{i})\mathbf{H}_{cf} + \mathbf{H}_{fg} + \mathbf{H}_{fc} + \mathbf{G}_{dec} - \mathbf{PI}_{i}].$

Therefore, the whole VSI admittance  $\mathbf{Y}_o$  and impedance  $\mathbf{Z}_o (= \mathbf{Y}_o^{-1})$  are fully derived for the VSI system with the proposed grid impedance compensation within the PLL, as shown in Fig. 1.

## B. Validation of Derived Small-Signal Impedance

After deriving the dq VSI admittance and impedance, its validation is carried out via the measurement method [29]. Normally, the derived  $\mathbf{Z}_o$  is used to compare to the measured VSI impedance. Two sets of 0.05 p.u. dq-independent AC current, which are essential for calculating 4 unknown impedance elements ( $Z_{odd} Z_{odq} Z_{oqq} Z_{oqq}$ ), are injected at the grid connection point (Fig. 1) between the VSI and the AC grid. The parameters of the VSI system are presented in Table I. The measured and derived impedance matrices are drawn in Fig. 8. It shows good accuracy of the derived impedance matrix comparing to the measured impedance, which proves that the derived VSI impedance is accurate for stability analysis.

## *C. High-Pass Filter Design for Proposed Grid Impedance Compensation*

To keep the balance between avoiding the steady-state error  $v_v$ at 0 Hz in the dq frame and maintaining the proper low-frequency effectiveness of virtual resistance. It is assumed that the total gain of the virtual resistance and the high-pass filter at  $\omega_s$  is  $\beta$ . The following relation is given below:

$$\frac{s}{s+\omega_c} \times R_v \tilde{i}_{gq}|_{\omega_s} = \beta \tag{24}$$

In normal operation  $i_{gd} \ll 1$ , which simplifies (24) as:

$$\left|\frac{\omega_s j}{\omega_s j + \omega_c}\right| \times R_v < \beta \tag{25}$$

Rearranging (25) for finding  $R_v$  yields:

$$R_v < \beta \sqrt{1 + (\frac{\omega_c}{\omega_s})^2} \tag{26}$$

#### **IV. COMPARISON STUDIES**

The VSI system, as shown in Fig. 1, is used to present the comparison study between the proposed grid impedance compensation and the conventional inductive grid impedance compensation for the PLL. This comparison study includes the stability effectiveness, consequences of excessive compensation, VSI performance and robustness with various grid impedance. The advance of the proposed grid impedance compensation will be presented via the comparison study.

A very weak AC grid (SCR = 1) is connected. The smallsignal impedance model of the conventional inductive grid impedance compensation is also derived for stability analysis and comparison. The cut-off frequency  $w_s$  and its gain  $\beta$  of the proposed grid impedance compensation are set at 6.28 rd/s and 0.1. Therefore, the virtual resistance in this compensation complies with  $R_v < 15$  based on (26). All Parameters of this VSI system are presented in Table I.

Static power limitation of a VSC is different, which depends on the rectifier operation or inverter operation. When operating as a rectifier, the static power limitation is -0.85 p.u. at SCR = 1. When operating as an inverter, the static power limitation is 1.1 p.u.. It is reported [13][14] that instability occurs when VSC operates as an inverter with rated power injection to the weak grid. Therefore, in our analysis, the inverter operation is analyzed.

## A. Stability Effectiveness

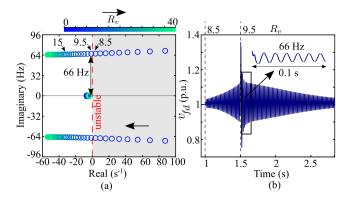

For validating the effectiveness of the proposed grid impedance compensation using virtual resistance, the pole map of the VSI system and its time-domain validation are shown in Fig. 9. As shown in Fig. 9(a), the poles close to x = 0 are presented.  $R_v = 0$  indicates the VSI system using original PLL, and the VSI system is unstable when SCR = 1. With increasing the value of virtual resistance, the poles move to the left-half plane, which indicates that VSI is getting stable. For validating the analyzed results in the time domain, two poles ( $R_v = 8.5$ and 9.5), that identify the unstable and stable conditions of this VSI, are simulated. The analyzed resonant frequency is 66 Hz as shown in Fig. 9(a) when  $R_v = 9.5$ .

The time-domain validation is shown in Figs. 9(b). When  $R_v = 8.5$  is applied at 1 s, VSI loses stability. this VSI is recovered after  $R_v = 9.5$  is applied at 1.4 s. It is validated that the analyzed unstable and stable conditions match the time-domain

Fig. 9. Stability analysis and time-domain validation for the proposed resistive grid impedance compensation within the PLL. (a) Pole map of the inverter system with increasing  $R_v$ . (b) Time-domain validation of virtual resistance.

Fig. 10. Stability analysis and time-domain validation for the conventional inductive grid impedance compensation within the PLL. (a) Pole map of the inverter system with increasing  $\alpha$ . (b) Time-domain validation of virtual negative inductance.

result. During 1 s to 1.5 s, the resonant frequency, as shown in Fig. 9(b), also matches the analyzed frequency. Moreover, the proposed grid impedance compensation can effectively stabilize the very-weak-grid connection.

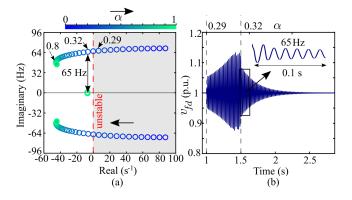

This very-weak-grid connection (SCR = 1) can also be stabilized by the conventional inductive grid impedance compensation using virtual negative inductance, as shown in Fig. 10(a). Compensation ratio  $\alpha$  is defined in (5). The time-domain validation is shown in Fig. 10(b). When  $\alpha$  is changed to 0.29 at 1 s,  $v_{fd}$ start to oscillate which becomes unstable gradually. When  $\alpha$  is changed to 0.32 at 1.5 s,  $v_{fd}$  stop oscillating gradually and return to the stable condition. It is found that the analyzed unstable and stable conditions match the time-domain results. The oscillation frequency is 65 Hz as shown in Fig. 10(b), which matches the analyzed frequency.

Comparing to the conventional inductive grid impedance compensation above, the proposed one can do the similar continuous stabilization for a VSI when connecting to a very weak grid.

## B. Power Injection Improvement and Performance Analysis

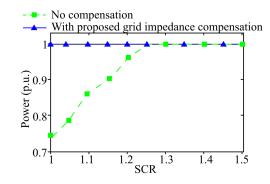

A PLL-based vector-controlled VSI suffers instability when injecting full power to a very weak AC grid (such as SCR = 1)

Fig. 11. Power injection capability of the VSI.

Fig. 12. Power step change comparison. (a) Active power. (b) *d*-axis voltage of connection point. (c) *d*-axis grid current. (d) Frequency.

which has been demonstrated in section IV-A. The maximum injected power of this VSI is identified based on the stability analysis, as shown in Fig. 11. When SCR = 1, only 0.75 p.u. power can be injected to the grid. By using the proposed grid impedance compensation, it is found that the full power injection is maintained even with SCR = 1, as shown in Fig. 11.

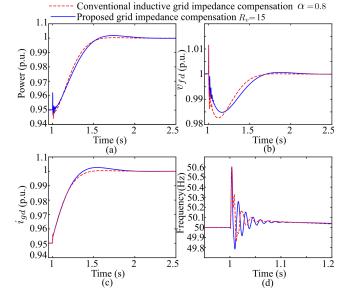

This power injection improvement is demonstrated via the performance test, which is a power step-change test with SCR = 1. Optimized parameters of both compensation are selected based on the stability analysis in section IV-C, where  $R_v = 15$  and  $\alpha = 0.8$ . Both compensation enable a smooth power step change from 0.95 to 1 p.u., as shown in Fig. 12(a). Their grid currents and voltages of the connection point, respectively, have similar and smooth dynamics during the power step change, as shown in Fig. 12(b), (c). For both compensation, the disturbances on the frequency are damped in a similar time period, as shown in Fig. 12(d).

In a sum, the proposed grid impedance compensation enables a full power injection with very-weak-grid connection, and its performance is similar to the conventional inductive grid impedance compensation.

Fig. 13. Overcompensation analysis on VSI stability. (a) Virtual resistance. (b) Virtual negative inductance.

### C. Overcompensation Impact

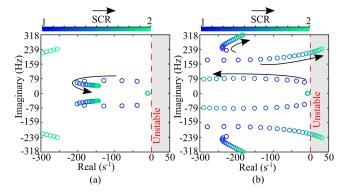

The parameters of  $R_v$  and  $\alpha$  are analyzed based on the smallsignal impedance model. Values of the virtual resistance and the virtual negative inductance are extended widely to explore their overcompensation impact on the VSI. The stability analysis of this VSI system with  $R_v \in [0 \ 100]$  and  $\alpha \in [0 \ 2]$  are presented in Fig. 13.

For the proposed grid impedance compensation within the PLL, as shown in Fig. 13(a), when  $R_v$  increases to 15, the poles are effectively moved to the left from 90 to  $-50 \ s^{-1}$ . However, the rest of  $R_v \in [15 \ 100]$  moves poles to the left from -50 to  $-70 \ s^{-1}$ . The poles in the mid of Fig. 13(a) are moved slight toward the right-half plane with increasing  $R_v$ , which makes the VSI system slightly less stable. Based on the stability analysis of the VSI system above,  $R_v = 15$  puts the VSI system in a good stable position. Furthermore, overcompensation of  $R_v$  does not cause a significant unstable impact.

For the conventional inductive grid impedance compensation within the PLL, as shown in Fig. 13(b), when  $\alpha$  increases to 0.8, the poles are moved to the left significantly. However, when  $\alpha \in$  increases from 0.8 to 2, some poles move to the right-half plane and lead to the instability at  $\alpha = 1.3$ . Based on the stability analysis of the VSI system above,  $\alpha = 0.8$  puts the VSI system in a good stable position. However, the virtual negative inductance cause the instability if the overcompensation occurs ( $\alpha > 1.3$ ).

## D. Influence of Grid Impedance Variance

For the SCR of a grid >1, the overcompensation will occur If the conventional inductive grid impedance compensation is applied based on the worst case SCR = 1. This case is likely to occur if the grid impedance varies or not be measured accurately. Therefore, the effectiveness of both grid impedance compensation are assessed considering grid impedance variance from 1 p.u. to 0.5 p.u., which is equivalent to SCR = 1 to 2.

VSI system stability is presented in Fig. 14 with grid impedance variance. With increasing SCR, poles of the inverter system using the proposed grid impedance compensation further moves to the left, which enables a consistently stable grid connection, as shown in Fig. 14(a). With increasing SCR, some poles of the VSI system using conventional inductive grid impedance

Fig. 14. Impact of grid impedance variance on PLL's grid impedance compensation. (a) Porposed resistive grid impedance compensaton. (b) Conventional inductive grid impedance compensation.

Fig. 15. Time-domain validation of grid impedance variance impact. (a) Porposed resistive grid impedance compensaton. (b) Conventional inductive grid impedance compensation.

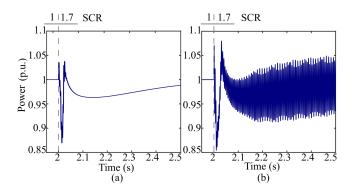

compensation move to the right-half plane, and the VSI loses stability when the SCR is above 1.7, as shown in Fig. 14(b). It proves that the proposed grid impedance compensation is more robust against the grid impedance variance compared to the conventional inductive grid impedance compensation.

Time-domain validation is also presented based on the SCR variance from 1 to 1.7 at 1 s. The results are shown in Fig. 15. The proposed grid impedance compensation enables a stable power injection, which power is maintained at 1 p.u. after 1 s, as shown in Fig. 15(a). On the contrary, after SCR variance occurs, the conventional inductive grid compensation is overcompensated for the grid, which results in instability, as shown in Fig. 15(b).

#### V. CONCLUSION

An improved grid impedance compensation for the PLL using virtual resistance is proposed in this paper to stabilize the very-weak-grid connection (SCR<1.3) for vector-controlled VSIs with rated power injection.

The drawbacks of the conventional inductive grid impedance compensation for the PLL are revealed and validated, which are sensitive to the grid impedance variance and cause the PLL instability if overcompensation occurs.

By comparing to the conventional inductive grid impedance compensation, it is validated that the proposed grid impedance compensation has the similar performance during VSI power regulation with SCR = 1 and possesses the excellent tolerance against a wide range of grid impedance variance. Furthermore, by stability analysis and time-domain validation, the instability caused by overcompensation is avoided by the proposed grid impedance compensation.

The small-signal impedance model of VSI system using the proposed grid impedance compensation is derived and validated via the impedance measurement. After the time-domain test for VSI system, this small-signal impedance model can effectively involve the parameter design for VSI connecting to a very weak grid.

#### REFERENCES

- NERC, "Integrating inverter-based resources into low short circuit strength systems: Reliability guideline," North Amer. Elect. Rel. Corp., Tech. Rep., Dec. 2017.

- [2] N. Pahalawaththa et al., "Connection of wind farms to weak ac networks," CIREG, WG B4.62, Tech. Rep., Dec. 2016.

- [3] J. Rose et al., "Wind energy systems sub-synchronous oscillations: Events and modeling," *IEEE Power Energy Society*, Tech. Rep., Jul. 2020.

- [4] Y. Li, L. Fan, and Z. Miao, "Wind in weak grids: Low-frequency oscillations, subsynchronous oscillations, and torsional interactions," *IEEE Trans. Power Syst.*, vol. 35, no. 1, pp. 109–118, Jan. 2020.

- [5] B. Wen, D. Boroyevich, R. Burgos, P. Mattavelli, and Z. Shen, "Analysis of D-Q small-signal impedance of grid-tied inverters," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 675–687, Jan. 2016.

- [6] A. Egea-Alvarez, S. Fekriasl, F. Hassan, and O. Gomis-Bellmunt, "Advanced vector control for voltage source converters connected to weak grids," *IEEE Trans. Power Syst.*, vol. 30, no. 6, pp. 3072–3081, Nov. 2015.

- [7] C. Li *et al.*, "Coupling influence on the DQ impedance stability analysis for the three-phase grid-connected inverter," *Energies*, vol. 12, no. 19, pp. 1–16, Sep. 2019.

- [8] C. Guo, S. Yang, W. Liu, C. Zhao, and J. Hu, "Small-signal stability enhancement approach for VSC-HVDC system under weak ac grid conditions based on single-input single-output transfer function model," *IEEE Trans. Power Del.*, vol. 36, no. 3, pp. 1313–1323, Jun. 2021.

- [9] Z. Xie, Y. Chen, W. Wu, W. Gong, and J. M. Guerrero, "Stability enhancing voltage feed-forward inverter control method to reduce the effects of phaselocked loop and grid impedance," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 3000–3009, Jun. 2021.

- [10] X. Zhang, D. Xia, Z. Fu, G. Wang, and D. Xu, "An improved feedforward control method considering PLL dynamics to improve weak grid stability of grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 54, no. 5, pp. 5143–5151, Sep. 2018.

- [11] M. Li et al., "The control strategy for the grid-connected inverter through impedance reshaping in q-axis and its stability analysis under a weak grid," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 3229–3242, Jun. 2021.

- [12] A. Adib and B. Mirafzal, "Virtual inductance for stable operation of gridinteractive voltage source inverters," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 6002–6011, Aug. 2019.

- [13] J. Z. Zhou, H. Ding, S. Fan, Y. Zhang, and A. M. Gole, "Impact of short-circuit ratio and phase-locked-loop parameters on the small-signal behavior of a VSC-HVDC converter," *IEEE Trans. Power Del.*, vol. 29, no. 5, pp. 2287–2296, Oct. 2014.

- [14] L. Zhang, L. Harnefors, and H.-P. Nee, "Power-synchronization control of grid-connected voltage-source converters," *IEEE Trans. Power Syst.*, vol. 25, no. 2, pp. 809–820, May 2010.

- [15] L. Zhang, H. Nee, and L. Harnefors, "Analysis of stability limitations of a VSC-HVDC link using power-synchronization control," *IEEE Trans. Power Syst.*, vol. 26, no. 3, pp. 1326–1337, Aug. 2011.

- [16] J. Liu, Y. Miura, and T. Ise, "Comparison of dynamic characteristics between virtual synchronous generator and droop control in inverter-based distributed generators," *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3600–3611, May 2016.

- [17] L. harnefors, M. Hinkkanen, U. Riaz, F. M. Rahman, and L. Zhang, "Robust analytic design of power-synchronization control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 5810–5819, Aug. 2019.

- [18] H. Wu and X. Wang, "Design-oriented transient stability analysis of gridconnected converters with power synchronization control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 6473–6482, Aug. 2019.

- [19] S. Lu, Z. Xu, L. Xiao, W. Jiang, and X. Bie, "Evaluation and enhancement of control strategies for VSC stations under weak grid strengths," *IEEE Trans. Power Syst.*, vol. 33, no. 2, pp. 1836–1847, Mar. 2018.

- [20] C. Li, J. Liang, L. M. Cipcigan, W. Ming, F. Colas, and X. Guillaud, "DQ impedance stability analysis for the power-controlled grid-connected inverter," *IEEE Trans. Energy Convers.*, vol. 35, no. 4, pp. 1762–1771, Dec. 2020.

- [21] M. Davari and Y. A. -R. I.Mohamed, "Robust vector control of a very weakgrid-connected voltage-source converter considering the phase-locked loop dynamics," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 977–994, Feb. 2017.

- [22] Y. Li, L. Fan, and Z. Miao, "Stability control for wind in weak grids," *IEEE Trans. Sustain. Energy*, vol. 10, no. 4, pp. 2094–2103, Oct. 2019.

- [23] M. F. M. Arani and Y. A. I. Mohamed, "Analysis and performance enhancement of vector-controlled vsc in hvdc links connected to very weak grids," *IEEE Trans. Power Syst.*, vol. 32, no. 1, pp. 684–693, Jan. 2017.

- [24] J. A. Suul, S. D'Arco, P. Rodriguez, and M. Molinas, "Impedancecompensated grid synchronisation for extending the stability range of weak grids with voltage source converters," *IET Gener. Transmiss. Distrib.*, vol. 10, no. 6, pp. 1315–1326, 2015.

- [25] J. Sun, "Impedance-based stability criterion for grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3075–3078, Nov. 2011.

- [26] B. Wen, D. Boroyevich, R. Burgos, P. Mattavelli, and Z. Shen, "Inverse nyquist stability criterion for grid-tied inverters," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 1548–1556, Feb. 2017.

- [27] H. Liu, X. Xie, and W. Liu, "An oscillatory stability criterion based on the unified dq-frame impedance network model for power systems with high-penetration renewables," *IEEE Trans. Power Syst.*, vol. 33, no. 3, pp. 3472–3485, May 2018.

- [28] W. Cao, Y. Ma, L. Yang, F. Wang, and L. M. Tolbert, "D-q impedance based stability analysis and parameter design of three-phase inverter-based AC power systems," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 6017–6028, Jul. 2017.

- [29] J. Huang, K. A. Corzine, and M. Belkhayat, "Small-signal impedance measurement of power-electronics-based AC power systems using lineto-line current injection," *IEEE Trans. Power Electron.*, vol. 24, no. 2, pp. 445–455, Feb. 2009.

- [30] S.-K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431–438, May 2000.

- [31] A. Yazdani and R. Iravani, *Voltage-Sourced Converters in Power Systems*, 1st ed. Hoboken, NJ, USA: Wiley, 2010, pp. 204–205.

**Chuanyue Li** (Member, IEEE) received the B.Eng. degrees from Cardiff University, Cardiff, U.K., and North China Electric Power University, Beijing, China, in 2013, and the Ph.D. degree from Cardiff University, in 2017. In 2018, he was a Postdoc with the Laboratory of Electrical Engineering and Power Electronics, Lille, France. He is currently a Research Associate with the School of Engineering, Cardiff University. His research interests include HVDC control and protection and power electronics.

Wei Liu (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. degrees from Zhejiang University, Hangzhou, China, in 2012 and 2015, respectively, and he is currently working toward the Ph.D. degree with Cardiff University, Cardiff, U.K. From 2015 to 2017, he was a Research Engineer with HVDC R&D Group, Rongxin Huiko Electric Technology Company, Ltd. China. From 2017 to 2018, he was a Research Assistant with Aalborg University, Aalborg, Denmark. Since April 2018, he has been a Marie Curie Early Stage Research Fellow funded by

the European Union's InnoDC Project. His research interests include HVDC technologies, DC protection, and renewable power generation.

Jun Liang (Senior Member, IEEE) received the B.Sc. degree from the Huazhong University of Science and Technology, Wuhan, China, in 1992, and the M.Sc. and Ph.D. degrees from China Electric Power Research Institute (CEPRI), Beijing, China, in 1995 and 1998, respectively. From 1998 to 2001, he was a Senior Engineer with CEPRI. From 2001 to 2005, he was a Research Associate with Imperial College London, London, U.K. From 2005 to 2007, he was a Senior Lecturer with the University of Glamorgan, Pontypridd, U.K. He is currently a Professor with the

School of Engineering, Cardiff University, Cardiff, U.K. He is a Fellow of the Institution of Engineering and Technology. He is the Chair of the IEEE U.K. and Ireland Power Electronics Chapter. He is an Editorial Board Member of CSEE JPES. He is the Coordinator and Scientist-in-Charge of two EC Marie-Curie Action ITN/ETN projects: MEDOW ( $\leq 3.9$  M) and InnoDC ( $\leq 3.9$  M). His research interests include HVDC, MVDC, FACTS, power system stability control, power electronics, and renewable power generation.

Liana M. Cipcigan (Member, IEEE) is currently a Professor with the School of Engineering, Cardiff University, Cardiff, U.K., leading the Sustainable Transport cross-cutting theme. She is the Director of the Electric Vehicle Centre of Excellence and Leader of Transport Futures Research Network. She was with the forefront of the shift to electrified transport for more than a decade being recognised nationally and internationally as an Expert in EVs and Smart Grids leading the  $\pounds 1$  M EPSRC Network+ "Decarbonising Transport through Electrification, a Whole system

approach". She has collaborated widely with industry, more recently during the secondment with National Grid under Royal Academy of Engineering Industrial Fellowship, working with the Energy Insights Department responsible for the Future Energy Scenarios. She has held as PI and Co-I grants in the excess of  $\pounds 6.5$  M from EPSRC, Royal Academy of Engineering, Innovate U.K., UKERC, Welsh European Funding Office, EU FP7/H2020 and industry.

Xiaolin Ding received the M.Sc. degree in electrical engineering from the University of Manchester, Manchester, U.K., in 2002, and the Ph.D. degree in electrical engineering from the Queen's University of Belfast, Belfast, U.K., in 2006. She is currently leading the innovation in power system and connection planning area with National Grid, U.K. She has more than a decade industry experience in network modeling, power system analysis, system planning, and power quality. Her research interests include integration of renewables, modelling, system stability,

and WAMS based protection and control.