# OPERATION AND PROTECTION OF VSC-HVDC GRIDS

THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

2022

Wei Liu

SCHOOL OF ENGINEERING CARDIFF UNIVERSITY

# **Declaration**

This thesis is the result of my own independent work, except where otherwise stated, and the views expressed are my own. Other sources are acknowledged by explicit references. The thesis has not been edited by a third party beyond what is permitted by Cardiff University's Use of Third-Party Editors by Research Degree Students Procedure.

Signed.....(candidate) Date .....

| STATEMENT 1                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This thesis is being submitted in partial fulfilment of the requirements for the degree of (insert PhD, MD, MPhil, etc., as appropriate).                                                                                                                                                                                                                           |

| Signed(candidate) Date                                                                                                                                                                                                                                                                                                                                              |

| STATEMENT 2                                                                                                                                                                                                                                                                                                                                                         |

| This work has not been submitted in substance for any other degree or award at this or any other university or place of learning, nor is it being submitted concurrently for any other degree or award (outside of any formal collaboration agreement between the University and a partner organisation).                                                           |

| Signed(candidate) Date                                                                                                                                                                                                                                                                                                                                              |

| STATEMENT 3                                                                                                                                                                                                                                                                                                                                                         |

| I hereby give consent for my thesis, if accepted, to be available in the University's Open Access repository (or, where approved, to be available in the University's library and for inter-library loan), and for the title and summary to be made available to outside organisations, subject to the expiry of a University-approved bar on access if applicable. |

| Signed(candidate) Date                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                     |

#### **Abstract**

Voltage source converter based high-voltage direct-current (VSC-HVDC) systems have shown their advantages over line commutated converter (LCC) based systems in renewable energy integrations, weak ac grid connections and passive network energisations. Worldwide applications of VSC-HVDC have created great potentials to build multi-terminal DC (MTDC) grids to further improve the efficiency and flexibility of power networks.

However, technical challenges still exist in operating MTDC grids safely and reliably. Current flow controls and fault protections within MTDC grids have not been fully addressed and remain critical aspects that need to be further studied. This thesis focuses on conducting investigations on operations and protections of VSC based dc grids.

Current flow controls in meshed MTDC grids are needed to avoid the overload of transmission lines. Analysis of different types of current flow controllers (CFCs) is conducted in this thesis. It is revealed that the half-bridge CFCs (HB-CFCs) are of low cost and high flexibility. A level-shift modulation method, as well as a dual-loop control, is proposed to reduce the switching losses of the HB-CFC and improve its controllability. To guide its controller design, small-signal models of HB-CFCs are derived. The function of the HB-CFC and the effectiveness of the proposed modulation method are verified through simulations.

Protection of dc faults is deemed to be of high cost since dc circuit breakers (DCCBs) are expensive. To cope with this issue, a new device, integrating of DCCBs and HB-CFCs, is proposed. The presented new device can significantly reduce the number of semiconductor devices while containing the functions of the two devices. Detailed analysis of the proposed device is conducted, and simulations are carried out in PSCAD/EMTDC to verify the analysis.

Besides dc faults and grid-side ac faults, valve-side ac faults will induce severe consequences to half-bridge (HB) and full-bridge (FB) modular multilevel converters (MMCs), especially in bipolar HVDC systems. However, fault behaviour and protection methods have not been fully studied for such faults. To bridge this gap, the analysis of valve-side single-phase fault for MMC based HVDC systems are investigated in this thesis. Protection methods against such faults are proposed. For completeness, the effectiveness of the proposed methods is verified by simulations conducted in PSCAD/EMTDC.

The study of this research is expected to contribute to the operation and protection of VSC-HVDC grids.

## Acknowledgements

First of all, my most profound and greatest gratitude goes to my supervisors, Prof. Jun Liang and Dr. Carlos E. Ugalde-Loo. It is a great honour for me to be a PhD student of Prof. Jun Liang for the past three and half years. Without his valuable instructions and support, the research work could not reach the same level. It is also a privilege for me to be under the supervision of Dr. Carlos E. Ugalde-Loo. His tremendous support and wise advice have made my PhD study a remarkable and happy journey, which will be treasured for my whole life.

I would like to thank the technical and financial support from the InnoDC project. It is a valuable and memorable experience within the family of InnoDC. Special thanks go to my project manager, Mrs Manon Davies, for her professional support, making my research work go smoothly as planned. I would like to thank all the colleagues in the InnoDC project, especially the Cardiff team, Dr. Peng Yang, Dr. Gayan Abeynayake, and Dr. Davide Pinzan.

I would like to thank the colleagues and friends at Cardiff University, Dr. Gen Li, Dr. Chuanyue Li, Dr. Sheng Wang, Dr. Yue Zhou, Dr. Xiandong Xu and Dr. Wenlong Ming, for their ponderable advice and suggestions during my research.

I would like to thank my supervisors during my secondments in EFACEC, Portugal and CEPRI, China: Mr. Hugo Martins, Mr. Rui Dias Jorge from EFACEC, Prof. Helder Leite from Uporto, and Dr. Yongning Chi and Dr. Yan Li from CEPRI.

My deepest thanks go to my family, especially to my parents and my parents-inlaw, for their unconditional love and support.

Last but not least, I would like to thank my beloved wife and son. Xiaoyu, thank you for your understanding and endless love. My life has been lit up since I met you. Thank you, Mingze, for the great joy and happiness you have brought to your Mum and me.

Wei Liu

## **Contents**

| ABSTRACT    |                                           | I    |

|-------------|-------------------------------------------|------|

| ACKNOWLE    | DGEMENTS                                  | II   |

| ABBREVIAT   | IONS                                      | VII  |

| LIST OF FIG | URES                                      | IX   |

| LIST OF TAE | BLES                                      | XIII |

| CHAPTER 1   | INTRODUCTION                              | 1    |

| 1.1. Bac    | kground                                   | 1    |

| 1.1.1.      | Renewable energy generation               | 1    |

| 1.1.2.      | VSC HVDC technology                       | 3    |

| 1.1.3.      | VSC HVDC projects                         | 4    |

| 1.1.4.      | Multi-terminal DC grids                   | 6    |

| 1.1.5.      | Technical challenges of VSC HVDC          | 9    |

| 1.2. Res    | earch objectives                          | 10   |

| 1.3. Con    | ntributions of this thesis                | 10   |

| 1.4. Out    | dine of this thesis                       | 11   |

| 1.5. List   | of publications                           | 13   |

| CHAPTER 2   | OVERVIEW OF VSC HVDC TECHNOLOGIES         | 16   |

| 2.1. Intr   | oduction                                  | 16   |

| 2.2. VSC    | C HVDC systems                            | 16   |

| 2.2.1.      | Topology of VSCs                          | 16   |

| 2.2.2.      | Configuration of VSC stations             | 21   |

| 2.2.3.      | DC grids                                  | 23   |

| 2.3. Con    | nponents for implementing MTDC grids      | 25   |

| 2.3.1.      | DC circuit breaker                        | 25   |

| 2.3.2.      | Current flow controller                   | 29   |

| 2.3.3.      | DC transformer                            | 32   |

| 2.4. DC     | fault protection                          | 34   |

| 2.4.1.      | Protection with ac circuit breakers       | 34   |

| 2.4.2.      | Protection with dc circuit breakers       | 35   |

| 2.4.3.      | Protection with fault handling converters | 36   |

| 2.5. AC     | fault protection                          | 37   |

| 2.5.1.      | Grid-side ac fault                        | 37   |

| 2.5.2.      | Valve-side ac fault                       | 38   |

| 2.6 Sun     | nmary                                     | 41   |

| CHAPTER             | 3 DC CURRENT FLOW CONTROLLER                        | 42 |

|---------------------|-----------------------------------------------------|----|

| 3.1. Ir             | ntroduction                                         | 42 |

| <b>3.2.</b> C       | urrent flow controllers in MTDC grids               | 43 |

| 3.3. H              | alf bridge-based CFC                                | 44 |

| 3.4. O              | peration modes of the HB-CFC                        | 45 |

| 3.4.1.              | Bypass mode                                         | 46 |

| 3.4.2               | . Current nulling mode                              | 46 |

| 3.4.3               | . Current sharing mode                              | 47 |

| 3.4.4               | . Current reversal mode                             | 48 |

| 3.5. Si             | mall-signal modelling and frequency domain analysis | 49 |

| 3.5.1               | . Small-signal modelling                            | 50 |

| 3.5.2               | . Frequency-domain analysis                         | 53 |

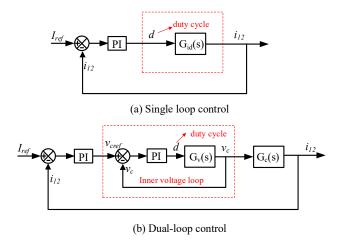

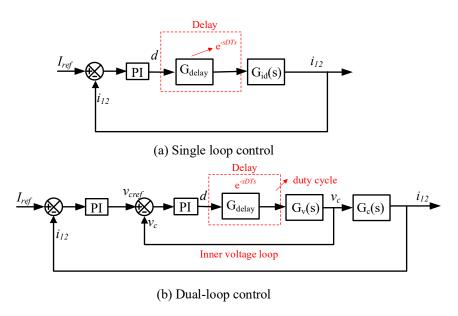

| 3.5.3               | . Cascaded controller design                        | 54 |

| 3.6. L              | evel shift modulation                               | 57 |

| 3.6.1               | . Switches without free-wheeling diodes             | 58 |

| 3.6.2               | . Switches with free-wheeling diodes                | 59 |

| 3.7. Si             | imulation results                                   | 60 |

| 3.7.1               | . Time-domain simulation results                    | 60 |

| 3.7.2               | . Frequency-domain simulation results               | 62 |

| 3.8. Si             | ummary                                              | 63 |

| CHAPTER<br>CAPABILI |                                                     |    |

| 4.1. Ir             | ntroduction                                         | 65 |

| <b>4.2.</b> C       | onfiguration of the CB/CFC                          | 66 |

| 4.2.1               | . Topology of the CB/CFC                            | 66 |

| 4.2.2               | . System-level configuration                        | 67 |

| 4.3. O              | perating as an HB-CFC                               | 68 |

| 4.4. O              | perating as an HCB                                  | 69 |

| 4.5. C              | omparison and analysis                              | 72 |

| 4.5.1               | . Components and costs evaluation                   | 72 |

| 4.5.2.              | . Modified topology                                 | 74 |

| <b>4.6.</b> Si      | imulation results                                   | 76 |

| 4.6.1               | . Current flow control                              | 77 |

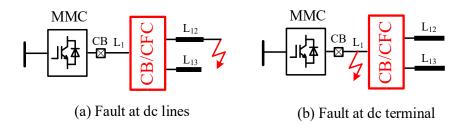

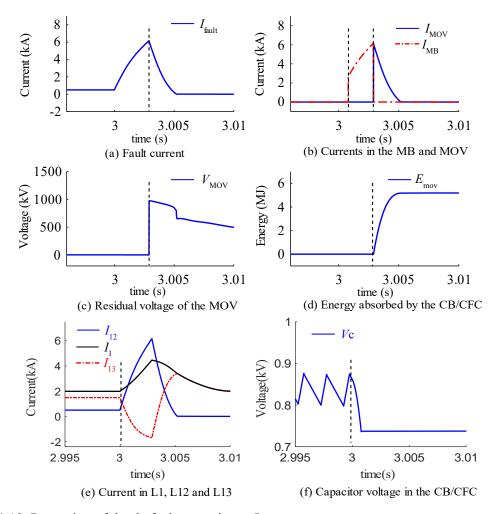

| 4.6.2               | DC fault isolation                                  | 80 |

| 4.7. Si             | ummarv                                              | 84 |

| CHAPTI<br>BIPOLA | _    | PROTECTION OF VALVE-SIDE FAULTS FOR HB-MMCS IN STEMS |       |

|------------------|------|------------------------------------------------------|-------|

| 5.1.             | Intr | oduction                                             | 85    |

| 5.2.             | Fau  | lt characteristic analysis                           | 86    |

| 5.               | 2.1. | Control of HB-MMCs in bipolar systems                | 86    |

| 5.               | 2.2. | Absence of zero-crossings                            | 88    |

| 5.               | 2.3. | Overvoltage of SMs                                   | 91    |

| 5.3.             | Fau  | lt detection                                         | 93    |

| 5.4.             | Pro  | tection methods                                      | 93    |

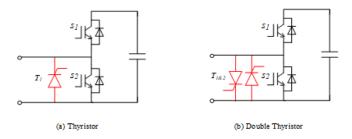

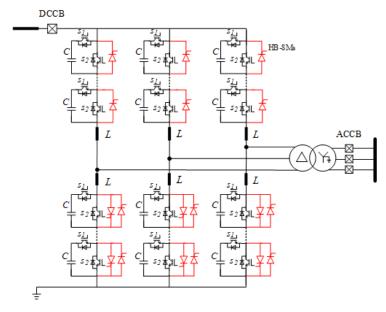

| 5.               | 4.1. | Double thyristor installed in SMs                    | 93    |

| 5.               | 4.2. | Double thyristor installed at the ac-side            | 95    |

| 5.5.             | Sim  | ulations                                             | 96    |

| 5.               | 5.1. | Block the converter only                             | 97    |

| 5.               | 5.2. | Double thyristors installed in SMs                   | 97    |

| 5.               | 5.3. | Double thyristors installed at the ac-side           | 98    |

| 5.6.             | Sun  | nmary                                                | 99    |

| CHAPTI<br>BIPOLA |      | PROTECTION OF VALVE-SIDE FAULTS FOR FB-MMCS IN STEMS |       |

| 6.1.             | Intr | oduction                                             | . 101 |

| 6.2.             | Fau  | lt characteristic analysis                           | . 102 |

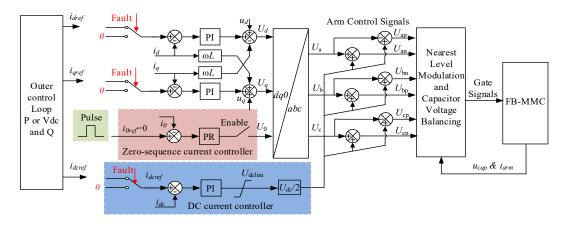

| 6.               | 2.1. | Control of FB-MMCs in bipolar systems                | . 102 |

| 6.               | 2.2. | Overvoltage of SMs                                   | . 103 |

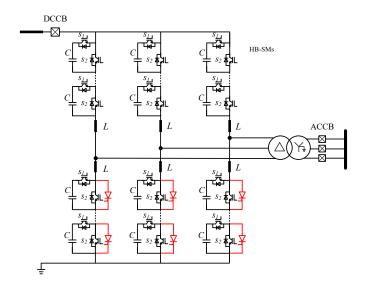

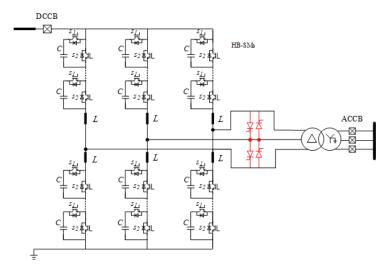

| 6.3.             | Pro  | tection methods                                      | . 106 |

| 6.               | 3.1. | Protection from dc-side                              | . 106 |

| 6.               | 3.2. | Protection from ac-side                              | . 108 |

| 6.               | 3.3. | Analysis of ac and dc side protections               | . 109 |

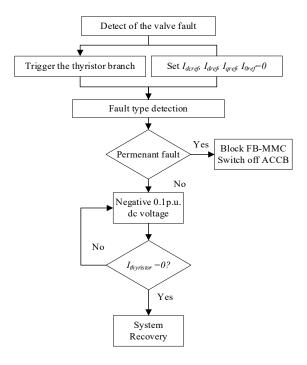

| 6.4.             | Tra  | nsient fault considerations                          | . 109 |

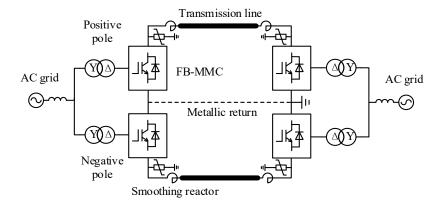

| 6.5.             | Sim  | ulations                                             | . 112 |

| 6.               | 5.1. | Blocking the FB-MMC only                             | .114  |

| 6.               | 5.2. | Protection from dc-side                              | .115  |

| 6.               | 5.3. | Protection from ac-side                              | . 118 |

| 6.               | 5.4. | Protection of transient fault                        | .119  |

| 6.6.             | Sun  | nmary                                                | . 121 |

| CHAPTI           | ER 7 | CONCLUSIONS AND FUTURE WORK                          | .123  |

| 7.1.             | Con  | clusion                                              | . 123 |

| 7.               | 1.1. | Current flow controllers for MTDC grids              | .123  |

| 7.1.2.    | DC protection device with current flow control capability | 124 |

|-----------|-----------------------------------------------------------|-----|

| 7.1.3.    | Protection of valve-side ac faults                        | 125 |

| 7.2. Fut  | ure work                                                  | 126 |

| 7.2.1.    | HB-CFCs                                                   | 126 |

| 7.2.2.    | DC circuit breakers                                       | 126 |

| 7.2.3.    | Valve-side ac faults                                      | 127 |

| REFERENCE | S                                                         | 128 |

### **Abbreviations**

ACCB Alternative current circuit breaker

ANPC Active neutral point clamped

CFC Current flow controller

DAB Dual active bridge

DCCB Direct current circuit breaker

FB Full bridge

GaN Gallium Nitride

HB Half bridge

HB-CFC Half-bridge current flow controller

HCB Hybrid circuit breaker

HVAC High voltage alternate current

HVDC High voltage direct current

IGBT Insulated gate bipolar transistor

LCC Line commutation converter

LCS Load commutation switch

LVDC Low voltage direct current

MB Main breaker

MMC Modular multilevel converter

MOSFET Metal-oxide-semiconductor field effect transistor

MOV Metal oxide varistor

MTDC Multi-terminal HVDC

MVDC Medium voltage direct current

NPC Neutral point clamped

OHL Overhead line

PCC Point of common coupling

PI Proportional integral

PLL Phase lock loop

p.u. Per unit

PWM Pulse width modulation

RHP Right-half plane

RES Renewable energy source

Si Silicon

SiC Silicon carbide

SM Submodule

SFG Single phase ground

STATCOM Static synchronous compensator

SSCB Solid-state circuit breaker

UFD Ultra-fast disconnector

UPFC Unified power flow controller

VSC Voltage source converter

ZOH Zero-order hold

# **List of Figures**

| Fig. 1-1. The evolution of offshore wind turbines.                              | 2  |

|---------------------------------------------------------------------------------|----|

| Fig. 1-2. Size of onshore and offshore wind turbines.                           | 2  |

| Fig. 1-3. The Shetland link in Scotland.                                        | 7  |

| Fig. 1-4. Zhangbei four-terminal MTDC grid.                                     | 8  |

| Fig. 2-1. Topology of the two-level converter.                                  | 17 |

| Fig. 2-2. Modulation waveforms of two-level converters.                         | 18 |

| Fig. 2-3. Topology of three-level neutral-point-clamped (NPC) converter         | 18 |

| Fig. 2-4. Topology of three-level active neutral-point-clamped (ANPC) converter | 19 |

| Fig. 2-5. Topology of modular multi-level converters (MMCs)                     | 20 |

| Fig. 2-6. Full bridge and clamped double SMs.                                   | 21 |

| Fig. 2-7. Configuration of symmetrical monopolar system.                        | 22 |

| Fig. 2-8. Configuration of asymmetrical monopolar system.                       | 22 |

| Fig. 2-9. Configuration of bipolar systems.                                     | 23 |

| Fig. 2-10. Single line diagram of a string connection of an MTDC grid           | 24 |

| Fig. 2-11. Single line diagram of a star connection of an MTDC grid             | 24 |

| Fig. 2-12. Single line diagram of a meshed MTDC grid.                           | 25 |

| Fig. 2-13. Diagram of a passive mechanical DCCB.                                | 26 |

| Fig. 2-14. Diagram of an active mechanical DCCB.                                | 26 |

| Fig. 2-15. Diagram of a solid-state circuit breaker (SSCB)                      | 27 |

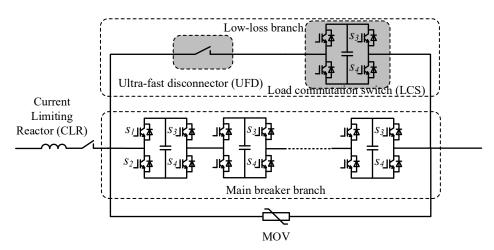

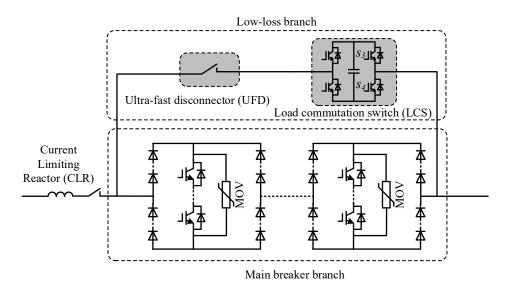

| Fig. 2-16. Diagram of a hybrid circuit breaker.                                 | 28 |

| Fig. 2-17. Schematic of an FB-SM based HCB.                                     | 28 |

| Fig. 2-18. Schematic of the diode-based HCB.                                    | 29 |

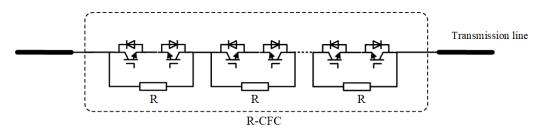

| Fig. 2-19. Resistor-based CFC (R-CFC)                                           | 30 |

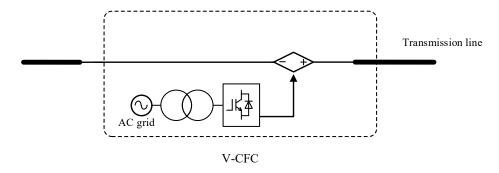

| Fig. 2-20. Series voltage source-based CFC (V-CFC)                              | 31 |

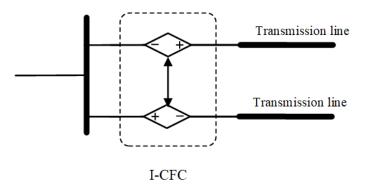

| Fig. 2-21. General diagram of interline CFC (I-CFC).                            | 31 |

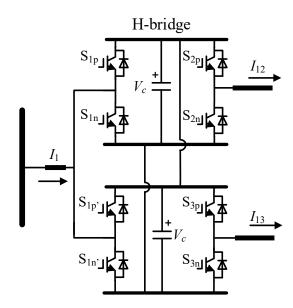

| Fig. 2-22. Diagram of dual H-bridge CFC.                                        | 32 |

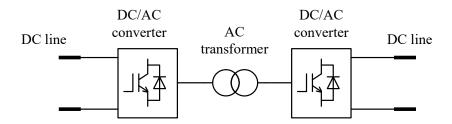

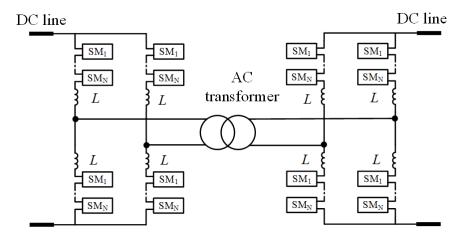

| Fig. 2-23. Typical schematic of dc transformers.                                | 33 |

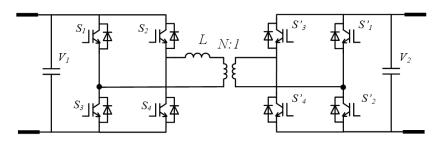

| Fig. 2-24. Topology of the dual active bridge (DAB) converter.                  | 33 |

| Fig. 2-25. Typical schematic of MMC based dc transformer.                       | 34 |

| Fig. 2-26. Fault current path when dc faults occur in HB based MMC systems      | 35 |

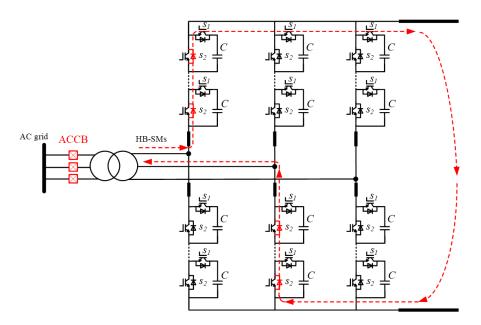

| Fig. 2-27. DC circuit breaker interrupts fault current in an HB-MMC system      | 36 |

| Fig. 2-28. DC fault current paths when FB-SMs and CDSMs are blocked             | 37 |

| Fig. 2-29. Combination of HB-and FB-SMs in one station.                         | 37 |

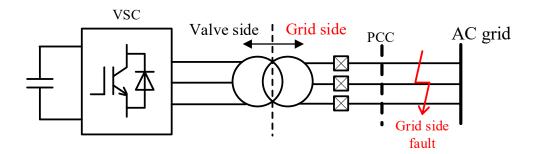

| Fig. 2-30. Grid-side ac faults in a VSC HVDC system.                                  | 38 |

|---------------------------------------------------------------------------------------|----|

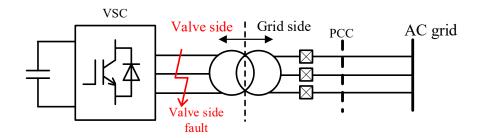

| Fig. 2-31. Valve side ac faults in a VSC HVDC system                                  | 38 |

| Fig. 2-32. Valve side ac faults in a symmetrical VSC HVDC system                      | 39 |

| Fig. 2-33. Fault current paths for an HB-MMC system following a valve-side ac ground- |    |

| Fig. 3-1. Meshed MTDC grids with parallel paths.                                      |    |

| Fig. 3-2. Meshed MTDC grids with CFCs installed.                                      | 44 |

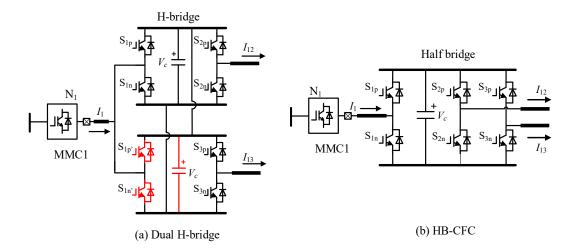

| Fig. 3-3. MTDC grid with dual H-bridge CFC.                                           | 45 |

| Fig. 3-4. Topology of HB-CFC                                                          | 45 |

| Fig. 3-5. HB-CFC operated under bypass mode.                                          | 46 |

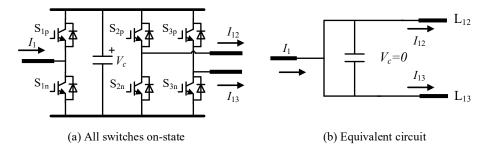

| Fig. 3-6. HB-CFC operated under the current nulling mode.                             | 47 |

| Fig. 3-7. HB-CFC operated under current sharing mode.                                 | 47 |

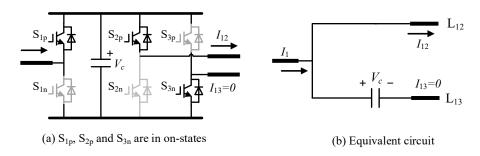

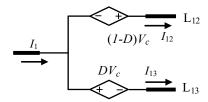

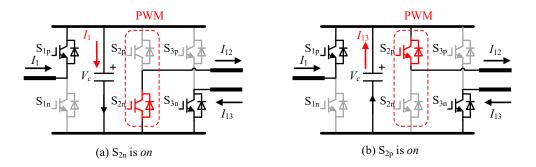

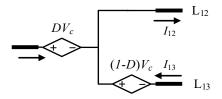

| Fig. 3-8. Equivalent circuit of the HB-CFC under the current sharing mode             | 47 |

| Fig. 3-9. HB-CFC operates under current reversal mode.                                | 48 |

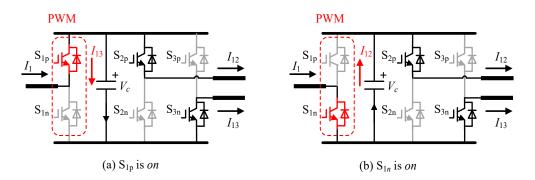

| Fig. 3-10. Equivalent circuit of the HB-CFC under the current reversal mode           | 49 |

| Fig. 3-11. Equivalent diagram of the HB-CFC in an MTDC grid                           | 50 |

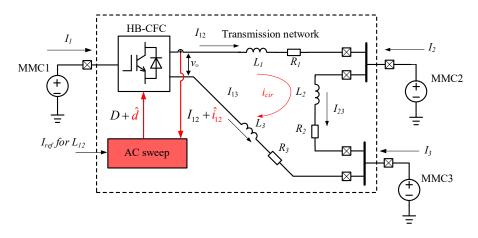

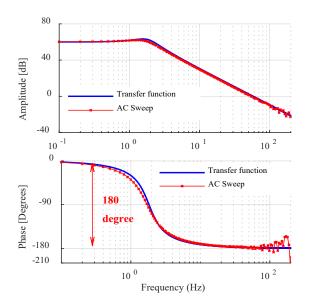

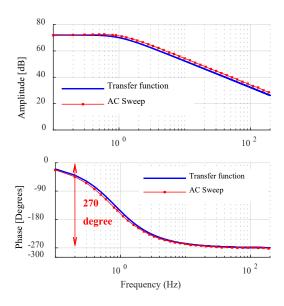

| Fig. 3-12. Frequency-domain analysis (ac sweep) of the HB-CFC.                        | 54 |

| Fig. 3-13. Dual-loop control.                                                         | 55 |

| Fig. 3-14. Control block diagram.                                                     | 55 |

| Fig. 3-15. Control block diagrams when delays are considered.                         | 57 |

| Fig. 3-16. Modulation strategy using switches without free-wheeling diodes            | 58 |

| Fig. 3-17. Modulation strategy using switches with free-wheeling diodes               | 59 |

| Fig. 3-18. Equivalent circuit of the HB-CFC.                                          | 60 |

| Fig. 3-19. Control diagram with level shift modulations.                              | 61 |

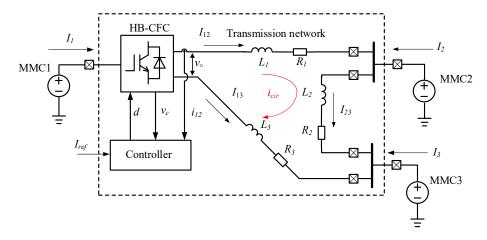

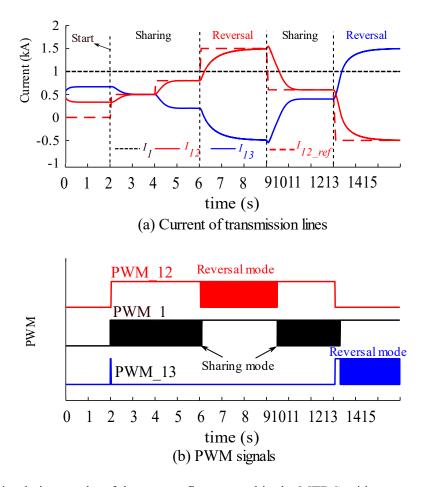

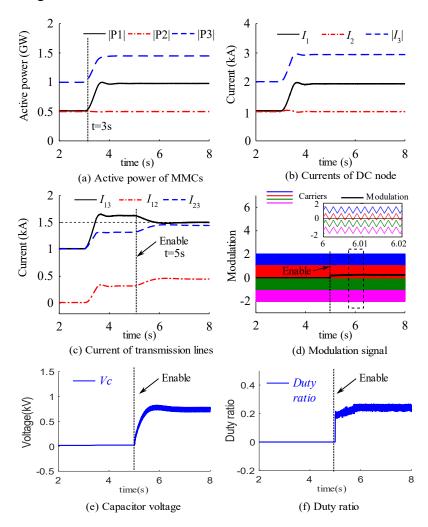

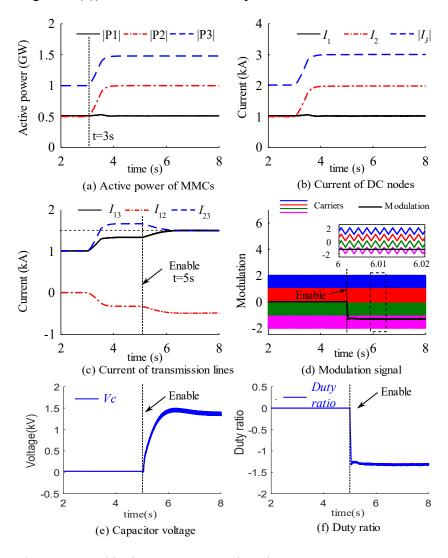

| Fig. 3-20. Simulation results of the current flow control in the MTDC grid            | 62 |

| Fig. 3-21. Frequency responses of the HB-CFC.                                         | 63 |

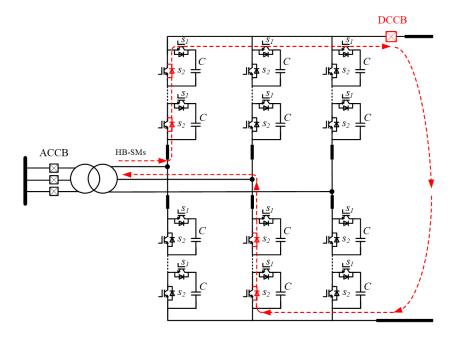

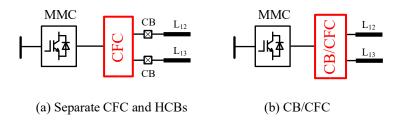

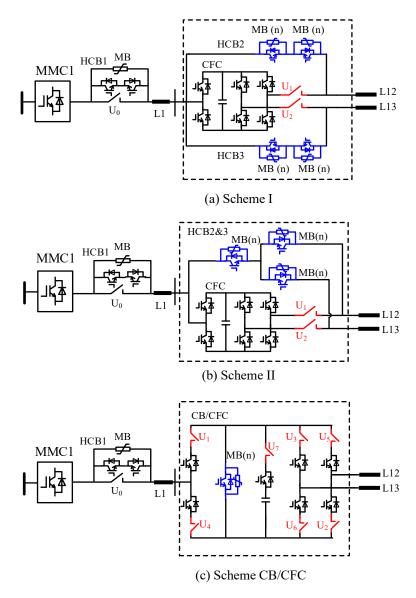

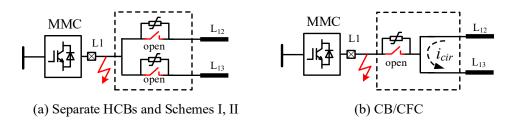

| Fig. 4-1. Configuration of the CB/CFC.                                                | 66 |

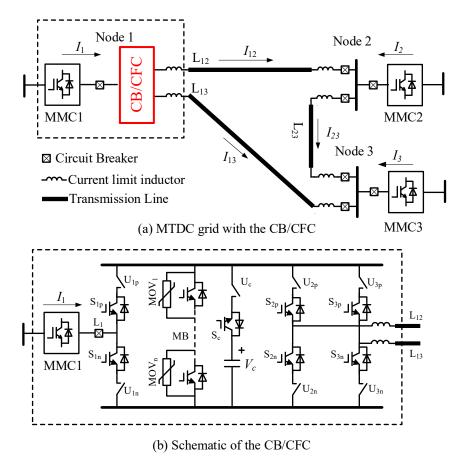

| Fig. 4-2. CB/CFC installed in the node of an MTDC grid                                | 67 |

| Fig. 4-3. System configuration with the CB/CFC in one node                            | 68 |

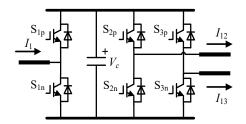

| Fig. 4-4. Simplified topology of the CB-CFC when operated as a CFC                    | 69 |

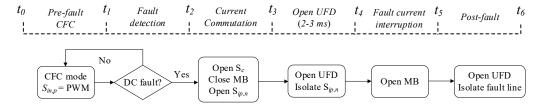

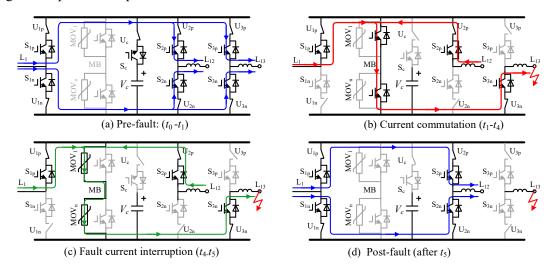

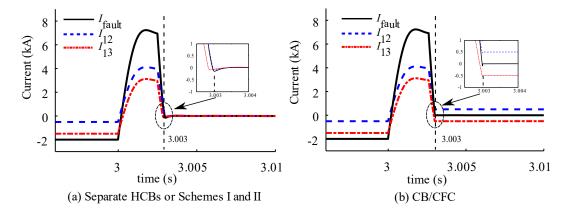

| Fig. 4-5. Operation sequence of the CB/CFC.                                           | 69 |

| Fig. 4-6. Fault isolation process.                                                    | 69 |

| Fig. 4-7. Current and voltage waveforms of a typical fault interruption process       | 71 |

| Fig. 4-8. Schematic of integrated schemes of CFC with HCB.                            | 72 |

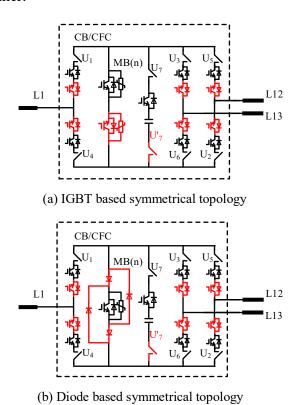

| Fig. 4-9. Modified topologies of the CB/CFC.                                          |    |

| Fig. 4-10. CB/CFC operated in the current sharing mode.                               |    |

| Fig. 4-11. CB/CFC operated in the current reversal mode.                                           | 79  |

|----------------------------------------------------------------------------------------------------|-----|

| Fig. 4-12. Location of the dc faults.                                                              | 80  |

| Fig. 4-13. Protection of the dc fault occurring at L <sub>12</sub>                                 | 81  |

| Fig. 4-14. Protection of the dc fault occurring at dc terminal                                     | 82  |

| Fig. 4-15. Fault isolation process at the dc terminal.                                             | 83  |

| Fig. 4-16. Waveforms of the currents in L <sub>12</sub> and L <sub>13</sub>                        | 83  |

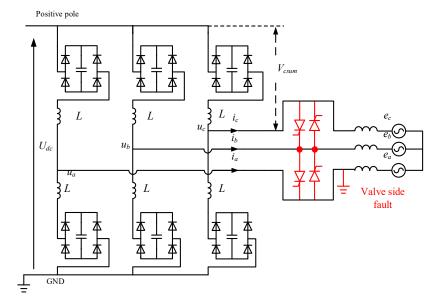

| Fig. 5-1. MMC based bipolar system                                                                 | 86  |

| Fig. 5-2. Schematic diagram of an HB-MMC with its interface transformer                            | 87  |

| Fig. 5-3. Single-phase equivalent circuit diagram of the HB-MMC                                    | 87  |

| Fig. 5-4. Zero-sequence current path caused by the valve-side ac ground fault                      | 89  |

| Fig. 5-5. Equivalent circuit of blocked HB-MMCs after valve-side ground faults                     | 89  |

| Fig. 5-6. Waveforms of valve-side pre-fault and post-fault ac voltages                             | 90  |

| Fig. 5-7. Fault current in the windings of the transformer.                                        | 90  |

| Fig. 5-8. The configuration of ACCB at the grid side.                                              | 91  |

| Fig. 5-9. A single-phase ground fault occurs in phase c.                                           | 91  |

| Fig. 5-10. Equivalent circuit of lower arms in phase <i>a</i> following a fault occurring          | _   |

| Fig. 5-11. Double thyristor-based SMs                                                              |     |

| Fig. 5-12. Schematic of the HB MMC with double thyristor-based protection                          | 94  |

| Fig. 5-13. Schematic of the HB MMC (Press-pack diode used) with single thyristo valve-side faults. |     |

| Fig. 5-14. Thyristors installed in the ac-side to protect valve-side faults                        | 96  |

| Fig. 5-15. Block the HB-MMC only following the fault                                               | 98  |

| Fig. 5-16. Trigger the double thyristors installed in the SMS following the fault                  | 98  |

| Fig. 5-17. Trigger the ac-side thyristors following the fault                                      | 99  |

| Fig. 6-1. Equivalent circuit of FB-MMCs (single phase is used as an example)                       | 102 |

| Fig. 6-2. Zero-sequence current path following an SFG fault at phase a                             | 104 |

| Fig. 6-3. Charging path of SMs in upper arms.                                                      | 105 |

| Fig. 6-4. Proposed dc-side thyristor-based protection method.                                      | 106 |

| Fig. 6-5. DC current control loop.                                                                 | 107 |

| Fig. 6-6. Thyristor based protection when installed at the ac-side.                                | 108 |

| Fig. 6-7. Active based protection method with its corresponding controllers                        | 110 |

| Fig. 6-8. Active protection procedure.                                                             | 112 |

| Fig. 6-9. FB-MMC based point-to-point link.                                                        | 112 |

| Fig. 6-10. FB-MMC based three-terminal grid (positive pole is shown)                               | 113 |

| Fig. 6-11. Block the faulted FB-MMC only following the fault                                       | 114 |

| Fig. 6-12. DC side protection method.                               | 115 |

|---------------------------------------------------------------------|-----|

| Fig. 6-13. The proposed method in an MTDC grid.                     | 116 |

| Fig. 6-14. AC side voltage under two- and three-phase fault.        | 117 |

| Fig. 6-15. Protection performance against two-phase ground fault.   | 118 |

| Fig. 6-16. Protection performance against three-phase ground fault. | 118 |

| Fig. 6-17. Trigger ac-side thyristors following the fault.          | 119 |

| Fig. 6-18. Active based protection method.                          | 120 |

| Fig. 6-19. Protection of a permanent fault.                         | 121 |

| Fig. 6-20. Protection of a non-permanent fault.                     | 121 |

## **List of Tables**

| Table 1-1. UK's VSC interconnectors with other countries      | 5   |

|---------------------------------------------------------------|-----|

| Table 1-2. VSC HVDC links for offshore wind farms in Germany  | 5   |

| Table 1-3. VSC HVDC projects in China.                        | 6   |

| Table 3-1. System parameters of the MTDC grid with the HB-CFC | 60  |

| Table 4-1. Number of high voltage components.                 | 73  |

| Table 4-2. Cost calculation of the MBs for 500 kV devices     | 74  |

| Table 4-3. Parameters of the MTDC system.                     | 76  |

| Table 4-4. Parameters of the CB/CFC.                          | 77  |

| Table 4-5. Operating points of the system.                    | 77  |

| Table 5-1. Parameters of the HB-MMC in each terminal          | 97  |

| Table 6-1. Comparisons of the two schemes.                    | 109 |

| Table 6-2. Parameters of the FB-MMC in each terminal          | 113 |

## **Chapter 1** Introduction

#### 1.1. Background

With the increasing concerns on climate and environmental changes, policies on net-zero greenhouse gas emissions have been proposed by major countries all over the world.

In June 2019, the UK became the first major country to legislate a net-zero target for carbon emissions by 2050 [1]. The UK government is shaping its policies and regulations to encourage sustainable development to achieve a net-zero for the whole society. In line with the Paris Agreement, the EU aims to be climate-neutral by 2050 - an economy with net-zero greenhouse gas emissions. The EU Commission proposed the first European Climate Law in March 2020 to enshrine the 2050 climate-neutrality target into law [2]. In Asia, on 22<sup>nd</sup> September 2020, China has announced the "30·and 60" target to peak its carbon dioxide (CO<sub>2</sub>) emissions before 2030 and reach carbon neutrality by 2060 [3].

#### 1.1.1. Renewable energy generation

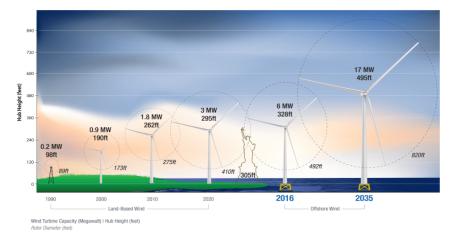

Renewable energy generations, such as wind power and solar photovoltaic, play a significant role in achieving carbon neutrality [4]. In 2018, the EU had an installed capacity of producing 160 GW onshore and 19 GW offshore wind energy. This accounted for around 14% of the EU's electricity demand [5]. Within the year 2020, the EU installed 14.6 GW new wind capacity and will increase to 105 GW over the next five years [6]. To meet the requirements for a climate-neutral sector in 2050, the capacity will increase from the level of 180 GW to 351 GW in 2030 and around 700-1200 GW by 2050 in the EU. Among them, it has been estimated that around 240 to 450 GW will be from offshore wind, which may supply 30% of the future electricity demand [5]. The UK has the largest installed offshore wind capacity globally, with 9.8 GW installed, which will rise to 19.5 GW by the mid-2020s [7]. In recent years, the capacities of one single wind turbine and the whole wind farm have kept increasing. The rating of the wind turbine manufactured by GE reached 12-13 MW in 2021 [8], and a 16 MW prototype of wind turbine was developed and tested by Mingyang Smart

#### Chapter 1 Introduction

Energy group in August 2021 [9]. Fig. 1-1 shows the evolution of offshore wind turbines between 1991 and 2021. The capacity may keep increasing to 17 MW by 2035, as shown in Fig. 1-2 [10].

Fig. 1-1. The evolution of offshore wind turbines [13].

Fig. 1-2. Size of onshore and offshore wind turbines [10].

The largest wind farm was London Array, with a capacity of 630 MW till 2018. Hornsea One project took over the status with a rating of 1.2 GW, which was the first time that the offshore wind farm had ever been built over one gigawatt [11]. Its sister project, Hornsea Two, will take the crown with a capacity of 1.4 GW once operational in 2022 [12]. The newly scheduled project, Dogger Bank wind farm, is estimated to generate 3.6 GW of power when completed in 2026 [8]. By 2030, one-third of the UK's electricity will come from offshore wind [13].

In the meantime, solar power is also developing fast and providing substantial power to the grid. It is estimated by BloombergNEF that solar power has the potential to meet 20% of the EU's electricity demand by 2040 [14].

#### 1.1.2. VSC HVDC technology

Renewable energy sources (RES) are normally located far away from load centres. Bulk power transmission with low power losses and high reliability is greatly needed. High-voltage direct-current (HVDC), as a power electronics-based technology, enables the transport of electricity over long distances and the integration of high shares of RES into the power system with high efficiency. Line commutation converters (LCCs) dominated this application due to their low cost and power losses at the early stage, which has been widely used for over 70 years [15]. With the fast development of the technologies in power electronics and increasing demands of renewable energy integrations, voltage source converters (VSCs) are exhibiting more advantages over LCCs as the commutation of LCCs is dependent on the stiffness of connected ac grids and the footprints of LLCs are much larger.

In 1997, the first experimental two-level VSC HVDC system (3 MW, ±10 kV) was tested in Hellisjon, Sweden. After that, in 1999, ABB commissioned the first commercial VSC HVDC project (called HVDC Light® by Hitachi Energy) on the island of Gotland in Sweden with a rating of 50 MW, ±80 kV [16]. With the evolution of VSC topologies from two-level, three-level to multilevel (e.g., modular multilevel converter (MMC)), power losses of a VSC HVDC system have been significantly reduced, which has pushed the increasing applications of VSCs in the high voltage area [17]. Thanks to these improvements, VSC-based systems have been widely deployed in practical projects in recent years, especially for offshore wind farms [18]. BorWin1 project was the first offshore wind farm connected onshore grids with the HVDC link (built by ABB). The project was commissioned in 2011 with a power rating of 400MW and a voltage level of ±150 kV [19].

Compared to LCC-based systems, VSC-based technologies can provide extra functionalities: a) full four-quadrant operations with independent active and reactive power control; b) flexible ac voltage control to support weak ac grids; c) capability to black start and feed passive systems; d) flexibility of forming multi-terminal DC grids [20]. Therefore, with such characteristics, VSC-based HVDC is more suitable for large-scale renewable energy integrations.

#### 1.1.3. VSC HVDC projects

VSC based HVDC projects have been built widely in recent years around the world thanks to the development of MMC based technologies. At the initial stage, most VSC HVDC systems are built as point-to-point or back-to-back configurations. Due to their good power quality performance, flexible control capability and small footprints, VSCs are preferred to be used in many areas, such as interconnectors between different power grids, integrations of offshore wind power, connections of different ac networks and transmissions of bulk power over long distances.

In this subsection, VSC HVDC systems in three typical countries, the UK, Germany and China, are introduced in detail to show their different functionalities. In the UK, at the current stage, VSC HVDC links are mainly used as interconnectors with other countries for power exchange. While in the North Sea of Germany, VSC HVDC links are mostly used to connect with offshore wind farms to integrate wind power into grids. In China, VSC HVDC systems are deployed as connectors between different ac grids to strengthen the ac networks or as links for bulk power transmission to send the power from the western area to its load centres. Typical projects in these three countries are listed below.

#### a) UK

The UK deployed HVDC links with its neighbouring countries to achieve power balance and enable excess power to be traded between countries. In the early years, four LCC based HVDC links were built up with France, Netherlands, Belgium, and Ireland to exchange power. The first interconnector, the IFA project, was put into operation in 1986, having the capability of transmitting 2000 MW between the UK and France.

With the successful application of VSCs, especially MMCs, most of the current constructed projects are deploying VSC HVDC technologies. Table 1-1 lists the existing and constructing VSC based interconnectors in the UK till now. It can be seen that the power capacities of such links have reached 1400 MW, and the dc-link voltage has reached  $\pm 525$  kV [27].

Table 1-1. UK's VSC interconnectors with other countries.

| Projects                      | Country<br>Interconnected | Year<br>Commission | Voltage rating       | Power rating |

|-------------------------------|---------------------------|--------------------|----------------------|--------------|

| East-West Interconnector [21] | Ireland                   | 2013               | $\pm200~kV$          | 500 MW       |

| NeMo [22][23]                 | Belgium                   | 2019               | $\pm400\;kV$         | 1000 MW      |

| IFA2 [24]                     | France                    | 2020               | $\pm 320 \; kV$      | 1000 MW      |

| North Sea Link[25]            | Norway                    | 2021               | $\pm 515 \text{ kV}$ | 1400 MW      |

| Eleclink [26]                 | France                    | 2022               | $\pm 320 \; kV$      | 1000 MW      |

| Viking Link [27]              | Denmark                   | 2023               | $\pm$ 525 kV         | 1400 MW      |

| FAB Link [28]                 | France                    | 2025               | $\pm 320 \; kV$      | 1400 MW      |

#### b) Germany

Offshore wind energy from the European powerhouse, the North Sea, will play a crucial role in climate neutrality by 2050. Germany has set ambitious goals, achieving 20 GW offshore wind power by 2030 [29]. The commissioned and the underconstructing offshore wind projects in Germany are summarised in Table 1-2. To further increase the pace, 2 GW programs have been set up. It is estimated that, under the 2 GW program, between 2028 and 2030, TenneT will realise at least six 525 kV 2 GW HVDC links at the German North Sea [30].

Table 1-2. VSC HVDC links for offshore wind farms in Germany.

| Projects | Year<br>Commission | Transmission distance | Voltage rating       | Power rating |

|----------|--------------------|-----------------------|----------------------|--------------|

| BorWin1  | 2011               | 200 km                | $\pm 150 \text{ kV}$ | 400 MW       |

| BorWin2  | 2015               | 200 km                | $\pm300~kV$          | 800 MW       |

| DolWin1  | 2015               | 165 km                | $\pm 320 \; kV$      | 800 MW       |

| HelWin1  | 2015               | 130 km                | $\pm 250 \; kV$      | 576 MW       |

| HelWin2  | 2015               | 130 km                | $\pm320~kV$          | 690 MW       |

| SylWin1  | 2015               | 205 km                | $\pm 320 \; kV$      | 864 MW       |

| DolWin2  | 2016               | 135 km                | $\pm 320 \text{ kV}$ | 900 MW       |

| DolWin3  | 2018               | 160 km                | $\pm 320 \; kV$      | 900 MW       |

| BorWin3  | 2019               | 200 km                | $\pm 320 \text{ kV}$ | 900 MW       |

| DolWin5  | 2024               | 130 km                | $\pm 320 \; kV$      | 900 MW       |

| DolWin6  | 2023               | 90 km                 | $\pm 320 \text{ kV}$ | 900 MW       |

| BorWin5  | 2025               | 230 km                | $\pm 320 \; kV$      | 900 MW       |

#### c) China

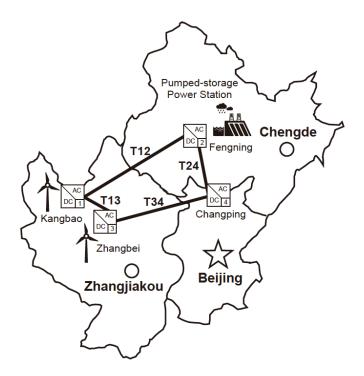

The VSC HVDC technologies have been developing rapidly in China following the first VSC HVDC link commissioned in 2011 at Nanhui, Shanghai. Around ten VSC HVDC projects have been built or are under construction so far in China. Table 1-3 summarises the list of projects. The largest capacity of VSC HVDC stations has reached 5 GW with ±800 kV dc voltages in the Wudongde project, which was constructed by the China Southern Power Grid (CSG). The length of the transmission lines (overhead lines) is around 1450 km. It is the first time that full-bridge FB-SMs (70%) and HB-SMs (30%) are used in one MMC station to handle dc faults [38]. In North China, when commissioned in 2020, the four-terminal Zhangbei project became the first meshed VSC-based MTDC grids globally and operated with 16 DCCBs to protect dc faults [47]. Details on the multi-terminal HVDC projects will be illustrated in Section 1.1.4.

| Projects        | Year<br>Commission | Transmission distance | Voltage rating       | Power rating |

|-----------------|--------------------|-----------------------|----------------------|--------------|

| Nanhui [31]     | 2011               | 8.4 km                | $\pm 30 \text{ kV}$  | 18 MW        |

| Dalian [32]     | 2013               | 43 km                 | $\pm 320 \; kV$      | 1000 MW      |

| Nan'ao [33]     | 2013               | 32 km                 | $\pm 160 \text{ kV}$ | 200 MW       |

| Zhoushan [34]   | 2014               | 134 km                | $\pm200~kV$          | 400 MW       |

| Luxi [34]       | 2016               | B2B                   | $\pm 350 \; kV$      | 1000 MW      |

| Yu'e [36]       | 2019               | B2B                   | $\pm 420 \; kV$      | 1250×4MW     |

| Xiamen [37]     | 2015               | 10.7 km               | $\pm 320 \; kV$      | 1000 MW      |

| Wudongde [38]   | 2021               | 1489 km               | $\pm~800~kV$         | 8000 MW      |

| Zhangbei [47]   | 2021               | 495 km                | $\pm 500 \; kV$      | 3000 MW      |

| Rudong [39][40] | 2022               | 100 km                | $\pm400~kV$          | 1100 MW      |

Table 1-3. VSC HVDC projects in China.

#### 1.1.4. Multi-terminal DC grids

The VSC HVDC systems commissioned in the EU and the UK are all point-to-point links so far. There is a potential to connect the existing HVDC links to form multi-terminal DC (MTDC) grids to promote systems' flexibility and efficiency further [41].

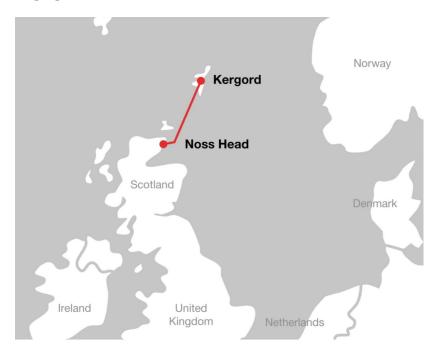

The UK is planning to build a three-terminal VSC MTDC grid in Scotland, the first VSC based MTDC grid in Europe, which aims to connect the Shetland Islands to the Scottish mainland, as shown in Fig. 1-3, to improve the security of power supply for Shetland. The project was awarded to Hitachi Energy by Scottish and Southern Electricity Networks Transmission (SSEN) in 2020 [42].

The Shetland interconnector will be connected with the existing 320 kV Caithness-Moray Link [43] to form an MTDC grid. The commissioning year of this project plans to be 2024. When completed, SSEN can efficiently benefit from both wind and hydropower to increase the reliability and capacity of the power network in the Scotland areas [44].

Fig. 1-3. The Shetland link in Scotland [44].

Demonstration projects of MTDC grids have been built in China by its State Grid and Southern Power Grid.

The Nan'ao three-terminal project is the first MTDC grid in the world that employs VSC-based HVDC technology. The dc voltage of the project is  $\pm 160$  kV, and the power ratings of the three terminals are 200 MW, 100 MW and 50 MW [45].

A five-terminal VSC HVDC system was built in Zhoushan, China and put into operation in 2014. The dc voltage is  $\pm 200$  kV. The capacity of the Zhoushan Station

is 400 MW, which is the largest station in this project. The capacities of other stations are 300 MW, 100 MW and 100 MW, respectively [46].

In Zhangbei, China, a four-terminal meshed HVDC grid, as shown in Fig. 1-4, began its construction in February 2018 and was commissioned in June 2020, which aims to provide up to 3 GW clean wind power to Beijing [47], [48]. The dc voltage of the system is ±500 kV with bipolar configurations. Its corridors of overhead transmission lines cover 227 km in Zhangbei, 126 km in Beijing, 219 km in Fengning, and 66 km in Kangbao areas [49]. The power capacities of Beijing and Zhangbei stations are 3 GW, and the other two stations are 1.5 GW. Pumped hydro storage has been used in one terminal (Fengning Station) to mitigate the intermittent fluctuations induced by wind speed and loads [50]. This project makes breakthroughs in the power capacity, voltage level and configuration of MTDC grids. There are 16 DCCBs deployed in the system to handle dc faults within the grid, which is the first time that DCCBs are commercially used in an MTDC grid [51]-[53]. This project provides a strong reference for future developments of MTDC grids.

Fig. 1-4. Zhangbei four-terminal MTDC grid [53].

#### 1.1.5. Technical challenges of VSC HVDC

The deployment of VSC HVDC systems brings advantages when integrating renewable energy into power grids. However, there are still challenges and obstacles on the way to building future HVDC grids [54].

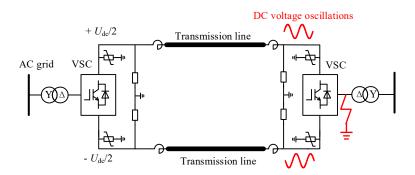

One of the issues within VSC based HVDC systems is the protection of dc faults [55]. No neutral zero-crossings exist in the dc current upon a dc-side fault, making the interruption of fault current more complex than that in an ac system [56]. Therefore, conventional ac circuit breakers are not applicable to a dc grid. On the other hand, since the transients within a dc grid are much faster than those in an ac grid, faster switches are needed to isolate dc faults [57]. DC circuit breakers (DCCBs) with high operating speeds are in great demand. Hybrid DCCBs (HCBs) have been proposed by manufacturers to satisfy these demands [58]-[59]. However, the capital cost of an HCB is still relatively high. The development of a low cost and high reliable DCCB remains an essential topic that needs to be studied.

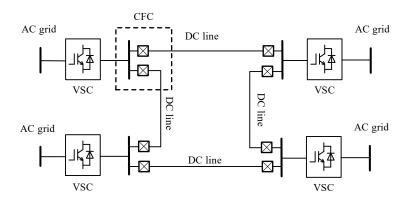

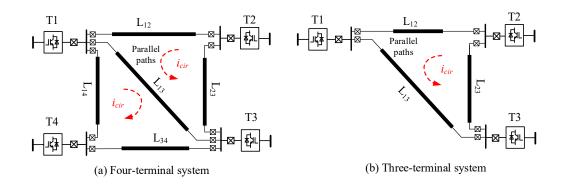

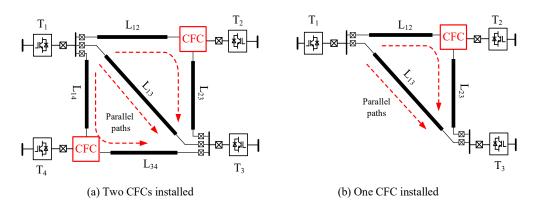

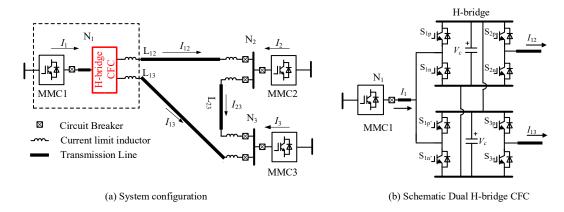

Meshed MTDC grids are promising solutions in the future to promote system-level flexibility and redundancy of power grids [41], [60]. However, power flows within MTDC grids need to be actively controlled to achieve these goals. Unfortunately, the converters installed at the terminal cannot achieve this task [61]. Therefore, devices with current flow control capability are required for MTDC grids [62]. Otherwise, imbalanced current flows may induce the overloading of transmission lines [63]. Several concepts on power (current) flow control of MTDC grids have been discussed in [64]-[65]. However, detailed control methods on such devices, such as modulations, have not been well presented. The topologies and control methods for these current flow control devices need to be investigated further.

Grid-side ac faults in an HVDC system have been widely analysed with related fault-ride through methods being proposed [66]-[67]. The behaviour of VSCs under grid-side ac fault has been regulated by grid codes [68]-[71]. However, valve-side ac ground fault, which occurs internally between the valve and its interface transformer, remains an area that has not been studied sufficiently. Although the occurrence of this type of fault is low, it may bring severe consequences to a VSC, especially for bipolar systems. Without proper protection methods in place, the fast transients following a

valve-side fault may damage power electronics converters. Protection methods against valve-side ac faults need to be proposed, and, therefore, this topic needs further studies.

In a summary, VSC based HVDC technologies are promising solutions for integrations of renewable energy. The development of MTDC grids can further promote the grid's efficiency and flexibility. However, there are still challenges before MTDC schemes are widely used. For instance, actions on reducing capital costs and power losses, protecting ac and dc faults, controlling dc power flows, and promoting systems' stability and reliability need to be taken. New materials, devices and control schemes still need to be studied to contribute to the development of MTDC grids.

#### 1.2. Research objectives

This thesis focuses on analysing the operations and protections of VSC HVDC grids. The objectives of this thesis include:

- a) To investigate current flow control devices (CFCs) for meshed MTDC grids.

- b) To develop modulation and control methods for the investigated half-bridge current flow controllers (HB-CFCs).

- c) To investigate a low-cost dc protection device integrated with current flow control capability

- d) To develop protection methods against valve-side ac faults for HB-MMCs and FB-MMCs in bipolar systems.

#### 1.3. Contributions of this thesis

The main contributions of this thesis are listed below:

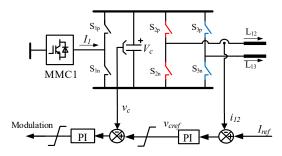

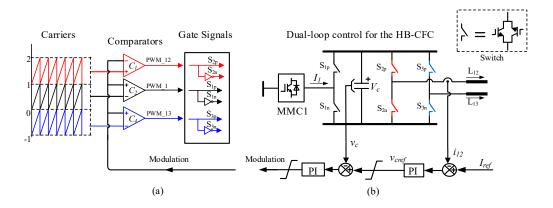

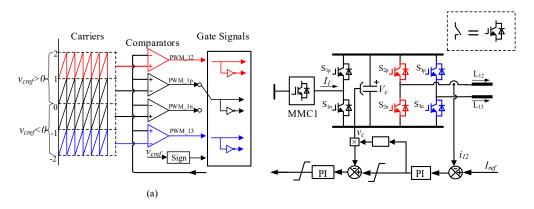

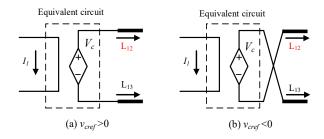

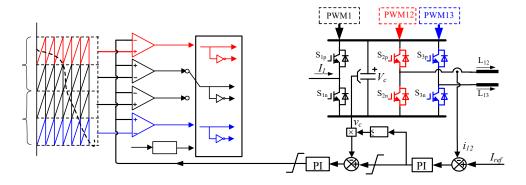

a) The operating modes of the HB-CFC have been investigated based on its function when regulating current flows. A level-shift modulation method has been proposed for the HB-CFC, which ensures that only one bridge is modulated by PWM signals for each specific mode. This can reduce the switching power losses and avoid interactions between different bridges, thus, simplifying the control of the HB-CFC. For completeness, small-signal models of the HB-CFC are derived, which provides a reference for designing controllers for the HB-CFC. Both time-domain and frequency-domain simulations have been conducted to verify the analysis.

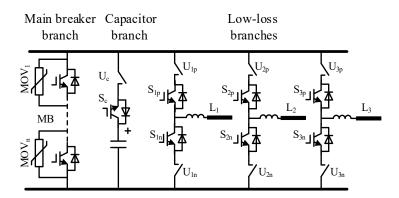

- b) A new device with the capability of dc fault protections and dc current regulations are proposed. HCBs and the investigated HB-CFC are integrated into one single device. Such a combination significantly reduces the number of semiconductor switches. Thus, the capital costs are reduced. The function and effectiveness of the proposed device are verified by simulations in PSCAD/EMTDC.

- c) The consequences of valve-side ground faults for HB-and FB-MMCs in bipolar systems are analysed. It is revealed that the absence of zero-crossings of the ac current and SM overvoltage appears when such a fault occurs in an HB-MMC based bipolar system. For an FB-MMC system, such faults may lead to severe SM overvoltage (around 2 p.u.), which may damage the converter. Protection methods for both HB-and FB-MMCs are proposed, with the effectiveness verified by simulation results in PSCAD/EMTDC.

#### 1.4. Outline of this thesis

The research is conducted through both theoretical analysis and simulation verifications, which focuses on the operations and protections of VSC HVDC grids. The current flow control and dc protections are discussed in Chapters 3 and 4. Besides dc current flow controls and dc protections, valve-side ac faults of MMCs have been investigated in this thesis. Analysis of valve-side ac faults on HB-MMCs is presented in Chapter 5, and on FB-MMCs is presented in Chapter 6.

The outline of the thesis is as below:

#### **Chapter 2: Overview of VSC HVDC technologies**

In this chapter, the state-of-the-art VSC based HVDC technologies are reviewed. The topologies of VSCs, their modulation and control methods are summarised first. The configuration of HVDC grids is described in detail. The challenges of operating HVDC links or MTDC grids are analysed. The demands of regulating dc current flow within a meshed MTDC network are elaborated. Furthermore, protections of ac and dc faults for VSC HVDC systems are discussed. Different strategies and protection devices are introduced and compared. Valve-side ac faults may damage power

electronic converters if proper protection methods are not in place. The demands of investigating protection strategies for such faults are highlighted.

#### **Chapter 3: DC current flow controller**

This chapter first presents the demands of dc current flow control in meshed MTDC networks, and the background of current flow controllers (CFCs) are introduced. The HB-CFC are studied in detail. Based on its different functions when regulating current flows, four operation modes are classified. Equations are derived under different operating modes. Meanwhile, a level-shift modulation method has been proposed to simplify the control of the HB-CFC. To better operate and control the HB-CFC in an MTDC network, a small-signal analysis has been conducted. The small-signal models obtained have been verified by frequency-domain analysis. Time-domain simulation results are given to verify the proposed scheme.

#### Chapter 4: DC protection device with current flow control capability

A new device, the CB/CFC, which combines the function of the DCCB with the HB-CFC, is proposed in this chapter to reduce the number of power electronic devices. The proposed device can operate as an HB-CFC to balance current flows and as a DCCB to isolate dc faults. The modulation and control methods proposed in Chapter 3 are extended and deployed by the CB/CFC when regulating current flows. Timedomain simulations are conducted to verify the function of the proposed device in an MTDC grid. The case studies in Chapter 4 further verify the effectiveness of the level-shift modulation and control methods proposed in Chapter 3.

To add further value, the functionality and its consumed semiconductor devices are calculated. The proposed device has been compared with two existing schemes in the open literature. It is revealed that the proposed CB/CFC can further reduce capital costs.

#### Chapter 5: Protection of valve-side faults for HB-MMCs in bipolar systems

Besides dc protection discussed in Chapter 4, protections of valve-side faults are investigated in this study. In this chapter, the characteristic of valve-side single-phase ground ac faults in an HB-MMC HVDC system is analysed. The critical challenges under such a fault for an HB-MMC, the issues of the absence of zero-crossings, are

illustrated. To protect the HB-MMC following a valve-side fault, strategies are proposed in this section. Simulation results are given to verify the effectiveness of the proposed strategies.

#### Chapter 6: Protection of valve-side faults for FB-MMCs in bipolar systems

In this chapter, the characteristic of valve-side single-phase ac faults in an FB-MMC HVDC system is analysed. The overcurrent and overvoltage problems caused by such faults are studied. Thyristor-based strategy is proposed to protect FB-MMCs following a valve-side fault. Schemes of installing thyristor at the dc and ac sides are proposed. The characteristics of these two methods are summarised with simulations conducted in PSCAD/EMTDC. To add further values, the presented methods have also been verified in a multi-terminal system. In addition, the post-fault restoration process under a transient fault condition is illustrated.

#### **Chapter 7: Conclusion**

This chapter concludes and summarises the thesis. Potential future work is presented.

#### 1.5. List of publications

The doctoral thesis has resulted in the following publications:

- [1] **W. Liu**, C Li, CE Ugalde-Loo, S Wang, G Li, J Liang "Operation and Control of an HVDC Circuit Breaker with Current Flow Control Capability," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4447-4458, Aug. 2021,

- [2] W. Liu, G. Li, J. Liang, C. E. Ugalde-Loo, C. Li and X. Guillaud, "Protection of Single-Phase Fault at the Transformer Valve Side of FB-MMC-Based Bipolar HVDC Systems," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 10, pp. 8416-8427, Oct. 2020.

- [3] G. Li, **W. Liu**, T. Joseph, J. Liang and Z. Song, "Double-Thyristor-Based Protection for Valve-Side Single-Phase-to-Ground Faults in HB-MMC-Based Bipolar HVDC Systems," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 7, pp. 5810-5815, July 2020.

- [4] **W. Liu**, J. Liang, C. E. Ugalde-Loo, C. Li, G. Li and P. Yang, "Level-shift Modulation and Control of a Dual H-bridge Current Flow Controller in Meshed HVDC systems," in *2019 IEEE Energy Conversion Congress and Exposition (ECCE)*, Baltimore, MD, USA, 2019, pp. 62-66.

- [5] **W. Liu**, J. Liang, C. E. Ugalde-Loo, G. Li, C. Li and F. Colas, "Modeling and Frequency Analysis of a Dual H-bridge Current Flow Controller in Meshed HVDC systems," in 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), Genova, Italy, 2019, pp. P.1-P.9.

The author has authored and co-authored the following publications during the PhD study:

- [1] **W. Liu**, J. Yu, G. Li, J. Liang, C.E. Ugalde-Loo, and A. Moon "Analysis and Protection of Converter-Side AC Faults in a Cascaded Converter-Based MVDC Link: ANGLE-DC Project," *IEEE Transactions on Smart grid (early access)*.

- [2] **W. Liu**, G. Li, C. E. Ugalde-Loo and J. Liang, "Start-up strategy for modular multilevel converters with modified nearest level modulation method," in *8th Renewable Power Generation Conference (RPG 2019)*, Shanghai, China, 2019, pp. 1-6. (3rd prize 'Best Conference Paper')

- [3] C. Li, **W. Liu**, J. Liang, X. Ding and L. Cipcigan, "Improved Grid Impedance Compensation for Phase-Locked Loop to Stabilize the Very-Weak-Grid Connection of VSIs," *IEEE Transactions on Power Delivery(early access)*.

- [4] S. Wang, W. Ming, W. Liu, C. Li, C. E. Ugalde Loo and J. Liang, "A Multi-Function Integrated Circuit Breaker for DC Grid Applications," *IEEE Transactions on Power Delivery*, vol. 36, no. 2, pp. 566-577, April 2021.

- [5] G. Li, W. Liu, T. Joseph, J. Liang, T. An, J. Lu, M. Szechtman, B. Andersen, Q. Zhuang, "Control Strategies of Full-Voltage to Half-Voltage Operation for LCC and Hybrid LCC/MMC based UHVDC Systems," *Energies*, vol. 12, no. 4, 742, February 2019.

- [6] G. Li, T. An, J. Liang, W. Liu, T. Joseph, J. Lu, M. Szechtman, B. R Andersen, Y. Lan., "Power reversal strategies for hybrid LCC/MMC HVDC systems," *CSEE Journal of Power and Energy Systems*, vol. 6, no. 1, pp. 203-212, March 2020.

- [7] G. Li, T. An, J. Liang, **W. Liu**, T. Joseph, J. Lu, Y. Lan. "Studies of commutation failures in hybrid LCC/MMC HVDC systems," *Global Energy Interconnection*, vol. 3, no. 3, pp. 193-204, June 2020.

- [8] P. Yang, W. Ming, J. Liang, J. Wu and W. Liu, "Reduction of DC-link Ripples for SiC-based Three-phase Four-wire Inverters with Unbalanced Loads," in *2019 IEEE Energy Conversion Congress and Exposition (ECCE)*, Baltimore, MD, USA, 2019, pp. 2819-2835.

## **Chapter 2 Overview of VSC HVDC**

## **Technologies**

#### 2.1. Introduction

The first commercialised VSC HVDC link constructed by ABB was put into operation in Gotland Island, Sweden, in 1999. Two-level converters were employed with a dc voltage of ± 80 kV and power capacity of 50 MW. Self-commutating devices (IGBTs) were used to build up the converters. Thanks to the development of power electronics, the level of voltage and the capacity of power for VSC HVDC systems have been significantly increased. By now, the highest dc voltage of the VSC station reaches ± 800 kV with a power rating of 5 GW, which is ten times the voltage level and one hundred times the power rating of the first VSC HVDC project, respectively [72]-[73]. Besides point-to-point links, meshed multi-terminal DC grids have been constructed. As introduced in Chapter 1, a four-terminal MTDC grid was commissioned in June 2020 with a dc voltage of ± 500 kV and a power rating of 3 GW in Beijing, China.

In this chapter, an overview of VSC based HVDC technologies will be given. Topologies of VSCs, configurations of VSC HVDC systems, and practical VSC HVDC projects, so far, are summarised. The state-of-the-art for dc circuit breakers and current flow controllers are presented. Protection methods on dc-and ac-faults are reviewed with challenges emphasised.

#### 2.2. VSC HVDC systems

In this section, the topologies of VSCs and configurations of HVDC systems are reviewed.

#### 2.2.1. Topology of VSCs

Power electronic-based converters are key devices for HVDC systems. At the early stage, thyristor-based LCC systems have dominated HVDC projects due to their low capital costs and high-power capacity. With the development of power electronic

devices and related converter topologies, VSCs have shown advantages over LCCs. The topologies of VSCs are summarised next.

#### a) Two-level converter

The two-level converter is one of the most frequently used types of VSCs, especially in systems with a voltage level of several kilovolts or below, such as motor drives and PV systems [74]-[75]. The schematic of a three-phase two-level converter is shown in Fig. 2-1. The two-level converter contains a dc bus which is normally provided by a dc capacitor to maintain its dc voltage approximately constant. There are six arms that are built up by fully controllable switching devices. IGBTs with antiparallel diodes or field-effect transistors (MOSFETs) are mostly used to build up two-level converters. However, in HVDC application areas, series-connected structures have to be used to withstand large voltage (typically tens or hundreds of kilovolts).

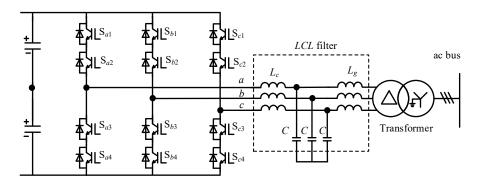

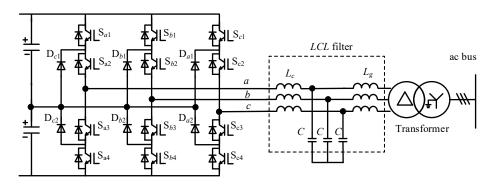

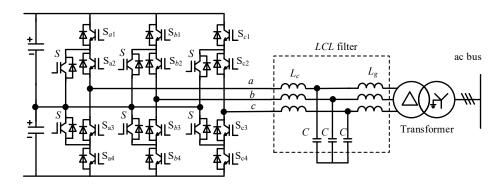

Fig. 2-1. Topology of the two-level converter.

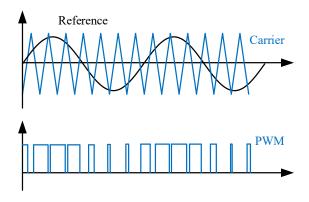

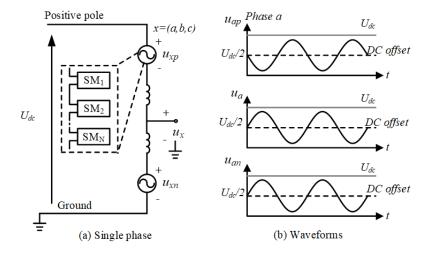

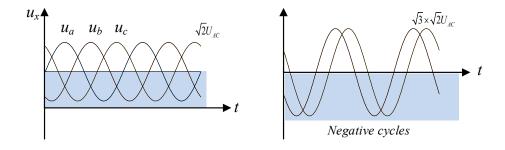

The two-level converter is regulated by pulse-width modulation (PWM) signals. The modulation signals are compared with high-frequency carriers (e.g. triangular carriers) to generate PWM signals, as shown in Fig. 2-2.

When the modulation signal is higher than the triangular carrier, the switching devices in the upper arm are switched on. Conversely, the devices in the lower arm are switched on. In this way, the two-level converter converts the constant dc bus voltage into ac voltages.

However, the output ac voltages typically contain high-frequency harmonics. Therefore, ac filters (*L, LC or LCL* filters), as shown in Fig. 2-1, are needed to remove high-frequency harmonics. A higher switching frequency leads to a higher frequency spectrum of its harmonics. Thus, the sizes and costs of ac filters can be reduced, and

power quality can be improved. However, a higher switching frequency will significantly increase the switching power losses. It is a trade-off to select the switching frequency when designing a VSC. A typical switching frequency of two-level converters in HVDC applications is around 1 kHz or 2 kHz [76]-[77].

Fig. 2-2. Modulation waveforms of two-level converters.

# b) Three-level NPC converter

The three-level neutral-point-clamped (NPC) converter was introduced in early 80s [78]-[79]. Since that, the topology has been widely used in applications with a power rating of several megawatts, such as medium motor drives [80]-[81]. The schematic of a three-level NPC converter is given in Fig. 2-3. Additional diodes are used to clamp the voltages applied to the IGBTs. Compared to conventional two-level converters, the three-level NPC converter provides higher power quality (e.g. fewer harmonics) [78].

Fig. 2-3. Topology of three-level neutral-point-clamped (NPC) converter.

Therefore, it is an alternative solution for HVDC systems. AC filters are still needed to remove the harmonics caused by the PWM switching. Similar to two-level

converters, switching devices in the three-level NPC need to be series-connected to withstand system-level voltage for HV applications. Several HVDC projects, in the early stage, use such topology instead of two-level converters, such as Eagle Pass in the USA [82].

One of the issues that three-level NPC converters face is that the power losses between different switching devices are not balanced [83]-[85]. This may lead to an over-temperature of semiconductors under some critical conditions. Therefore, overrating design is required. However, the capital costs will, at the same time, be increased. To tackle this issue, the three-level active NPC (ANPC) converter is proposed [86]-[87]. The topology is shown in Fig. 2-4. The replacement of diodes into controllable devices (e.g. IGBTs) ensures that the power losses are better distributed among different devices.

Fig. 2-4. Topology of three-level active neutral-point-clamped (ANPC) converter.

The three-level ANPC converter has been used in several VSC HVDC links. The Murrraylink, located in South Australia and Sunraysia region, was commissioned in 2002 with ANPC converters. The dc voltage of the HVDC link is  $\pm$  150 kV, and its power rating is 220 MW[88]. The same topology was used in the CrossSound link in the USA with a power rating of 330 MW and a dc voltage of  $\pm$  150 kV. This project was manufactured by ABB and commissioned in 2002 [89].

#### c) Modular multilevel converter

The modular multilevel converter (MMC) was first proposed by R. Marquardt and A. Lesnicar in 2003 [90]. The first commercial MMC based HVDC system is the ± 200 kV Trans Bay Cable (TBC) project with a power rating of 400 MW, which is located in San Francisco and was completed in 2010 [91]-[92]. Following that, the

MMC has become the most popular and commonly used type of VSCs for HVDC applications. The MMC significantly reduces power losses of VSC HVDC systems and improve their power quality [93]-[94]. By exclusion of large ac filters, the footprint of an MMC based HVDC system is much smaller. Furthermore, due to the modularised concept, the design and implementation of an MMC are technically more accessible than that of a conventional two-level or three-level converter.

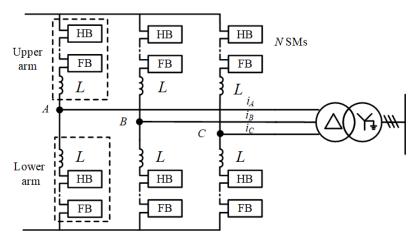

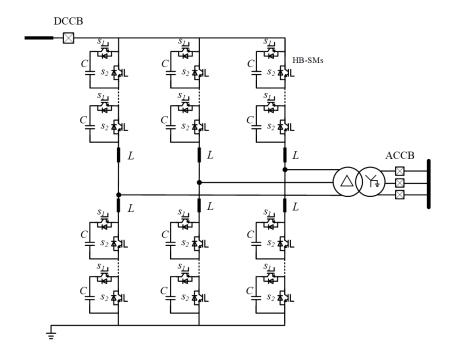

Fig. 2-5 shows the topology of an MMC with HB SMs. It consists of three legs for a three-phase application. Each leg contains one upper arm and one lower arm. The arm is built by *N* submodules (SMs) with a series-connected inductor. The dc voltage is divided by *N* SMs instead of series-connected switching devices as that of a two-level converter. Therefore, with such a configuration, the voltage balancing issues caused by directly series connected IGBTs are relieved, and the gate signals do not have to be as sophisticated as those of two- or three-level converters [95].

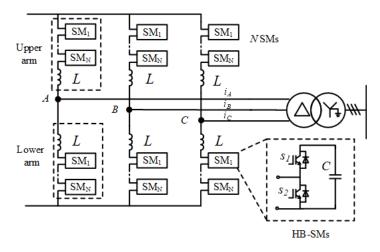

Fig. 2-5. Topology of modular multi-level converters (MMCs).

Since being proposed in 2003, HB topologies have dominated the applications of MMCs due to their low capital costs and power losses [96]. However, HB based MMCs cannot interrupt dc fault currents. The free-wheeling diodes still carry fault currents even when the HB-MMC is blocked, which endangers the safe operation of HVDC systems [97].

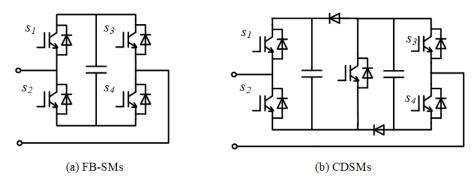

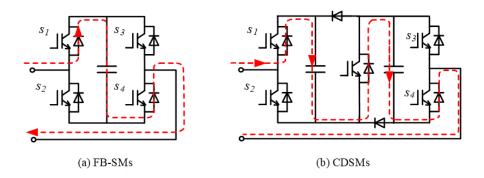

To solve this issue, different configurations of SMs have been investigated. Full bridge SMs (FB-SMs) and clamped double SMs (CDSMs) are proposed [96], and their schematics are shown in Fig. 2-6 [98]. When adopting such a topology, MMCs have

the capability to isolate dc faults. Once the gate signals are removed, the dc capacitors of SMs are inserted into the fault paths. In such a way, the fault current will be blocked and reduced to zero in a short time. However, when FB-MMCs are used, the capital costs are significantly increased [99]. Hybrid schemes, such as adopting both FB- and HB-SMs in one MMC, are proposed to reduce the number of semiconductor devices but still with the capability of dc fault isolation [100]. These topologies with capabilities of dc fault handlings are preferred by systems where transient faults occasionally occur, such as transmission line-based systems. FB-MMCs have been discussed in [101]-[104]. A hybrid scheme with both FB- and HB-SMs in one MMC has been used in the Wudongde project [73].

Fig. 2-6. Full bridge and clamped double SMs.

#### 2.2.2. Configuration of VSC stations

Three basic configurations, i.e. symmetrical monopole, asymmetrical monopole, and bi-pole, are typically adopted by HVDC systems. The configurations of VSC stations and their characteristics will be introduced in this subsection.

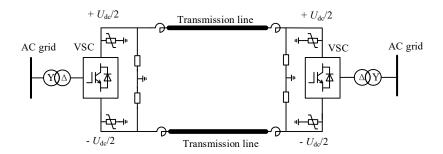

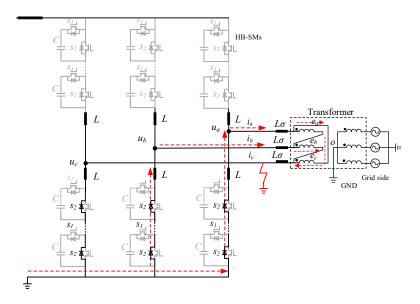

#### a) Symmetrical monopolar system

Fig. 2-7 shows the configuration of a symmetrical monopolar system. For such systems, two fully insulated conductors are adopted. The magnitudes of dc voltage are equal, and their polarities are opposite. Such a system can be grounded through a high impedance at the dc-side at the middle point of shunt capacitors/resistors or ac side through transformers [105]. It should be noted that, with a high impedance grounding, once a pole-to-ground dc fault occurs, the voltage of the healthy pole will increase to around 2 times its rated value [106]-[107]. This should be considered when designing the insulation schemes. Symmetrical monopolar configurations have been widely

employed in VSC HVDC systems at the early stage since the transmission lines only withstand half of the rated dc voltage during normal conditions [108].

Fig. 2-7. Configuration of symmetrical monopolar system.

## b) Asymmetrical monopolar system

Fig. 2-8 shows the configuration of an asymmetrical monopolar system. The system is grounded at its dc-side. Different to a symmetrical system, only one high voltage insulated transmission line is needed in such a system. Natural conductors or metallic returns can be used for the other path with the ground potential. This can reduce the costs and risks of insulation failure for the grounded pole [41]. Omitting the ground conductors may be possible when ground currents are permitted. But it may have influences on the environment [109]. It should be noted that the transformer windings of the secondary side will have to withstand dc offset voltage in such systems, which is half of the dc voltage[110]. This factor should be considered when designing transformers for such systems. So far, only a few projects use such configurations [114].

Fig. 2-8. Configuration of asymmetrical monopolar system.

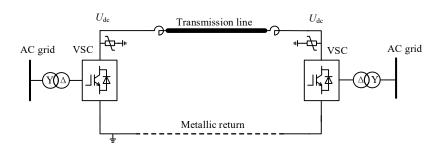

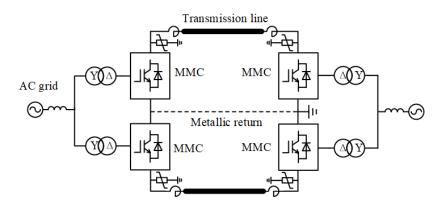

#### c) Bipolar system

Fig. 2-9 shows the configuration of a bipolar system. A bipolar system can be seen as a combination of two asymmetrical systems. The groundings with the connected

metallic return are shared by the two asymmetrical systems [110]. Each pole has its ac transformers, and under normal conditions, the two poles are operated under balanced modes, which ensures the current at the grounded line is zero. This is needed when the system is directly grounded with the earth or sea. Similar to asymmetrical systems, the transformer of the system needs to withstand a dc component, which is half of the dc voltage [111].

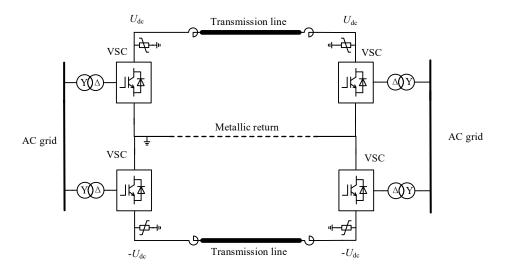

Fig. 2-9. Configuration of bipolar systems.

The two converters in a bipolar system can operate independently. Therefore, 50% of the power capacity is left when one pole experiences a fault or is under maintenance. This improves the reliability of the system [112]. With increasing demands of power capacity, bipolar systems are more and more commonly deployed by VSC HVDC systems [25], [115].

## **2.2.3. DC** grids

The successful development of point-to-point HVDC links has proven the advantages of HVDC technologies. LCC HVDC systems have been well recognised as solutions for bulk power transmissions over a long distance, interconnectors of submarine cables and connection of asynchronous ac grids [109]. At the early stage, LCC HVDC has dominated practical projects. However, LCC based HVDC systems are not suitable to form an MTDC grid to enhance systems' reliability and efficiency further since the directions of the current of LCCs cannot be reversed [110]. Moreover, the VSC based HVDC technology has broadened the application range of HVDC to

new areas such as connections with weak ac grids, offshore wind farms, and further forming an MTDC grid [41].

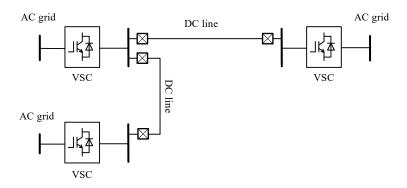

Typical types of MTDC grids includes radial and meshed configurations [109]. A string connection of the radial MTDC grid is shown in Fig. 2-10. The radial connection can be extended from point-to-point links. Flexibility is improved by such a configuration in case disturbance occurs for some of the stations [113]. DC circuit breakers are recommended to be installed in case of dc faults and to avoid the outage of the entire network. The three-terminal Nan'ao project and five-terminal Zhoushan project are configurated as a radial network [33], [45], [46]. A star connection of MTDC grids, as shown in Fig. 2-11, could be an alternative solution [118]. Switching stations are used to provide connections for different dc lines.

Fig. 2-10. Single line diagram of a string connection of an MTDC grid.

Fig. 2-11. Single line diagram of a star connection of an MTDC grid.

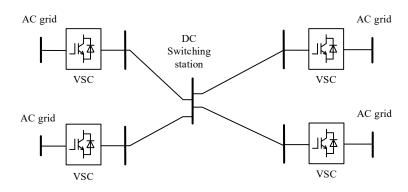

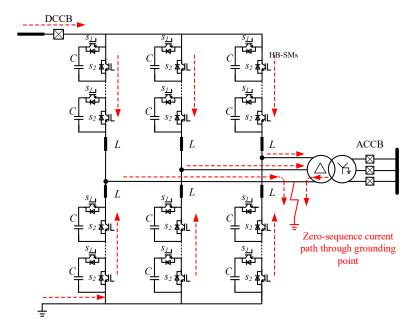

To further enhance the reliability and efficiency, meshed MTDC grids are proposed and developed. A typical diagram is illustrated in Fig. 2-12. The Zhangbei project is configurated as a four-terminal meshed MTDC grid to provide redundancy and compensate for the fluctuation of renewable generation [47]. Within such a network,

as paralleled current paths exist, dc circuit breaker and current flow controller are normally required to supervise the operation of the grid.

Fig. 2-12. Single line diagram of a meshed MTDC grid.

#### 2.3. Components for implementing MTDC grids

MTDC grids are promising solutions to increase the level of renewable energy integrations. Reliability and flexibility can be improved through establishing dc grids either by connecting existing HVDC links or building new infrastructures [116]. However, there are still obstacles on the way to achieving MTDC grids. The isolation of dc faults, the control of dc power flows, and the connections between different dc voltage levels remain technical challenges [117]. In this section, components used in an MTDC grid to tackle these challenges will be reviewed.

#### 2.3.1. DC circuit breaker

The interruption of dc current is much more difficult than ac due to the absence of neutral zero-crossings. Conventional ac circuit breakers with a mechanical switch cannot be used in a dc system directly [98], [110]. Circuit breakers for HVDC systems should be developed. Different topologies of DCCBs have been proposed. By analysing their mechanism, the types of DCCBs can be categorised into three types, i.e. mechanical circuit breakers, solid-state circuit breakers and hybrid circuit breakers [119]-[121].

## a) Mechanical circuit breaker (MCB)

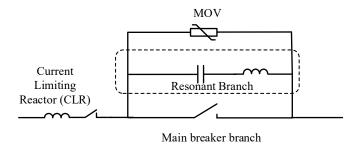

Fig. 2-13 illustrates the typical schematic of a mechanical breaker. Different from a conventional circuit breaker, a resonant branch is added to create zero-crossings for

the current interruption [41]. The load current flows through the mechanical branch under normal conditions with low power losses. When a fault is detected, the resonant branch will generate a resonant current, which helps to create a zero-crossing for the mechanical branch. Thus, the mechanical switch can be open when zero-crossing appears. At the early stage, passive resonant circuits are used. But the time of the appearance of a zero-crossing may still take several ac cycles, and the load conditions influence the behaviour of the passive MCBs [122].

Fig. 2-13. Diagram of a passive mechanical DCCB.

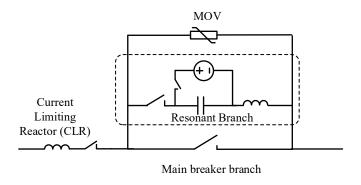

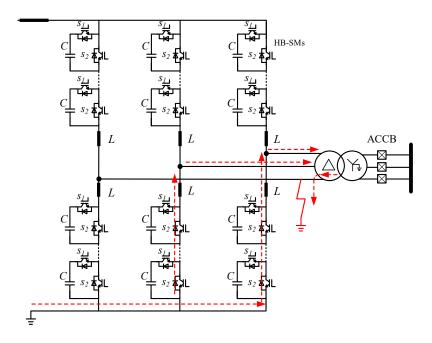

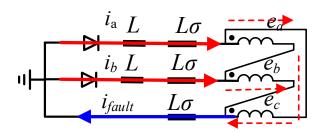

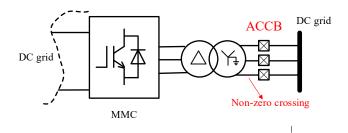

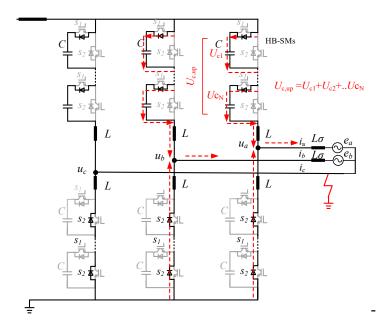

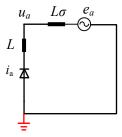

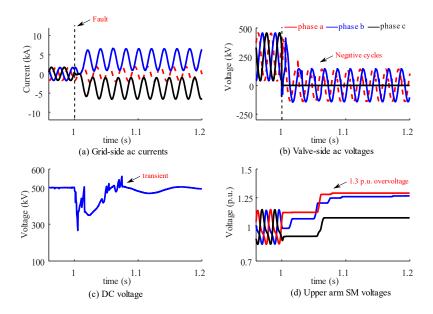

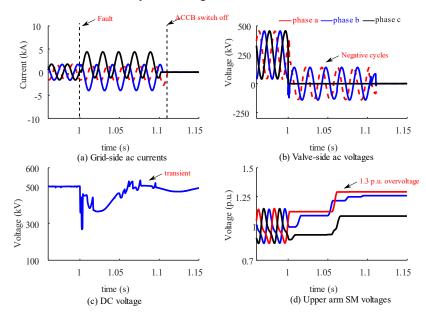

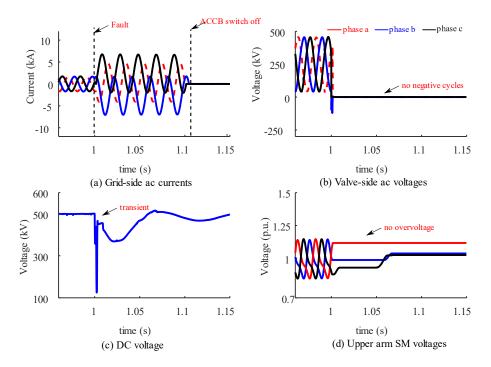

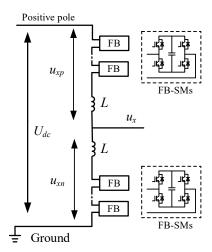

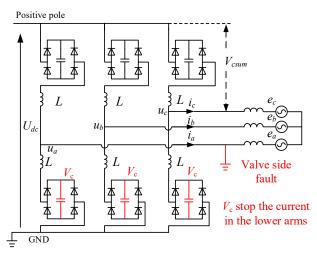

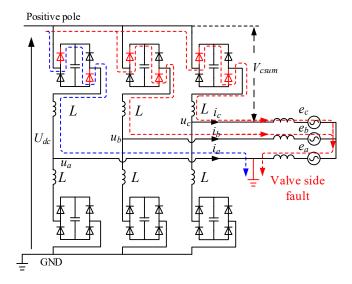

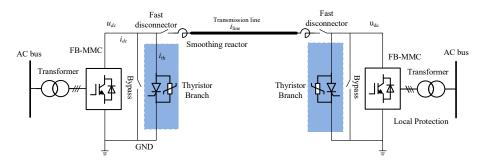

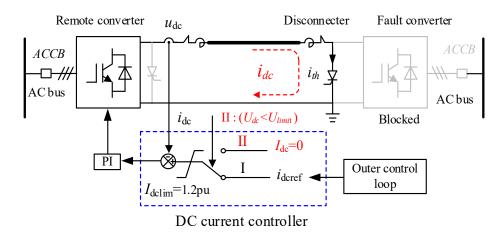

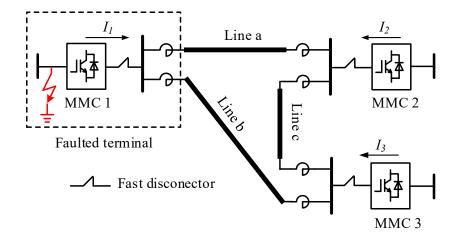

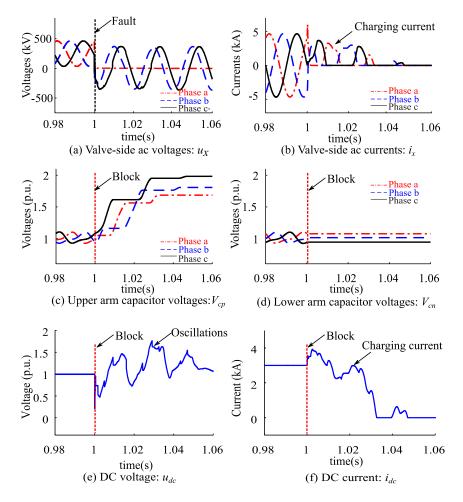

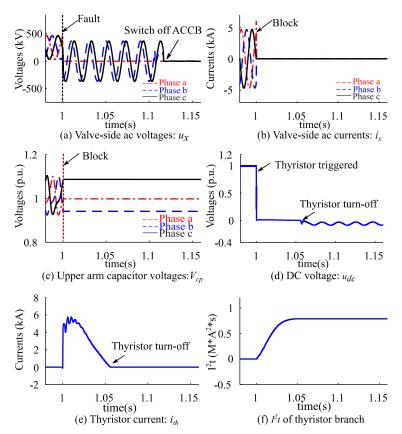

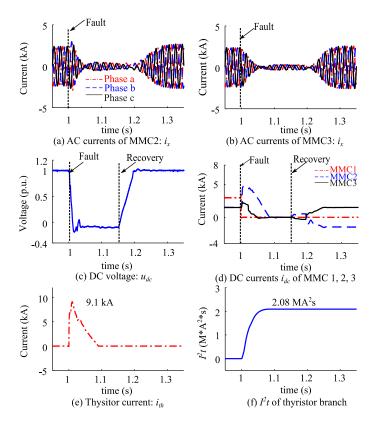

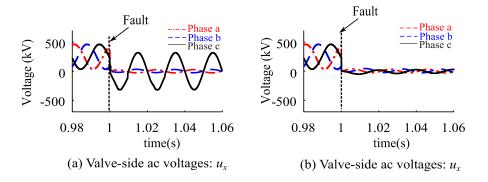

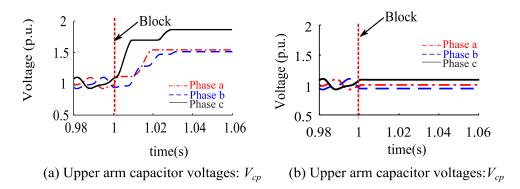

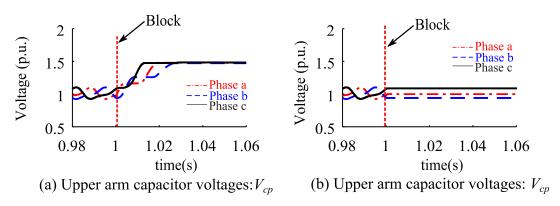

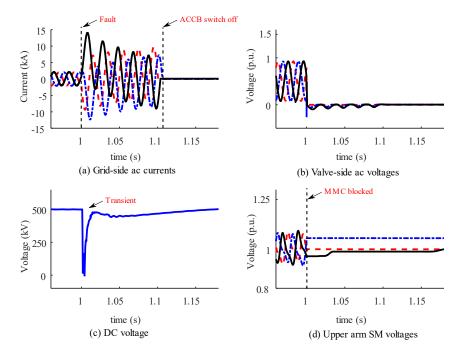

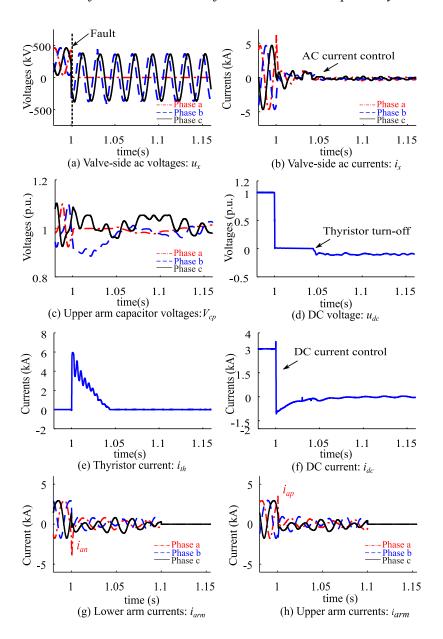

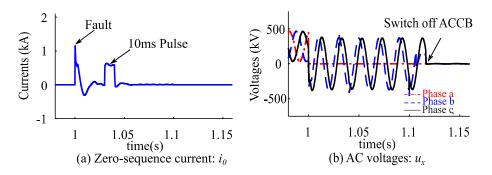

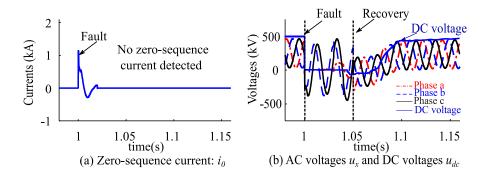

This causes a delay in the interruption of dc faults in an HVDC grid. The active resonant scheme with pre-charged circuits is proposed to reduce the interruption time. A general diagram of active MCB is shown in Fig. 2-14. The capacitors in the resonant path are pre-charged, which will speed up the process of creating zero-crossings. By this method, the time of interruption of a dc fault is reduced [123]. On the other hand, to improve the response of the mechanical switch, electromagnetic forced technology has been proposed [124]. Such schemes have been discussed in MVDC systems [125]-[127].