# Accurate Characterisation and Modelling of SiC MOSFETs for Transient Simulation

Peng Yang

School of Engineering

Cardiff University

A thesis submitted to

**Cardiff University**

for the degree of

**Doctor of Philosophy**

January 2022

### Abstract

Silicon carbide (SiC) metal-oxide-semiconductor field-effect transistors (MOSFETs) possess properties that are superior compared to their silicon counterparts, such as low conduction and switching losses, high thermal conductivity and operating temperatures, etc. SiC MOSFETs need to be evaluated either experimentally or through simulation to fully exploit or understand their benefits. Compared to experimentation, simulation is more time and cost-efficient so is preferred at the initial converter design stage. However, accurate and fast models of SiC MOSFETs need to be established for such simulation, which is challenging due to fast switching speed and frequency of SiC MOSFETs. This thesis focuses on improving the accuracy and speed of models of SiC MOSFETs and simplifying the modelling process at the same time.

Firstly, the characteristics of SiC MOSFETs required for the modelling were analysed. It was found that the I-V and C-V characteristics in their dynamic state have a significant impact on the accuracy of the models. However, the existing methods to measure and extract these characteristics are complex due to the multiple measurement equipment configurations are required. This thesis proposes a simplified dynamic-state characterisation method. This method analyses the relationship between characteristics and the switching waveforms of SiC MOSFETs, and extracts these characteristics directly from the switching waveforms measured by a double pulse tester to simplify the measurement process. These measured dynamic-state characteristics, combined with the conventional static-state characteristics, were used to built the SiC MOSFET model. The re-

lative root-mean-square (RMS) errors of the model can be reduced by at least a factor of 3, compared to the model that only considers the conventional static-state characteristics.

Based on the extracted characteristics, a measurement-based hybrid data-driven modelling method is proposed. Conventional equation-based models have drawbacks such as a complex modelling process, poor adaptability, low accuracy and slow simulation speed. The proposed modelling method utilised a hybrid data-driven model based on artificial neural networks to simplify the modelling process and improve the adaptability. The switching waveforms simulated by the proposed model are  $1.5 \sim 3$  times closer to the experimental waveforms, compared to the commercial equation-based Angelov model. At the same time, the proposed model is 30% faster than the Angelov model in terms of simulation speed.

However, equipment required for the measurement-based modelling may not be available for some converter designers, therefore, a step-by-step datasheet-based modelling method is proposed, which is completely based on the datasheet without the use of any further data or equipment. Compared to the measurement-based modelling method, the datasheet-based modelling method results in 24% increase in RMS errors and cannot accurately match the gate driver resistor used in practical experiment. However, the datasheet-based modelling method features a simpler modelling process and 15% faster simulation speed so provides a more cost and time-efficient process for converter designers to quickly validate their converter design.

# Acknowledgments

I would like to firstly express my sincere thanks to my supervisor, Prof. Jun Liang. His inspiration, advice and encouragement helped me throughout my research study. In addition, his patience and continuous guidance in improving my research ability is of great value to me and my future academic life.

I would like to express my heartfelt gratitude to my supervisor, Dr. Wenlong Ming, for his invaluable assitance, guidance and constructive criticism in conducting my research and developing this thesis. He is always available and patient to offer insightful guidance, ideas and suggestions to me.

I would like to thank my colleagues in CIREGS. Their friendship, help and encouragement made my PhD journey so enjoyable. Here, I would like to mention some of them and they are Dr. Gen Li, Dr. Sheng Wang, Dr. Chuanyue Li, Dr. Yue Zhou, Mr. Jinlei Chen, Miss Chen Li, Mr. Xun Jiang, Dr. Carlos E. Ugalde-Loo, Prof. Jianzhong Wu and Prof. Nick Jenkins.

I would like to acknowledge the financial support from the European Commission's Marie Curie InnoDC project, which provided me the best opportunity to explore and develop my career with valuable trainings. My thanks also go to other Early Stage Researchers and supervisors in InnoDC project for the interesting and useful discussions we shared during this project and also to the project manager Manon Davies for her patience dealing with our issues.

Finally, I would like to express my deepest thanks to my family for their endless encouragement, understanding, patience and support throughout my life.

# Contents

|   | Abst | tract . |                                                         | iv  |

|---|------|---------|---------------------------------------------------------|-----|

|   | Ackı | nowledg | gments                                                  | v   |

|   | List | of Tab  | les                                                     | xi  |

|   | List | of Figu | ires                                                    | xvi |

|   | Acro | onyms a | and Symbols                                             | xix |

| 1 | Intr | oducti  | ion                                                     | 1   |

|   | 1.1  | Backg   | round                                                   | 1   |

|   |      | 1.1.1   | Climate Change and Role of Power Electronics            | 1   |

|   |      | 1.1.2   | Emergence of SiC MOSFETs                                | 2   |

|   |      | 1.1.3   | Fast Switching Speed of SiC MOSFETs: Benefits and Chal- |     |

|   |      |         | lenges                                                  | 5   |

|   |      | 1.1.4   | Transient Simulation of SiC MOSFETs                     | 11  |

|   | 1.2  | Resear  | rch Motivation                                          | 12  |

|   |      | 1.2.1   | Characterisation of SiC MOSFETs                         | 13  |

|   |      | 1.2.2   | Measurement-based Modelling of SiC MOSFETs              | 14  |

|   |      | 1.2.3   | Datasheet-based Modelling of SiC MOSFETs                | 14  |

|   | 1.3  | Objec   | tives and Contributions of This Thesis                  | 15  |

|   | 1.4  | Thesis  | s Outline                                               | 17  |

|   | 1.5  | List of | f Publications                                          | 18  |

| 2 | Lite | rature  | e Review                                                | 21  |

|   | 2.1  | Opera   | tion Principle of SiC MOSFETs                           | 21  |

|   |            | 2.1.1                                                                     | Structure of SiC MOSFETs                                                                                                    | 21                                                               |

|---|------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|   |            | 2.1.2                                                                     | Forward Blocking Mode of SiC MOSFETs                                                                                        | 22                                                               |

|   |            | 2.1.3                                                                     | Forward Conduction Mode of SiC MOSFETs                                                                                      | 23                                                               |

|   |            | 2.1.4                                                                     | Capacitances of SiC MOSFETs                                                                                                 | 24                                                               |

|   |            | 2.1.5                                                                     | Switching Process of SiC MOSFETs                                                                                            | 26                                                               |

|   | 2.2        | Chara                                                                     | cterisation of SiC MOSFETs                                                                                                  | 30                                                               |

|   |            | 2.2.1                                                                     | Dynamic Characterisation                                                                                                    | 30                                                               |

|   |            | 2.2.2                                                                     | <i>I-V</i> Characterisation                                                                                                 | 34                                                               |

|   |            | 2.2.3                                                                     | C- $V$ Characterisation                                                                                                     | 38                                                               |

|   | 2.3        | Model                                                                     | ling of SiC MOSFETs                                                                                                         | 41                                                               |

|   |            | 2.3.1                                                                     | Types of SiC MOSFET Models                                                                                                  | 41                                                               |

|   |            | 2.3.2                                                                     | Behavioural Modelling of SiC MOSFETs                                                                                        | 42                                                               |

|   | 2.4        | Summ                                                                      | ary                                                                                                                         | 47                                                               |

| 3 | Sim        | plified                                                                   | Characterisation of SiC MOSFETs                                                                                             | 49                                                               |

|   |            | -                                                                         |                                                                                                                             |                                                                  |

|   | 3.1        | Introd                                                                    | uction                                                                                                                      | 49                                                               |

|   | 3.1<br>3.2 |                                                                           | uction                                                                                                                      |                                                                  |

|   |            |                                                                           |                                                                                                                             | 52                                                               |

|   |            | Conve                                                                     | ntional Static-state $I$ - $V$ and $C$ - $V$ Characterisation                                                               | 52<br>52                                                         |

|   |            | Conve<br>3.2.1<br>3.2.2                                                   | ntional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation Conventional Static-state $I\text{-}V$ Characterisation | 52<br>52                                                         |

|   | 3.2        | Conve<br>3.2.1<br>3.2.2<br>Insuffi                                        | ntional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation Conventional Static-state $I\text{-}V$ Characterisation | 52<br>52<br>54                                                   |

|   | 3.2        | Conve<br>3.2.1<br>3.2.2<br>Insuffi                                        | ntional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation Conventional Static-state $I\text{-}V$ Characterisation | <ul><li>52</li><li>52</li><li>54</li><li>57</li></ul>            |

|   | 3.2        | Conve<br>3.2.1<br>3.2.2<br>Insuffi<br>Motiva                              | ntional Static-state <i>I-V</i> and <i>C-V</i> Characterisation                                                             | <ul><li>52</li><li>52</li><li>54</li><li>57</li><li>57</li></ul> |

|   | 3.2        | Conve<br>3.2.1<br>3.2.2<br>Insuffi<br>Motive<br>3.3.1                     | Conventional Static-state <i>I-V</i> and <i>C-V</i> Characterisation                                                        | 52<br>52<br>54<br>57<br>57<br>60                                 |

|   | 3.2        | Converge 3.2.1 3.2.2 Insuffice Motive 3.3.1 3.3.2 3.3.3                   | Conventional Static-state I-V and C-V Characterisation                                                                      | 52<br>52<br>54<br>57<br>57<br>60<br>61                           |

|   | 3.2        | Converge 3.2.1 3.2.2 Insuffice Motive 3.3.1 3.3.2 3.3.3                   | Conventional Static-state I-V and C-V Characterisation                                                                      | 52<br>52<br>54<br>57<br>57<br>60<br>61<br>62                     |

|   | 3.2        | Converge 3.2.1 3.2.2 Insuffication Motive 3.3.1 3.3.2 3.3.3 DPT-1         | ntional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation Conventional Static-state $I\text{-}V$ Characterisation | 52<br>52<br>54<br>57<br>57<br>60<br>61<br>62                     |

|   | 3.2        | Converge 3.2.1 3.2.2 Insuffice Motive 3.3.1 3.3.2 3.3.3 DPT-1 3.4.1 3.4.2 | Conventional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation                                                    | 52<br>52<br>54<br>57<br>57<br>60<br>61<br>62<br>64<br>68         |

|   | 3.3        | Converge 3.2.1 3.2.2 Insuffice Motive 3.3.1 3.3.2 3.3.3 DPT-1 3.4.1 3.4.2 | ntional Static-state $I\text{-}V$ and $C\text{-}V$ Characterisation Conventional Static-state $I\text{-}V$ Characterisation | 52<br>52<br>54<br>57<br>57<br>60<br>61<br>62<br>64<br>68<br>70   |

|   | 3.6 | DPT-    | based Measurement of $C_{GD}$ Characteristics                      | 3          |

|---|-----|---------|--------------------------------------------------------------------|------------|

|   |     | 3.6.1   | Analysis of Turn-off Process and On-state $C_{GD}$                 | <b>'</b> 4 |

|   |     | 3.6.2   | Analysis of Turn-off Process and Dynamic $C_{GD}$                  | '5         |

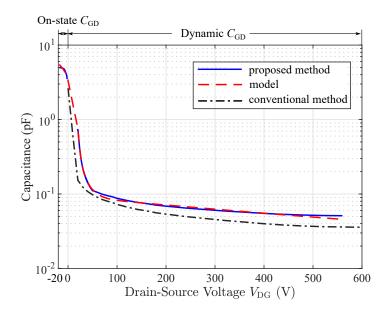

|   |     | 3.6.3   | Measurement Results of On-state and Dynamic $C_{GD}$               | <b>'</b> 6 |

|   | 3.7 | Summ    | nary                                                               | '8         |

| 4 | Mea | asuren  | nent-based Accurate Modelling of SiC MOSFETs 8                     | 0          |

|   | 4.1 | Introd  | luction                                                            | 30         |

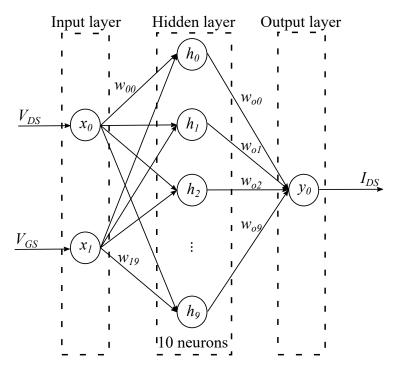

|   | 4.2 | Revie   | w of the Existing ANN Model                                        | 3          |

|   |     | 4.2.1   | Structure of Artificial Neural Network                             | 34         |

|   |     | 4.2.2   | Limitations of the Existing ANN Model                              | 35         |

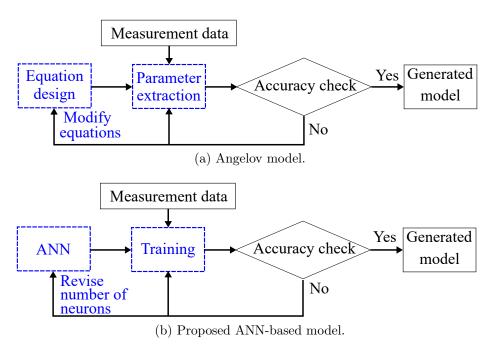

|   | 4.3 | Propo   | sed Hybrid Modelling Methodology for Transient Simulation . 8      | ;7         |

|   |     | 4.3.1   | Data-driven Modelling of $I\text{-}V$ Characteristics in the Whole |            |

|   |     |         | $V_{DS}$ Region                                                    | 8          |

|   |     | 4.3.2   | Hybrid Modelling with Behaviour-based Model for Cutoff             |            |

|   |     |         | Region                                                             | 39         |

|   |     | 4.3.3   | Modelling of $C$ - $V$ Characteristics                             | 12         |

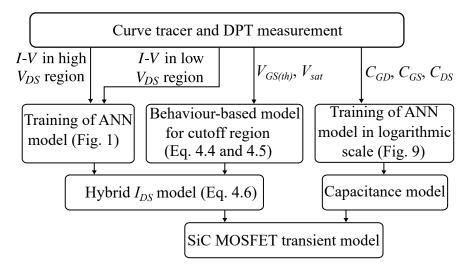

|   |     | 4.3.4   | Modelling Flowchart and Neural Network Selection 9                 | 13         |

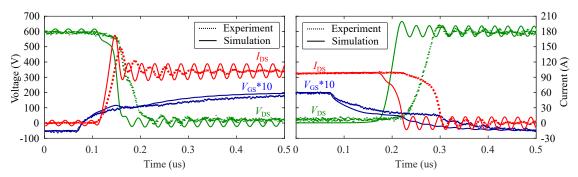

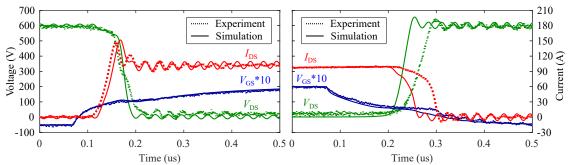

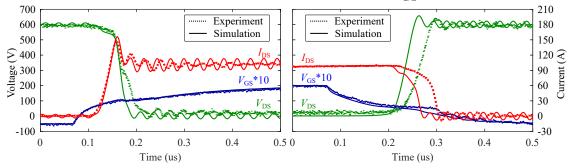

|   | 4.4 | Exper   | imental Model Verification                                         | 17         |

|   | 4.5 | Comp    | arisons with Angelov Model                                         | 0          |

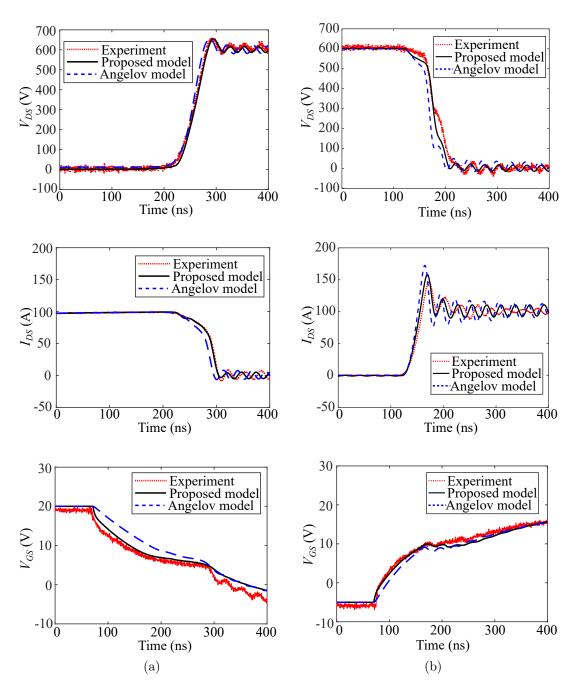

|   |     | 4.5.1   | Model Accuracy                                                     | 12         |

|   |     | 4.5.2   | Computation Time                                                   | 13         |

|   |     | 4.5.3   | Model Adaptability                                                 | 15         |

|   |     | 4.5.4   | Modelling Process                                                  | 17         |

|   | 4.6 | Verific | eation of Proposed DPT-based Measurement Method 10                 | 18         |

|   |     | 4.6.1   | Experimental Verification                                          | 18         |

|   |     | 4.6.2   | Comparison with Conventional Measurement Method 11                 | 2          |

|   | 17  | Summ    | nary 11                                                            | 2          |

| 5            | Dat   | asheet | -based Fast Modelling of SiC MOSFETs                         | 114   |

|--------------|-------|--------|--------------------------------------------------------------|-------|

|              | 5.1   | Introd | uction                                                       | 114   |

|              | 5.2   | Model  | Description                                                  | 117   |

|              |       | 5.2.1  | $I_{DS}$ Model                                               | . 117 |

|              |       | 5.2.2  | Diode Model                                                  | 118   |

|              |       | 5.2.3  | Capacitance Models                                           | 119   |

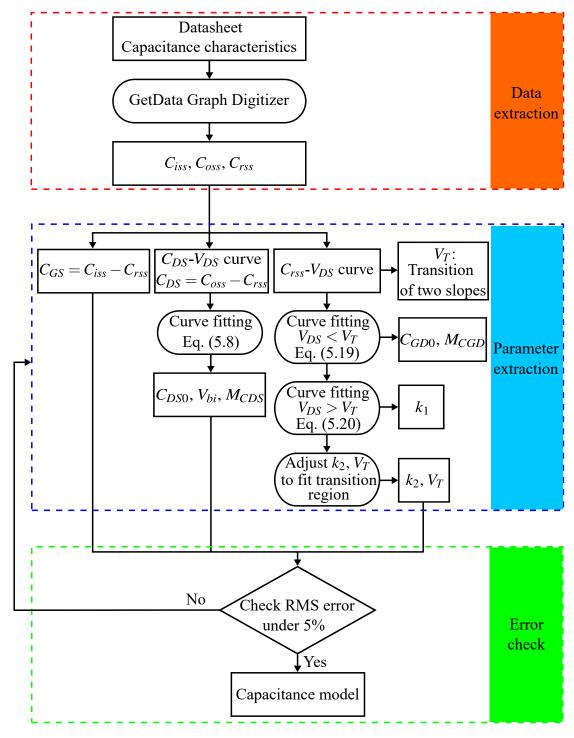

|              | 5.3   | Step-b | y-step Modelling Approach                                    | 119   |

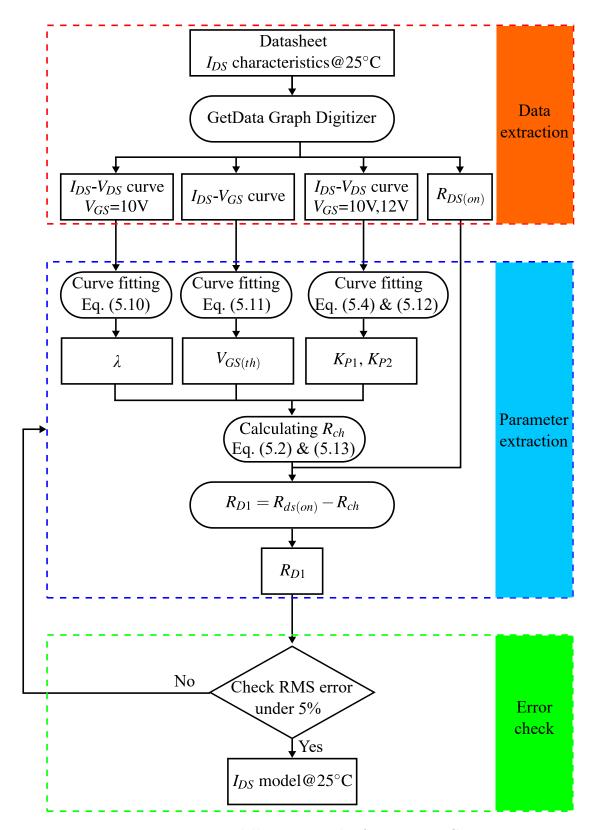

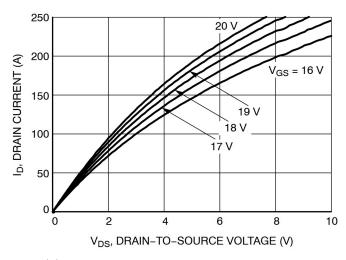

|              |       | 5.3.1  | Modelling Approach of $I_{DS}$ at 25 °C                      | . 119 |

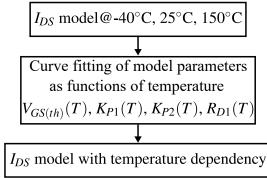

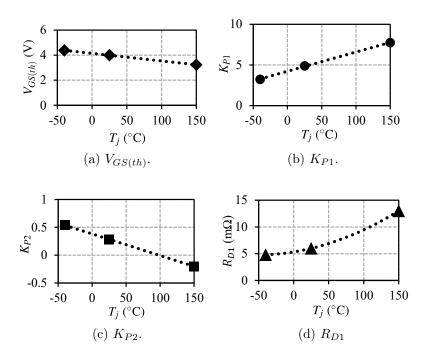

|              |       | 5.3.2  | Modelling Approach of $I_{DS}$ with Temperature Dependency . | . 124 |

|              |       | 5.3.3  | Modelling Approach of Diode                                  | . 127 |

|              |       | 5.3.4  | Modelling Approach of Parasitic Capacitors                   | 129   |

|              | 5.4   | Model  | Verification                                                 | 132   |

|              | 5.5   | Compa  | arison with Measurement-based Modelling Method               | 137   |

|              |       | 5.5.1  | Complexity                                                   | 137   |

|              |       | 5.5.2  | Accuracy                                                     | 138   |

|              |       | 5.5.3  | Gate Driver Resistor                                         | 139   |

|              |       | 5.5.4  | Comparison Results                                           | 140   |

|              | 5.6   | Summ   | ary                                                          | 140   |

| 6            | Con   | clusio | ns and Future Work                                           | 143   |

|              | 6.1   | Conclu | ısions                                                       | 143   |

|              |       | 6.1.1  | Simplified Characterisation of SiC MOSFETs                   | . 143 |

|              |       | 6.1.2  | Measurement-Based Accurate Modelling of SiC MOSFETs .        | . 144 |

|              |       | 6.1.3  | Datasheet-based Fast Modelling of SiC MOSFETs                | . 145 |

|              | 6.2   | Future | e Work                                                       | 146   |

|              |       | 6.2.1  | Characterisation and Modelling of Temperature Dependency     | 146   |

|              |       | 6.2.2  | Verification and Application of Models in Converter Design . | . 147 |

|              |       | 6.2.3  | Development of Modelling Tools with User Interface           | . 148 |

| $\mathbf{R}$ | efere | nces   |                                                              | 148   |

# List of Tables

| 3.1 | Relative RMS errors of simulated switching waveforms 69                  |

|-----|--------------------------------------------------------------------------|

| 4.1 | Switching characteristics simulated by the proposed model 101            |

| 4.2 | Switching characteristics simulated by the Angelov model 101             |

| 4.3 | Relative RMS errors of switching transients                              |

| 4.4 | Relative RMS errors of $C\text{-}V$ and $I\text{-}V$ characteristics 103 |

| 4.5 | Computation time of the proposed model and Angelov model $105$           |

| 4.6 | Relative RMS errors of switching transients                              |

| 5.1 | Extracted $K_p$ with different $V_{GS}$                                  |

| 5.2 | Parameters of $I_{DS}$ at 25 °C                                          |

| 5.3 | Parameters of diode model                                                |

| 5.4 | Parameters of capacitance model                                          |

| 5.5 | Computation time of the proposed measurement-based and datasheet-        |

|     | based models                                                             |

| 5.6 | Relative RMS errors of switching transients                              |

| 5.7 | Advantages and disadvantages of the proposed measurement-based           |

|     | and datasheet-based modelling methods                                    |

# List of Figures

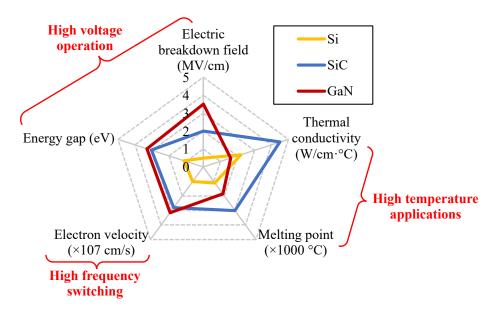

| 1.1  | Comparison of Si, SiC and GaN relevant material properties                       | 3  |

|------|----------------------------------------------------------------------------------|----|

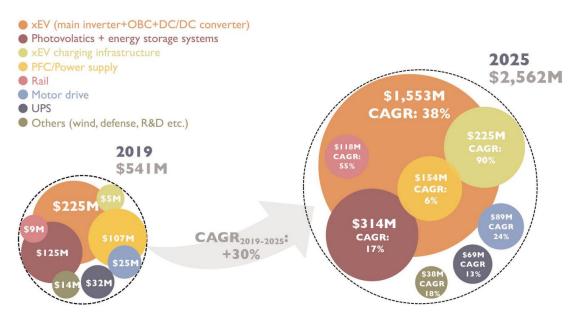

| 1.2  | 2019-2025 market forecast of SiC power semiconductor split by ap-                |    |

|      | plication                                                                        | 4  |

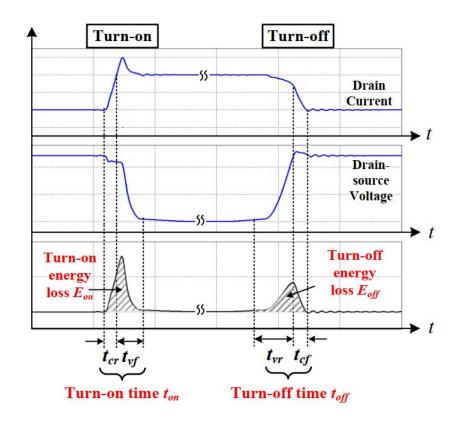

| 1.3  | Switching waveform of power semiconductors                                       | 6  |

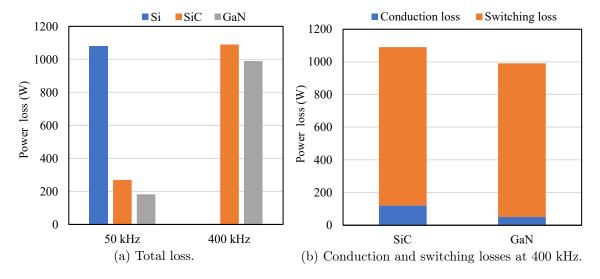

| 1.4  | Comparison of power loss of different power semiconductors                       | 6  |

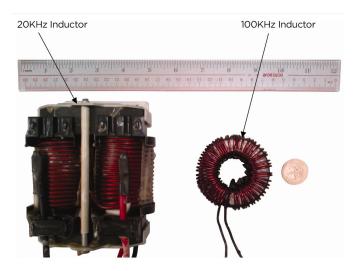

| 1.5  | $5~\mathrm{kW}$ filter inductors at switching frequencies of 20 kHz and 100 kHz. | 8  |

| 1.6  | Measured EMI spectra of Si-based and SiC-based inverters                         | 10 |

| 1.7  | Counteracting effects of key performance indicators of power elec-               |    |

|      | tronics [1]                                                                      | 11 |

| 1.8  | Virtual prototyping and multi-objective optimisation of power elec-              |    |

|      | tronics based on characterisation and modelling of SiC MOSFETs                   | 13 |

| 2.1  | Two typical structures of SiC MOSFETs                                            | 22 |

| 2.2  | Illustration of the forward blocking mode of SiC MOSFETs                         | 23 |

| 2.3  | Forward conduction mode of SiC MOSFETs                                           | 24 |

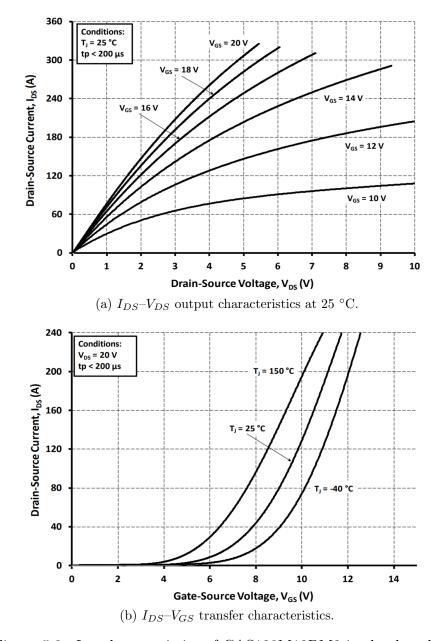

| 2.4  | $\emph{I-V}$ characteristics of SiC MOSFET power module CAS120M12BM2.            | 24 |

| 2.5  | Capacitances within SiC MOSFETs                                                  | 25 |

| 2.6  | Double pulse tester to evaluate the switching process of the SiC                 |    |

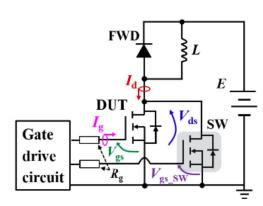

|      | MOSFET                                                                           | 27 |

| 2.7  | Switching process of the SiC MOSFET                                              | 28 |

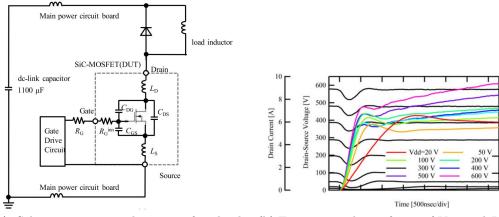

| 2.8  | DPT setup                                                                        | 30 |

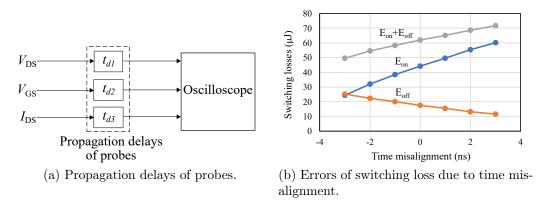

| 2.9  | Time misalignment of dynamic characterisation                                    | 33 |

| 2.10 | The B1505A power device analyser/curve tracer                                    | 34 |

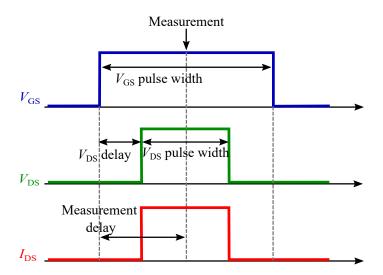

| 2.11 | Pulsed waveforms and measurement timing for 1-v characterisation.                        | 33 |

|------|------------------------------------------------------------------------------------------|----|

| 2.12 | Load-short-circuit-switching test for $I\text{-}V$ characterisation in high              |    |

|      | $V_{DS}$ region                                                                          | 36 |

| 2.13 | Turn-on waveforms of the SiC MOSFET for $I\text{-}V$ characterisation                    |    |

|      | in high $V_{DS}$ region                                                                  | 37 |

| 2.14 | Modified DPT for $I$ - $V$ characterisation in high $V_{DS}$ region                      | 37 |

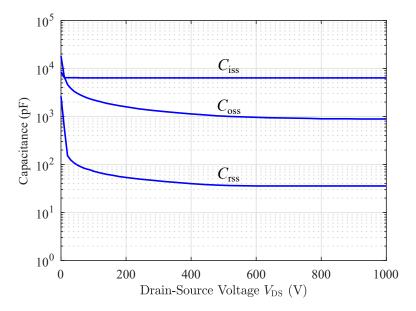

| 2.15 | C-V characteristics of SiC MOSFET power module CAS120M12BM2.                             | 39 |

| 2.16 | On resistance and capacitances within the SiC MOSFETs                                    | 43 |

| 2.17 | Equivalent circuit model of the SiC MOSFET                                               | 43 |

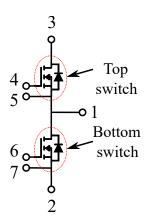

| 3.1  | Half-bridge configuration of SiC power module CAS120M12BM2. $$ .                         | 50 |

| 3.2  | Configuration of a B1505A curve tracer to measure $I\text{-}V$ character-                |    |

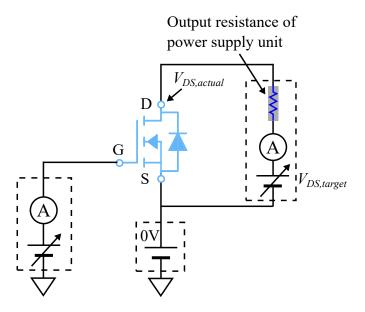

|      | istics                                                                                   | 53 |

| 3.3  | $\emph{I-V}$ characteristics of SiC power module CAS120M12BM2 at 25 °C.                  | 54 |

| 3.4  | Test setups and AC equivalent circuits of the conventional $C\text{-}V$                  |    |

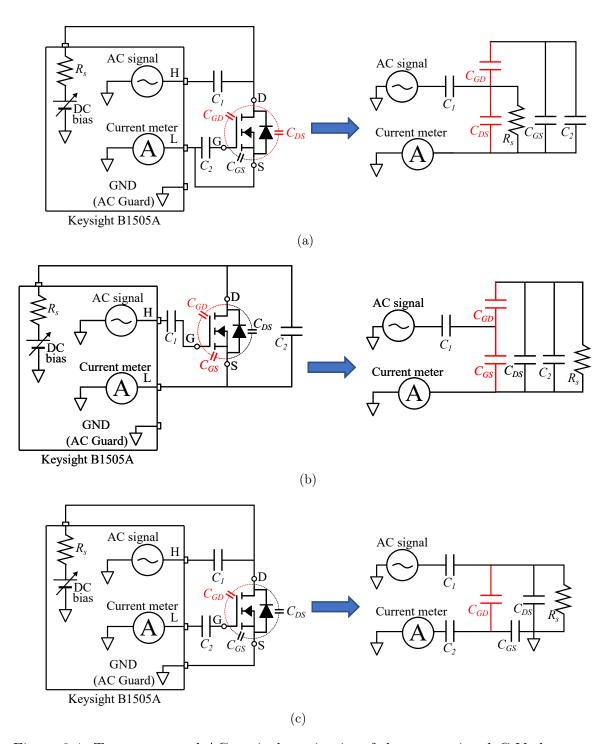

|      | characterisation using Keysight B1505A                                                   | 56 |

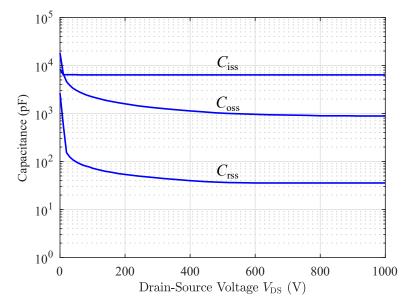

| 3.5  | C-V characteristics of SiC MOSFET power module CAS120M12BM2.                             | 57 |

| 3.6  | MOS structure and characteristics of gate-source capacitor $C_{GS}$                      | 59 |

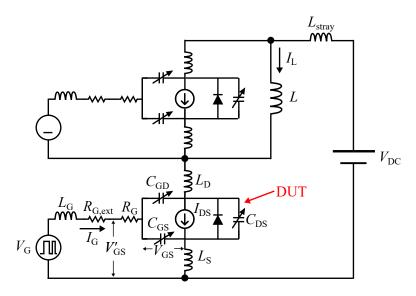

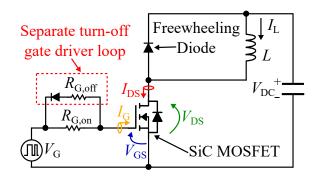

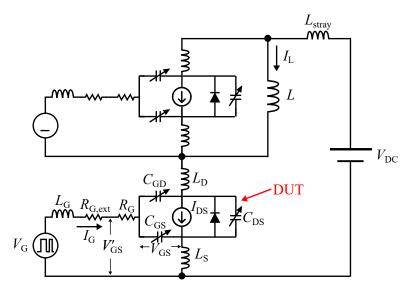

| 3.7  | Circuit diagram of the double pulse tester                                               | 62 |

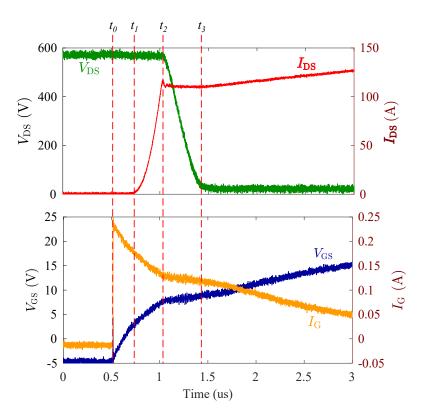

| 3.8  | Turn-on waveforms measured by the DPT with $R_{G,ext}=100\Omega.$                        | 63 |

| 3.9  | Turn-off waveforms measured by the DPT with $R_{G,ext} = 100 \Omega.$                    | 63 |

| 3.10 | Circuit diagram of the double pulse tester                                               | 65 |

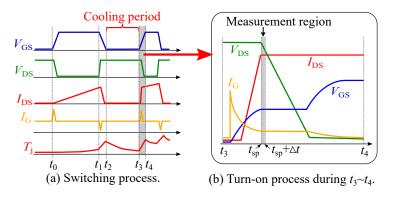

| 3.11 | The switching process and self-heating of the SiC MOSFET in DPT. $$                      | 65 |

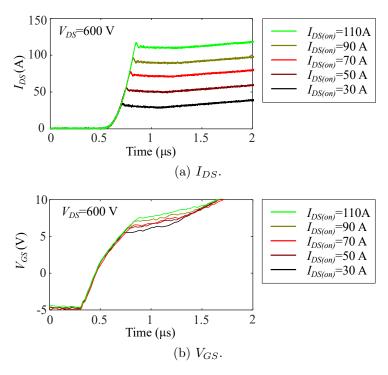

| 3.12 | Turn-on waveforms of $I_{DS}$ and $V_{GS}$ with different turn-on current                |    |

|      | under $V_{DC} = 600 \text{ V.}$                                                          | 66 |

| 3.13 | DPT waveforms for measuring HVHC $I_{DS}\text{-}V_{DS}$ characteristics with             |    |

|      | $V_{DS} = 600 \text{V}$ and $I_{DS} = 120 \text{A.} \dots \dots \dots \dots \dots \dots$ | 67 |

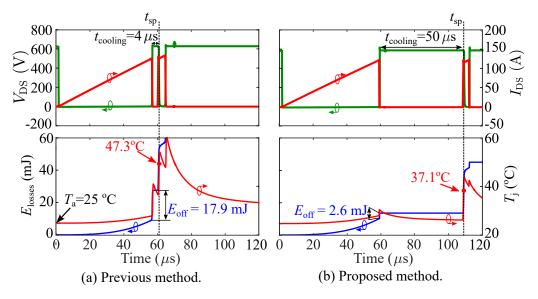

| 3.14 | $I_{DS}$ - $V_{DS}$ characteristics in the high $V_{DS}$ region measured by the (a)      |    |

|      | previous and (b) proposed method                                                         | 68 |

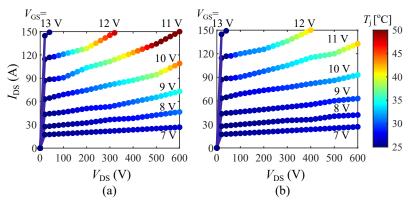

| 3.15 | Measured $I_{DS}$ - $V_{CS}$ characteristics at $V_{DS} = 600 \mathrm{V}$                | 69 |

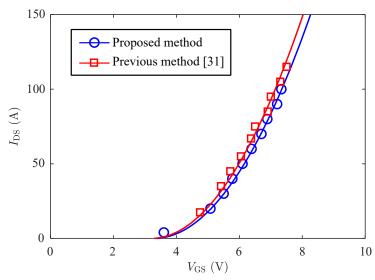

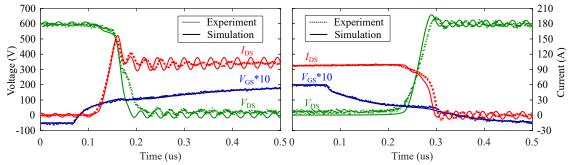

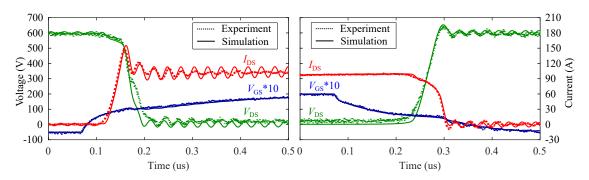

| 3.16 | The measured and simulated switching waveforms. Dashed and                     |    |

|------|--------------------------------------------------------------------------------|----|

|      | solid lines denote the experimental and simulated waveforms, re-               |    |

|      | spectively. (a) Turn on by conventional model. (b) Turn off by                 |    |

|      | conventional model. (c) Turn on by proposed model. (d) Turn off                |    |

|      | by proposed model                                                              | 70 |

| 3.17 | Circuit diagram of the double pulse tester                                     | 71 |

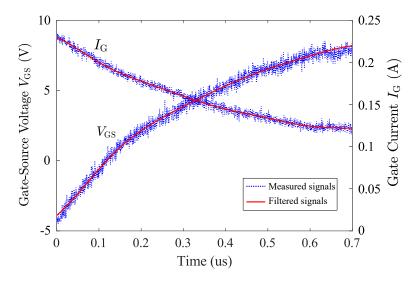

| 3.18 | Turn-on waveforms $(t_0 \sim t_2)$ filtered by artificial neural networks      |    |

|      | (ANNs)                                                                         | 73 |

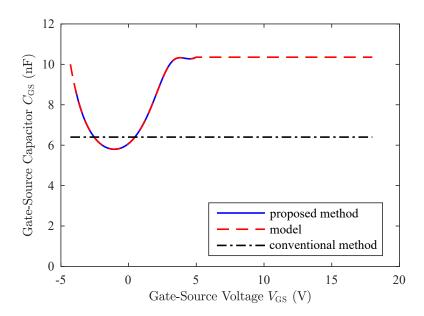

| 3.19 | Calculated $C_{GS}$ - $V_{GS}$ characteristics based on DPT measurement        | 74 |

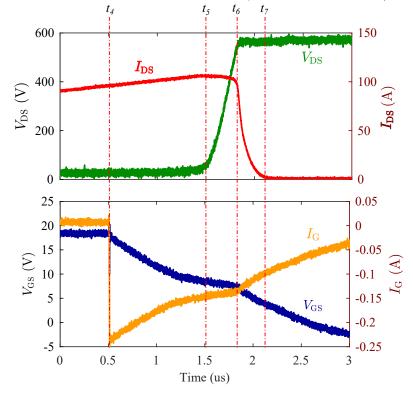

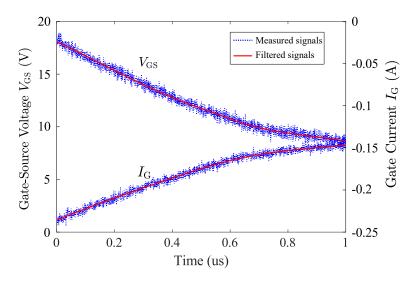

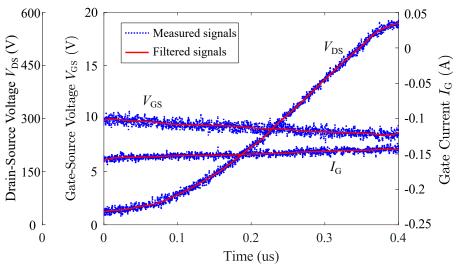

| 3.20 | Turn-off waveforms $(t_4 \sim t_5)$ filtered by ANNs                           | 77 |

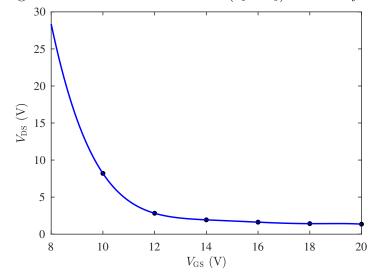

| 3.21 | $V_{DS}$ - $V_{GS}$ curve with $I_{DS} = 100 \mathrm{A.}$                      | 77 |

| 3.22 | Turn-off waveforms $(t_5 \sim t_6)$ filtered by ANNs                           | 77 |

| 3.23 | Modeling of $C_{GD}$ - $V_{DG}$ characteristics                                | 78 |

| 4.1  | ANN topology.                                                                  | 84 |

| 4.2  | Existing ANN model that is trained with measured $I-V$ character-              |    |

|      | istics in a low $V_{DS}$ region                                                | 86 |

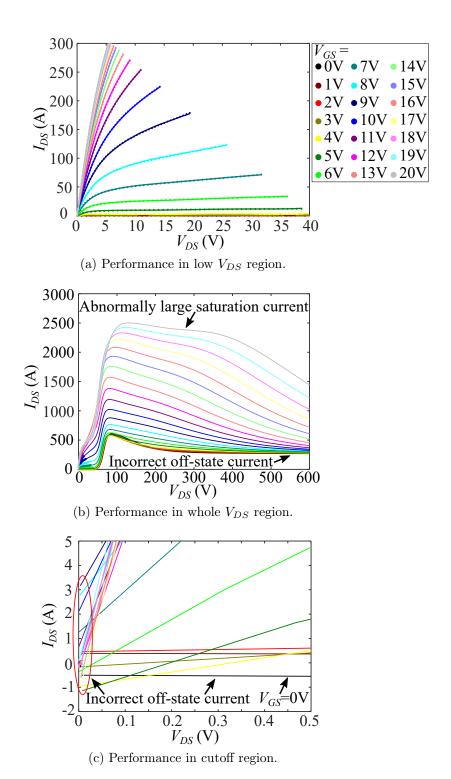

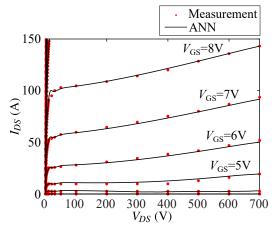

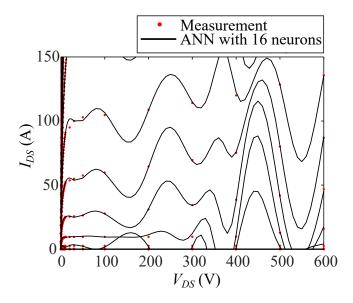

| 4.3  | ANN model trained with $I$ - $V$ characteristics in whole $V_{DS}$ region      | 90 |

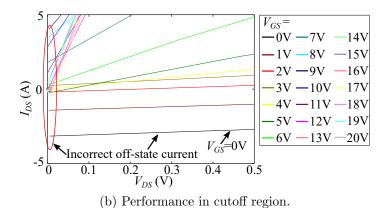

| 4.4  | Performance of the proposed hybrid modelling methodology                       | 92 |

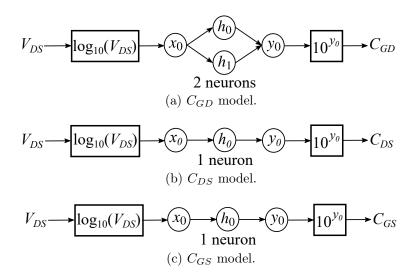

| 4.5  | ANN capacitance models trained in logarithmic scale                            | 93 |

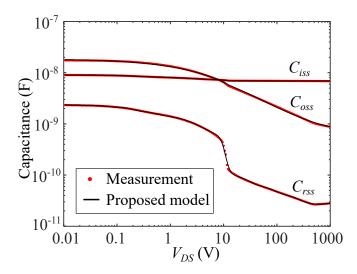

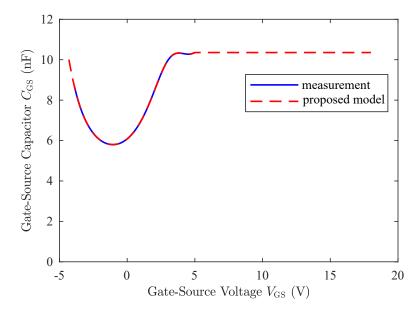

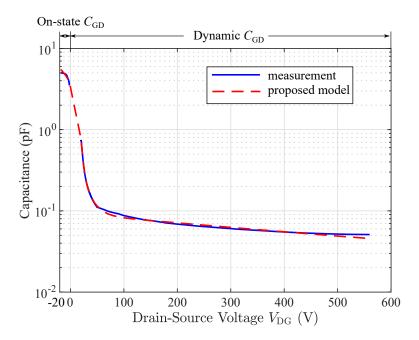

| 4.6  | Results of ANN capacitance models trained in logarithmic scale                 | 94 |

| 4.7  | Modelling of the nonlinear $C_{GS}$ - $V_{GS}$ characteristics measured by the |    |

|      | proposed DPT-based measurement method                                          | 94 |

| 4.8  | Modelling of on-state and dynamic $C_{GD}$ - $V_{DG}$ characteristics meas-    |    |

|      | ured by the proposed DPT-based measurement method                              | 95 |

| 4.9  | Flowchart of the proposed hybrid modelling methodology                         | 95 |

| 4.10 | Overfitting of ANN with excessive hidden neurons                               | 96 |

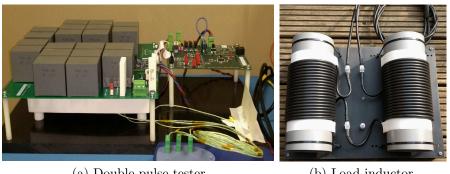

| 4.11 | Experimental setup                                                             | 97 |

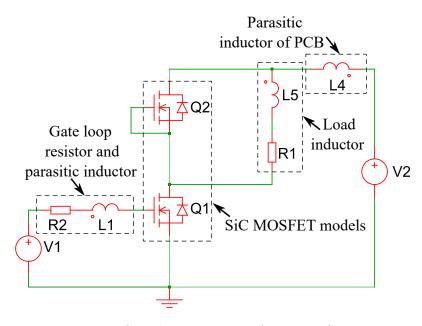

| 4.12 | Simulation circuit of DPT in SIMetrix                                          | 97 |

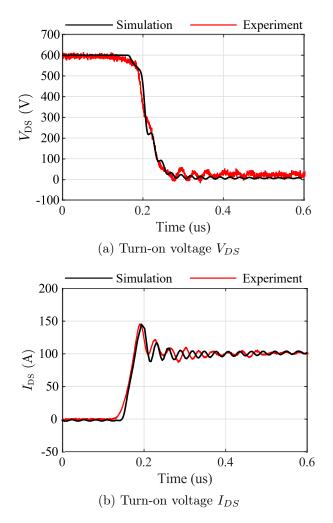

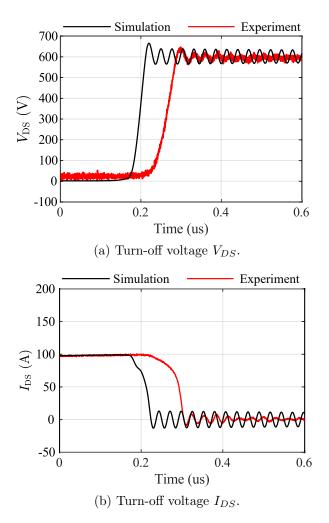

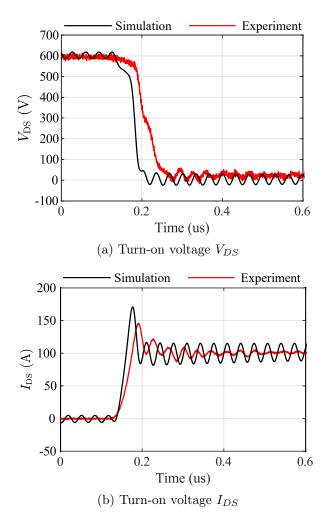

| 4.13 | Measured and simulated (a) turn-off and (b) turn-on transients                 | 98 |

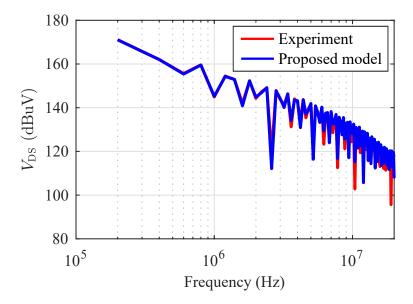

| 4.14          | Comparison of Drain-Source voltage spectra of experimental and                |

|---------------|-------------------------------------------------------------------------------|

|               | simulation results for EMI analysis                                           |

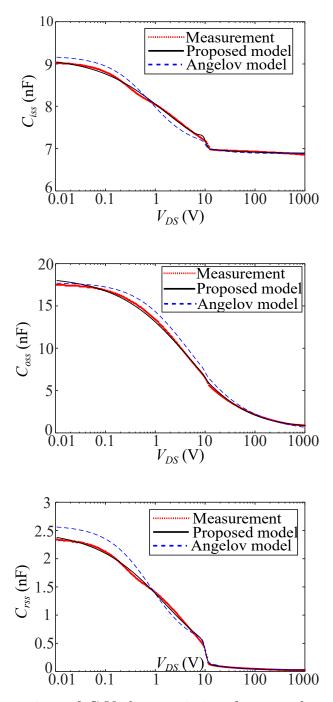

| 4.15          | Comparison of $C\text{-}V$ characteristics of proposed model and Angelov      |

|               | model                                                                         |

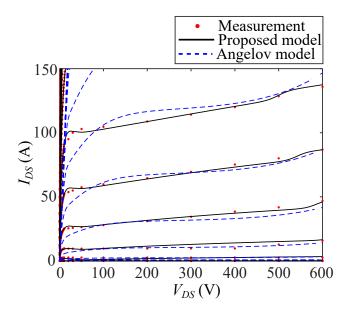

| 4.16          | Comparison of $I\text{-}V$ characteristics of proposed model and Angelov      |

|               | model                                                                         |

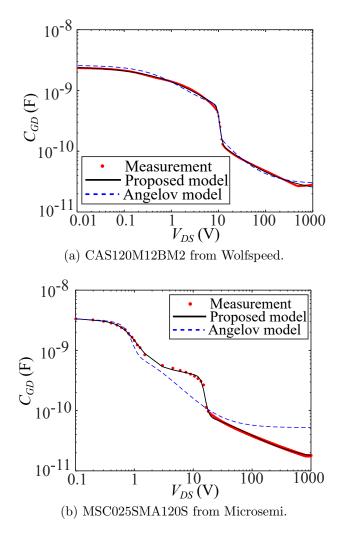

| 4.17          | Simulated and measured $C_{GD}$ characteristics of two different devices. 106 |

| 4.18          | Modelling processes of Angelov and proposed ANN-based model 107               |

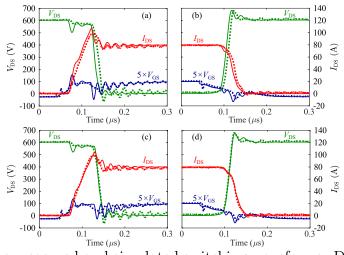

| 4.19          | Simulated and experimental turn-on (left) and turn-off (right) wave-          |

|               | forms. The device is modelled based on the datasheet 109                      |

| 4.20          | Simulated and experimental turn-on (left) and turn-off (right) wave-          |

|               | forms. The device is modelled with measured nonlinear $C_{GS}$ 109            |

| 4.21          | Simulated and experimental turn-on (left) and turn-off (right) wave-          |

|               | forms. The device is modelled with measured nonlinear $C_{GS}$ and            |

|               | $I-V$ characteristics in the high $V_{DS}$ region                             |

| 4.22          | Simulated and experimental turn-on (left) and turn-off (right) wave-          |

|               | forms. The device is modelled with measured nonlinear $C_{GS}$ , $I\text{-}V$ |

|               | characteristics in the high $V_{DS}$ region and on-state $C_{GD}$ 109         |

| 4.23          | Simulated and experimental turn-on (left) and turn-off (right) wave-          |

|               | forms. The device is modelled with all measured characteristics $110$         |

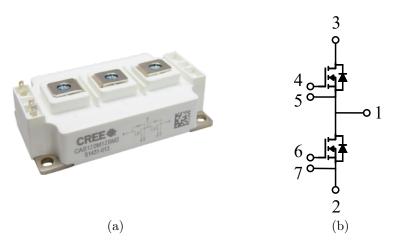

| 5.1           | A 1200-V 120-A SiC half-bridge power module CAS120M12BM2 116                  |

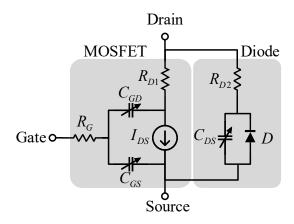

| 5.2           | Subcircuit model of a pair of SiC MOSFET and anti-parallel diode              |

|               | in the power module                                                           |

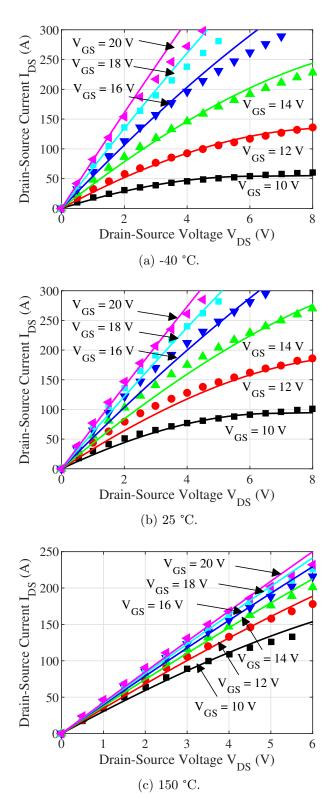

| 5.3           | $I_{DS}$ characteristics of CAS120M12BM2 in the datasheet 120                 |

| 5.4           | Modelling approach of $I_{DS}$ at 25 °C                                       |

| 5.5           | Modelling approach of $I_{DS}$ with temperature dependency 124                |

| 5.6           | Temperature dependency of model parameters                                    |

| $\overline{}$ | - romporatare dependency of moder parameters                                  |

| 5.7  | $I_{DS}$ - $V_{DS}$ characteristics at different temperatures compared to data- |

|------|---------------------------------------------------------------------------------|

|      | sheet. The coloured dots denote the results from the datasheet. The             |

|      | coloured lines denote the results from the model                                |

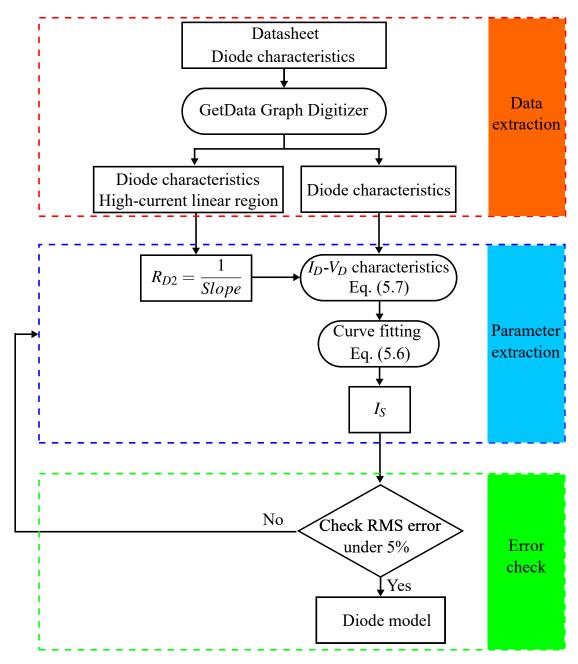

| 5.8  | Modelling approach of diode                                                     |

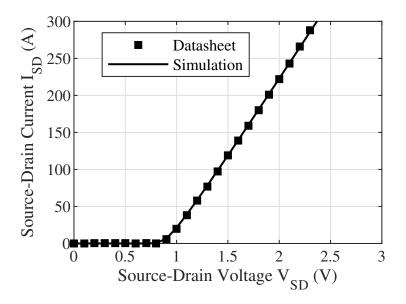

| 5.9  | Diode characteristics compared to datasheet                                     |

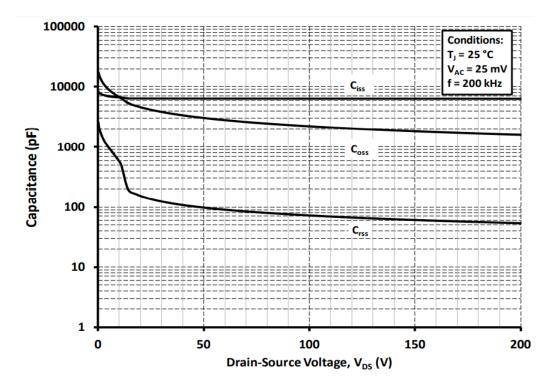

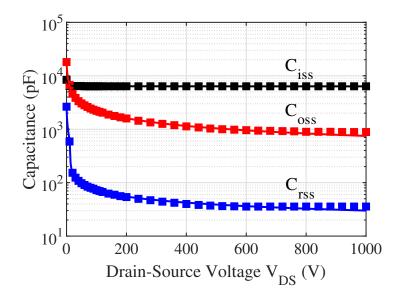

| 5.10 | Capacitance characteristics of CAS120M12BM2 in the data<br>sheet. $$ . 130      |

| 5.11 | Modelling approach of parasitic capacitors                                      |

| 5.12 | Capacitance characteristics compared to datasheet. The coloured                 |

|      | dots denote the results from the datasheet. The coloured lines de-              |

|      | note the results from the model                                                 |

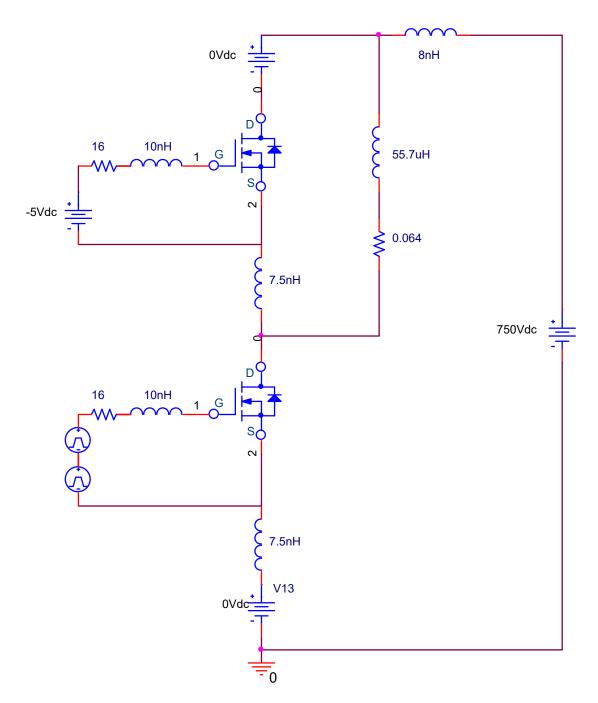

| 5.13 | Simulation circuit of DPT in PSpice                                             |

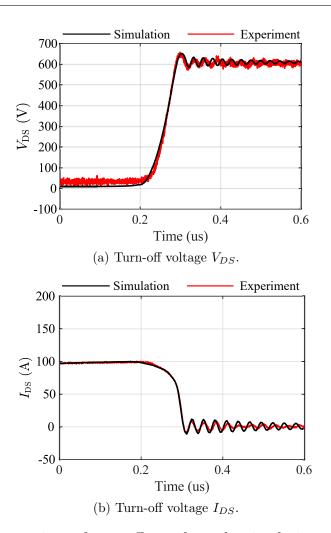

| 5.14 | Comparison of turn-off waveforms by simulation and experiment. $$ . 134         |

| 5.15 | Comparison of turn-on waveforms by simulation and experiment $135$              |

| 5.16 | Comparison of $I\text{-}V$ characteristics in two data<br>sheets                |

| 5.17 | Simulated turn-off waveforms of the datasheet-based model with a                |

|      | gate driver resistor of $10\Omega.$                                             |

| 5.18 | Simulated turn-on waveforms of the datasheet-based model with a                 |

|      | gate driver resistor of $10 \Omega$                                             |

# Acronyms and Symbols

#### Acronyms

AI Artificial Intelligence

ANN Artificial Neural Network

CAGR Compound Annual Growth Rate

DPT Double Pulse Tester

DUT Device Under Test

EMI Electromagnetic Interference

EV Electric Vehicle

GaN Gallium Nitride

GHG Greenhouse Gas

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

RMS Root Mean Square

SiC Silicon Carbide

Si Silicon

VNA Vector Network Analyser

WBG Wide Bandgap

#### **Symbols**

$C_{DS}$  drain-source capacitance

$C_{GD}$  gate-drain capacitance

$C_{GS}$  gate-source capacitance

$C_{iss}$  input capacitance

$C_{oss}$  output capacitance

$C_{rss}$  reverse transfer capacitance

di/dt current rate-of-change

dv/dt voltage rate-of-change

$E_{off}$  the turn-off loss of SiC MOSFET

$E_{on}$  the turn-on loss of SiC MOSFET

$I_G$  gate current

$I_L$  load current

$I_{DS}$  drain-source current

$K_p$  transconductance coefficient of datasheet-based model

$\lambda$  coefficient of short-channel effect of the datasheet-based model

$R_G$  gate resistor

$R_{CH}$  channel resistance

$R_{DRIFT}$  the resistance of the drift region

$R_{JFET}$  the resistance of the JFET region

$R_{on}$  on resistance

$R_{SUB}$  the resistance of the substrate

$T_j$  junction temperature

$t_{off}$  the turn-off time of SiC MOSFET

$t_{on}$  the turn-on time of SiC MOSFET

$V_{DC}$  dc-bus voltage

$V_{DG}$  drain-gate voltage

$V_{DS}$  drain-source voltage

$V_{GP}$  gate plateau voltage

$V_{GS,th}$  threshold voltage

$V_{GS}$  drain-source voltage

# Chapter 1

## Introduction

#### 1.1 Background

#### 1.1.1 Climate Change and Role of Power Electronics

Global climate change is one of the biggest environmental challenges facing the world. Greenhouse gas (GHG) emission from human activities is a significant and dominant cause of climate change, resulting in temperature rise, melting glaciers, drought, wildfires, etc. [2].

Worldwide efforts have been made in fighting climate change. The Paris Agreement, a legally binding global climate change agreement adopted at Paris climate conference (COP21) in December 2015, has set out a global framework to avoid dangerous climate change by limiting global warming to well below 2 °C and pursuing efforts to limit it to 1.5 °C [3]. To achieve the goals of Paris Agreement, the European Union (EU) has announced the European Green Deal in December 2019, setting out an overarching objective for the EU to become climate neutral (i.e., net zero GHG emissions) by 2050, with an intermediate target of reducing net GHG emissions by at least 55% by 2030, compared to 1990 levels [4]. The UK government has also committed to cutting GHG emissions by 78% by 2035 compared to 1990 levels, and achieving net zero GHG emissions by 2050 [5].

To assist the government to deliver these goals, in energy and transport sectors,

a substantial increase in using renewable energy sources (e.g. wind energy, solar energy, etc.) and electric vehicles (EVs) is required. The UK government plans to increase its offshore wind capacity from 30 GW to 40 GW by 2030. Besides, sales of new petrol and diesel cars and vans will be banned by 2030 in UK to accelerate the transition from internal combustion engine vehicles to EVs [6].

Power electronics play a crucial role in the development of renewable energy sources and EVs. Most renewable energy sources rely on power electronics to regulate the voltage, frequency and power so that they can be connected to the power grid. In EVs, power electronics are indispensable to convert DC power from the battery into AC power to drive the motor or to convert AC power from the grid into DC power to charge the battery.

For their application in renewable energy sources and EVs, the development of power electronics has a continuous trend towards higher power density and higher efficiency. The development of power semiconductors is a crucial enabling factor to achieve these targets. Today's power semiconductors are still dominated by the mature and well-established silicon (Si) technology. In low voltage applications below 600 V, Si MOSFETs dominate the market, whereas Si insulated gate bipolar transistors (IGBTs) dominate the high voltage market from 600 V to 6.5 kV. However, after decades of development, Si power semiconductors are approaching their material theoretical limitations which become a barrier to the further improvement of power electronics. For high voltage applications, the maximum blocking voltage of the Si IGBT is lower than 6.5 kV, and the practical operating temperature is lower than 175 °C. Besides, in the bipolar structure of IGBTs, the switching speed is relatively slow due to the slow carrier velocity of holes, limiting the efficiency and switching frequency of power electronics [7].

#### 1.1.2 Emergence of SiC MOSFETs

Since Si-based power semiconductors are facing a bottleneck, the emerging power semiconductors based on wide-bandgap (WBG) materials are drawing the atten-

Figure 1.1: Comparison of Si, SiC and GaN relevant material properties [9].

tion due to their superior properties far beyond the limitations of their Si counterparts. These materials include silicon carbide (SiC), gallium nitride (GaN), gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), diamond, etc. Among the possible candidates of WBG materials, silicon carbide (SiC) and gallium nitride (GaN) are the most popular ones due to the best trade-off between theoretical characteristics, commercial availability and technological maturity [8]. Ga<sub>2</sub>O<sub>3</sub> and diamond have even wider bandgap than SiC and GaN, which are promising to achieve better performance. However, semiconductors based on Ga<sub>2</sub>O<sub>3</sub> and diamond still have very low technical readiness level so they are not focused by this thesis. Fig. 1.1 highlights some key material properties of SiC and GaN compared to Si [9]. It is shown that the energy gap, electric breakdown field, thermal conductivity, melting point and electron velocity of WBG materials are significantly higher than those of Si. These advantages allow WBG semiconductors to operate at much higher voltage, temperature and switching frequency than Si semiconductors. Compared to GaN semiconductors, in today's market, SiC semiconductors presents more advantages in high-voltage high-power (600 V, kilowatts or above) applications [10].

Due to their superior properties, the market of SiC semiconductors is predicted to grow very quickly in the next few years. As shown in Fig. 1.2, a compound annual growth rate (CAGR) of 30%, from \$225m in 2019 to \$2.5bn in

Figure 1.2: 2019-2025 market forecast of SiC power semiconductor split by application (CAGR: compound annual growth rate) [11].

2025, is estimated according to a report by Yole Development [11]. The adoption of SiC semiconductors covers a wide range of industrial applications including EVs, photovaltics, energy storage systems, power supply, motor driver, etc.

Among SiC semiconductors, SiC MOSFETs are the most developed active switches in the market. Since the breakdown field of SiC is 10 times higher than that of Si, SiC MOSFETs with ultra-high-voltage ratings (>10 kV) are practically achievable. Currently, SiC MOSFETs rated at 1.2 kV [12], 1.7 kV [13] and 3.3 kV [14] are commercially available, which can replace the Si insulated gate bipolar transistors (IGBTs) at the same voltage ratings. Wolfspeed has released the 10 kV SiC MOSFETs beyond the maximum voltage rating of 6.5 kV IGBTs and there are some laboratory research works on it [15]. The high breakdown voltage of SiC MOSFETs is attractive to reduce the complexity and increase the reliability of power electronics in high voltage applications.

Owing to the much wider energy bandgap of SiC materials, SiC MOSFETs can theoretically operate at temperatures beyond 500 °C [16]. Additionally, SiC has more than 3 times higher thermal conductivity than Si. This excellent thermal conductivity leads to a lower thermal resistance from junction to case, which allows SiC MOSFETs to dissipate more power losses with the same temperature

rise of junction temperature. The higher operating temperature, combined with the higher thermal conductivity can significantly reduce the cost and volume of cooling system for SiC-based power electronics.

SiC MOSFETs can switch more quickly than their Si counterparts. Firstly, since the breakdown field of SiC is 10 times higher than that of Si, a thinner drift layer with higher doping concentration can be utilised to manufacture the SiC MOSFET with a similar blocking voltage to their Si counterparts. Thus, a lower specific on-resistance and a smaller chip size is achieved in SiC MOSFETs. The reduced chip size enables smaller junction capacitance, resulting in a fast switching speed [17]. Secondly, due to the higher electron velocity of SiC, charge can be swept into and out of the junction capacitance very quickly, leading to a further increased switching speed of SiC MOSFETs.

# 1.1.3 Fast Switching Speed of SiC MOSFETs: Benefits and Challenges

The fast switching speed of SiC MOSFETs significantly affects overall performance of power electronics. On the one hand, it brings huge benefits to power electronics, including reduced power losses and increased switching frequency. These benefits lead to power electronics converters with high efficiency and high power density. On the other hand, the fast switching speed of SiC MOSFETs brings new challenges to power electronics, including electromagnetic interference (EMI) and reliability issues. Another challenge is that the high-efficiency high-power density design of power electronics requires accurate analysis of the fast switching behaviour of SiC MOSFETs to fully exploit their benefits in practical applications. These benefits and challenges are detailed as below:

Figure 1.3: Switching waveforms of power semiconductors [17].

Figure 1.4: Comparison of power loss in different power semiconductors [18].

#### **Benefits:**

#### 1) Loss and Efficiency

The power loss generated by power semiconductors consists of the conduction loss and the switching loss. The fast switching speed of the SiC MOSFET directly affects its switching loss. As shown in Fig. 1.3, each switching event (turn-on or turn-off) of power semiconductors takes a certain amount of switching time (i.e.,  $t_{on}$  and  $t_{off}$  in Fig. 1.3). The overlapping of voltage and current of semiconductors during the switching event causes the switching loss (i.e.,  $E_{on}$  and  $E_{off}$  in Fig. 1.3). Since SiC MOSFETs can switch much faster than Si IGBTs, the switching time of SiC MOSFETs is shorter than that of Si IGBTs, resulting in the reduced switching loss. Fig. 1.4 presents the total power loss of different power semiconductors for a 40 kW traction inverter [18]. It is shown in Fig. 1.4a that power loss of SiC MOSFETs is only 1/4 of the loss of Si IGBTs under the same switching frequency of 50 kHz. Fig. 1.4b shows that the switching loss is the main contributor to the total semiconductor loss for power electronics with a high switching frequency. Therefore, the greatly reduced switching loss due to the fast switching speed of SiC MOSFETs can significantly improve the efficiency of power electronics.

#### 2) Power Density

Passive components (e.g., bulky dc bus capacitors, ac inductors and transformers, as well as harmonics and EMI filters) and cooling systems (e.g., heat sinks and cooling fans) are the dominating factors of the power density (size and weight) of power electronics [19].

The size and weight of passive components will be affected by the switching frequency of power semiconductors. For example, in a 5 kW boost converter, the size and weight of the filter inductor can be reduced by 70 % and 80%, respectively, if the switching frequency is increased from 20 kHz to 100 kHz, as shown in Fig. 1.5 [20]. The upper limit of the switching frequency is determined by the switching speed and switching loss. Firstly, it is obvious that the switching period

Figure 1.5: 5 kW filter inductors at switching frequencies of 20 kHz and 100 kHz [20].

(i.e., reciprocal of the switching frequency) must be longer than the switching time  $(t_{on} + t_{off})$ . Secondly, since the switching losses are proportional to the switching frequency, the switching frequency is limited by the maximum power losses that can be extracted by the cooling systems of power electronics. Therefore, the fast switching speed and low switching loss of SiC MOSFETs enables higher switching frequency of power electronics. As shown in Fig. 1.4a, in hard-switching converters, SiC MOSFETs can operate at 400 kHz with the same power loss as Si IGBTs operated at 50 kHz, resulting in significantly reduced size and weight of passive components.

The power loss of power semiconductors is one of the crucial parameters for designing the cooling systems of power electronics. Lower switching loss of SiC MOSFETs results in reduced weight and size of cooling systems. For example, in a 40 kW traction inverter presented in [18], the size of the heat sink can be reduced by 60% if Si IGBTs are replaced by SiC MOSFETs at the same switching frequency of 50 kHz.

#### Challenges:

#### 1) EMI and Reliability

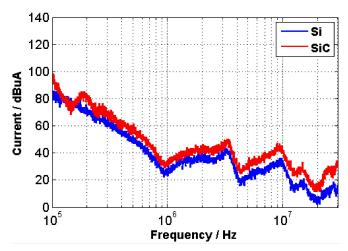

Although the fast switching speed of SiC MOSFETs can significantly improve the efficiency and power density of power electronics, it also causes challenges such as more serious electromagnetic interference (EMI) noise. EMI noise will affect the operation reliability of the power electronics converter and its neighbouring equipment. The dv/dt and di/dt generated during the switching transients are the main noise sources of EMI, especially at high-frequency range [21]. Faster switching speed of SiC MOSFETs inevitably causes higher dv/dt and di/dt, resulting in more critical EMI issues. Besides, the fast switching speed of the SiC MOSFET makes it more sensitive to circuit parasitics, causing ringing during the switching transient. Such ringing also plays an important role in increasing EMI noise. Furthermore, EMI noise, including common mode (CM) noise and differential mode (DM) noise, also increase with the switching frequency of power electronics. Since SiC MOSFETs usually operate at much higher switching frequency than Si IGBTs in practical applications, they will cause more EMI noise. As shown in Fig. 1.6, the measured EMI spectra of the inverter based on SiC MOSFETs are higher than those of the inverter based on Si IGBTs [22].

Considering their higher operating temperature and higher thermal conductivity, SiC has higher thermal reliability compared to Si [23]. However, some challenges exist in the reliability of SiC MOSFETs. Firstly, as an emerging technology, the reliability of SiC MOSFETs needs to be demonstrated for various applications [24]. Secondly, high temperature operation of SiC MOSFETs indicates more stringent requirement for the package material of SiC MOSFETs [7]. Thirdly, SiC MOSFETs have smaller die size than their Si counterparts under the same voltage and current ratings, resulting in higher current density and thermal stress of the SiC MOSFETs [25].

Figure 1.6: Measured EMI spectra of Si-based and SiC-based inverters [22]. The Si-based inverter operates at the switching frequency varying between 20-30 kHz. SiC-based inverter operates at the switching frequency between 80-120 kHz.

#### 2) Design Optimisation of Power Electronics

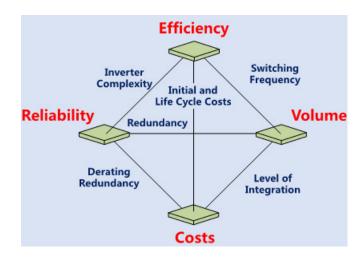

Another challenge brought by the emergence of SiC MOSFETs is the design optimisation of power electronics to fully exploit the advantages of SiC MOSFETs and to mitigate the drawbacks. As described previously, some key performance indicators of power electronics, including efficiency, power density and reliability are all closely related to the fast switching behaviour of SiC MOSFETs. The cost is another key indicator although it is not mentioned above. However, these indicators might contradict each others in practical design as presented in Fig. 1.7. For example, by designing a smaller gate driver resistor for the SiC MOSFET, its switching speed becomes faster, resulting in reduced switching losses and increased efficiency. However, this also increases the dv/dt, di/dt and ringing of the switching transients, resulting in increased EMI noise and reduced reliability. By designing a higher switching frequency for the power electronics converter, the size and weight of passive components can be reduced, which can potentially increase the converter's power density. However, the increased switching frequency induces more switching loss, causing reduced efficiency of the converter. Besides, increased switching loss requires larger cooling systems, which reduces the converter's power density. Due to the counteracting effects between these indicators, trade-offs have to be made when a power electronics converter is designed.

Figure 1.7: Counteracting effects of key performance indicators of power electronics [1].

Hardware prototyping is typically employed to design and optimise the performance indicators of the power electronics converter. However, due to the complex counteracting effects between these indicators, it requires multiple rounds of hardware prototyping to optimise the design parameters, which is expensive and time-consuming. Alternatively, virtual prototyping is a promising solution for the design optimisation of power electronics converters [26]. The virtual prototyping is based on mathematical models and multi-physics simulations to digitally design the converter parameters, which is less expensive and more time-efficient compared to hardware prototyping [27, 28]. Based on accurate mathematical multi-physics models of the converter and its components in virtual prototyping, multi-objective optimisation can be conducted to optimise the performance of the converter [29]. Since the fast switching transients of SiC MOSFETs affect many performance indicators (efficiency, power density, reliability, etc.), accurate transient simulation of SiC MOSFETs is essential for the virtual prototyping and multi-objective optimisation.

#### 1.1.4 Transient Simulation of SiC MOSFETs

Transient simulation is to simulate the switching waveforms of SiC MOSFETs in practical converter applications. The performance of SiC MOSFETs related to

switching transients, such as power losses, di/dt, dv/dt, ringings and EMI can all be analysed from the simulated switching waveforms. The simulated results can be used as the input data for the multi-objective optimisation approach in virtual prototyping.

One of the biggest challenges for transient simulation of SiC MOSFETs is that the simulation need to be as accurate as possible so that the validity of the virtual prototyping can be guaranteed [30]. This challenge is much more critical for SiC MOSFETs than Si IGBTs because SiC MOSFETs feature much faster switching speed and much shorter switching transients. At the same time, the simulation needs to be fast enough for converters with complicated topologies.

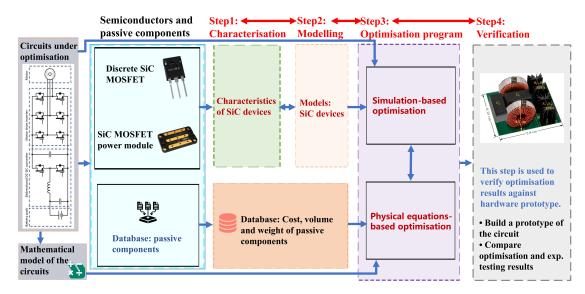

The premise of accurate transient simulation is accurate characterisation and modelling of SiC MOSFETs. The characteristics of SiC MOSFETs need to be accurately measured at the first stage. Afterwards, an accurate model of SiC MOSFETs is built based on the measured characteristics. The model is then used for transient simulation and multi-objective optimisation of the power electronics converter. Finally, a converter prototype can be manufactured based on the optimisation results to validate the design. Such a design process is summarised as a design flow chart in Fig. 1.8. It can be seen that the characterisation (Step 1) and modelling (Step 2) of SiC MOSFETs play crucial roles in this flowchart.

#### 1.2 Research Motivation

From the previous discussion of the background, it is aware that more effort is needed in the design optimisation of SiC-based power electronics before the superiorities of the SiC MOSFETs can be fully utilised, especially in the characterisation and modelling of SiC MOSFETs for accurate transient simulation.

Figure 1.8: Virtual prototyping and multi-objective optimisation of power electronics based on characterisation and modelling of SiC MOSFETs.

#### 1.2.1 Characterisation of SiC MOSFETs

Since the SiC MOSFET model is built based on its characteristics, the measurement method for accurate characterisation is required. The current-voltage (I-V)characteristics and capacitance-voltage (C-V) characteristics are the most important characteristics of SiC MOSFETs, which have great impacts on the switching behaviour of SiC MOSFETs. Therefore, there is a need to pay attention to the accurate measurement of these characteristics otherwise the models based on inaccurate characteristics will result in inaccurate simulation results and invalid design. In addition to the I-V and C-V characteristics in static state, it was found that the I-V and C-V characteristics in dynamic state (i.e., switching transient) have great impact on the accuracy of the model. However, the characterisation methods in previous studies [31–33] are very complex because multiple specialised measurement equipment such as the vector network analyser (VNA), the LCR meter, the gate charge evaluation circuit and the double pulse tester are required. Therefore, a research work on the simplified I-V and C-V characterisation methods in dynamic state is required to simplify the characterisation process and, at the same time, improve the accuracy of SiC MOSFET models.

#### 1.2.2 Measurement-based Modelling of SiC MOSFETs

Once the characteristics of SiC MOSFETs are accurately measured, a measurement-based model can be built. And behavioural models can then be used. Firstly, the equivalent circuit model of SiC MOSFETs is constructed based on their physical structures. Secondly, the nonlinear components in the equivalent circuit are modelled based on mathematical equations to match the measured characteristics. Due to the high nonliearity of these characteristics, behavioural models (the detailed discussion is in Section 2.3.2) have following issues: 1) Complicated mathematical equations are required, which make it difficult to design suitable equations and to extract equation parameters; 2) The equations cannot accurately match the complex characteristics of the SiC MOSFET; 3) The designed mathematical equations lack adaptability to model different SiC MOSFETs with different characteristics accurately; 4) The complicated models have slow simulation speed. To address these issues, a research work is needed to investigate the modelling method of SiC MOSFETs which is accurate, fast, easy to use and adaptable to different devices.

#### 1.2.3 Datasheet-based Modelling of SiC MOSFETs

Although measurement-based modelling method can deliver an accurate model for transient simulation based on measured characteristics, in some cases, the equipment required for the measurement-based modelling may not be achievable due to limited resources and high cost. The datasheet-based modelling method can be an alternative solution which is purely based on the characteristics of SiC MOSFETs obtained from the datasheet without the use of any further data or equipment. Many manufacturers provide transient simulation models along with the datasheets for their discrete devices. These models can be directly used by designers. However, the models for SiC MOSFETs power modules are currently not provided by manufacutures. There is a need to build models for these power modules based on the datasheets provided by manufacturers. Therefore, a study on the datasheet-based modelling method is required. Furthermore, a comprehens-

ive comparison between the measurement-based and datasheet-based modelling methods is required to provide a guidance for converter designers to choose the suitable method for their own applications.

#### 1.3 Objectives and Contributions of This Thesis

The objectives and contributions of this thesis are outlined as follows:

• Objective 1: Investigate the method to measure the *I-V* and *C-V* characteristics of SiC MOSFETs in dynamic state to simplify the measurement process and improve the model accuracy of SiC MOSFETs in transient simulation.

Contribution 1: A double-pulse-tester-based characterisation method was proposed to measure the I-V and C-V characteristics in dynamic state to improve the model accuracy in transient simulation. Conventionally, the DPT mainly focuses on measuring the switching waveforms of SiC MOS-FETs. The contribution of the proposed method is to utilise the switching waveforms measured by the DPT to extract the dynamic-state I-V and C-V characteristics. The proposed method analysed the relationship of these characteristics with the switching waveforms of SiC MOSFETs, where these characteristics can be directly extracted from the switching waveforms. Since only a double pulse tester (DPT) is needed to be designed for the measurement of the switching waveforms, the proposed measurement method is much simpler than existing methods and can therefore be widely adopted by converter designers with low cost. The proposed method also reduced the self-heating of the SiC MOSFET when measuring the I-V characteristics in the high-voltage high-current ranges so that the errors induced by the increased junction temperature were reduced. These measured dynamic-state characteristics, combined with the conventional static-state characteristics, were used to built the SiC MOSFET model. The relative root-mean-square (RMS) errors of the model can be reduced by at least 3 times, compared to the model that only considers the conventional static-state characteristics.

• Objective 2: Investigate the measurement-based method to accurately model the measured characteristics of SiC MOSFETs for fast transient simulation. In addition to accuracy and simulation speed, the modelling process needs to be simple and the modelling method needs to have good adaptability to model different types of SiC MOSFETs.

Contribution 2: A measurement-based hybrid data-driven behavioural modelling methodology based on artificial neural networks (ANNs) has been proposed. For the first time, an ANN-based hybrid data-driven modelling method is proposed and verified for accurate transient simulation of SiC MOSFETs. The model was built based on the measured I-V and C-V characteristics. This proposed modelling method can overcome the challenges of the conventional behavioural modelling methods, such as model accuracy, simulation speed, adaptability, complex equation design, difficulties of parameter extraction, etc. The required training dataset and a proper hybrid model were identified for SiC MOSFETs. The switching waveforms simulated by the proposed model are  $1.5 \sim 3$  times closer to the experimental waveforms, compared to a commercial Angelov model. At the same time, the proposed model is 30% faster than Angelov model in simulation speed.

• Objective 3: Investigate the datasheet-based modelling method to model the characteristics of SiC MOSFETs obtained from the datasheet. Besides, the comparison between the datasheet-based method and the measurement-based method need to be focused on to identify the usage of both methods.

Contribution 3: A step-by-step modelling approach for SiC MOSFETs based on datasheet was proposed. A detailed and easy-to-follow parameter extraction process of each component in the model was clearly illustrated. The method is completely based on characteristics obtained from the data-

sheet without the need of any further data or equipment. Besides, a comprehensive comparison between the datasheet-based model and the measurement-based model was studied to provide a guidance for users to choose the suitable method for their own applications. Compared to the measurement-based modelling method, the datasheet-based modelling method presents 24% more relative RMS errors and cannot accurately match the gate driver resistor used in practical experiment. However, the datasheet-based modelling method features simpler modelling process and 15% faster simulation speed so provides a more cost and time-efficient process for converter designers to quickly validate their converter design.

#### 1.4 Thesis Outline

The rest of this thesis is organised as follows:

Chapter 2 provides a literature review of operation principles of SiC MOS-FET, state-of-the-art and challenges for the characterisation and modelling of SiC MOSFETs: including existing methods and challenges of: 1) static and dynamic characterisation of SiC MOSFETs; 2) the measurement-based behavioural modelling of SiC MOSFETs; 3) datasheet-based modelling of SiC MOSFETs.

Chapter 3 focuses on the accurate characterisation of SiC MOSFETs, including *I-V* and *C-V* characteristics. Firstly, the conventional *I-V* and *C-V* characterisation methods in static state and their limitations are illustrated. Secondly, after analysing the relation between the characteristics of the SiC MOSFET and its switching process, a double-pulse-tester-based characterisation method is proposed to measure the additional *I-V* and *C-V* characteristics in dynamic state as the complements of the conventionally-measured static-state characteristics. The measured dynamic-state characteristics can be used to improve the accuracy of the measurement-based model in Chapter 4.

Chapter 4 introduces a measurement-based modelling methodology for SiC

MOSFETs, i.e., a hybrid data-driven behavioural modelling methodology based on artificial neural networks. The model is trained with the *I-V* and *C-V* characteristics measured in Chapter 3. This proposed modelling method can overcome the challenges of the conventional behavioural modelling methods, such as model accuracy, simulation speed, adaptability, complex equation design, difficulties of parameter extraction, etc. The required training dataset and a proper hybrid model are identified for SiC MOSFETs. The effectiveness of the proposed modelling method is verified by comparing to a commercial measurement-based modelling method. The characterisation methods proposed in Chapter 3 are also verified based on the proposed hybrid data-driven model.

Chapter 5 illustrates a datasheet-based modelling methodology of SiC MOSFETs. Compared to the measurement-based methods in Chapter 4, the proposed datasheet-based modelling method only requires characteristics obtained from the datasheet of the SiC MOSFETs. Thus, the datasheet-based method can avoid complicated, time-consuming and expensive characterisation procedures. The detailed datasheet-based modelling approach is introduced step-by-step in this chapter, and its performance is compared to the measurement-based method in Chapter 4, in terms of required data, model accuracy, complexity and gate driver parameters.

Chapter 6 presents the conclusions and future work.

#### 1.5 List of Publications

#### Published Academic Journal Papers

- P. Yang, W. Ming, J. Liang, I. Ludtke, S. Berry and K. Floros, "Hybrid Data-driven Modelling Methodology for Fast and Accurate Transient Simulation of SiC MOSFETs," *IEEE Transactions on Power Electronics*, vol. 37, no. 1, pp. 440-451, Jan. 2022, doi: 10.1109/TPEL.2021.3101713.

- 2. P. Yang, W. Ming, J. Liang, C. Ugalde, R. Navaratne, O. Ellabban, and

- I. Ludtke, "SiC-Based Improved Neutral Legs with Reduced Capacitors for Three-phase Four-wire EV Chargers," *IEEE Transactions on Transportation Electrification*, Early Access, 2022, doi: 10.1109/TTE.2021.3138333.

- X. Jiang, Y. Zhou, W. Ming, P. Yang, and J. Wu, "An Overview of Soft Open Points in Electricity Distribution Networks", *IEEE Transactions on* Smart Grid, Early Access, 2022.

#### Journal Papers Under Review or Preparation

- P. Yang, W. Ming, J. Liang, R. Navaratne, I. Ludtke, and K. Floros, "Measurement Methodology for Self-Heating Reduction in High-Voltage High-Current Characterization of SiC MOSFETs," *IEEE Electron Device Letters* (first round review finished).

- 2. **P. Yang**, W. Ming, J. Liang, R. Navaratne, I. Ludtke, and K. Floros, "Double-Pulse-Tester-Based Measurement Method for Accurate Modeling of SiC MOSFETs," (under preparation for submission to *IEEE Transactions on Power Electronics*).

- M. Abdelrahman, P. Yang, W. Ming, J. Wu, and N. Jenkins, "Modified Unified Power Flow Controller for Medium Voltage Distribution Networks," IET Generation, Transmission and Distribution, (under first round review).

- 4. C. Li, **P. Yang**, J. Wu, Y. Liu, I. Ludtke, and W Ming, "S-parameter-based Measurement Methodology for Accurate Extraction of Parasitic Inductance of SiC Power Modules", (under preparation for submission to *IEEE Transactions on Power Electronics*).

#### Peer-reviewed Conference Papers

- P. Yang, W. Ming and J. Liang, "A Step-by-step Modelling Approach for SiC Half-bridge Modules Considering Temperature Characteristics," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 2827-2834, doi: 10.1109/ECCE44975.2020.9235594.

- P. Yang, W. Ming, J. Liang and J. Wu, "A SiC-based Neutral Leg for the Three-phase Four-wire Inverter," *IECON 2019 - 45th Annual Confer*ence of the *IEEE Industrial Electronics Society*, 2019, pp. 1555-1560, doi: 10.1109/IECON.2019.8927531.

- P. Yang, W. Ming, J. Liang and J. Wu, "A Four-leg Buck Inverter for Three-phase Four-wire Systems with the Function of Reducing DC-bus Ripples,"

IECON 2019 45th Annual Conference of the IEEE Industrial

Electronics Society, 2019, pp. 1508-1513, doi: 10.1109/IECON.2019.8927264.

- P. Yang, W. Ming, J. Liang and J. Wu, "Reduction of DC-link Ripples for Three-phase Four-wire Inverters with Unbalanced Loads," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 2819-2835, doi: 10. 1109/ECCE.2019.8912810.

- W. Liu, J. Liang, C. E. Ugalde-Loo, C. Li, G. Li and P. Yang, "Level-shift Modulation and Control of a Dual H-bridge Current Flow Controller in Meshed HVDC systems," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 62-66, doi: 10.1109/ECCE.2019.8912857.

- W. Ming, Q. Zhong, P. Yang and J. Liang, "Dual-Buck Arbitrary Voltage Divider with One Output Having Reduced Ripples," *IECON* 2018 - 44th Annual Conference of the IEEE Industrial Electronics Society, 2018, pp. 3621-3626, doi: 10.1109/IECON.2018.8591447.

# Chapter 2

# Literature Review

# 2.1 Operation Principle of SiC MOSFETs

#### 2.1.1 Structure of SiC MOSFETs

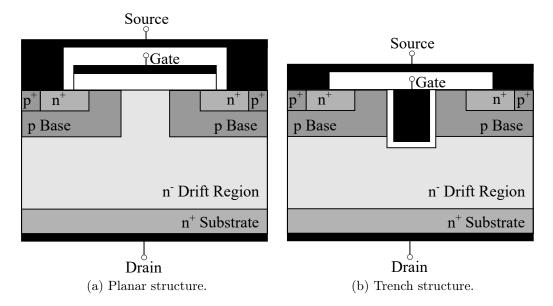

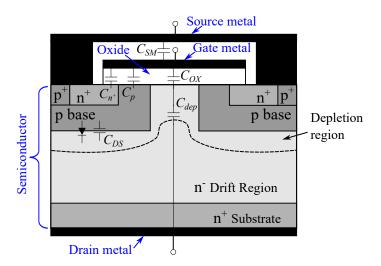

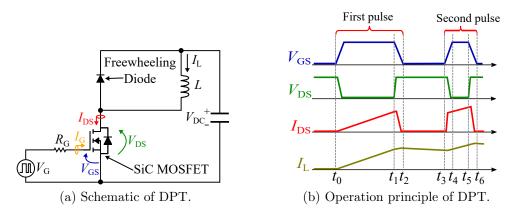

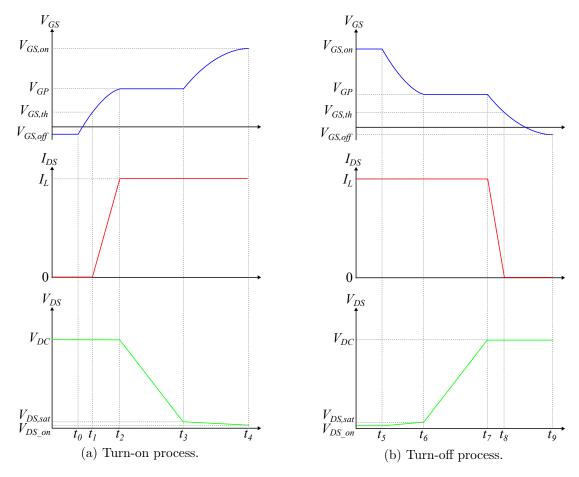

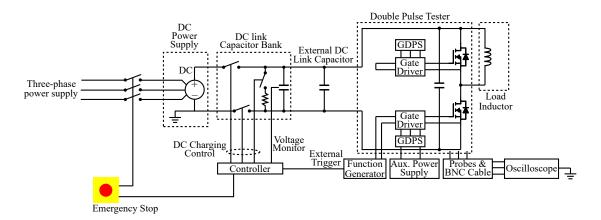

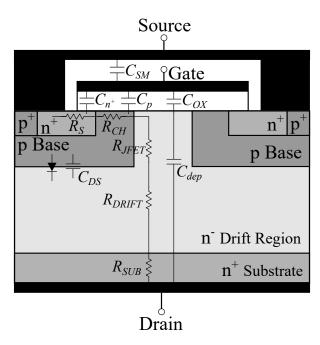

Vertical structures are typically used for SiC MOSFETs to achieve a high blocking voltage. Fig. 2.1 shows two vertical structures of SiC MOSFETs, one is the planar structure (Fig. 2.1a), the other is the trench structure (Fig. 2.1b). These two structures are currently the most popular structures adopted by manufacturers. For example, Wolfspeed uses planar structure for its SiC MOSFETs in C2M<sup>TM</sup> and C3M<sup>TM</sup> series [34]; Infineon uses the trench structure for its SiC MOSFETs in CoolSiC<sup>TM</sup> series [35]; Rohm uses both the planar structure in its SCT2 series products and the trench structure in its SCT3 series products [36].

It can be seen that the major difference between these two structures is their gate structures. The planar SiC MOSFET features a simple gate structure which can be easily manufactured, but it has high on-resistance causing high conduction loss. The trench SiC MOSFET is more attractive in lowering the on-resistance, but its complicated structure is relatively difficult to be manufactured [37]. It is worth noting that both planar SiC MOSFETs and trench SiC MOSFETs have undergone considerable development and optimisation, and several features have been added to the basic structures of Fig. 2.1 to improve their performance and

Figure 2.1: Two typical structures of SiC MOSFETs.

reliability. Since both the planar and trench SiC MOSFETs have similar operating principles, the planar type will be taken as an example to illustrate the operating principles of SiC MOSFETs.

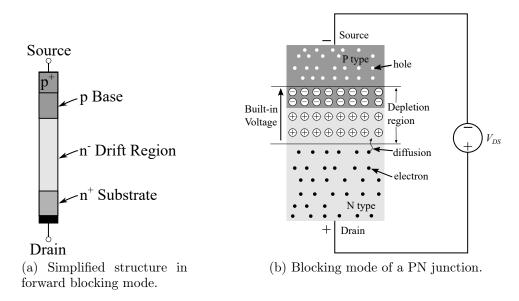

#### 2.1.2 Forward Blocking Mode of SiC MOSFETs

The operation mode of the SiC MOSFET is controlled by the gate-source voltage  $V_{GS}$ . When  $V_{GS}$  is lower than the threshold voltage, a forward conduction channel is not formed on the surface of the p-base region and thus the SiC MOSFET works in the forward blocking mode. In this mode, the operation principle of the SiC MOSFET can be simplified as a PN junction (i.e., a diode) as shown in Fig. 2.2a [38]. Therefore, the blocking mode of a diode can be used to understand the blocking mode of the SiC MOSFET.

As shown in Fig. 2.2b, when a positive drain-source voltage  $V_{DS}$  is applied to the SiC MOSFET in the forward blocking mode, the holes in the p type material (which is connected to the negative side of the voltage source) are pulled away from the PN junction. Similarly, the electrons in the n type material (which is connected to the positive side of the voltage source) are pulled away from the PN junction. Therefore, the thickness of the depletion region at the PN junction increases due to

Figure 2.2: Illustration of the forward blocking mode of SiC MOSFETs.

the positive  $V_{DS}$ , causing an increased built-in voltage. An equilibrium condition is reached and no current can flow when the built-in voltage in the depletion region equals to  $V_{DS}$  [39].

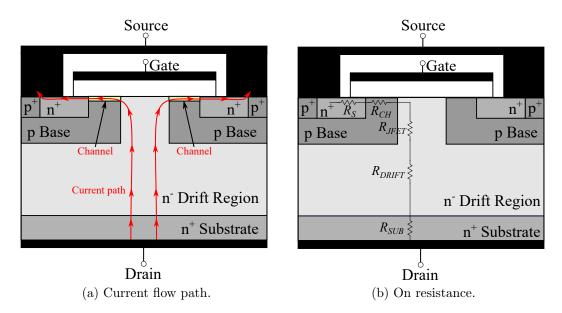

#### 2.1.3 Forward Conduction Mode of SiC MOSFETs

When the gate-source voltage  $V_{GS}$  is larger than the threshold voltage, an inversion layer channel on the surface of the p-base region is formed as shown in Fig 2.3a and the SiC MOSFET works in the forward conduction mode [40]. The current can flow from drain to source through the inversion layer channel [41]. The current path is illustrated in Fig. 2.3a. The total on resistance in the current flow path is the sum of the resistance in each specific region as shown in Fig. 2.3b:

$$R_{on} = R_S + R_{CH} + R_{JEFT} + R_{DRJFT} + R_{SUB}$$

(2.1)

where  $R_S$  is the source resistance;  $R_{CH}$  is the channel resistance;  $R_{JEFT}$  is the resistance of the JFET region;  $R_{DRIFT}$  is the resistance of the drift region;  $R_{SUB}$  is the resistance of the substrate. The values of these resistances can be physically determined by the dimension and doping concentration of each region, as well as the bias gate-source and drain-source voltages ( $V_{GS}$  and  $V_{DS}$ ). Detailed physical

Figure 2.3: Forward conduction mode of SiC MOSFETs.

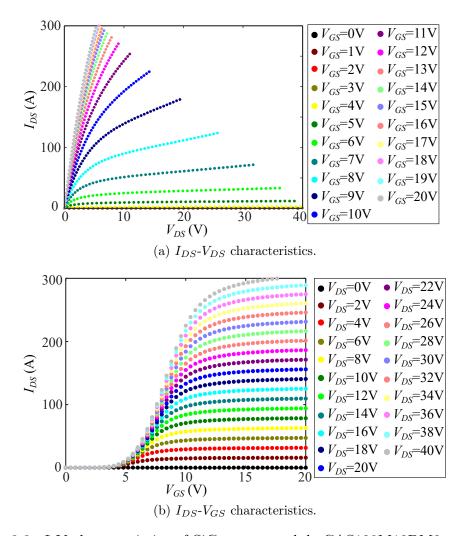

Figure 2.4: *I-V* characteristics of SiC MOSFET power module CAS120M12BM2.

equations of the on resistance have been derived in [42].

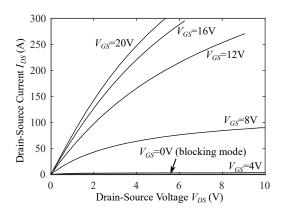

Due to the dependency of the on resistance on the bias voltages  $V_{GS}$  and  $V_{DS}$ , the current-voltage relation (i.e., I-V characteristics) is used to illustrate the on resistance and blocking mode under various bias conditions. Fig. 2.4 shows the nonlinear I-V characteristics of a SiC MOSFET power module CAS120M12BM2 [43].

## 2.1.4 Capacitances of SiC MOSFETs

Due to the unipolar conduction mechanism of SiC MOSFETs [44], only electrons are involved in the forward conduction mode as the majority carriers for N-channel SiC MOSFETs. The absence of minority carriers (i.e., holes for N-channel SiC

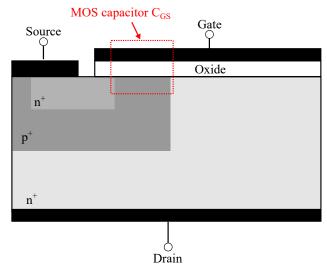

Figure 2.5: Capacitances within SiC MOSFETs.

MOSFETs) in the forward conduction mode allows immediate interruption of the current flow after the gate bias voltage is reduced below the threshold voltage [45]. Although this implies a very fast switching speed for SiC MOSFETs, in practice the switching speed is limited by the parasitic capacitances of SiC MOSFETs [46].

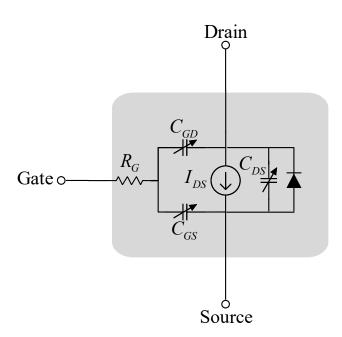

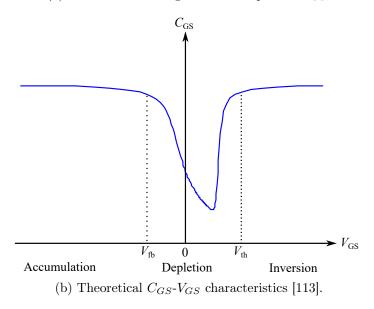

The capacitances within the SiC MOSFETs are presented in Fig. 2.5. According to their locations, they can be summarised as three capacitances: gate-source capacitance  $C_{GS}$ , gate-drain capacitance  $C_{GD}$  and drain-source capacitance  $C_{DS}$ .

As shown in Fig. 2.5, the gate-source capacitance is primarily determined by the overlap of the gate metal electrode with the  $N^+$  source region and the p base region of the semiconductor, interfaced by the gate oxide. This forms the metal-oxide-semiconductor (MOS) capacitances  $C_{n^+}$  and  $C_p$  [47]. Besides, in the structure of SiC MOSFETs, the source metal electrode overlaps the gate metal electrode, producing the parallel metal plate capacitance  $C_{SM}$ . The values of  $C_{n^+}$ ,  $C_p$  and  $C_{SM}$  can be determined by the geometry of the SiC MOSFET structure such as the width of the overlapping region and the thickness of the gate oxide. Detailed physical equations have been derived in [48]. The total gate-source capacitance  $C_{GS}$  can be obtained by adding up these three individual capacitances:

$$C_{GS} = C_{n^+} + C_p + C_{SM} (2.2)$$

The gate-drain capacitance  $C_{GD}$  is also a MOS capacitance formed by the overlap of the gate metal electrode with the n<sup>-</sup> drift region of the semiconductor. As shown in Fig. 2.5,  $C_{GD}$  can be treated as two individual capacitance ( $C_{OX}$  and  $C_{dep}$ ) in series.  $C_{OX}$  is the specific capacitance of the gate oxide capacitance.  $C_{dep}$  is the specific capacitance of the semiconductor depletion region under the gate oxide. The value of  $C_{dep}$  is determined by the width of the depletion region. When the bias voltage  $V_{DG}$  increases, the width of the depletion region under the gate oxide increases, resulting in the reduction of  $C_{dep}$ . Detailed illustration and equations of  $C_{OX}$  and  $C_{dep}$  have been provided in [49]. Eventually, the gate-drain capacitance  $C_{GD}$  can be obtained as: