# Thermal Regulation and Balancing in Modular Multilevel Converters

Jorge Gonçalves

School of Engineering

Cardiff University

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

January 2018

# Contents

| A  | bstra | ct            |                                                    |   |   |   | vi   |

|----|-------|---------------|----------------------------------------------------|---|---|---|------|

| D  | eclar | ation o       | of Authorship                                      |   |   |   | vii  |

| A  | cknov | wledge        | ements                                             |   |   |   | ix   |

| A  | bbrev | viation       | 1S                                                 |   |   |   | 3    |

| Sy | ymbo  | ls            |                                                    |   |   |   | xii  |

| Li | st of | Figure        | es                                                 |   |   |   | хv   |

| Li | st of | Tables        | ${f s}$                                            |   |   |   | xix  |

| 1  | Intr  | oducti        | ion                                                |   |   |   | 1    |

|    | 1.1   | Backg         | ground                                             |   |   |   | . 1  |

|    | 1.2   |               | rs of HVDC Transmission Systems                    |   |   |   |      |

|    | 1.3   | Techn         | ical Challenges                                    |   |   |   | . 4  |

|    | 1.4   | Resear        | rch Objectives                                     |   |   |   | . 6  |

|    | 1.5   | Thesis        | s Structure                                        |   |   |   | . 7  |

|    | 1.6   | Public        | cations by the Author                              |   |   |   |      |

|    |       | 1.6.1         | Journal Publications                               |   |   |   | . (  |

|    |       | 1.6.2         | Conference Publications                            |   |   |   |      |

|    |       | 1.6.3         | Research Workshops                                 |   | • | • | . 9  |

| 2  | Pow   |               | ectronic Converters for HVDC Grids                 |   |   |   | 11   |

|    | 2.1   |               | luction                                            |   |   |   |      |

|    | 2.2   |               | C Conversion                                       |   |   |   |      |

|    |       | 2.2.1         | Line Commutated Converters                         |   |   |   |      |

|    |       | 2.2.2         | 2- and 3-Level Voltage Source Converters           |   |   |   |      |

|    |       | 2.2.3         | Modular Multilevel Converters                      |   |   |   |      |

|    |       |               | 2.2.3.1 Half-Bridge MMC                            |   |   |   |      |

|    | 0.0   | 0             | 2.2.3.2 Full-Bridge MMC                            | • | • |   | . 17 |

|    | 2.3   | _             | ation and Control of Modular Multilevel            |   |   |   | 1 (  |

|    |       |               | $egin{array}{cccccccccccccccccccccccccccccccccccc$ |   |   |   |      |

|    |       | 2.3.1         |                                                    |   |   |   |      |

|    |       | 2.3.2 $2.3.3$ | Vector Control                                     |   |   |   |      |

|    |       | ۵.ئ.ئ         | 2.3.3.1 Modulation                                 | • | • | • | . 26 |

|    |       |               | 44. C.         | _ | - |   |      |

Contents

|   |     |             | 2.3.3.2 Capacitor Voltage Balancing                      | 30 |

|---|-----|-------------|----------------------------------------------------------|----|

|   |     |             | 2.3.3.3 Circulating Current Suppression                  | 34 |

|   |     |             | 2.3.3.4 Alternative MMC Control Strategies               | 36 |

|   | 2.4 | Opera       | ational Requirements and Challenges                      | 38 |

|   |     | 2.4.1       | Semiconductors Temperature Control                       | 38 |

|   |     | 2.4.2       | Management of Sub-Modules Redundancy and State of Health |    |

|   |     |             | Monitoring                                               | 40 |

|   | 2.5 | Summ        | nary                                                     | 42 |

| 3 | Jun | ction '     | Temperature Estimation in Power Electronic Modules       | 45 |

|   | 3.1 | Introd      | luction                                                  | 45 |

|   | 3.2 | Semic       | conductors Electro-Thermal Dynamics                      | 45 |

|   |     | 3.2.1       | Thermal Model                                            | 45 |

|   |     | 3.2.2       | Semiconductors Cooling                                   | 48 |

|   |     | 3.2.3       | Losses and Temperature Calculation                       | 50 |

|   |     |             | 3.2.3.1 Conduction Losses                                | 50 |

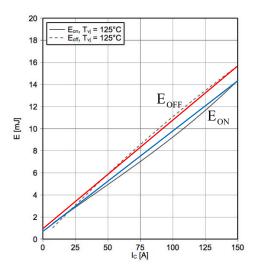

|   |     |             | 3.2.3.2 Switching Losses                                 | 51 |

|   |     |             | 3.2.3.3 Losses Distribution                              | 53 |

|   |     |             | 3.2.3.4 Temperature Calculation                          | 55 |

|   | 3.3 | Juncti      | ion Temperature Acquisition and Estimation               | 57 |

|   |     | 3.3.1       | Challenges and Requirements                              | 57 |

|   |     | 3.3.2       | Junction Temperature Estimation                          | 57 |

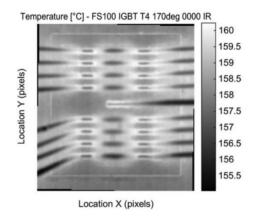

|   |     |             | 3.3.2.1 Optical Methods                                  | 57 |

|   |     |             | 3.3.2.2 Physical Contact Sensors                         | 58 |

|   |     |             | 3.3.2.3 Thermal Model-based Methods                      | 60 |

|   |     |             | 3.3.2.4 Thermo-Sensitive Electric Parameters (TSEPs)     | 62 |

|   | 3.4 | Summ        | nary                                                     | 67 |

| 4 |     |             | CM-11-M-12-AC                                            |    |

| 4 |     | ${f ation}$ | n of Modular Multilevel Converters with Dynamic Rating   | 69 |

|   | 4.1 | _           | luction                                                  | 69 |

|   | 4.2 | Tempe       | erature Control Strategies                               | 70 |

|   |     | 4.2.1       | Semiconductor Limitations                                | 70 |

|   |     | 4.2.2       | Conventional Control Strategies                          | 71 |

|   |     | 4.2.3       | Proposed Active Thermal Control Concept                  | 72 |

|   |     | 4.2.4       | Dynamic Rating Strategy A: Proportional Current Control  | 75 |

|   |     | 4.2.5       | Dynamic Rating Strategy B: PI-based Current Control      | 76 |

|   | 4.3 | Enhar       | nced Current Control Loop with Temperature Feedback      | 77 |

|   | 4.4 | Transi      | ient Overload Capability of Semiconductors               | 79 |

|   | 4.5 | Stabil      | lity Analysis                                            | 85 |

|   |     | 4.5.1       | Thermal Model                                            | 85 |

|   |     | 4.5.2       | Current Limit                                            | 87 |

|   |     |             | 4.5.2.1 Strategy A                                       | 88 |

|   |     |             | 4.5.2.2 Strategy B                                       | 91 |

|   |     | 4.5.3       | Eigenvalue Analysis                                      | 95 |

|   |     |             | 4.5.3.1 Strategy A                                       | 95 |

|   |     |             | 4.5.3.2 Strategy B                                       | 97 |

Contents

|   | 4.6 | Result   | ts                                                               | . 99  |

|---|-----|----------|------------------------------------------------------------------|-------|

|   |     | 4.6.1    | Steady-State Operation                                           | . 99  |

|   |     | 4.6.2    | Cooling System Failure                                           | . 101 |

|   |     | 4.6.3    | Converter Overload                                               | . 104 |

|   |     | 4.6.4    | Improvement of Frequency Support                                 | . 108 |

|   | 4.7 | Summ     | nary                                                             | . 117 |

| 5 | Sub | -Mod     | ule Temperature Regulation and Balancing                         | 119   |

|   | 5.1 | Introd   | luction                                                          | . 119 |

|   | 5.2 | Thern    | nal Imbalances in Sub-Modules of Modular Multilevel Converters . | . 119 |

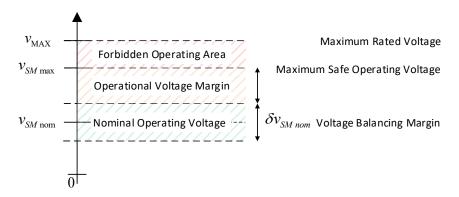

|   | 5.3 | Voltag   | ge-Temperature Regulation and Balancing                          | . 120 |

|   |     | 5.3.1    | Proposed Control Strategy for Individual Sub-Module Voltage Con- | •     |

|   |     |          | trol                                                             | . 121 |

|   |     | 5.3.2    | Proposed Control Strategy for Sub-Modules Temperature Regula-    |       |

|   |     |          | tion                                                             | . 121 |

|   |     | 5.3.3    | Considerations Regarding Capacitor Voltage Modulation            | . 123 |

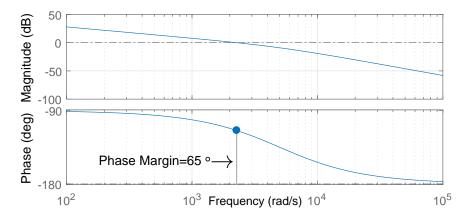

|   |     | 5.3.4    | Stability of Sub-Module Temperature Regulation                   | . 124 |

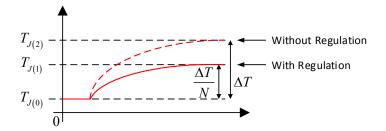

|   |     | 5.3.5    | Analysis and Limitations of the Thermal Regulation               | . 125 |

|   | 5.4 | Result   | $\operatorname{ts}$                                              | . 127 |

|   |     | 5.4.1    | Scenario I: Thermal Disturbance without Voltage Regulation for   |       |

|   |     |          | a small number of SMs                                            | . 128 |

|   |     | 5.4.2    | Scenario II: Thermal Disturbance with Voltage Regulation for a   |       |

|   |     |          | small number of SMs                                              | . 129 |

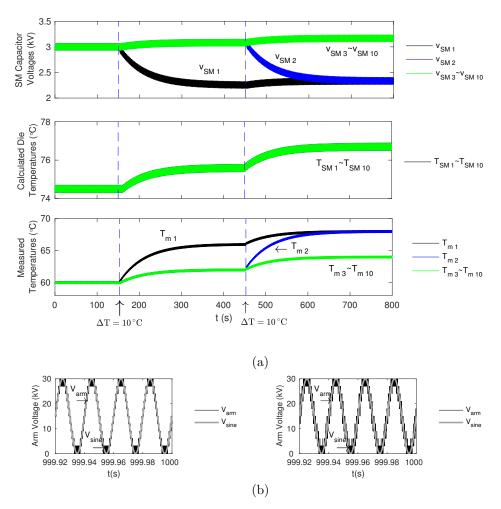

|   |     | 5.4.3    | Scenario III: Thermal Disturbance with Voltage Regulation for a  |       |

|   |     |          | large number of SMs                                              | . 131 |

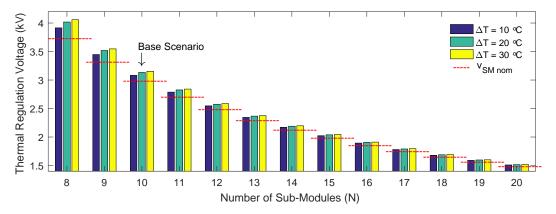

|   |     | 5.4.4    | Influence of the Thermal Imbalance Amplitude and Number of       | 199   |

|   | 5.5 | Carrosso | SMs in the Thermal Regulation                                    |       |

|   | 5.5 | Sullill  | iary                                                             | . 155 |

| 6 | _   |          | ental Tests                                                      | 137   |

|   | 6.1 |          | duction                                                          |       |

|   | 6.2 |          | ced-Order Modular Multilevel Converter Setup                     |       |

|   |     | 6.2.1    | Rationale and Description                                        |       |

|   |     | 6.2.2    | Operation and Control                                            |       |

|   | 0.0 | 6.2.3    | Controller Design                                                |       |

|   | 6.3 | •        | rimental Platform                                                |       |

|   |     | 6.3.1    | Overall System Structure                                         |       |

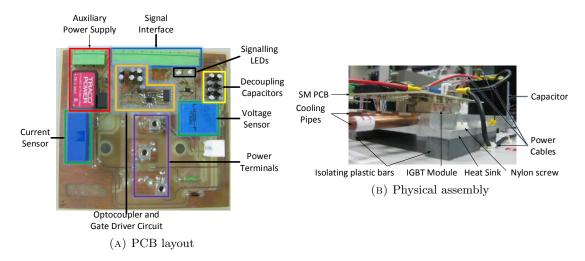

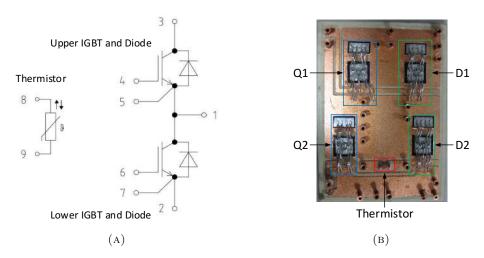

|   |     | 6.3.2    | Sub-Module Structure                                             |       |

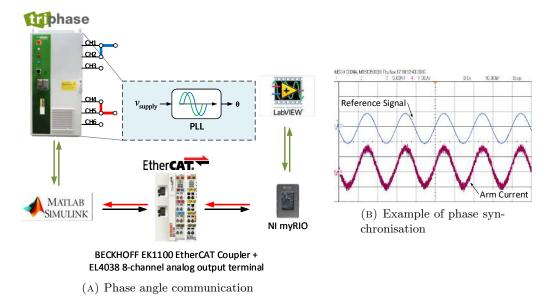

|   |     | 6.3.3    | Phase Synchronisation                                            |       |

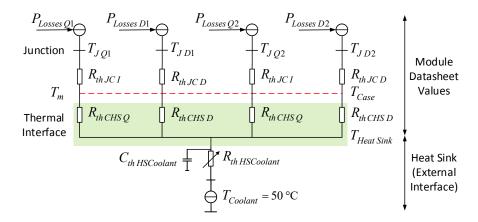

|   |     | 6.3.4    | Temperature Measurement and Calculation                          |       |

|   | 6.4 |          | rimental Results and Discussion                                  |       |

|   |     | 6.4.1    | Dynamic Performance                                              |       |

|   |     | 6.4.2    | Active Thermal Control                                           |       |

|   |     |          | 6.4.2.1 Cooling System Failure                                   |       |

|   |     |          | 6.4.2.2 Converter Overload                                       |       |

|   |     | 0.40     | 6.4.2.3 Improvement of Frequency Support                         |       |

|   |     | 6.4.3    | Sub-Module Temperature Regulation and Balancing                  |       |

|   |     |          | 6.4.3.1 Thermal Imbalances without Voltage Regulation            | . 164 |

*Contents* vi

|    |       |         | 6.4.3.2   | Thermal Imbalances with Voltage Regulation             | . 165 |

|----|-------|---------|-----------|--------------------------------------------------------|-------|

|    | 6.5   | Summ    | ary       |                                                        | . 167 |

| 7  | Con   | clusio  | ns and F  | Recommendations for Future Research                    | 169   |

|    | 7.1   | Conclu  | usions    |                                                        | . 169 |

|    |       | 7.1.1   | Operation | on of Modular Multilevel Converters with Dynamic       |       |

|    |       |         | Rating S  | Strategies                                             | . 169 |

|    |       | 7.1.2   | Sub-Moo   | dule Temperature Regulation and Balancing              | . 170 |

|    |       | 7.1.3   | Reduced   | l-Order Experimental Modular Multilevel Converter      |       |

|    |       |         | Platform  | 1                                                      | . 171 |

|    | 7.2   | Recon   | nmendatio | ons for Future Research                                | . 172 |

|    |       | 7.2.1   | Improve   | d Semiconductor Temperature Estimation Method          | . 172 |

|    |       | 7.2.2   | Alternat  | ive Dynamic Rating Strategies                          | . 172 |

|    |       | 7.2.3   | Inclusion | n of Semiconductors Lifetime Estimation in the Voltage |       |

|    |       |         | Balancin  | ng and Load Sharing Algorithms                         | . 173 |

| Re | efere | nces    |           |                                                        | 175   |

| A  | Wir   | ing Di  | agram o   | of the Experimental Setup                              | 209   |

| В  | Vali  | idation | of the    | Analytical Model of Dynamic Rating Strategies          | 211   |

## Abstract

Modular multilevel converters (MMCs) are envisaged as the key power electronic converter topology to enable a multi-terminal pan-European high voltage direct current (HVDC) Supergrid for the interconnection of offshore wind farms and exchange of energy between different countries.

A key feature of MMCs in the large number of semiconductor devices employed in each converter station, distributed over a stack of series-connected sub-modules (SMs). These semiconductors possess strict thermal limits, which can constrain the operating range on the converter by limiting its capability of providing enhanced functionalities to the AC grid such as short-term power overloads. Furthermore, due to different loading conditions and ageing, significant temperature differences can exist between SMs which can lead to a very different lifetime expectancies for the semiconductor modules.

This thesis proposes active thermal control methodologies to act of two distinct converter levels. Firstly, two novel dynamic rating strategies are proposed to define the converter current injection limit as a response to the maximum semiconductor temperature feedback. This enables the exploitation of the semiconductors thermal headroom to provide short-term power overloads, which can be used for the improvement of the frequency support of a power-distressed AC grid. Secondly, a SM-level temperature regulation and balancing algorithm is proposed, aiming at the equalisation of the maximum semiconductor die temperature in all the SMs of an MMC arm.

The proposed methods are validated in a detailed and combined electro-thermal simulation model with 3 and 10 SMs per arm developed in MATLAB®/Simulink® using PLECS® Blockset. An experimental platform has been designed and utilised to verify the effectiveness of the dynamic rating strategies and the SM temperature regulation and balancing strategy.

# Acknowledgements

In the first place, I would like to thank my supervisors, Dr. Daniel James Rogers and Professor Jun Liang, for their guidance, support, trust and patience!

I would also like to thank European Union for funding MEDOW Project, a Marie Curie Initial Training Network, through the Seventh Framework Programme. This project enable me to expand the scope of my research by undertaking two four months-long secondments at China Electric Power Research Institute (CEPRI) in Beijing, China and at the CITCEA Group of the Technical University of Catalonia (UPC BarcelonaTech) in Barcelona, Spain, and an eight months-long secondment at the Energy and Power Group of the University of Oxford in Oxford, UK . A work of appreciation to all the colleagues I have worked with and all the friends I have made during these (ad)ventures.

Last but not least, I want to thank my girlfriend, Jingli Guo, and my family, mother Alice, father Manuel and brother Manuel António, for their unconditional support before and during my move to the UK to work as an Early State Researcher in the MEDOW Project and as a PhD student at Cardiff University and also for the support during this journey. This work is dedicated to them.

# Abbreviations

AAC Alternate Arm Converter

AC Alternating Current

CTL Cascaded Two-Level

CVB Capacitor Voltage Balancing

DC Direct Current

FPGA Field-Programmable Gate Array

${f HVDC}$  High Voltage Direct Current

EtherCAT Ethernet for Control Automation Technology

IGBT Insulated Gate Bipolar Transistor

LCC Line Commutated Converter

MMC Modular Multilevel Converter

MTDC Multi Terminal High Voltage Direct Current

OWF Offshore Wind Farm

PI Proportional-Integral (controller)

PLL Phase-Locked Loop

PWM Pulse-Width Modulation

SM Sub-Module

SOA Safe Operating Area

SOH State Of Health

TOEn Transient Overload Energy

TOE Transient Operational Envelope

TSO Transmission System Operator

VHDL VHSIC (Very High Speed Integrated Circuit) Hardware

${\bf D} escription \ {\bf L} anguage$

VSC Voltage Source Converter

# Symbols

| C        | Capacitance           | F,                                 |

|----------|-----------------------|------------------------------------|

| $C_{th}$ | Thermal Capacitance   | $J/^{\circ}C$                      |

| D        | Load Damping Constant | W/Hz                               |

| f        | Electrical Frequency  | $_{\mathrm{Hz}}$                   |

| $H_s$    | Inertia Constant      | $\mathbf{S}$                       |

| I        | Current               | A                                  |

| L        | Inductance            | Н                                  |

| P        | Active Power          | W                                  |

| $R_{th}$ | Thermal Resistance    | $^{\circ}\mathrm{C/W}$             |

| Q        | Reactive Power        | var                                |

| R        | Permanent Droop       | $\mathrm{Hz/W}$                    |

| T        | Temperature           | $^{\circ}\mathrm{C}$               |

| V        | Voltage               | V                                  |

| $Z_{th}$ | Thermal Impedance     | $^{\circ}\mathrm{C/W}$             |

|          |                       |                                    |

| $\omega$ | angular frequency     | $\mathrm{rad}\cdot\mathrm{s}^{-1}$ |

|          |                       |                                    |

# List of Figures

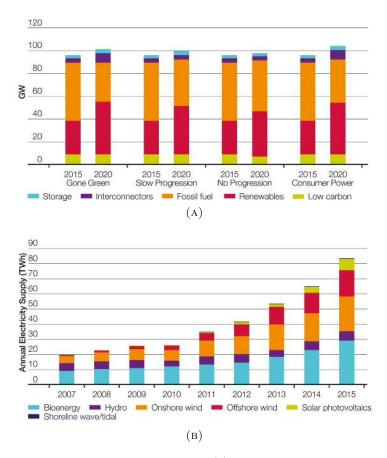

| 1.1  | Electricity generation in the UK: (a) - Amount installed by type 2015-2020 and (b) - Renewable generation history [1] | 2    |

|------|-----------------------------------------------------------------------------------------------------------------------|------|

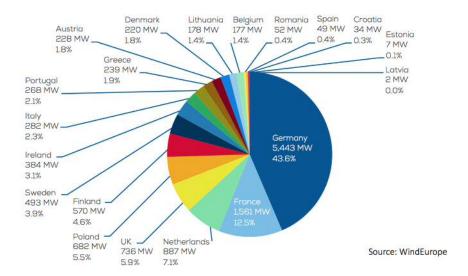

| 1.2  | Market shares for new wind energy capacity installed in Europe during 2016 [2]                                        |      |

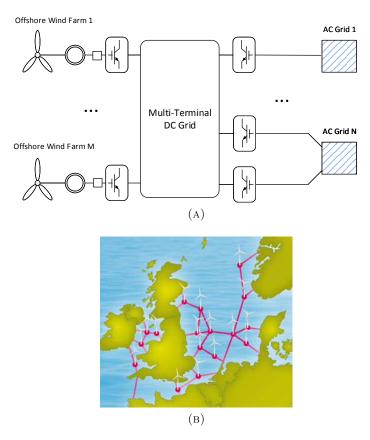

| 1.3  | MTDC supergrid for offshore wind: (a) - General structure and (b) - North Sea vision [3].                             |      |

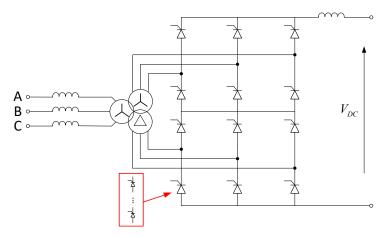

| 2.1  | Typical configuration of a 12-pulse LCC [4]                                                                           | 12   |

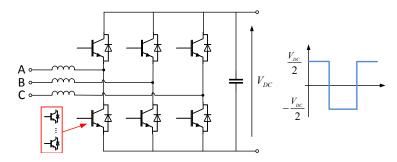

| 2.2  | Reduced-level VSC topologies.                                                                                         |      |

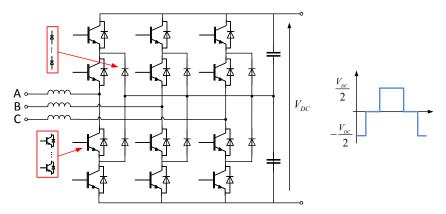

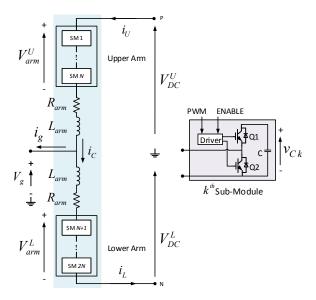

| 2.3  | MMC topology                                                                                                          |      |

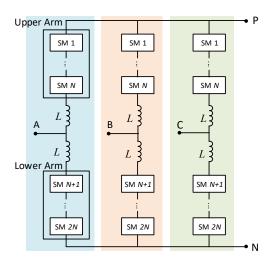

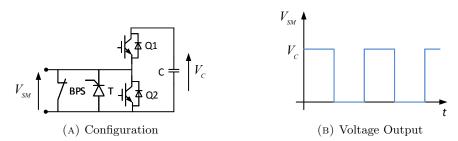

| 2.4  | HB SM                                                                                                                 |      |

| 2.5  | CTL structure [5]                                                                                                     | 17   |

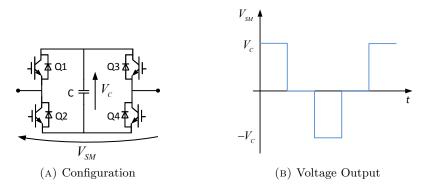

| 2.6  | FB SM                                                                                                                 |      |

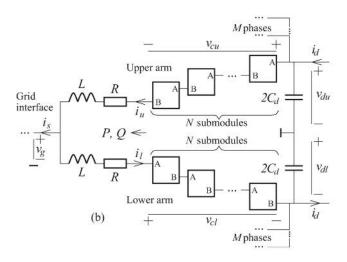

| 2.7  | Single-phase MMC configuration with HB SMs                                                                            | 19   |

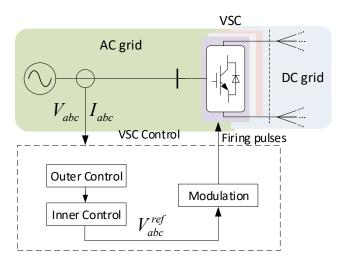

| 2.8  | General control structure of a VSC                                                                                    | 23   |

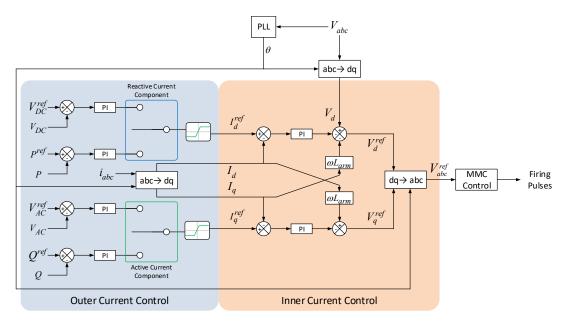

| 2.9  | Outer and inner current control loops of VSCs                                                                         | 24   |

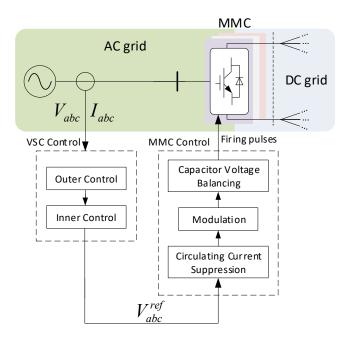

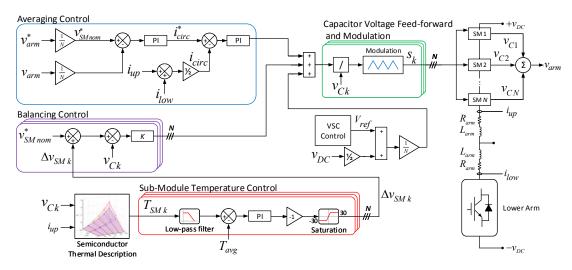

| 2.10 | Control structure of a MMC                                                                                            | 25   |

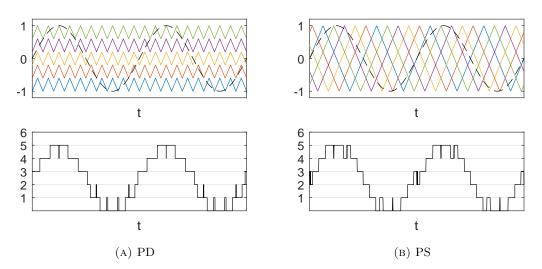

| 2.11 | Typical carriers used in PWM schemes                                                                                  | 27   |

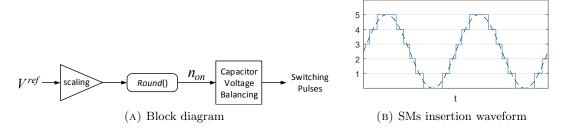

| 2.12 | NLC modulation                                                                                                        | 29   |

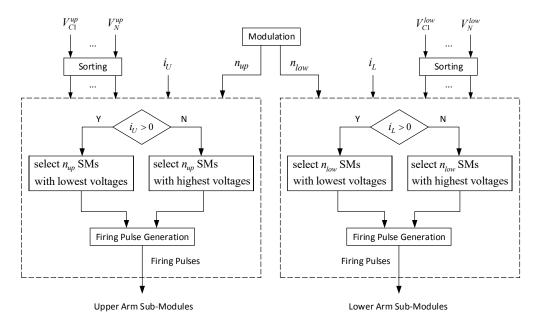

| 2.13 | CVB in a Phase of a MMC                                                                                               | 31   |

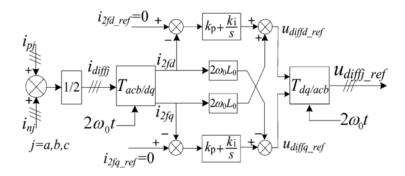

| 2.14 | Circulating current suppression controller [6]                                                                        |      |

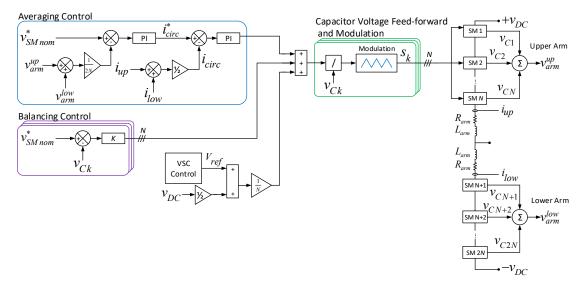

|      | Averaging and balancing control-based CVB in a MMC                                                                    |      |

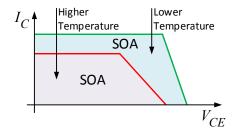

| 2.16 | SOA of a semiconductor module [7]                                                                                     | 39   |

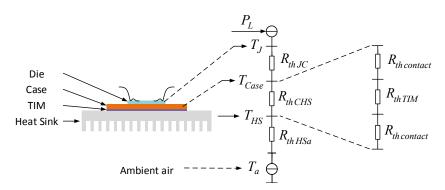

| 3.1  | Equivalent thermal model of a semiconductor module considering the thermal interface with a heat sink                 | 47   |

| 3.2  | Equivalent thermal model of a semiconductor module for the estimation of junction temperature                         |      |

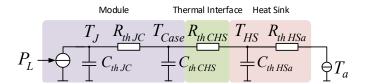

| 3.3  | Flow diagram of a water cooling system [8]                                                                            |      |

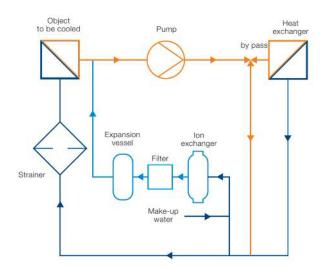

| 3.4  | Typical output characteristic of IGBT die [9]                                                                         |      |

| 3.5  | Typical switching energy losses of IGBT die [9]                                                                       |      |

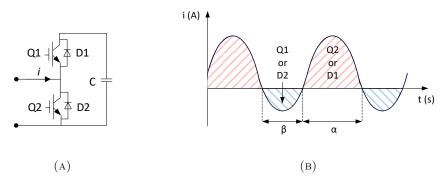

| 3.6  | HB IGBT SM: (a) - Configuration and (b) - Typical waveform for the arm current in an MMC                              | 54   |

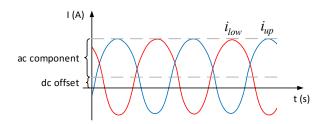

| 3.7  | Typical waveforms for the arm currents in an MMC                                                                      | 54   |

| 3.8  | IR temperature measurement of an IGBT module [10]                                                                     | 58   |

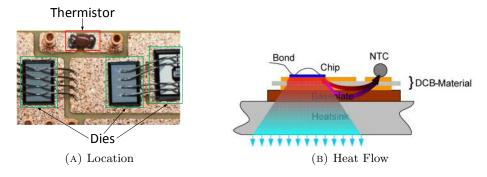

| 3.9  | Thermistor-based temperature measurement in a semiconductor module                                                    |      |

|      | [11]                                                                                                                  | 60   |

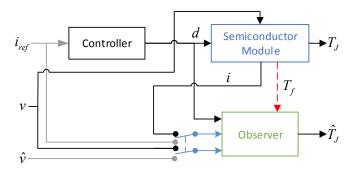

| 3.10 | SO-based junction temperature estimation in a semiconductor module [11]                                               | . 61 |

List of Figures xvi

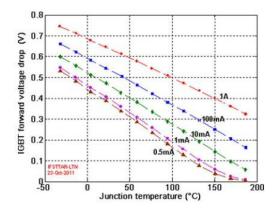

| 3.11 | IGBT forward voltage drop as a function of the device temperature for different measured currents [12].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 63  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

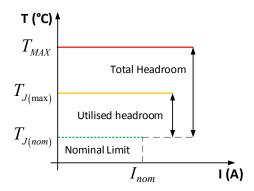

| 4.1  | Influence of the maximum operating temperature on the semiconductor thermal headroom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 71  |

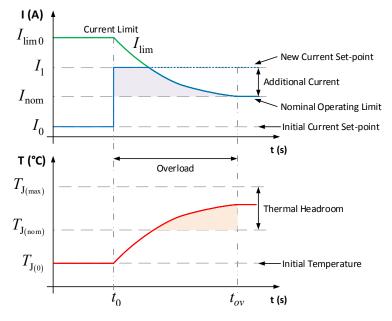

| 4.2  | System response to a current order step with fixed and dynamic current limit with junction temperature feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 73  |

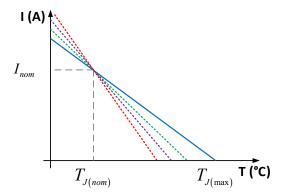

| 4.3  | Influence of the maximum allowed temperature on the dynamic current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 74  |

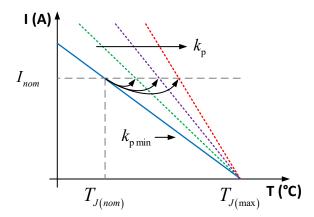

| 4.4  | Shift of the maximum operating temperature at nominal current with increasing proportional gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 75  |

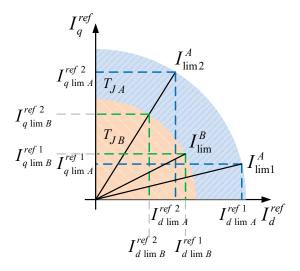

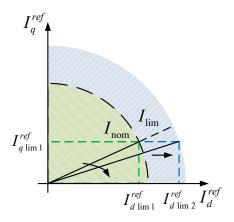

| 4.5  | Extended current limit diagram with flexible limits for the current references $(T_j^A < T_J^B)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 77  |

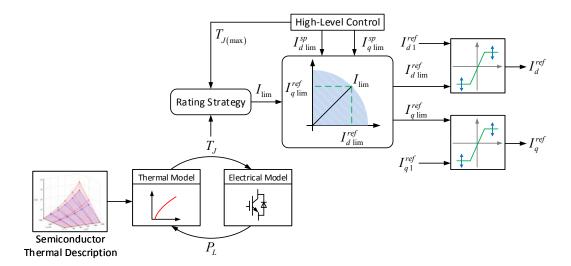

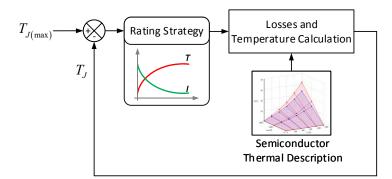

| 4.6  | Current control structure of an MMC with dynamic current limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 79  |

| 4.7  | Maximisation of active current component with dynamic current limits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 79  |

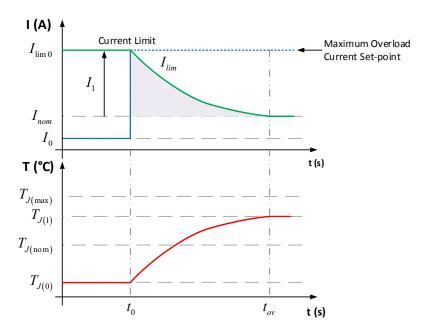

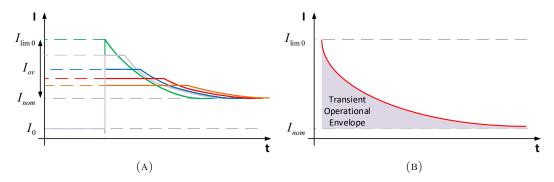

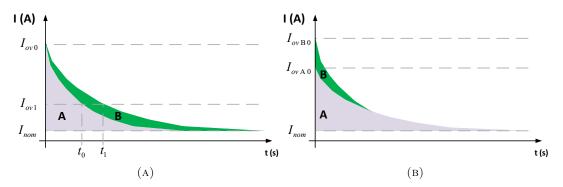

| 4.8  | Transient current overload capability of semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 80  |

| 4.9  | Transient current overload capability of semiconductors: (a) - Mapping of overload current magnitude (y-axis) for different overload times (x-axis)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99    |

| 4.10 | and (b) - TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 82  |

|      | and (b) - Different peak overload current magnitudes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 83  |

| 4.11 | Simple closed-loop system for current limit regulation with semiconduc-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|      | tors temperature feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 85  |

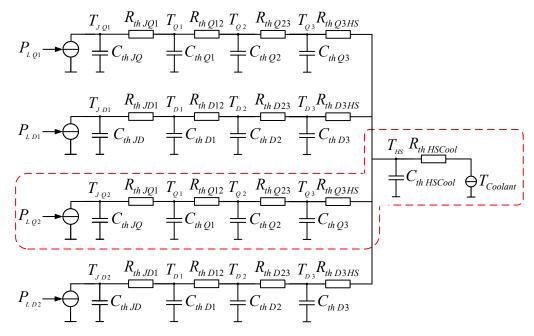

| 4.12 | Cauer-type thermal network for HB semiconductor module Infine<br>on FF75R $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12YT3 |

|      | [9] mounted on a liquid-cooled Seat-Sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

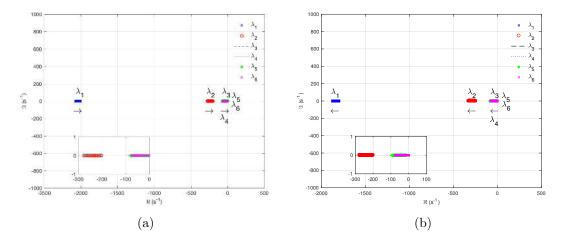

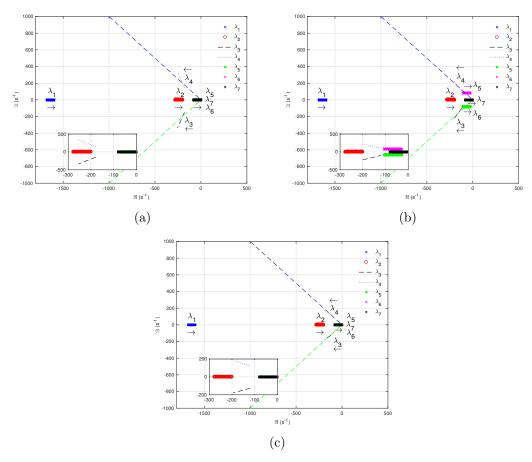

| 4.13 | Eigenvalues of the system for Strategy I: (a) - $k_p$ variation from 0.1 A/°C to 100 A/°C in 0.1 A/°C steps ( $T_{J(max)} = 95$ °C) and (b) - $T_{J(max)}$ variation from 80 °C to 100 °C in 1 °C steps ( $k_p = 5$ A/°C). Arrows indicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|      | growing parameter values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 96  |

| 4.14 | Eigenvalues of the system for Strategy I: (a) - $K_P$ variation from 1 A/°C to 20 A/°C in 0.1 A/°C steps ( $K_I = 0.001$ A/(°C s) and $T_{J(max)} = 95$ °C); (b) - $K_I$ variation from 0.0001 A/(°C s) to 0.025 A/(°C s) in 0.0001 A/(°C s) steps ( $K_P = 5$ A/°C and $T_{J(max)} = 95$ °C) and (c) - $T_{J(max)}$ variation from 80 °C to 100 °C in 1 °C steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s)) A significant steps ( $K_P = 5$ A/°C and $K_I = 0.001$ A/(°C s) | 00    |

| 4.15 | 0.001A/(°Cs)). Arrows indicate growing parameter values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 98  |

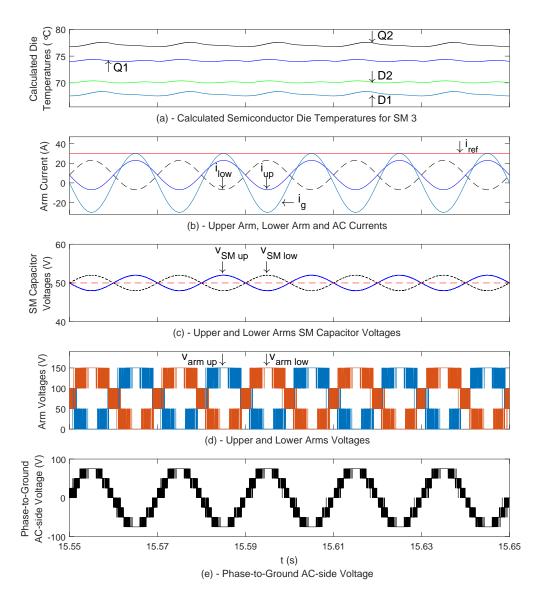

|      | Steady-state quantities in phase A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 4.16 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

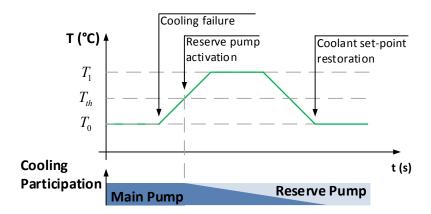

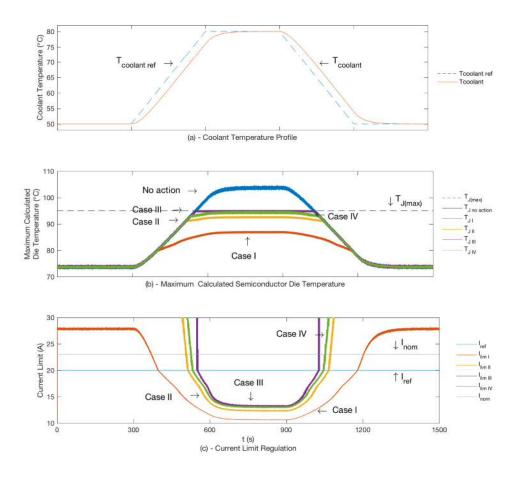

|      | Temperature regulation during a cooling failure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 102 |

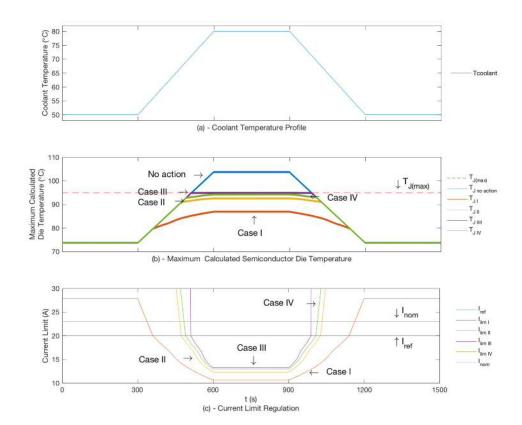

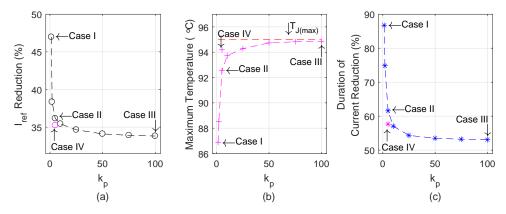

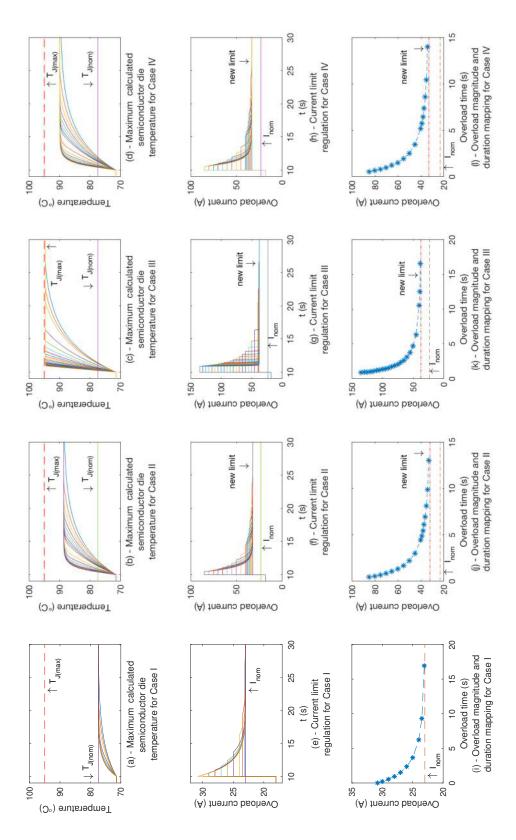

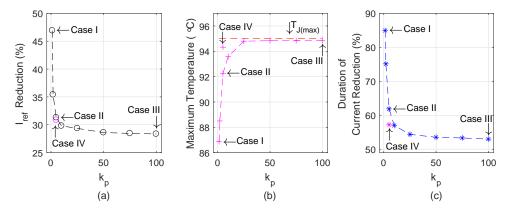

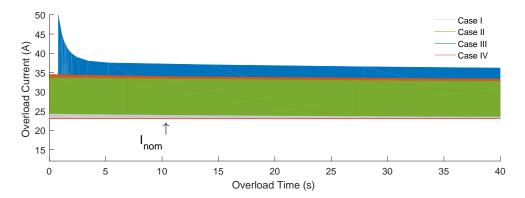

| 4.18 | Simulation results of temperature regulation during a cooling failure as a function of the proportional gain: (a) - Maximum percent reduction in the reference current; (b) - Maximum calculated semiconductor die temperature and (c) - Percent duration of the current curtailment period with respect to the duration of the cooling profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 103   |

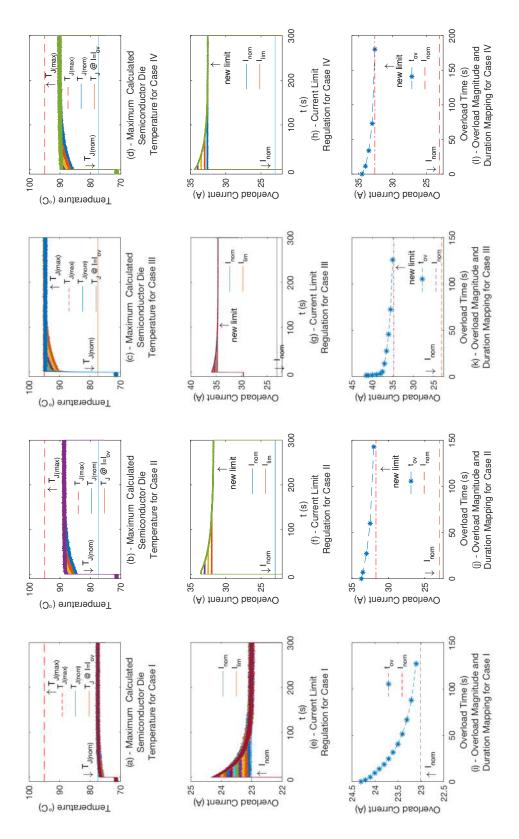

| 4.19 | Temperature regulation during a current overload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

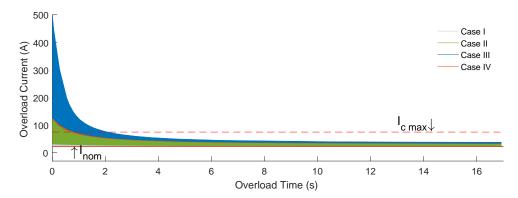

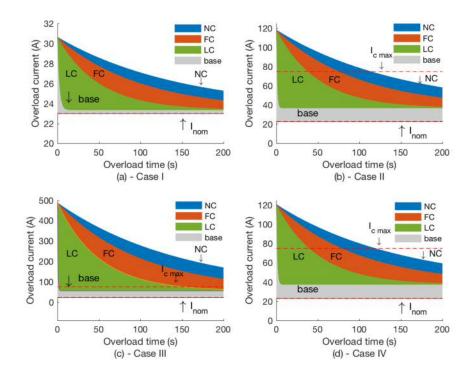

|      | Semiconductors TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|      | Variation of semiconductors TOE for different heat sink time constants.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

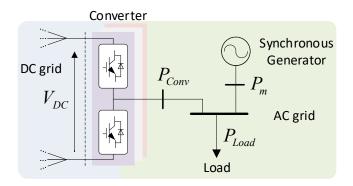

|      | Single-line representation of the test system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

List of Figures xvii

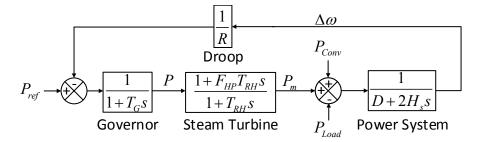

| 4.23 | Primary frequency regulation of the AC grid, including speed governor and steam turbine | 110      |

|------|-----------------------------------------------------------------------------------------|----------|

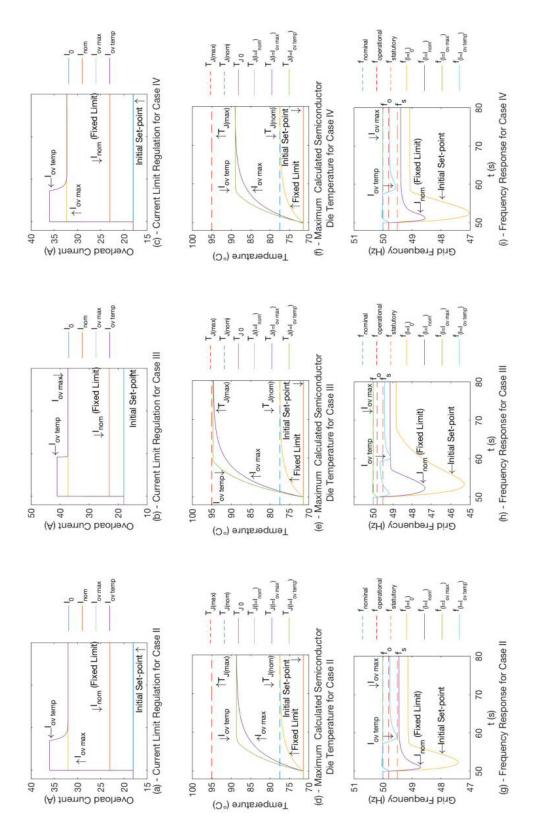

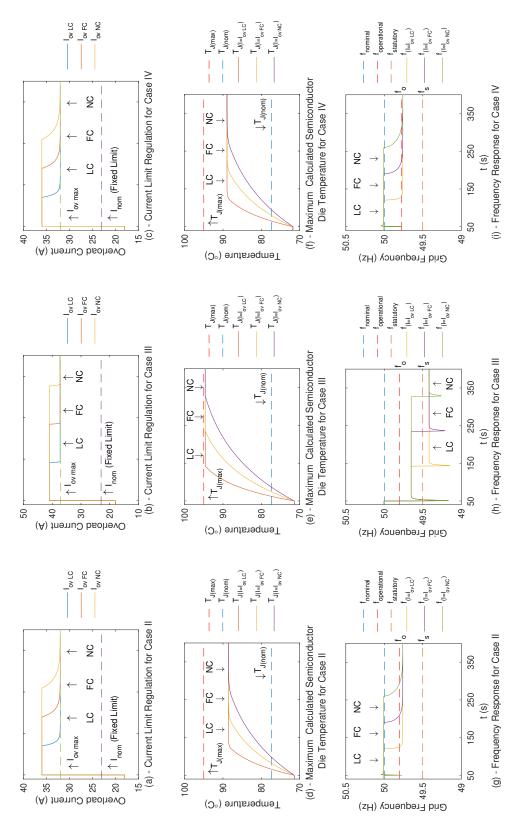

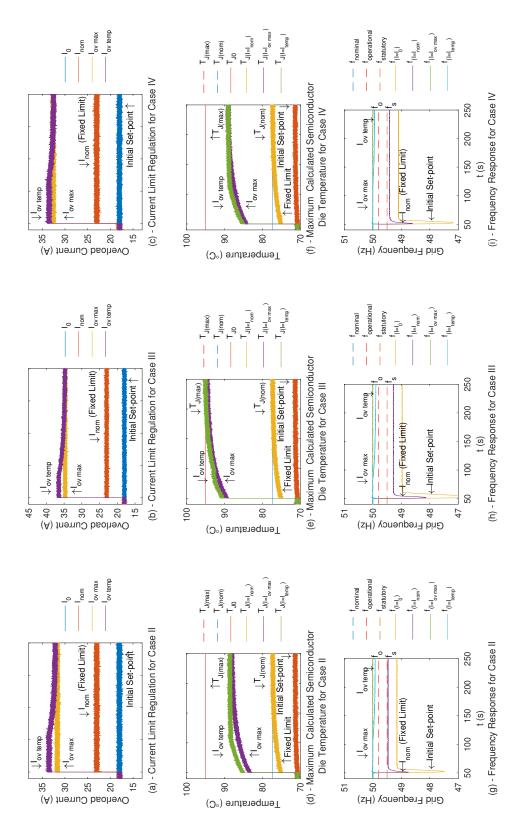

| 4 24 | Frequency regulation during current overload as response to a load increase             |          |

|      | Frequency regulation during current overload as response to a load in-                  | 110      |

| 1.20 | crease for different heat sink time constants                                           | 116      |

|      |                                                                                         | 110      |

| 5.1  | Proposed per-arm individual SM voltage control strategy with tempera-                   |          |

|      | ture regulation and balancing                                                           |          |

| 5.2  | Operational voltage limits in a SM                                                      | 123      |

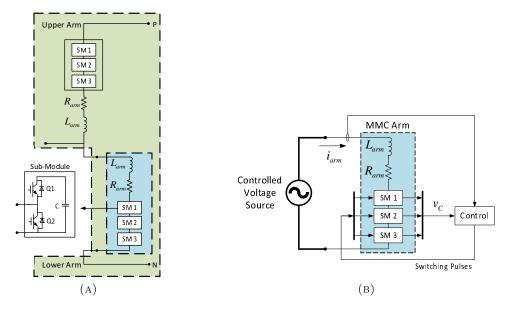

| 5.3  | Bode Diagram of the SM temperature control open-loop transfer function.                 | 125      |

| 5.4  | SM temperature profile with and without thermal regulation when sub-                    |          |

|      | jected to a thermal disturbance                                                         | 126      |

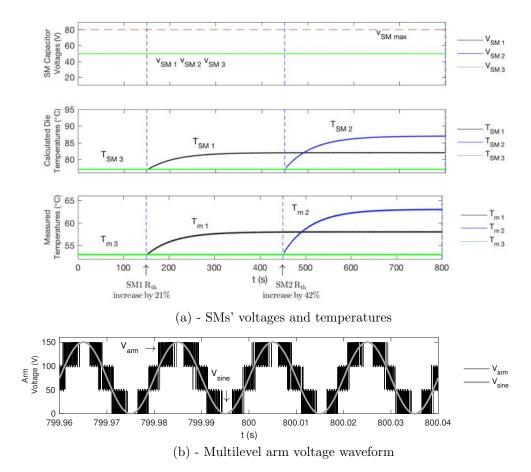

| 5.5  | Simulation of response of SMs' voltages and temperatures to thermal                     |          |

|      | imbalances without thermal regulation                                                   |          |

| 5.6  | Simulation of SMs thermal regulation as a response to thermal imbalances                | 130      |

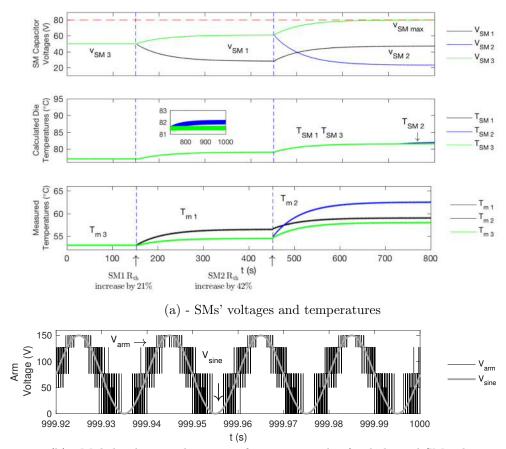

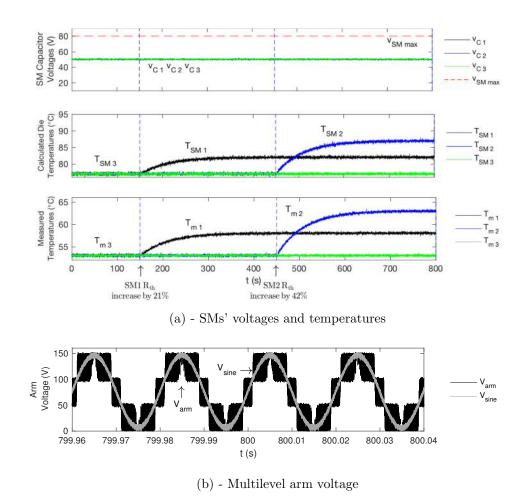

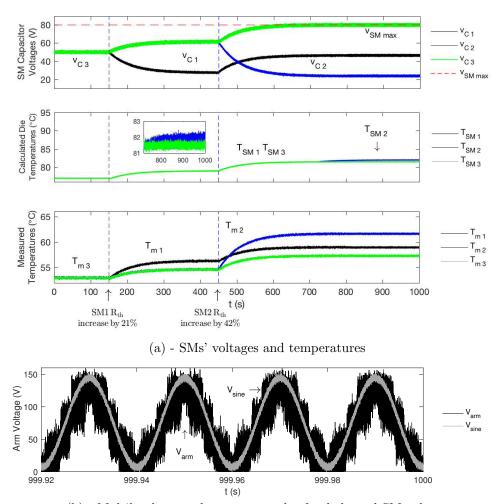

| 5.7  | SMs thermal regulation for a thermal disturbance: (a) - Sub-Modules'                    |          |

|      | voltages and temperatures and (b) - Multilevel arm voltage waveform                     |          |

|      | without (left) and with (right) unbalanced SM voltages as a result of                   |          |

|      | thermal regulation                                                                      | 132      |

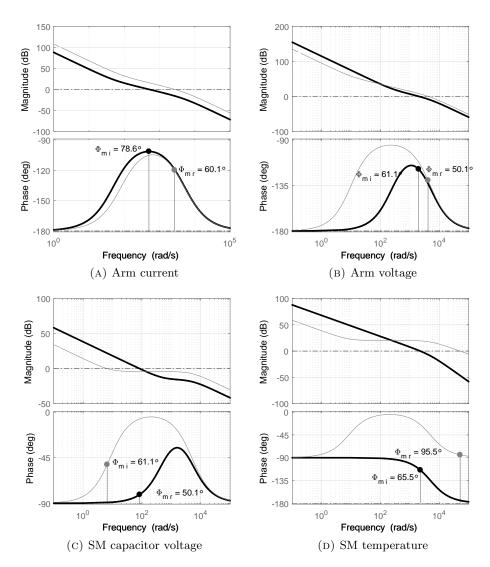

| 5.8  | SMs thermal regulation voltages as a function of the number of SMs for                  | 100      |

|      | different thermal imbalances                                                            | 133      |

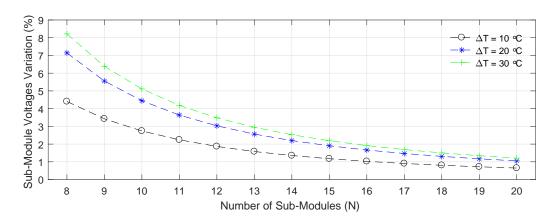

| 5.9  | SM voltages variation as a function of the number of SMs for different                  | 104      |

| F 10 | thermal imbalances.                                                                     | 134      |

| 5.10 |                                                                                         | 194      |

|      | for different thermal imbalances                                                        | 134      |

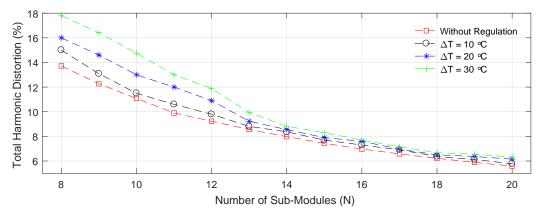

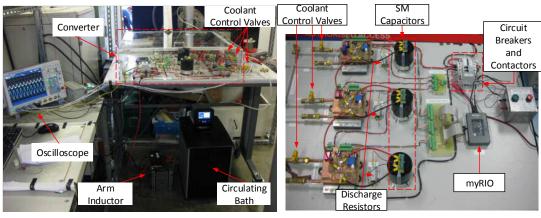

| 6.1  | MMC setup: (a) - Complete phase leg and (b) - Reduced-order arm setup.                  | 139      |

| 6.2  | Control strategy of the reduced-order MMC converter arm                                 |          |

| 6.3  | Open-loop transfer functions Bode diagrams for different controllers in the             |          |

|      | reduced-order MMC arm control strategy. Solid black and dashed grey                     |          |

|      | curves represent the system with the ideal analytical and experimental PI               |          |

|      | controller's parameters, respectively                                                   | 146      |

| 6.4  | Experimental MMC arm setup                                                              | 147      |

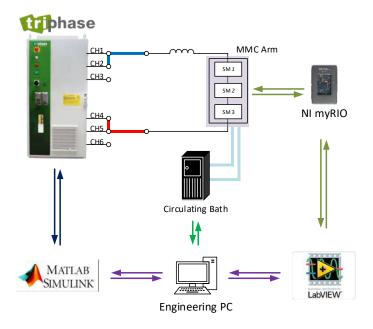

| 6.5  | Overall connection and communication structure for the control of the                   |          |

|      | experimental MMC arm setup                                                              |          |

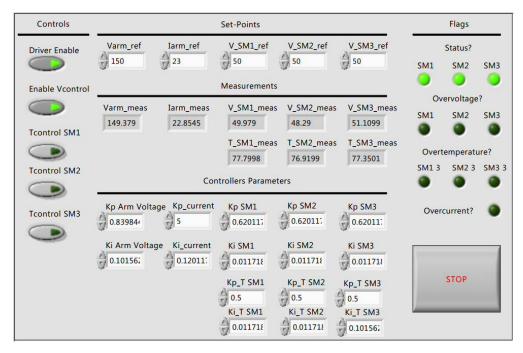

| 6.6  | LabVIEW Graphical User Interface                                                        | 148      |

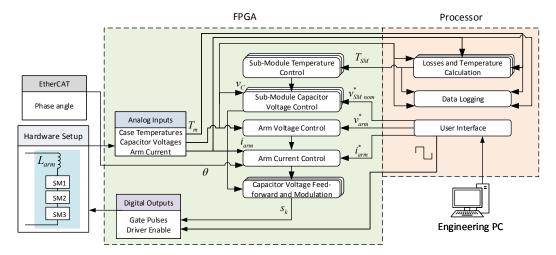

| 6.7  | Task coordination between the processor and the FPGA in the myRIO                       |          |

|      | board                                                                                   |          |

| 6.8  | Experimental SM configuration                                                           | 150      |

| 6.9  | PLL-based synchronisation between MMC arm voltage and current and                       |          |

|      | Triphase output                                                                         | 151      |

| 6.10 | Thermistor placement in Infineon HB IGBT module FF75R12YT3: (a) -                       |          |

|      | Configuration [9] and (b) - Physical module with embedded thermistor                    | 152      |

| 6.11 | Thermal network of IGBT module Infineon FF75R12YT3 [9] considered                       |          |

|      | in the experimental tests                                                               |          |

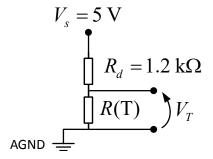

|      | Thermistor resistance measurement circuit                                               | 153      |

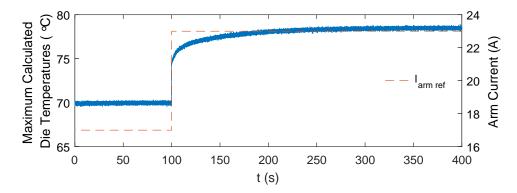

| 6.13 | Maximum calculate die temperatures response to a step in the arm current                | <b>.</b> |

|      | reference.                                                                              |          |

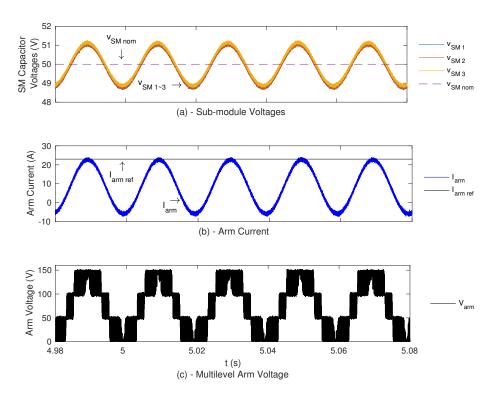

| 6 14 | Experimental MMC arm results                                                            | 156      |

List of Figures xviii

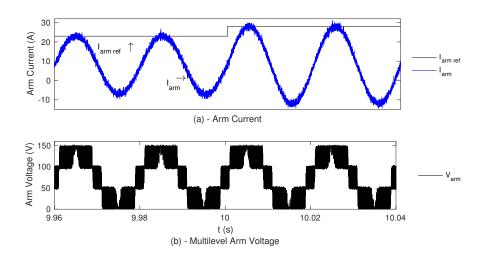

| 6.15 | Experimental response to a step in the arm current reference 156                                                                                                                                                                                                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.16 | Experimental temperature regulation during a cooling failure 157                                                                                                                                                                                                                               |

| 6.17 | Experimental results of temperature regulation during a cooling failure as a function of the p roportional gain: (a) - Maximum percent reduction in the reference current; (b) - Maximum calculated semiconductor die temperature and (c) - Percent duration of the current curtailment period |

|      | with respect to the duration of the cooling profile                                                                                                                                                                                                                                            |

| 6.18 | Experimental results of temperature regulation during a current overload. 160                                                                                                                                                                                                                  |

| 6.19 | Semiconductors experimental TOE                                                                                                                                                                                                                                                                |

| 6.20 | Experimental frequency regulation during current overload as response to                                                                                                                                                                                                                       |

|      | a load increase                                                                                                                                                                                                                                                                                |

| 6.21 | Experimental response of SMs' voltages and temperatures to thermal imbalances without thermal regulation                                                                                                                                                                                       |

| 6.22 | Experimental SMs thermal regulation as a response to thermal imbalances. 166                                                                                                                                                                                                                   |

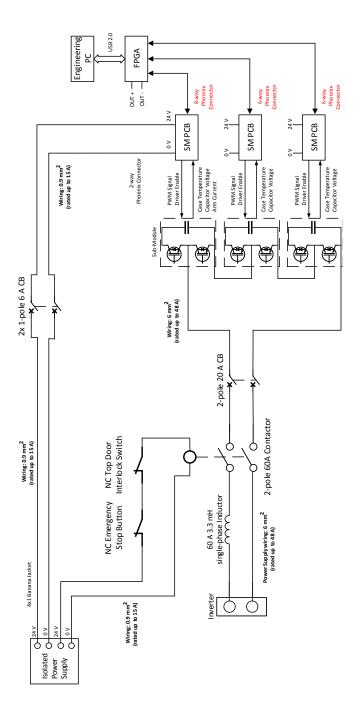

| A.1  | Wiring diagram of the experimental MMC arm setup                                                                                                                                                                                                                                               |

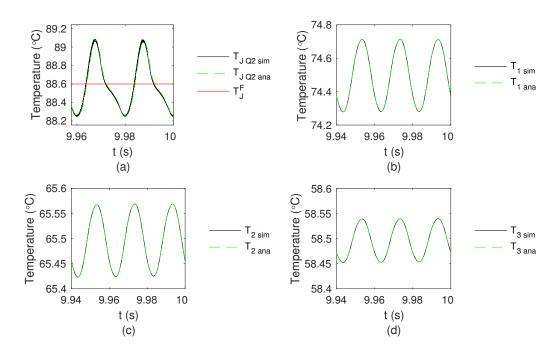

| B.1  | Comparison between simulation and analytical model for dynamic rating strategy A, with $k_p = 5$ A/°C and $T_{J(max)} = 95$ °C: (a) - $T_{JQ2}$ and $T_J^F$ ;                                                                                                                                  |

|      | (b) - $T_1$ ; (c) - $T_2$ and (d) - $T_3$                                                                                                                                                                                                                                                      |

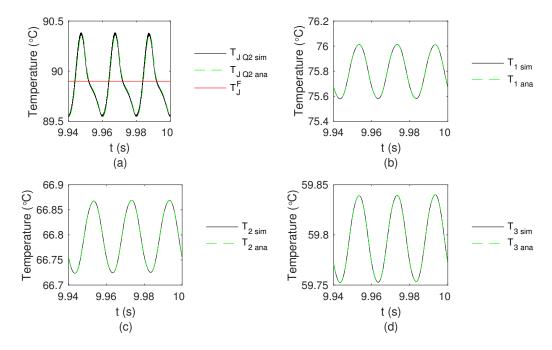

| B.2  | Comparison between simulation and analytical model for dynamic rating strategy B, with $k_p = 5 \text{A}/^{\circ}\text{C}$ , $T_{J(max)} = 95 ^{\circ}\text{C}$ and $K_I = 0.001 \text{A}/(^{\circ}\text{C}\text{s})$ :                                                                        |

|      | (a) - $T_{JQ2}$ and $T_J^F$ ; (b) - $T_1$ ; (c) - $T_2$ and (d) - $T_3$                                                                                                                                                                                                                        |

# List of Tables

| 4.1 | Thermal network parameters for IGBT module Infineon FF75R12YT3 [9] 86                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| 4.2 | MMC system parameters                                                                                                               |

| 4.3 | Semiconductor specifications for IGBT module FF75R12YT3 96                                                                          |

| 4.4 | Eigenvalues of the system for strategy A                                                                                            |

| 4.5 | Eigenvalues of the system for strategy B                                                                                            |

| 4.6 | Dynamic rating strategies case studies parameters                                                                                   |

| 4.7 | Semiconductors TOEn for different heat sink time constants (kA <sup>2</sup> s) 108                                                  |

| 4.8 | Comparison between analytical and simulation results for the variation of overload durations for different heat sink time constants |

| 4.9 | Primary frequency regulation model parameters [13]                                                                                  |

| 5.1 | Parameters of the MMC with 10 SMs per arm                                                                                           |

| 6.1 | Reduced-order MMC arm controllers parameters                                                                                        |

| 6.2 | Experimental thermal network parameters for IGBT module Infineon                                                                    |

|     | FF75R12YT3 [9]                                                                                                                      |

| 6.3 | Dynamic rating strategies case studies' parameters for experimental tests 155                                                       |

| 6.4 | Comparison of simulation and experimental results for the semiconductors                                                            |

|     | $TOEn (kA^2s)$                                                                                                                      |

## Chapter 1

# Introduction

#### 1.1 Background

The consequences of global warming and the need for CO<sub>2</sub> emissions reduction lead the push to a low carbon power system and the shift from fossil fuels towards renewable energy based generation [14–16]. Ambitious targets to the decarbonisation of the electricity sector have been set by the European Union (EU) [17]. In the UK these policies mandate that 15 % of the total generation must come from renewable energy resources by 2020 [18], aiming at achieving a greenhouse gas emissions reduction of 80 % by 2050. This has lead to an increasing market penetration of renewable energy resources such as wind and solar [19–21].

Achieving these targets requires a significant shift in the paradigm by which power generation and transmission presently occurs. For all the different scenarios analysed by National Grid, the UK Transmission System Operator (TSO) for Gas and Electricity, by which these targets can be met, only the 'Gone Green' scenario embodies a balanced and realistic strategy. This scenario combines the power generation, transport and heat. It can be observed in Figure 1.1 (a) that between 2015 and 2020 the installation of renewable generation is the main contributor to the reduction in the fossil fuel in the power generation mix, as aged and inefficient coal based power plants are decommissioned [22].