# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/111500/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Zaidi, Z. H., Lee, K. B., Roberts, J. W., Guiney, I., Qian, H., Jiang, S., Cheong, J. S., Li, P., Wallis, D. J., Humphreys, C. J., Chalker, P. R. and Houston, P. A. 2018. Effects of surface plasma treatment on threshold voltage hysteresis and instability in metal-insulator-semiconductor (MIS) AlGaN/GaN heterostructure HEMTs. Journal of Applied Physics 123 (18), 184503. 10.1063/1.5027822

Publishers page: http://dx.doi.org/10.1063/1.5027822

# Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See <a href="http://orca.cf.ac.uk/policies.html">http://orca.cf.ac.uk/policies.html</a> for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

Effects of surface plasma treatment on threshold voltage hysteresis and instability in metal-insulator-semiconductor (MIS) AlGaN/GaN heterostructure HEMTs

Z.H. Zaidi<sup>1</sup>, K.B. Lee<sup>1</sup>, J.W. Roberts<sup>2</sup>, I. Guiney<sup>3</sup>, H. Qian<sup>1</sup>, S. Jiang<sup>1</sup>, S.J. Cheong<sup>1</sup>, P. Li<sup>1</sup>, D.J. Wallis<sup>3</sup>, C.J. Humphreys<sup>3</sup>, P.R. Chalker<sup>2</sup> and P.A. Houston<sup>1</sup>

<sup>1</sup> Department of Electronic and Electrical Engineering, The University of Sheffield, Mappin Street Sheffield, S1 3JD,

United Kingdom

$^2 Centre\ for\ Materials\ and\ Structures,\ University\ of\ Liverpool,\ The\ Quadrangle,\ Brownlow\ Hill,\ Liverpool,\ L69\ 3GH,\ United\ Materials\ Additional Conference of the Conference$

Kingdom

<sup>3</sup>Department of Material Science and Metallurgy, The University of Cambridge, 27 Charles Babbage Road Cambridge,

CB3 0FS, United Kingdom

\*corresponding author: zaffar.zaidi@sheffield.ac.uk

**Abstract:** In a bid to understand the commonly observed hysteresis in the threshold voltage in MISHEMTs during gate forward bias stress, we analyzed a series of measurements on samples with no pretreatment and with two different plasma pretreatments. The observed changes is quasi-equilibrium threshold voltage ( $V_{TH}$ ), forward bias related  $V_{TH}$  hysteresis and electrical response to reverse bias stress required the use of a disorder induced gap state (DIGS) model combined with a discrete level donor at the dielectric/semiconductor interface. TCAD modelling was carried out which demonstrated the possible differences in the interface state distributions to explain the observations consistently.

#### Introduction

In recent years, GaN based AlGaN/GaN high electron mobility transistors (HEMTs) have demonstrated excellent potential for both RF and power electronics applications owing to very favorable material characteristics such as high 2DEG mobility and concentration and a wide band gap to support a large blocking voltage. Metal-insulator-semiconductor (MIS) structures are often preferred over Schottky gate structures in power electronics applications because of their ability to suppress the gate leakage current, engineer the threshold voltage for both depletion and enhancement mode operation, enhance the device capability to withstand larger gate voltage swing and to improve the gate-drain breakdown voltage [1-3].

There have been several successful demonstrations of using various gate dielectric layers by different deposition techniques [4-11] to achieve the aforementioned objectives in AlGaN/GaN HEMTs. However, introducing a gate dielectric layer inserts an additional, likely non-ideal, interface in the structure which can result in charge trapping/de-trapping effects associated with the dielectric/III-nitride interface and/or the bulk dielectric itself. The dynamic charging and discharging process of these traps can affect the stability of the threshold voltage causing significant variations in switching performance. The effects can be observed through threshold voltage hysteresis in bi-directional gate transfer sweeps from below threshold to high forward bias and back again [12-17]. Previously, dynamic processes have been studied in detail using CV dispersion measurements as a function of frequency and temperature [18] and stress recovery analysis in HEMTs by monitoring the threshold voltage  $(V_{TH})$  after forward gate bias [14-25]. These studies have yielded a broad distribution of stress and recovery time constants, suggesting a wide distribution of traps both at the interface and within the AlGaN barrier [16]. However, attempts at directly comparing different surface preparations before the dielectric deposition have been limited [26]. Also, in power switching applications, GaN HEMTs are required to block large voltages in the pinched-off state and any threshold voltage instability in such situations can be a serious concern. There are a few reports on the influence of negative gate bias stress on the threshold voltage in recessed barrier AlGaN/GaN MISHEMTs [27] and MOS GaN FETs [28-29] but there has been no comparisons highlighting the differences between surface preparations and no attempts at consistency between forward and reverse stress models.

In terms of mitigation of these unwanted dynamic effects, using a NH<sub>3</sub>/Ar/N<sub>2</sub> or N<sub>2</sub> plasma to achieve surface nitridation [18,19,30,31] and oxygen plasma treatment [20] prior to dielectric deposition have been shown to be effective. In most of this past work the focus has been on understanding the dynamic mechanisms leading to drift and/or hysteresis in  $V_{TH}$ . In practical device operation the quasi-equilibrium value and stability of  $V_{TH}$ , as well as its dynamical responses, are important and the effects of surface treatment prior to dielectric deposition are crucial to minimise these effects. There is no standard for stress magnitudes and times, which make it difficult to compare publications across the literature and direct comparison of different surface preparations on the same samples using a wide range of probing techniques are lacking and consistency between all observations has still not been reported.

In this work, we have used aluminum oxide ( $Al_2O_3$ ) as a gate dielectric in AlGaN/GaN MISHEMTs because of its wide band gap (7-9eV), large conduction band offset (2.16eV), high breakdown field (>10MV/cm) and dielectric constant (8-10) [13]. We have performed *in-situ* nitrogen ( $N_2$ ) and argon (Ar) plasma treatments before atomic layer deposition (ALD) of  $Al_2O_3$  in an attempt to understand the role of both the plasma and its chemical nature. In the past, *in-situ*  $N_2$  plasma [18,19,30,31] and Ar plasma treatment [21] were studied separately. Here we have compared *in-situ*  $N_2$  and Ar plasma treatments on depletion mode AlGaN/GaN MISHEMTs before the deposition of 20nm  $Al_2O_3$  dielectric using ALD and carried out positive and negative gate bias stress measurements to evaluate the stability of the threshold voltage. We have studied the effects of high forward gate overdrive, negative gate bias stress and the shift in the quasi-equilibrium  $V_{TH}$ . We propose a model to link and explain all these observations which has not been attempted in the past.

#### **Results and Discussion**

The wafers were grown by Metal Organic Chemical Vapor Deposition (MOCVD) on 6-inch Si substrates. To facilitate the growth on Si, a nucleation layer of AlN (250nm) was used together with a series of compositionally graded carbon doped AlGaN and GaN layers. A 1 nm mobility enhancement AlN layer was grown on the channel layer and an Al<sub>0.28</sub>Ga<sub>0.78</sub>N barrier layer of thickness 27nm grown on top of that. Finally, the wafer was capped with a 2nm undoped GaN layer. A standard device fabrication procedure was followed with mesa isolation achieved by a chlorine-based recipe in an inductively coupled plasma etching chamber. The ohmic contacts used Ti/Al/Ni/Au (20nm/120nm/20nm/45nm) metal stacks which were annealed at 850°C for 30 seconds. After ohmic contact formation, a standard 100nm SiO<sub>2</sub> layer was deposited using the plasma enhanced chemical vapor deposition (PECVD) technique. A 1.5µm gate window was etched through the SiO2 layer. Before the 20nm Al2O3 gate dielectric atomic layer deposition, in-situ 150W N<sub>2</sub> plasma or 50W Ar plasma treatment for 5 minutes was performed on the samples and one sample was prepared without any pre-treatment to serve as the reference sample. After dielectric depositions, forming gas annealing (FGA) was performed in N<sub>2</sub> and H gas ambient at 430°C for 30 minutes. Then T-shape gates with 1µm gate field plates were defined using a standard Ni/Au (20nm/180nm) metal stack. Finally, bond pads using Ti/Au (20nm/200nm) were formed via etches through the dielectric layers. Hall measurements yielded a mobility of 1909 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 2DEG density of 8.7×10<sup>12</sup>cm<sup>-2</sup>.

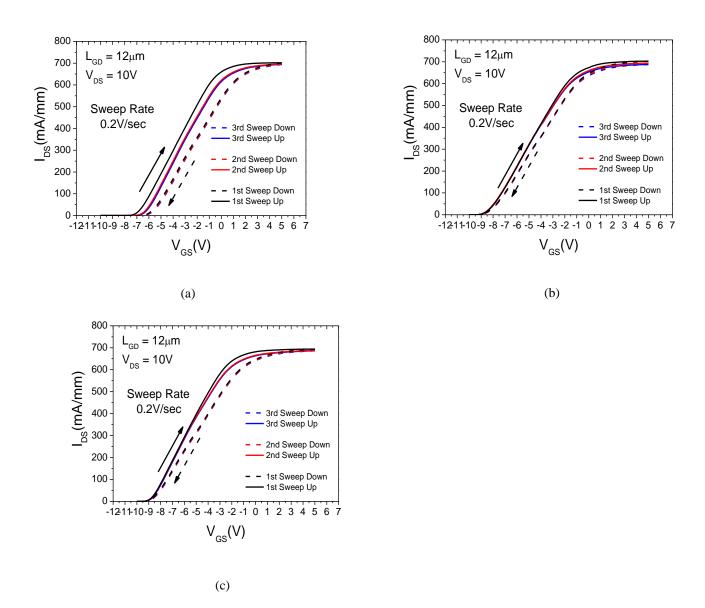

Figure 1. The gate transfer characteristics of AlGaN/GaN MISHEMT before (a) and after (b) 150W  $N_2$  and (c) 50W Ar plasma pre-treatment.

The gate transfer characteristics of AlGaN/GaN MISHEMT devices with and without in-situ N<sub>2</sub> and Ar plasma pre-treatment before the 20nm Al<sub>2</sub>O<sub>3</sub> deposition are shown in figure 1. Starting from the virgin device, the gate transfer sweep is performed from -10V to +5V  $V_{GS}$  upward and then backward from +5V to -10V  $V_{GS}$  with  $V_{DS}$  kept at 10V. This bi-sweep is repeated three times. It can be seen from figure 1 (a) that, in the reference sample after the first upward sweep, there is a positive shift in the threshold voltage compared with the second upward sweep and a considerable hysteresis (~1.2V) in the threshold voltage. This is attributed to trapped electrons at the interface between the dielectric and III/nitride semiconductor and/or bulk dielectric traps when the gate is sufficiently positive biased to facilitate electron transfer from the 2DEG. Once the electrons are trapped they are slow to emit and travel to the channel when the positive gate bias is removed. This gives rise to a time dependent positive shift in the threshold voltage or hysteresis. Regardless of the quasi-equilibrium threshold voltage the transferred charge injected into the dielectric interface is related to the voltage only, since the forward bias capacitance is just that due to the dielectric once electron transfer occurs, as indicated by the loss of gate control (figure 1). The origin of the interface traps can be due to the presence of a poor quality native oxide layer formed on the semiconductor surface, dangling bonds or interface impurities. In the  $N_2$  and Ar plasma treatment samples in figure 1 (b) and (c) the shift in the threshold voltage between the first and subsequent sweeps and hysteresis, measured at the mid current point, is reduced ( $\Delta V_{TH}$  from 1.2V (reference) to 0.2V in the N<sub>2</sub> and 0.25V in the Ar plasma treated sample). In addition, there is also a negative shift in the quasiequilibrium threshold voltage (allowed to stabilize over several days) of about ~1.5 to 2V after both plasma pre-treatments.

## **Hysteresis**

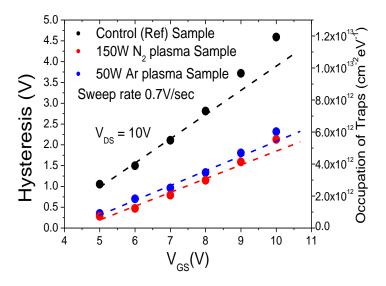

Considering the hysteresis first, the corresponding reduction in the hysteresis voltage on the plasma treated samples compared to the untreated samples under the same bias sweep conditions indicates either a reduction in the number of trapped electrons and/or changes to the capture/emission dynamics. To test for a change in the number of trapped electrons due to the treatment, we performed hysteresis measurements as a function of forward gate bias, keeping the forward bias duration constant. Figure 2 shows the hysteresis increasing systematically with the increase in positive gate bias voltage up to +10V  $V_{GS}$  for all samples. The lack of saturation of the hysteresis voltage with increasing bias indicates the number of interface traps exceeds the electron charge resulting from the forward gate bias for the range of biases and samples considered. Any net reduction in the number of interfacial traps due the plasma

treatment would have little effect under these conditions, provided the trap numbers still dominate. Note, however, that the slopes of the linear portion of theses curves ( $V_{GS}$  below ~8 V) are different for the plasma and untreated samples. For hysteresis measurement times much less than the emission times of the trapped electrons, the slopes should be related to the oxide geometric capacitance which is fixed. Hence, the lack of a common slope confirms a decrease in the trapped electron emission times as a result of the plasma treatment. This observation is reinforced by the tapering of the hysteresis voltage observed near the end of the measurement in the treated samples which indicates significant emission of trapped electrons during the full measurement time (~25 s). However, the emission pathway for electrons from the interface to the 2DEG channel through the AlGaN barrier is expected to be unchanged between the treated and untreated samples. A possible reason for the decreased emission time could be that a greater proportion of trapped electrons occur near the conduction band of the barrier, enabling these electrons to more easily emit into the conduction band or gain an energy advantage during the hopping transport through the barrier (further explanation later). Over the range of devices measured, the N<sub>2</sub> plasma treated sample showed only marginally improved hysteresis compared to the Ar plasma treated sample, indicating perhaps that nitridation [18,19,30,31] in not important under these conditions.

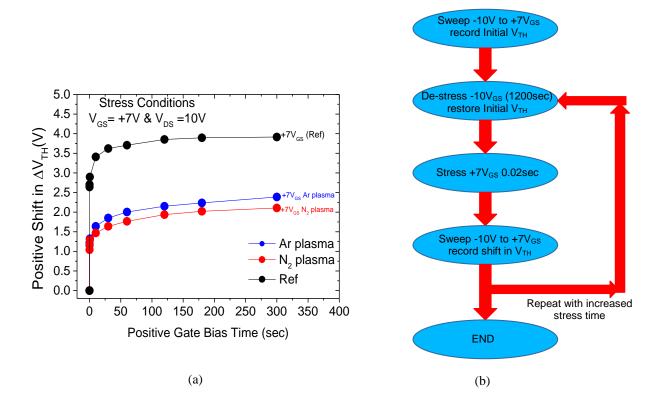

We next look at the effects of increasing the gate forward bias stress time. Figure 3 (a) and (b) shows the positive threshold shift with forward bias stress time and the measurement sequence respectively. The devices are de-stressed with negative gate bias to restore the initial threshold voltage and the experiment is repeated with increasing gate stress time. The gate transfer sweep used to measure the shift in threshold voltage takes about 25 seconds to complete, at which time some relaxation of the trapped charge will occur, resulting in a reduction in the measured threshold voltage shift over that immediately after the forward bias stress. Despite this, the data of Figure 3 indicates two distinct charging mechanisms. These can be explained by a rapid occupation of interfacial traps occurring initially, followed by a much slower tunneling to traps within the dielectric [14-17]. The observed (slower) timescale for the tunneling into the dielectric is similar for all three samples, as expected since the pretreatment will not affect the bulk properties of the dielectric. The data is also consistent with the notion that the pretreatment increases the speed of relaxation of the charge from the interface to the 2DEG where the faster plasma treated samples show a reduced shift in threshold voltage during the hysteresis measurement.

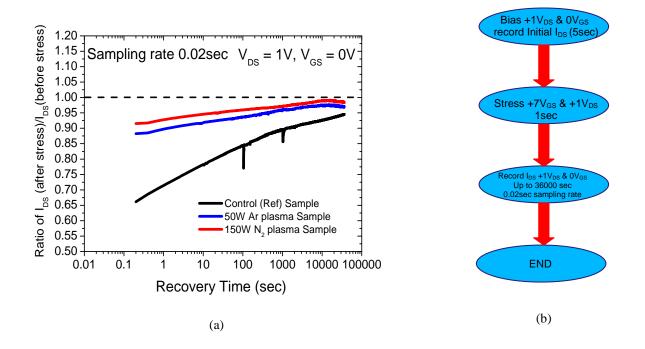

To gain a better understanding of the hysteresis-related relaxation process, continuous recovery times in response to forward gate bias were measured and are shown in figure 4. The device drain current was first measured with no gate bias and  $V_{DS} = 1$ V to serve as a reference.  $V_{DS}$  was limited to 1 V in this setup to avoid influence due to heating effects. The devices are then subjected to a high positive gate overdrive condition ( $V_{GS} = +7V$ ,  $V_{DS} = 0V$ ) for 1 sec. The duration for the positive gate overdrive of 1 sec was chosen to limit the electron charge trapping to within the semiconductor/dielectric interface and avoid charge spillover as much as possible to the slower emitting bulk dielectric traps. After the forward gate overdrive, the devices are biased back to  $V_{GS} = 0V$  and  $V_{DS} = 1V$  and the drain current, which reflects the changes in the 2DEG charge due to trapping in the semiconductor/dielectric interface, is measured over a period of 10 hours with a 200 msec sampling rate. The ratio of drain current before and after the gate overdrive and experimental test sequence is shown in figure 4(a) and (b) respectively. The variations in the drain current reflect the variations in trapped charge under the gate. Due to the rapid sampling of the relaxation process this method [14] greatly reduces inaccuracies in the measured threshold drift. However, significant relaxation may occur for all curves within the first measurement time period (0-200 ms) [14] and the initial relaxation characteristics therefore cannot be resolved. For the same bias voltage, the trapped charge at the instant of the removal of the bias would be the same and hence, in this case, the plasma treated samples appear to relax more quickly compared to the untreated sample during this initial period, in line with the differences in hysteresis. The prolonged recovery times indicates that threshold voltage instabilities can cause difficulties over a wide range of switching conditions in practical systems.

Figure 2. The built up of hysteresis with increase in the positive gate bias voltage and estimated occupation of trapped charge.

Figure 3. (a) The positive shift in threshold voltage with positive gate bias stress time (b) experimental test sequence.

Figure 4. (a) The drain current recovery time after 1sec  $+7V_{GS}$  stress in reference and plasma treated samples (b) experimental test sequence.

#### **Reverse Bias Stress**

Power devices are often required to withstand large blocking voltages in the pinched-off state and any threshold voltage shift in such situations can be problematic. There are a few reports of negative gate bias stress in recessed barrier AlGaN/GaN MISHEMTs and MOS structure GaN FETs [26-28]. However, there has been no comparison between different surface preparation methods and no attempt at correlation with forward bias stress results. In this work, we have performed negative gate bias stress on conventional AlGaN/GaN MISHEMT devices both with and without plasma pre-treatment to evaluate the stability of threshold voltage in such scenarios and gain some further insight into the differences between pretreated and untreated samples.

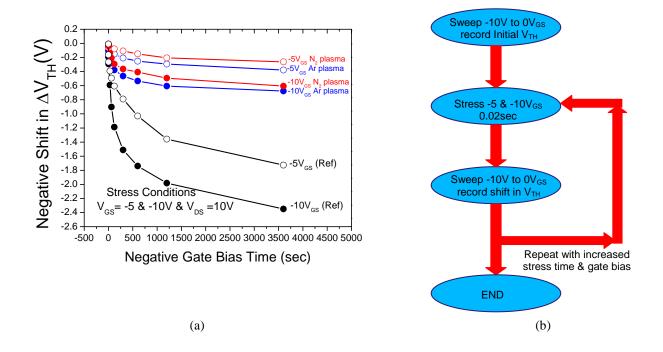

The negative shift in the threshold voltage of AlGaN/GaN MISHEMTs with negative gate bias stress time using -5V and -10V  $V_{GS}$  is shown in figure 5 (a) along with the experimental sequence (b). In this experiment, virgin devices are initially swept from -10V to 0V  $V_{GS}$  to record the initial threshold voltage and then negative gate bias stress is applied with -5V or -10V  $V_{GS}$  for 0.02 seconds after that, devices are swept from -10V to 0V  $V_{GS}$  to record the shift in the threshold voltage. The experiment is then repeated with increased negative gate bias stress time.

Figure 5 (a) shows the shift in the threshold voltage as a function of stress time, which is due to the transport of electrons from the dielectric/barrier interface towards the channel. The shift is considerably greater in the reference sample compared to the plasma-pretreated samples. Contrary to the results for positive gate bias stress, the charge adjustment under negative stress is much slower than the measurement time, giving a reduced error in sampling the threshold shift. The difference between the reference and  $N_2$  and Ar plasma treated samples after one hour stress time is ~1.7 V, which is similar to the observed quasi-equilibrium threshold voltage differences (figure 1). This is most likely due to the differences in stored charge close to the quasi-equilibrium Fermi level which gives rise to the differences in the quasi-equilibrium  $V_{TH}$  (further explanation later).

Figure 5. (a) The negative shift in threshold voltage with negative gate bias stress, and (b) experimental sequence with negative gate bias stress.

## **Model and Discussion**

To date, the origin of the 2DEG charge in AlGaN/GaN heterostructures is still a conundrum. Although it is widely accepted that the surface and interface states (in MIS structures) play a vital role, the exact nature of these interface states and their distribution within the forbidden gap is still under debate. The various models were summarized and discussed by Bakeroot et al [32]. Each model has its own limitations but may explain behavior within limited specific conditions.

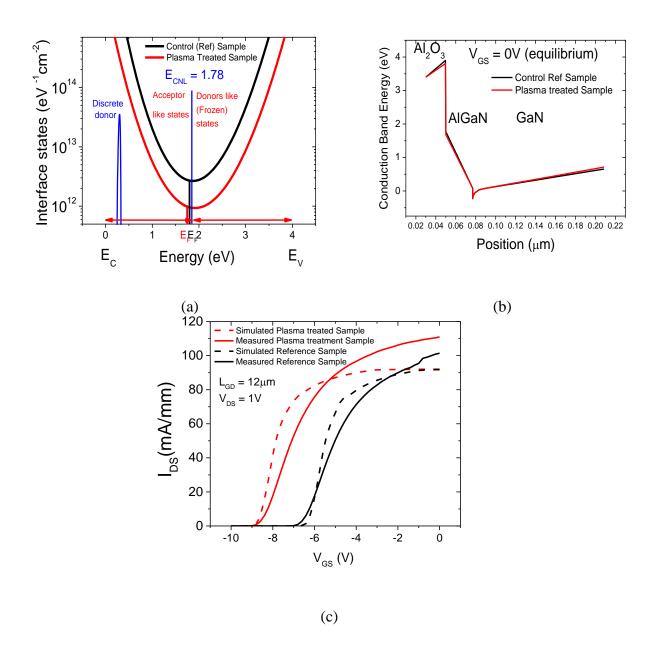

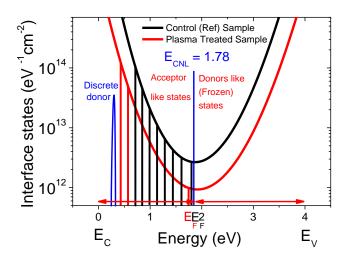

The unified disorder induced gap states (DIGS) model [33,34] has often been utilised to explain different  $V_{TH}$  hysteresis behavior. This model divides the U-shaped interface state density into donor- and acceptor-like states separated by the charge neutrality level ( $E_{CNL}$ ) [33] with the Fermi level ( $E_F$ ) close by (figure 6(a)). Although the DIGS model can explain the formation of the 2DEG, some additional discrete donor-like interface states, particularly those which have been associated with nitrogen vacancies [35], may still be needed to explain the 2DEG variation with barrier thickness and composition, and to place  $E_F$  above  $E_{CNL}$  [32, 35]. The latter is a requirement for our model. Therefore, to help establish the charge details at the interface as a result of the plasma pretreatments, we used SENTAURUS TCAD to simulate a DIGS model together with discrete donor states associated with nitrogen vacancies, 0.37eV below the

conduction band [35], to explain our three main experimental observations after plasma pretreatment. These are 1) the negative shift in the quasi-equilibrium  $V_{TH}$  (~2V), 2) the faster emission rates (reduced hysteresis) and 3) the reduced negative shift in the  $V_{TH}$  during negative gate bias stress.

Figure 6 (a) shows the distribution of interface states along with the energy levels used in the SENTAURUS simulation to represent the plasma pretreated and reference (higher interface state density) samples. Note that the number of discrete donors and the magnitude of the DIGS distribution was chosen to yield the experimental 2DEG concentrations. The discrete donors are necessary to place the Fermi level above  $E_{CNL}$  but should not be large enough in number to pin the Fermi level at that level. However, many concentration combinations of DIGS and discreet donor levels will give the correct value of the 2DEG. Here we are mostly interested in the relative values of the DIGS density to model the observed electrical differences between the samples. The conduction band diagram at  $V_{GS} = 0$  V (equilibrium state) for both samples is also shown in figure 6 (b). Note the small differences in the Fermi level position with respect to the conduction band. We excluded the 1nm AlN mobility enhancement layer in our model since it is unlikely to make any significant difference to our explanation. An  $E_{CNL}$  value of 1.78eV, as calculated by Mönch [36], was used. Due to the presence of the discrete donor states, the Fermi level position is slightly above the  $E_{CNL}$  level and donor-like states below the  $E_{CNL}$  level are considered frozen or fixed, i.e. they remained neutral (occupied) throughout, under all bias conditions considered [34]. The rationale for this assumption is that the time constants associated with states below mid band gap in AlGaN can be very large  $(10^{12} - 10^{20} \text{ sec})$  [34] and therefore are unlikely to change charge state in the gate transfer measurements. This is also borne out by the medium term stability of the pinch-off condition in normal HEMT operation.

The 2DEG charge per unit area,  $n_s$ , formed as a result of this model is given by

$$n_s = N_D^+ - N_A^-$$

(1)

where  $N_D^+$  the ionized donor density per unit area (here assigned to nitrogen vacancies) and  $N_A^-$  is the occupied acceptor-like state density below the Fermi level. To explain the observations we assume that the plasma pretreatment reduces the density of the U-shaped distribution of interface states, and hence the number of negatively charged acceptor states below the Fermi level,  $N_A^-$ , is reduced. Whilst the shift in  $n_s$  and hence the quasi-equilibrium  $V_{TH}$  after the plasma pretreatment can also be explained by simply

increasing the discrete donor states in equation 1, the explanation of the hysteresis and reverse bias observations require changes in the acceptor-like state densities [32, 34].

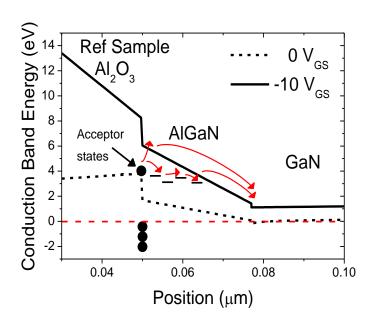

Figure 6 (c) shows the modelled results as described above compared with the experimental transfer characteristics for the reference and plasma pretreated samples. Reasonable agreement is obtained. In our model the  $\sim$ 2V shift in the quasi-equilibrium  $V_{TH}$  after plasma pretreatment is the manifestation of the reduced DIGS acceptor states density,  $N_A$ , in equation 1. The conduction band diagram of the reference sample under 0 V (equilibrium) and -10 V  $V_{GS}$  showing the charge transfer mechanism is shown in figure 7. In the equilibrium condition (0 V  $V_{GS}$ ), occupied acceptor states are below the Fermi level and, as the gate is swept to reverse bias (-10  $V_{GS}$ ), these acceptor states are lifted above the Fermi level. However, the emission time constants of electrons in these acceptor states are such that they are unable to emit during the gate transfer sweep and so behave as fixed negative states in the reference sample. The presence of these additional acceptor states over and above those in the plasma treated samples results in the  $\sim 2V V_{TH}$  difference. When the negative gate bias is applied for a long enough time such as in the reverse bias stress measurements of figure 5(a), then the electrons in these acceptor states are eventually able to reach the 2DEG channel as shown in figure 5(a) via hopping through the AlGaN barrier traps and/or emission into the barrier conduction band. After nearly one hour negative gate bias stress (-10 $V_{GS}$ ) the  $V_{TH}$  difference between the reference and plasma pretreated sample is ~2V as seen in the figure 5(a) which is equal to the difference in the equilibrium  $V_{TH}$ , reflecting the extra charge transfer in the nontreated samples. As stated previously, the donor-like states below  $E_{CNL}$  are considered too slow to take part in the reverse bias transients.

Figure 6. (a) The distribution of interface states used in the model of the reference and plasma treated samples. (b) Modelled conduction band diagram at equilibrium state in reference and plasma treated sample (c) Modelled and measured gate transfer sweep of reference and plasma treated sample.

Figure 7. Conduction band diagram of reference sample at 0 and  $-10V_{GS}$  showing the electron transfer mechanism.

When the gate is sufficiently forward biased, the acceptor-like states above the Fermi level are filled with electrons and are responsible for the  $V_{TH}$  hysteresis in bi-directional gate transfer sweeps (figure 1). Under the forward bias condition, to trap the same amount of charge (fixed forward bias voltage) more states closer to the conduction band would get filled in the plasma pretreated sample compared to the reference sample, as shown by the red and black shading in figure 8. This difference in the occupation distribution of interface acceptor-like states can lead to faster electron emission in the plasma pretreated sample and reduced hysteresis.

Figure 8. Filling of acceptor like states in reference (black lines) and plasma treated sample (red lines) to accommodate same amount of charge (7V) under the forward gate bias stress condition.

# **Surface Study**

To understand the possible chemical changes on the surface after both plasma pretreatments, we performed X-Ray photoelectron spectroscopy (XPS) with 2.5nm Al<sub>2</sub>O<sub>3</sub> dielectric layer thickness on both untreated and plasma pretreated GaN. Both plasma pretreatments reduced the O-C peaks equally which were previously reported to be detrimental to device performance [30]. In addition, the N<sub>2</sub> treated sample increases the Al-N bonding ratios which suggests a possible nitridation effect. There is also an increase in the Al-OH bond ratio after N<sub>2</sub> plasma pretreatment, which indicates an increase in surface reactivity. Since N<sub>2</sub> plasma treated devices showed only marginally improved hysteresis and threshold voltage stability over the Ar plasma, it can be concluded that cleaning the surface (reducing O-C bonds) is the likely dominant factor to improve the interface quality.

#### **Conclusions**

We have developed a model to explain the main electrical differences resulting from untreated and plasma pretreated surfaces in MOSHEMTs. Despite the uncertainty in the interface state density and distribution, we have been able to use the DIGS model combined with discrete donors to explain consistently the observed changes in quasi-equilibrium threshold voltage, hysteresis and reverse bias stress resulting from different pre-deposition surface preparations. Our measurements and analysis add further insight into the mechanisms affecting  $V_{TH}$  instabilities, but indicate that the elimination of these effects relate to the significant reduction in interface states, which are implicated in the inability to easily achieve E-mode devices.

## References

- [1] P. D. Ye, B. Yang, K. K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, "GaN metal-oxide-semiconductor high-electron-mobility-transistor with atomic layer deposited Al2O3 as gate dielectric," Applied Physics Letters, 86, 063501, January 2005.

- [2] N. Ikeda *et al.*, "GaN Power Transistors on Si Substrates for Switching Applications," in *Proceedings of the IEEE*, vol. 98, no. 7, pp. 1151-1161, July 2010.

- [3] W. Choi, O. Seok, H. Ryu, H.-Y. Cha, and K.-S. Seo, "High-voltage and low-leakage-current gate recessed normally-off GaN MIS-HEMTs with dual gate insulator employing PEALD-SiN<sub>x</sub> /RF-sputtered-HfO<sub>2</sub>," IEEE Electron Device Letters, vol. 35, no. 2, pp. 175–177, Febuary 2014.

- [4] Zhikai Tang, Qimeng Jiang, Yunyou Lu, Sen Huang, Shu Yang, Xi Tang, and Kevin J. Chen, "600-V Normally Off SiN<sub>x</sub> /AlGaN/GaN MIS-HEMT With Large Gate Swing and Low Current Collapse," in IEEE Electron Device Letters, vol. 34, no. 11, pp. 1373-1375, November 2013.

- [5] P. Kordoša, Slovakia G. Heidelberger, J. Bernát, A. Fox, M. Marso, and H. Lüth, "High-power SiO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor heterostructure field-effect transistors," Applied Physics Letters, 87, 143501, September 2005.

- [6] Jie-Jie Zhu, Xiao-Hua Ma, Yong Xie, Bin Hou, Wei-Wei Chen, Jin-Cheng Zhang, and Yue Hao, "Improved Interface and Transport Properties of AlGaN/GaN MIS-HEMTs With PEALD-Grown AlN Gate Dielectric," in IEEE Transactions on Electron Devices, vol. 62, no. 2, pp. 512-518, February 2015.

- [7] Chang Liu, Eng Fong Chor, and Leng Seow Tan, "Investigations of HfO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor high electron mobility transistors," Applied Physics Letters 88, 173504, April 2006.

- [8] Huan-Yu Shih, Fu-Chuan Chu, Atanu Das, Chia-Yu Lee, Ming-Jang Chen and Ray-Ming Lin, "Atomic Layer Deposition of Gallium Oxide Films as Gate Dielectrics in AlGaN/GaN Metal–Oxide–Semiconductor High-Electron-Mobility Transistors," Nanoscale Research Letters, 11:235, April 2016.

- [9] H.-C. Chiu, C.-W. Lin, C.-H. Chen, C.-W. Yang, C.-K. Lin, J. S. Fu, L.-B. Chang, R.-M. Lin, and K.-P. Hsueh, "Low Hysteresis Dispersion La<sub>2</sub>O<sub>3</sub>AlGaN/GaN MOS-HEMTs," Journal of the Electrochemical Society, 157, issue 2, H160-4, December 2009.

- [10] Bo-Yi Chou, Wei-Chou Hsu, Ching-Sung Lee, Han-Yin Liu and Chiu-Sheng Ho, "Comparative studies of AlGaN/GaN MOS-HEMTs with stacked gate dielectrics by the mixed thin film growth method," Semiconductor Science and Technology, 28, 074005, June 2013.

- [11] Hiroshi Kambayashi, Takehiko Nomura, Hirokazu Ueda, Katsushige Harada, Yuichiro Morozumi, Kazuhide Hasebe, Akinobu Teramoto, Shigetoshi Sugawa, and Tadahiro Ohmi, "High Quality SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> Gate Stack for GaN Metal—Oxide—Semiconductor Field-Effect Transistor," Japanese Journal of Applied Physics, 52, 04CF09, March 2013.

- [12] S. Huang, S. Yang, J. Roberts, et al., "Threshold voltage instability in Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN metal-insulator-semiconductor highelectron mobility transistors," Japanese Journal of Applied Physics, vol. 50, no. 11, pp. 110202-1–110202-3, November 2011.

- [13] C. Mizue, Y. Hori, M. Miczek, et al., "Capacitance-voltage characteristics of Al2O3/AlGaN/GaN structures and state density distribution at Al2O3/AlGaN interface," Jpn. J. Appl. Phys., vol. 50, no. 2, pp. 021001-1–021001-7, February 2011.

- [14] P. Lagger, C. Ostermaier, G. Pobegen and D. Pogany, "Towards understanding the origin of threshold voltage instability of AlGaN/GaN MIS-HEMTs," Electron Devices Meeting (IEDM), IEEE International, San Francisco, CA, pp. 13.1.1-13.1.4. 2012, December 2012.

- [15] Y. Lu, S. Yang, Q. Jiang, et al., "Characterization of VT-instability in enhancement-mode Al2O3-AlGaN/GaN MIS-HEMTs," in Proc. Int. Symp. Compound Semicond., pp. 2–4, May 2013.

- [16] P. Lagger, M. Reiner, D. Pogany and C. Ostermaier, "Comprehensive Study of the Complex Dynamics of Forward Bias-Induced Threshold Voltage Drifts in GaN Based MIS-HEMTs by Stress/Recovery Experiments," in IEEE Transactions on Electron Devices, vol. 61, no. 4, pp. 1022-1030, April 2014.

- [17] S. Yang, S. Liu, C. Liu, Z. Tang, Y. Lu and K. J. Chen, "Thermally induced threshold voltage instability of III-Nitride MIS-HEMTs and MOSC-HEMTs: Underlying mechanisms and optimization schemes," IEEE International Electron Devices Meeting, San Francisco, CA, pp. 17.2.1-17.2.4, December 2014.

- [18] K. Chen, S. Yang, Z. Tang, S. Huang, Y. Lu, Q. Jiang, S. Liu, C. Liu. and B. Li, "Surface nitridation for improved dielectric/III-nitride interfaces in GaN MIS-HEMTs," Phys. Status Solidi A 212, No. 5, pp. 1059–1065, December 2014.

- [19] Shu Yang, Zhikai Tang, King-Yuen Wong, Yu-Syuan Lin, Cheng Liu, Yunyou Lu, Sen Huang, and Kevin J. Chen, "High-Quality Interface in Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MIS Structures With In Situ Pre-Gate Plasma Nitridation," in IEEE Electron Device Letters, vol. 34, no. 12, pp. 1497-1499, December 2013.

- [20] T. H. Hung, P. S. Park, S. Krishnamoorthy, D. N. Nath and S. Rajan, "Interface Charge Engineering for Enhancement-Mode GaN MISHEMTs," in IEEE Electron Device Letters, vol. 35, no. 3, pp. 312-314, March 2014.

- [21] S.J. Cho, J.W. Roberts, I. Guiney, X. Li, G. Ternent, K. Floros, C.J. Humphreys, P.R. Chalker, I.G. Thayne, "A study of the impact of in-situ argon plasma treatment before atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> on GaN based metal oxide semiconductor capacitor," Microelectronic Engineering, vol. 147, pp 277-280, ISSN 0167-9317, November 2015.

- [22] P. Lagger, C. Ostermaier and D. Pogany, "Enhancement of Vth drift for repetitive gate stress pulses due to charge feedback effect in GaN MIS-HEMTs," 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, pp. 6C.3.1-6C.3.6, June 2014.

- [23] P. Lagger, A. Schiffmann, G. Pobegen, D. Pogany and C. Ostermaier, "Very Fast Dynamics of Threshold Voltage Drifts in GaN-Based MIS-HEMTs," in IEEE Electron Device Letters, vol. 34, no. 9, pp. 1112-1114, September 2013.

- [24] A. Guo and J. A. del Alamo, "Positive-bias temperature instability (PBTI) of GaN MOSFETs," IEEE International Reliability Physics Symposium, Monterey, CA, pp. 6C.5.1-6C.5.7, June 2015.

- [25] Derek W. Johnson, Rinus T. P. Lee, Richard J. W. Hill, Man Hoi Wong, Gennadi Bersuker, Edwin L. Piner, Paul D. Kirsch, and H. Rusty Harris, "Threshold Voltage Shift Due to Charge Trapping in Dielectric-Gated AlGaN/GaN High Electron Mobility Transistors Examined in Au-Free Technology," in IEEE Transactions on Electron Devices, vol. 60, no. 10, pp. 3197-3203, October 2013.

- [26] M. Tapajna and J. Kuzmı'k, "A comprehensive analytical model for threshold voltage calculation in GaN based metal-oxide-semiconductor high-electron-mobility transistors," Applied Physics Letters, 100, 113509, March 2012.

- [27] Matteo Meneghini, Isabella Rossetto, Davide Bisi, Maria Ruzzarin, Marleen Van Hove, Steve Stoffels, Tian-Li Wu, Denis Marcon, Stefaan Decoutere, Gaudenzio Meneghesso, and Enrico Zanoni, "Negative Bias-Induced Threshold Voltage Instability in GaN-on-Si Power HEMTs," IEEE Electron Device Letters, vol. 37, no.4, April 2016.

- [28] Fei Sang, Maojun Wang, Chuan Zhang, Ming Tao, Bing Xie, Cheng P. Wen, Jinyan Wang, Yilong Hao, Wengang Wu, and Bo Shen, "Investigation of the threshold voltage drift in enhancement mode GaN MOSFET under negative gate bias stress," Japanese Journal of Applied Physics, vol. 54, no. 4, March 2015.

- [29] A. Guo and J. A. del Alamo, "Negative-bias temperature instability of GaN MOSFETs," IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, pp. 4A-1-1-4A-1-6, April 2016.

- [30] Shih-Chien Liu, Bo-Yuan Chen, Yueh-Chin Lin, Ting-En Hsieh, Huan-Chung Wang, and Edward Yi Chang, "GaN MIS-HEMTs With Nitrogen Passivation for Power Device Applications," IEEE Electron Device Letters, vol. 35, no. 10, October 2014.

- [31] Zhili Zhang, Weiyi Li, et al., "AlGaN/GaN MIS-HEMTs of Very-Low Vth Hysteresis and Current Collapse with In-Situ Pre-Deposition Plasma Nitridation and LPCVD-Si3N4 Gate Insulator," IEEE Electron Device Letters, vol. 38, no. 2, February 2017.

- [32] B. Bakeroot, S. You, T. L. Wu, J. Hu, M. Van Hove, B. De Jaeger, K. Geens, S. Stoffels, and S. Decoutere, "On the origin of the two-dimensional electron gas at AlGaN/GaN heterojunctions and its influence on recessed-gate metal-insulator-semiconductor high electron mobility transistors," Journal of Applied Physics 116, 134506, October 2014.

- [33] H. Hasegawa and H. Ohno, "Unified disorder induced gap state model for insulator-semiconductor and metal-semiconductor interfaces," Journal of vacuum science and technology B, 4, 1130, April 1986.

- [34] C. Mizue, Y. Hori, M. Miczek, and T. Hashizume, "Capacitance–Voltage Characteristics of Al2O3/AlGaN/GaN Structures and State Density Distribution at Al2O3/AlGaN Interface," Japanese Journal of Applied Physics, 50, 021001, February 2011.

- [35] H. Hasegawa, T. Inagaki, S. Ootomo, and T. Hashizume, "Mechanisms of current collapse and gate leakage currents in AlGaN/GaN heterostructure field effect transistors," Journal of vacuum science and technology, B 21, 1844, August 2003.

- [36] W. Mönch, "Elementary calculation of the branch-point energy in the continuum of interface-induced gap states," Applied surface science, vol 117-118, pp 380-387, June 1997.