## ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/112085/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Han, Yu, Li, Qiang and Lau, Kei May 2017. Fin-array tunneling trigger with tunable hysteresis on (001) silicon substrate. IEEE Electron Device Letters 38 (5), pp. 556-559. 10.1109/LED.2017.2689027

Publishers page: http://dx.doi.org/10.1109/LED.2017.2689027

## Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# Fin-array tunneling trigger with tunable hysteresis on (001) silicon substrate

Yu Han, Qiang Li, member, IEEE, and Kei May Lau, Fellow, IEEE

Abstract— We report the fabrication and characterization of a GaAs fin-array tunneling trigger monolithically integrated on an exact (001) silicon substrate. A Schmitt-trigger-like behavior was observed under double sweep condition by connecting the tunnel diode with an on-chip load resistor. The tunneling trigger circuit was studied using load line analysis. Critical parameters of the circuit were extracted. We found that the circuit hysteresis can be tuned by tailoring of the diode dimensions and load resistor values.

Index Terms— Tunnel diodes, GaAs fin-array, Schmitt trigger, monolithic integration, digital circuits.

### I. INTRODUCTION

iming at enhancing circuit performance and functionalities, Amerging III-V electronic and photonic technologies with silicon complementary metal-oxide-semiconductor (CMOS) process is receiving a tremendous amount of attention [1]-[4]. Integrating III-V tunnel diodes on Si can form the building blocks for a new class of ultra-high speed circuits with reduced power consumption and circuit complexity [5]-[11], if challenges associated with the thermal and lattice mismatches and the polar/non-polar growth can be properly addressed [12]-[16]. In addition, direct integration on (001) silicon substrates is fully compatible with the well-established processing technologies of advanced CMOS foundries. Taking advantage of the defect necking effect in the aspect ratio trapping (ART) process, we have recently demonstrated GaAs/InGsAs fin-array tunnel diodes and inverters on exact (001) silicon substrates using a GaAs buffer with a thickness of only 160 nm [17], [18].

When a tunnel diode is connected with a load resistor or transistor, hysteresis of current-voltage (IV) characteristics can be observed if the value of the load resistance is larger than that of the negative differential resistance (NDR). This hysteresis has been utilized to build various digital circuits, including universal and reconfigurable logic gates [19], trigger circuits [20], and multi-valued memory cells [21]. In this work, we fabricated a tunneling trigger with two fin-array tunnel diodes connected back to back. By sweeping forward and backward at the input end, a Schmitt-trigger-like behavior is observed at the output end. We also show that the tunneling trigger circuit is

Manuscript received 2017; revised xxx. This work was supported by grants (Nos. 16245216 and ITS/320/14) from the Research Grants Council of Hong Kong. The review of this letter was arranged by Editor xx.

Y. Han, Q. Li, and K.M. Lau are with the Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Kowloon, Hong Kong. (E-mail: eekmlau@ust.hk).

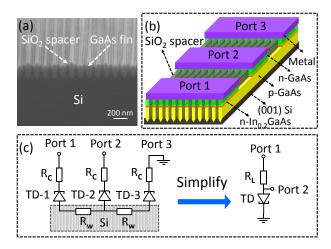

Fig. 1. (a) 70° tilted SEM image of the as-grown GaAs fin-array on (001) Si substrate. (b) Schematic of the GaAs fin-array tunneling trigger monolithically integrated on (001) Si substrates. (c) Equivalent circuit of the tunneling trigger. Simplified circuits is shown on the right.

highly predictable and controllable by varying the device size and series resistance.

### II. DEVICE STRUCTURE AND FABRICATION

Fig. 1(a) presents a 70° tilted-view SEM image of the highly ordered GaAs fin-array grown on (001) silicon. Detailed material growth and characterization of this structure has been reported [17]. Prior to device fabrication, the sample was thermally annealed at 550 °C for 30 sec to activate the hydrogen-passivated carbon in the p-GaAs. Metal stack (Ni/Ge/Au) was firstly patterned on the n-GaAs fins. Then, wet etching  $(H_3PO_4:H_2O_2:H_2O=3:1:50)$  was performed to remove the top n-GaAs/InGaAs and partially etch the p-GaAs. Fig. 1(b) displays the schematic of the fabricated fin-array tunneling trigger. Three identical tunnel diodes are electrically connected by partially etched p-GaAs fins. Each fin consists of three epi-layers: 80 nm n-GaAs, 5 nm n-In<sub>0.2</sub>GaAs and 150 nm p-GaAs. Fig. 1(c) shows the equivalent circuit of the fabricated tunneling trigger, where R<sub>C</sub> corresponds to the contact resistance between the metal stack and the n-GaAs fins, while R<sub>W</sub> refers to the resistance of the partially etched p-GaAs fins. The input voltage was applied on Port 1 and the output voltage was measured from Port 2, with Port 3 grounded. During the measurement, TD-1 was reverse biased and served as a resistor. Therefore, the simplified circuit, consisting of series-connected tunnel diode and resistor, is displayed on right side of Fig. 1(c).

### III. RESULTS AND DISCUSSION

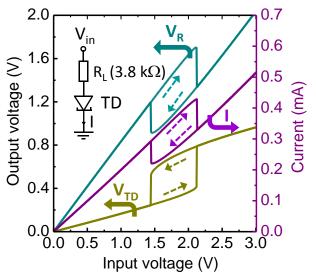

We measured the voltage and current characteristics of the fabricated fin-array tunneling trigger under a double sweep condition (0 to 3 V and then 3 V to 0). For clear comparison, the curves of tunnel diode voltage ( $V_{TD}$ ), load resistor voltage ( $V_R$ ) and total current (I) are plotted together in Fig. 2. The voltage drop across the tunnel diode exhibits a Schmitt-trigger-like behavior, with abrupt increase and decrease at different input voltages. When the input voltage was increased to 2.12 V (sweep forward), the output voltage increased suddenly from 0.41 V to 0.80 V. Similarly, the output voltage slumped from 0.54 V to 0.25 V, when the input voltage was decreased to 1.45 V (sweep backward). Bistable characteristic can be observed in all the measured parameters when the input voltage falls between 1.45 V and 2.12 V.

Fig. 2. Measured current and voltage across both series resistor and tunnel diode when sweep forward and backward. Hysteresis was observed in all parameters and Schmitt-trigger-like behavior was obtained from the voltage across the tunnel diode.

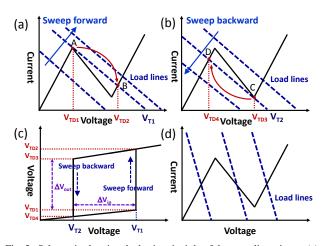

Fig. 3. Schematic showing the basic principle of the tunneling trigger. (a) Tunnel diode IV curve with load line when sweeping forward. Switch point resides around the peak point. (b) Tunnel diode IV curve with load line when sweeping backward. Switch point resides around the valley point. (c) Schematic showing the Schmitt-trigger characteristic (d) No switch point can be found when series resistance is smaller than the negative differential resistance.

Fig. 3 briefly summarizes the basic principle of the tunneling trigger. To simplify the analysis, we used an ideal tunnel diode IV curve with constant resistance at different regions before the valley voltage. While after the valley point, we treated the tunnel diode as a simple forward-biased PN junction. The current-voltage relationship of an ideal PN junction can be written as  $J = J_0 \exp(\frac{qV}{kT} - 1)$ , where  $J_0$  is the saturation current density. The trigger behavior can only be observed when the series resistance exceeds the NDR of the tunnel diode. As shown by the load line analysis in Fig. 3(a), the intersections of the load line of the resistor and the IV curve of the tunnel diode indicate stable working points of the circuit. The intersection of the load line and the abscissa axis refers to the input voltage value, and the abscissa of the working point corresponds to the voltage drop across the tunnel diode (output voltage). When sweeping forward, the output voltage increases linearly until the input voltage reaches the value of  $V_{T1}$ , where two stable working points A and B co-exist. Further increase of the input voltage leads to the transition to a single working point and an abrupt increases of output voltage from V<sub>TD1</sub> to V<sub>TD2</sub>. However, when sweeping backward, we observe the turning point when the input voltage decreases to the value of  $V_{T2}$ , as indicated by the red arrow in Fig. 3(b). Fig. 3(c) presents the voltage drop across the tunnel diode under the double sweep condition with clearly Schmitt-trigger-like behavior. When the series resistance is smaller than the NDR, only one stable working point exists and no trigger behavior can be obtained, as evidenced by the load lines analysis in Fig. 3(d).

TABLE I

CALCULATED PARAMETER VALUES OF TUNNELING TRIGGER

| Parameters         | Theoretical values                                                                                                             | Experimental values                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| $V_{T1}$           | $V_{Pi} + J_P A(R_L + R_P)$                                                                                                    | 2.12 V                             |

| $V_{T2}$           | $\boldsymbol{V}_{Vi} + \boldsymbol{J}_{V}\!\boldsymbol{A}(\boldsymbol{R}_{L}\!+\boldsymbol{R}_{P})$                            | 1.44 V                             |

| $V_{TD1}$          | $V_{pi} + J_p AR_p$                                                                                                            | 0.41 V                             |

| $V_{TD2}$          | $V_{V_i} + J_V AR_P < V_{TD2} < \frac{kT}{a} \ln(\frac{J_P}{I_o} +$                                                            | 1) 0.79 V                          |

| $V_{TD3}$          | $V_{Vi} + J_{V}AR_{P}$                                                                                                         | 0.52 V                             |

| $V_{TD4}$          | $0 < \ V_{TD4} < V_{pi} + J_{P}\!AR_{P}$                                                                                       | 0.24 V                             |

| $\Delta V^{}_{in}$ | $(V_{Pi} - V_{Vi}) + A(J_P - J_V)(R_L + R_I)$                                                                                  | e) 0.68 V                          |

| $\Delta V_{out}$   | $(V_{Vi}\!-\!V_{Pi})-A(J_{P}\!-\!J_{V})R_{P}$                                                                                  | 0.11 V                             |

| NDR                | $(\boldsymbol{V}_{Pi}\!-\!\boldsymbol{V}_{Vi})/\!\boldsymbol{A}(\boldsymbol{J}_{P}\!-\!\boldsymbol{J}_{V})-\boldsymbol{R}_{P}$ | $1.25 \text{ k}\Omega$ (intrinsic) |

Based on the ideal case in Fig. 3, we calculated the values of different parameters of the tunneling trigger circuit and summarized the results (both theoretical and experimental) in Table I. Both  $V_{T1}$  and  $V_{T2}$  are influenced by the intrinsic peak and valley voltage ( $V_{Pi}$  and  $V_{Vi}$ ) of the tunnel junction, the peak and valley current density ( $J_P$  and  $J_V$ ), and device size "A".  $V_{Pi}$  and  $V_{Vi}$  are determined solely by the properties of the tunnel junction.  $R_P$  is the parasitic resistance of the tunnel diode and  $R_L$  is the load resistance of the circuit. The definition of other critical parameters is illustrated in Fig. 3(c). As summarized in Table II, when R approaches infinity (load line parallel to abscissa axis),  $\Delta V_{in}$  would also be infinity and the ratio  $\Delta V_{out}/\Delta V_{in}$  (describing the curve shape) would be zero. When

$R_L$  is equal to NDR,  $\Delta V_{in}$  is zero and the curve ratio  $\Delta V_{out}/\Delta V_{in}$  would approach infinity.

TABLE II

BOUNDARY CONDITIONS OF THE TUNNELING TRIGGER

|                          | $\Delta V_{in}$ | $\Delta V_{out}/\Delta V_{in}$ |

|--------------------------|-----------------|--------------------------------|

| $R_L \rightarrow \infty$ | $\infty$        | 0                              |

| $R_L \rightarrow NDR$    | 0               | $\infty$                       |

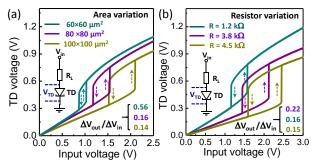

We demonstrated the hysteresis is tunable by varying the device dimensions. As shown in Fig. 4(a), we observe a monotonic decrease of the curve ratio  $\Delta V_{out}/\Delta V_{in}$  as device size increases. As illustrated previously in Table I, both  $\Delta V_{out}$  and  $\Delta V_{\text{in}}$  are directly related to device size "A", area of the metal contacts. Changes in the device size would result in a direct scaling of the peak current. Although the contact resistance R<sub>P</sub> and R<sub>L</sub> would also scale with the device area, the effect is much smaller. Therefore, the observed change of  $\Delta V_{out}$  and  $\Delta V_{in}$  with device dimension scales agrees with the theoretical analysis shown in Fig. 3. The hysteresis can also be tuned by varying the values of the load resistor, as verified by the measurement in Fig. 4(b). An increase of the load resistor value results in the decrease of the curve ratio  $\Delta V_{out}/\Delta V_{in}$ . It should be noted that both  $V_{TD1}$ and  $V_{TD3}$  become smaller as  $R_L$  increases and  $V_{TD1}$  exhibits a much larger dependence on  $R_L$  than  $V_{TD3}$ . The shift of  $V_{TD1}$  with R<sub>L</sub> might be due to the rounded peak point and the kinks in the NDR region, as has been reported in Ref. [12] and [22]. The mechanism of the weak dependence of V<sub>TD3</sub> on R<sub>L</sub> is still under investigation.

Fig. 4. (a) Tunneling trigger behavior measured from devices with different sizes. (b) Tunneling trigger behavior measured from devices with different load resistance.

### IV. CONCLUSION

In conclusion, we have demonstrated tunneling trigger characteristics in fin-arrays with tunable hysteresis on exact (001) silicon substrates. The tunable hysteresis was theoretically proven by load line analysis and experimentally validated by varying device dimension and load resistance. These results show promises for III-V tunnel diode based digital circuits on exact (001) silicon substrates.

### ACKNOWLEDGMENT

The authors would like to thank SEMATECH for providing the initial patterned Si substrates and the NFF and MCPF of HKUST for technical support.

### REFERENCES

- [1] N. Waldron, C. Merckling, L. Teugels, P. Ong, S.A.U. Ibrahim, F. Sebaai, A. Pourghaderi, K. Barla, N. Collaert, A. Thean, "InGaAs gate-all-around nanowire devices on 300 mm Si substrates," *IEEE Electron Device Lett.*, vol. 35, no. 11, pp. 1097–1099, Nov. 2014. DOI: 10.1109/LED.2014.2359579

- [2] Z.C. Wang, B. Tian, M. Pantouvaki, W.M Guo, P. Absil, J.V. Campenhout, C. Merckling, and D. V. Thourhout,, "Room-temperature InP distributed feedback laser array directly grown on silicon," Nature Photon., vol. 9, no. 12, pp. 837–842, 2015. DOI: 10.1038/nphoton.2015.199

- [3] S. A. Ringel, J. A. Carlin, C. L. Andre, D. M. Wilt, E. B. Clark, P. Jenkins, D. Scheiman, C. W. Leitz, A. A. Allerman, and E. A. Fitzgerald, "Single-junction InGaP/GaAs solar cells grown on Si substrates with SiGe buffer layers," Prog. Phot., vol. 10, pp. 417–426, Sep. 2002. DOI: 10.1002/pip.448

- [4] F. E. Ejeckam, C. L. Chua, Z. H. Zhu, Y. H. Lo, M. Hong, R. Bhat, "High performance InGaAs photodetectors on Si and GaAs substrate," Appl. Phys. Lett., vol. 67, no. 26, pp. 3936–3939, 1995. DOI: <u>10.1063/1.114410</u>

- [5] P. Mazumder, S. Kulkarni, M. Bhattacharya, J. P. Sun, and G. I. Haddad, "Digital circuit applications of resonant tunneling devices," Proc. IEEE, vol. 86, pp. 664–686, Apr. 1998. DOI: 10.1109/5.663544

- [6] J. P. A. van der Wagt, "Tunneling based SRAM," Proc. IEEE, vol. 87, pp. 571–595, 1999. DOI: 10.1109/5.752516

- [7] A. Seabaugh, X. Deng, T. Blake, B. Brar, T. Broekaert, R. Lake, F. Morris, and G. Frazier, "Transistors and tunnel diodes for analog/mixedsignal circuits and embedded memory," in Int. Elect. Dev. Meeting Tech. Dig., 1998, pp. 429–432. DOI: 10.1109/IEDM.1998.746390

- [8] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," IEEE Trans. Electron Devices, vol. 36, pp. 2065-2082, Oct. 1989. DOI: 10.1109/16.40888

- [9] H.-L. E. Chan, S. Mohan, W. L. Chen, P. Mazumder, and G. I. Haddad, "Ultrafast, compact multiple-valued multiplexers using quantum electronic devices," in Proc. Government Microcircuit Applications Conf., San Diego, CA, 1994, pp. 115–118. DOI: <u>10.1109/4.508262</u>

- [10] N. Jin, S-Y. Chung, R.M. Heyns, P.R. Berger, R. Yu, P. E. Thompson, S. L. Rommel, "Tri-state logic using vertically integrated Si-SiGe resonant interband tunneling diodes with double NDR," *IEEE Electron Device Lett.*, vol. 25, no. 9, pp. 646-648, Sep. 2004. DOI: 10.1109/LED.2004.833845

- [11] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," IEEE Trans. Electron Devices, vol. 36, pp. 2065–2082, Oct. 1989. DOI: 10.1109/16.40888

- [12] S.L. Rommel, D. Pawlik; P. Thomas, M. Barth, K. Johnson, S.K. Kurinec, A. Seabaugh, Z. Cheng, J.Z. Li, J.-S. Park, J.M. Hydrick, J. Bai, M. Carroll, J.G. Fiorenza, A. Lochtefeld, "Record PVCR GaAs-based tunnel diodes fabricated on Si substrates using aspect ratio trapping," in *IEDM Tech. Dig.*, Dec. 2008, pp. 30.6.1—30.6.4. DOI: 10.1109/IEDM.2008.4796801

- [13] W. Prost V. Khorenko, A.-C. Mofor, S. Neumann, A. Poloczek, A. Matiss, A. Bakin, A. Schlachetzki, F.-J. Tegude, "High performance III/V RTD and PIN diode on a silicon (001) substrate," *Appl. Phys. A (Mater. Sci. Process.*), vol. 87, no. 3, pp. 539–544, Jun. 2007. DOI: 10.1007/s00339-007-3920-1

- [14] C. D. Bessire, M.T. Björk, H. Schmid, A. Schenk, K. B. Reuter, and H. Riel, "Trap-assisted tunneling in Si–InAs NW heterojunction tunnel diodes," *Nano Lett.*, vol. 11, no. 10, pp. 4195–4199, Oct. 2011. DOI: 10.1021/nl202103a

- [15] T. Yang, S. Hertenberger, S. Morkötter, G. Abstreiter and G. Koblmüller, "Size, composition, and doping effects on In (Ga) As nanowire/Si tunnel diodes probed by conductive atomic force microscopy," Appl. Phys. Lett., vol. 101, no. 23, pp. 233102-1-233102-5, Dec, 2012. DOI: 10.1063/1.4768001

- [16] P. Thomas, M. Filmer, A. Gaur, D.J. Pawlik, B. Romanczyk, E. Marini, S.L. Rommel, K. Majumdar, W.-Y. Loh, M.H. Wong, C. Hobbs, K. Bhatnagar, R. Contreras-Guerrero, R. Droopad, R, "Performance Evaluation of In<sub>0.53</sub>Ga<sub>0.47</sub>As Esaki Tunnel Diodes on Silicon and InP Substrates," *IEEE Trans. Electron Devices*, Vol. 62, no. 8, pp. 2450-2456, Aug, 2015. DOI: 10.1109/TED.2015.2445731

- [17] Q. Li, Y. Han, X. Lu, Lau, K.M. Lau, "GaAs-InGaAs-GaAs Fin-Array Tunnel Diodes on (001) Si Substrates with Room-Temperature Peak-to-Valley Current Ratio of 5.4," *IEEE Electron Device Lett.*, vol.37, no.1, pp.24-27, Jan. 2016. DOI: <u>10.1109/LED.2015.2499603</u>

- [18] Y. Han, Q. Li, and K.M. Lau. "Monolithic Integration of Tunnel Diode-Based Inverters on Exact (001) Si Substrates." *IEEE Electron Device Lett.*, vol.37, no.6, pp.717-720, June. 2016. DOI: 10.1109/LED.2016.2552219

- [19] L. Worschech, F. Hartmann, T. Y. Kim, S. Hofling, M. Kamp, A. Forchel, J. Ahopelto, I. Neri, A. Dari, and L. Gammaitoni, "Universal and reconfigurable logic gates in a compact three-terminal resonant tunneling diode," Appl. Phys. Lett., vol. 96, no. 4, pp. 042 112-1–042 112-3, Jan. 2010. DOI: 10.1063/1.3302457

- [20] K.H Yang, T.H Kim, Y. Jeong, inventors; "SET/RESET latch circuit, Schmitt trigger circuit, and MOBILE based D-type flip flop circuit and frequency divider circuit thereof. *United States patent* US 7,573,310. Aug, 2009.

- [21] M.H. Shieh and H.C. Lin. "Modeling hysteretic current-voltage characteristics for resonant tunneling diodes." *IEEE Trans. on* computer-aided design of integrated circuits and systems., vol. 14, no. 9 pp. 1098-1103. Sept. 1995. DOI: <u>10.1109/43.406702</u>

- [22] D. Pawlik, B. Romanczyk, P. Thomas, S. Rommel, M. Edirisooriya, R. Contreras-Guerrero, R. Droopad, W-Y Loh, M. H. Wong, K. Majumdar, W.-E Wang, P. D. Kirsch, and R. Jammy, "Benchmarking and improving III-V Esaki diode performance with a record 2.2 MA/cm² peak current density to enhance TFET drive current," in *IEDM Tech. Dig.*, Dec. 2012, pp. 27.1.1 27.1.3. DOI: 10.1109/IEDM.2012.6479118