# ORCA - Online Research @ Cardiff

This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:https://orca.cardiff.ac.uk/id/eprint/146573/

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Wang, Yaoqiang, Wang, Changlong, Wang, Yi, Wang, Kewen and Liang, Jun 2022. A single-input extended multilevel inverter based on switched-capacitor with reduced number of devices. International Journal of Electrical Power & Energy Systems 138, 107872. 10.1016/j.ijepes.2021.107872

Publishers page: http://dx.doi.org/10.1016/j.ijepes.2021.107872

Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See http://orca.cf.ac.uk/policies.html for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

## A Single-Input Extended Multilevel Inverter Based on Switched-Capacitor with Reduced Number of Devices

Yaoqiang Wang, Senior Member, IEEE, Changlong Wang, Yi Wang, Kewen Wang, Member, IEEE, Jun Liang, Senior Member, IEEE

Abstract—The existing multilevel inverter (MLI) has problems such as a large number of devices, a complex structure, and a large voltage stress of the semiconductor. These shortcomings are not conducive to the modularization, high efficiency and miniaturization of the inverter. Therefore, a topology of extended switched capacitor multilevel inverter utilizing single power supply is proposed. In which, the capacitor is used as a virtual power supply, through the switching control strategy, capacitors and the power supply are reasonably combined, then a multilevel output voltage can be acquired. The proposed topology mainly has the following advantages. Firstly, it can be expanded to further increase the number of output levels. Secondly, the structure of the basic switched capacitor circuit used in the topology is simple, which can reduce the number of devices when the output is the same. Thirdly, the terminal H-bridge for output voltage polarity conversion can be eliminated in the proposed topology, which is beneficial to reduce the total standing voltage and peak inverse voltage. Therefore, an opportunity for the application of the inverter in medium and high voltage is provided. Additionally, the inherent capacitor voltage self-balancing capability of the proposed topology can eliminate the additional balancing control algorithms, therefore, the modulation strategy is simplified. Finally, the correctness and effectiveness of the topology are verified by the extensive simulation and experimental results carried out on the 13-level inverter.

*Index Terms*—Multilevel, single-input, bipolar inverter, switched-capacitor, self-balancing.

#### I. INTRODUCTION

In recent years, with the large-scale deployment of distributed generation, as an energy conversion interface between distributed energy and power grid or AC load, the DC-AC link of distributed generation has attracted extensive attention [1]-[2]. Due to the low total standing voltage (TSV), low total harmonic <sup>1</sup> distortion (THD) and effective reduction of electromagnetic interference, multilevel inverters have become one of the preferred circuit configurations for high efficiency in the DC-AC link [3]. There are many traditional multilevel inverters such as neutral point clamped (NPC) multilevel inverter [4], flying capacitor (FC) multilevel inverter [5], and cascaded H-bridge (CHB) multilevel inverter [6]. However, with the number of output voltage levels increasing, the number of power devices they required soars, which will inevitably complicate the structure of the inverter and increase manufacturing costs. The NPC multilevel inverter can reduce the voltage stress of capacitor, but the diode clamped by the topology is subjected to different reverse voltage stress, and the inner switches are turned on for longer than the outer switches. Therefore, the capacitor has the problem of voltage imbalance [7]-[8]. FC multilevel inverter uses capacitors instead of clamped diodes, which solves the problem of slow recovery of diode reverse voltage. However, a large number of capacitors are used. In order to ensure the stable operation of the inverter, the balance of capacitor voltage is the most important issue for this type of topology [9]-[10]. The cascaded H-bridge multilevel inverter uses isolated power instead of capacitors and reduces the use of diodes and capacitors. However, the number of output levels is directly related to the number of isolated power supplies. The extensive use of isolated power supplies complicates circuit protection. Therefore, the application in actual engineering has been limited [11]-[12].

In addition, in the grid-connected system of distributed generation or new energy electric vehicles, the above-mentioned multilevel inverters usually need to increase the voltage transformation link when the input voltage does not satisfy the output conditions. The bulky core and multiple coils of the transformer inevitably complicate the system and increase the area occupied [13]. For which, the research on the more efficient topologies has aroused a wide interest of experts and scholars. In the DC-DC conversion link, the switched capacitor (SC) structure has been widely adopted. In SC convertor, the capacitor is charged in parallel with the power supply, and the high voltage gain is obtained by superposing the capacitor and the power supply in series, avoiding the use of bulky inductance components [14]-[15].

Motivated by which, SC structure was introduced into a multilevel inverter system. Several switched capacitor multilevel inverters (SCMLIs) were proposed in [16]-[22]. The 5-level inverter was proposed in [16], but the boost gain of the inverter is 1. Two 9-level inverters were proposed in [17] and [18], the bipolar level of the topology is generated by the H bridge. A 9level inverter with inductive load ability was proposed in [19]. In [20] and [21], two 13-level inverters with similar structures

This work was supported in part by the National Natural Science Foundation of China under Grant 51507155, and in part by the Youth Key Teacher Project of Henan Higher Educational Institutions under Grant 2019GGJS011. (*Corresponding author: Yi Wang*).

Yaoqiang Wang, Changlong Wang, Yi Wang, and Kewen Wang are with th e School of Electrical Engineering, Zhengzhou University, Zhengzhou 45000

<sup>1,</sup> China, and also with the Henan Engineering Research Center of Power Elec tronics and Energy Systems, Zhengzhou 450001, China (e-mails:WangyqEE@ 163.com; Wangcclong@163.com; wangyi1414599008@163.com; kwwang@ zzu.edu.cn).

Jun Liang is with Zhengzhou University, Zhengzhou 450001, China, and Cardiff University, Cardiff CF24 3AA, U.K. (e-mail: LiangJ1@cardiff.ac.uk).

were proposed. The topology does not use the H-bridge circuit to output bipolar levels, which reduces the voltage stress of the semiconductor device. A 13-level inverter was proposed in [22], which uses a small number of components. However, it should be pointed out that these topologies are fixed, which are not only inconvenient for the expansion of inverter bridge, but also the number of output levels is limited seriously.

In general, with the increase of inverter output level, the quality of output voltage waveform can be improved effectively and the rate of voltage harmonic distortion can be decreased obviously. Therefore, the extensible switched capacitor inverter has become a hot topic.

In [23], a high-efficiency multilevel inverter topology was proposed, where the number of output levels is linear with the number of voltage sources. Thus, the scope of its application is limited seriously. In [24], the proposed topology owns a simple structure and low switching frequency. However, its output voltage is a superposition of the isolated power supply used, resulting that the proposed topology without boosting capability. Two operating modes were introduced in the topologies that designed in [25]-[26]. In the asymmetric mode, two power supplies with a specific voltage ratio were used to make the inverter output more levels, which can reduce the use of semiconductor devices. But due to the special requirements of the voltage source, the flexibility of the inverter application scenarios will be reduced seriously. In [27], a single-input multilevel inverter was proposed. However, many power devices being employed. The disadvantage of the topology developed in [28]-[30] is that with the increase of expansion modules, semiconductor devices need to withstand higher peak inverse voltage (PIV), especially in high-voltage applications, which will severely reduce the choice of devices.

The high voltage stress of semiconductor devices is mainly caused by the use of H-bridge circuit to output bipolar level. Therefore, newly developed topologies tend to reduce the use of H-bridge circuits. An extended switched capacitor topology was proposed in [31]. Although the H-bridge circuit has not been adopted, there are still two switches that need to withstand large voltage stress. The topology proposed in [32]-[33] effectively reduces the voltage stress of semiconductor devices. However, the topology in [32] has a small boost gain and uses many components, and the topology in [33] has a large TSV. In [34] and [35], the proposed topology has a constant PIV. However, the small rated charging voltage of the capacitor leads to low capacitance energy efficiency.

To address the aforementioned drawbacks, in this paper, a novel multilevel topology by utilizing the switched capacitor is proposed. It has the following salient features:

- Relying on the ability of the extended module output bipolar levels, the proposed topology can eliminate the terminal H-bridge and make the inverter has a low TSV and PIV.

- The proposed topology can reduce the number of devices effectively. The structure of the proposed topology is simplified, the voltage of the capacitor has the ability of self-balancing.

• The single-input topology can be extended easily, and the capacitor has high energy efficiency. Furthermore, the proposed inverter can achieve better output efficiency.

The remainder of this paper is organized as follows. In Section II, the general structure of the proposed topology is presented, its operating principle and modulation strategy are also introduced in detail. In Section III, the principle to determine the capacitance value and the losses analysis of the 13-level inverter are given. In Section IV, the comparisons between the proposed topology and other topologies are discussed. In Section V, extensive simulation and experimental results are provided to demonstrate the efficacy of the proposed 13-level inverter, and finally the conclusions are drawn in Section VI.

#### II. CIRCUIT DESCRIPTION

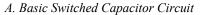

Fig. 1 The structure and operating principle of BSCC. (a) Structure of BSCC, (b) Charging path, (c) Positive discharge path, (d) Negative discharge path.

The structure and operating principle of basic switched capacitor circuit (BSCC) are shown in Fig. 1. In Fig. 1(b), the capacitor is charged to the rated voltage in parallel with the charging path. Fig. 1(c) and Fig.1(d) show the discharge path of the capacitor. Through different switching strategies, the structure achieves the opposite discharge polarity to the outside. Due to the periodicity of the operating principle of the capacitor, the voltage balance of the capacitor does not have to be considered. Therefore, the use of additional voltage balancing circuits and complex modulation strategies can be avoided.

#### B. Proposed General Switched Capacitor Multilevel Topology

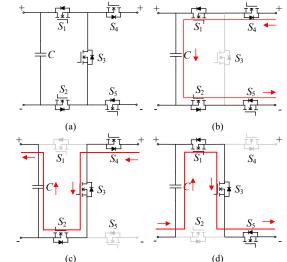

Fig. 2 shows the generalized topology of the proposed switched capacitor inverter, the intermediate switched capacitor circuit (ISCC) consists of a voltage source  $V_{dc}$ , a diode D, a capacitor C, and three switches. Unlike other topologies that obtain bipolar levels by using H-bridges, the proposed topology implements bipolar level output by placing equivalent number of BSCC on the both sides of ISCC, respectively. The left half

bridge of the proposed topology is composed of switches  $S_{01}$ and  $S_{02}$ , and the corresponding right half bridge is composed of switches  $S_{03}$  and  $S_{04}$ , these two half bridges are placed at the both ends of the topology, respectively. For the proposed topology, if the number of pairs of BSCC placed on both sides of the ISCC is *n*, the number of required diodes ( $N_{Diode}$ ), switches ( $N_{Switch}$ ), capacitors ( $N_{Capacitor}$ ), the number of generated output levels ( $N_{Level}$ ) and the output gain *G* can be obtained by

$$N_{Diode} = 1 , \qquad (1)$$

$$N_{Switch} = 10n + 7, \qquad (2)$$

$$N_{Capacitor} = 2n + 1, \qquad (3)$$

$$N_{Level} = 2^{n+3} - 3, (4)$$

$$G = 2^{n+2} - 2. (5)$$

In this case, the number of output levels can be increased by adding the same number of BSCCs on the both sides, it is worth noting that the capacitor C in the ISCC is charged to  $V_{dc}$  in parallel with the power supply. In the extension step, the capacitors  $C_{Ln}$  and  $C_{Rn}$  in the extended BSCC are step-charged by the source and the capacitors in the previous extension step. In an ideal situation, the capacitor charging voltage  $V_{CLn}$  and  $V_{CRn}$  can be computed as

$$V_{CLn} = V_{CRn} = V_{dc} + V_C + V_{CL1} + + V_{CL(n-1)}.$$

(6)

Due to the step charging of capacitor, the capacitor in the path of the inverter works can pump more charge, therefore, more voltage levels can be generated by the inverter.

In general, switched capacitor multilevel inverters always face some of the same problems. For instance, the release of charge in the capacitor will reduce its voltage value and cause its voltage ripple loss. Especially, the output voltage of switched capacitor multilevel inverter is superimposed by the power supply and the capacitors participating in the discharge, which will highlight the adverse impact of the capacitor voltage ripple. As a result, the output voltage of inverter may drop greatly and its quality is inevitably reduced. Sometimes, there is no reverse current loop in the topology, this will make it unable to carry inductive load. Next, in order to address these problems, as a typical representative of the proposed generalized topology, the 13-level switched capacitor inverter will be analyzed in detail.

Fig. 2 Generalized topology of the proposed switched capacitor multilevel inverter.

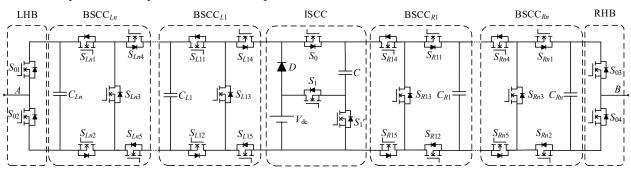

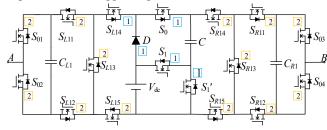

#### C. Thirteen-Level Inverter

The structure of the proposed 13-level inverter is shown in Fig. 3, which consists of a voltage source  $V_{dc}$ , a diode D, three capacitors, and seventeen switches. The state of the switch  $S_1$  and  $S_1'$  are complementary and the states of the switch  $S_{L1n}$  and the switch  $S_{R1n}$  (n = 1, 2, 3, 4, 5) are consistent when the inverter output levels have opposite polarities.

Fig. 3 Topology of the proposed 13-level inverter.

Unlike other topologies that use the H-bridges to acquire bipolar levels, the proposed topology owns inherent level polarity reversal capabilities, which can effectively reduce the PIV of semiconductors. As presented in Fig. 3, the maximum PIV of the semiconductors is  $2V_{dc}$ , consistent with the maximum charging voltage of the capacitors. The half-bridge of the inverter outputs a peak level of  $4V_{dc}$  and a valley level of  $-2V_{dc}$ , respectively. Therefore, the maximum output level of the inverter is  $6V_{dc}$ , which obtains a boost gain of 6 times. The output bus voltage  $V_{bus}$  of the proposed 13-level inverter can be calculated by

$$V_{bus} = V_A - V_B. \tag{7}$$

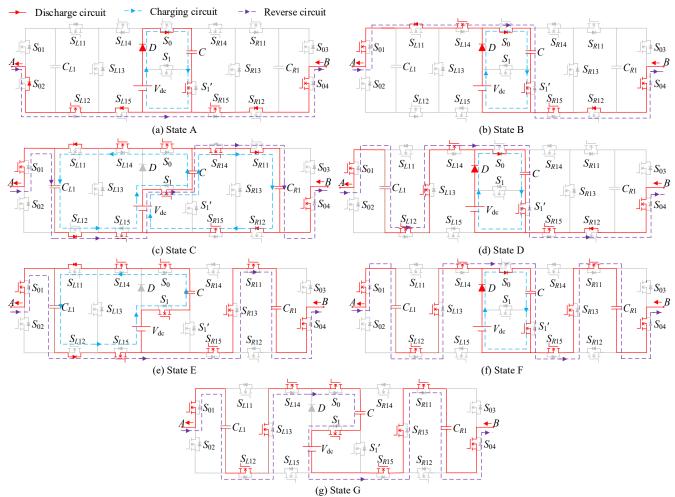

#### D. States of 13-Level Inverter

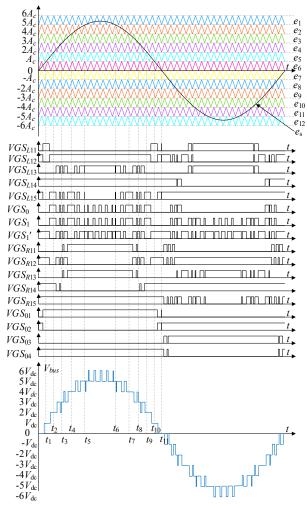

In general, according to the output level, the 13-level inverter can be divided into 13 operating states. In this part, due to the page limitation, only seven operating states (states A ~ G) of the 13-level inverter during the positive half cycle are shown in Fig. 4. In which, the purple dotted line represents the reverse current circuit of the inverter that ensures its inductive load capacity. Fig. 5 shows the modulation strategy of the 13-level inverter. To make the concept clearly, it is assumed that all the components of the inverter are ideal, and there is no internal resistance and forward voltage drop in the inverter. In addition, the capacitance of the circuit is large enough, and the inverter works in a stable state, voltages of the capacitors are constant at  $V_C = V_{dc}$  and  $V_{CL1} = V_{CR1} = 2V_{dc}$ , respectively.

TABLE I

SWITCHING STATE AND CAPACITANCE STATE OF THE PROPOSED INVERTER

| Reference                  | State | On-State Switches                                                                | Output Valtage V                | Capacitors |          |          |

|----------------------------|-------|----------------------------------------------------------------------------------|---------------------------------|------------|----------|----------|

|                            | State | On-State Switches                                                                | Output Voltage V <sub>bus</sub> | С          | $C_{L1}$ | $C_{R1}$ |

| $e_{s} > e_{1}$            | G     | $S_{L12}, S_{L13}, S_{L14}, S_{R11}, S_{R13}, S_{R15}, S_0, S_1, S_{01}, S_{04}$ | $6V_{\rm dc}$                   | ▼          | ▼        | ▼        |

| $e_1 \ge e_s > e_2$        | F     | SL12, SL13, SL14, SR11, SR13, SR15, S1', S01, S04                                | $5V_{\rm dc}$                   |            | ▼        | ▼        |

| $e_2 \ge e_s > e_3$        | Е     | $S_{L12}, S_{L14}, S_{L15}, S_{R11}, S_{R13}, S_{R15}, S_0, S_1, S_{01}, S_{04}$ | $4V_{ m dc}$                    | ▼          |          | •        |

| $e_3 \ge e_s > e_4$        | D     | SL12, SL13, SL14, SR12, SR15, S1', S01, S04                                      | $3V_{dc}$                       |            | ▼        | -        |

| $e_4 \ge e_s > e_5$        | С     | $S_{L12}, S_{L14}, S_{L15}, S_{R14}, S_{R15}, S_0, S_1, S_{01}, S_{04}$          | $2V_{\rm dc}$                   | ▼          |          |          |

| $e_5 \ge e_s > e_6$        | В     | SL11, SL14, SR12, SR15, S1', S01, S04                                            | $V_{ m dc}$                     |            | -        | -        |

| $e_6 \ge e_s > e_7$        | А     | SL12, SL15, SR12, SR15, S1', S02, S04                                            | 0                               |            | -        | _        |

| $e_7 \ge e_s > e_8$        | -     | $S_{L12}, S_{L15}, S_{R11}, S_{R14}, S_1', S_{02}, S_{03}$                       | $-1V_{dc}$                      |            | -        | _        |

| $e_8 \ge e_s > e_9$        | -     | $S_{L14}, S_{L15}, S_{R12}, S_{R14}, S_{R15}, S_0, S_1, S_{02}, S_{03}$          | $-2V_{dc}$                      | ▼          |          |          |

| $e_9 \geq e_s > e_{10}$    | -     | SL12, SL15, SR12, SR13, SR14, S1', S02, S03                                      | $-3V_{dc}$                      |            | -        | ▼        |

| $e_{10} \geq e_s > e_{11}$ | -     | $S_{L11}, S_{L13}, S_{L15}, S_{R12}, S_{R14}, S_{R15}, S_1, S_{02}, S_{03}$      | $-4V_{dc}$                      | ▼          | ▼        |          |

| $e_{11} \geq e_s > e_{12}$ | -     | $S_{L11}, S_{L13}, S_{L15}, S_{R12}, S_{R13}, S_{R14}, S_1', S_{02}, S_{03}$     | $-5V_{\rm dc}$                  |            | ▼        | •        |

| $e_{12} \ge e_s$           | -     | SL11, SL13, SL15, SR12, SR13, SR14, S1, S02, S03                                 | $-6V_{dc}$                      | ▼          | •        | ▼        |

As depicted in Fig. 5, during time  $0 \le t \le t_1$ , the switches  $S_{L11}$ ,  $S_{L12}$ ,  $S_{L15}$ ,  $S_{01}$  and  $S_{02}$  are respectively driven by the gate-source voltage  $VGS_{L11}$ ,  $VGS_{L12}$ ,  $VGS_{L15}$ ,  $VGS_{01}$  and  $VGS_{02}$ , the other switches are turned on or off as given in Fig. 5. When the switches  $S_{L11}$ ,  $S_{L12}$ ,  $S_{L15}$ ,  $S_{01}$  and  $S_{02}$  alternately switch states, the inverter output states shown in Fig. 4(a) and (b) are switched alternately. In the situation of Fig. 4(a), the output bus voltage  $V_{bus}$  can be computed as

$$V_{bus} = V_A - V_B = 0.$$

<sup>(8)</sup>

As shown in Fig. 4(b), the capacitor C is charged in parallel with the source  $V_{dc}$ . At this time, the output bus voltage is

$$V_{bus} = V_A - V_B = V_{dc} \,. \tag{9}$$

Therefore, during this time, the inverter outputs a bus voltage of 0 or  $V_{dc}$  as shown in Fig. 5.

It can be seen that in Fig. 5, while  $t_1 < t \le t_2$ , the switches  $S_{L11}$ ,  $S_{L12}$ ,  $S_{L15}$ ,  $S_{R12}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  are respectively driven by the gatesource voltage  $VGS_{L11}$ ,  $VGS_{L12}$ ,  $VGS_{L15}$ ,  $VGS_{R12}$ ,  $VGS_0$ ,  $VGS_1$  and  $VGS_1'$ , the other switches are turned on or off. When the switches  $S_{L11}$ ,  $S_{L12}$ ,  $S_{L15}$ ,  $S_{R12}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  alternately switch states, the inverter output states shown in Fig. 4(b) and (c) are switched alternately. In Fig. 4(c), the capacitors  $C_{L1}$  and  $C_{R1}$  are charged by a series combination of source  $V_{dc}$  and capacitor C, the output bus voltage  $V_{bus}$  can be calculated as

$$V_{bus} = V_A - V_B = 2V_{dc} . (10)$$

Therefore, during this time, the inverter outputs a bus voltage of  $V_{dc}$  or  $2V_{dc}$  as shown in Fig. 5.

In Fig. 5, when  $t_2 < t \le t_3$ , the switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_{R12}$ ,  $S_{R14}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  are respectively driven by the gate-source voltage  $VGS_{L13}$ ,  $VGS_{L15}$ ,  $VGS_{R12}$ ,  $VGS_{R14}$ ,  $VGS_0$ ,  $VGS_1$  and  $VGS_1'$ , the other switches are turned on or off. While the switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_{R12}$ ,  $S_{R12}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  alternate switch status, the inverter output states in Fig. 4(c) and (d) are switched alternately. As it can be seen in Fig. 4(d), the capacitor C is charged in parallel with the source  $V_{dc}$ , the capacitor  $C_{L1}$  participates in discharge. the output bus voltage  $V_{bus}$  in the state shown in Fig. 4(d) is

$$V_{bus} = V_A - V_B = V_{dc} + V_{CL1} \,. \tag{11}$$

Therefore, during this time, the inverter outputs a bus voltage of  $2V_{dc}$  or  $3V_{dc}$  as shown in Fig. 5.

In Fig. 5, while  $t_3 < t \le t_4$ , the switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_{R11}$ ,  $S_{R12}$  $S_{R13}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  are respectively driven by the gate-source voltage  $VGS_{L13}$ ,  $VGS_{L15}$ ,  $VGS_{R11}$ ,  $VGS_{R12}$ ,  $VGS_{R13}$ ,  $VGS_0$ ,  $VGS_1$  and  $VGS_1'$ , the other switches are turned on or off. When the switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_{R11}$ ,  $S_{R12}$ ,  $S_{R13}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  alternately switch states, the inverter output states shown in Fig. 4(d) and (e) are switched alternately. As shown in Fig. 4(e), the capacitors  $C_{L1}$  are charged by series combination of source  $V_{dc}$  and capacitor C, the capacitor  $C_{R1}$  participates in discharge. the output bus voltage  $V_{bus}$  in the state shown in Fig.4(e) is

$$V_{bus} = V_A - V_B = V_{dc} + V_C - (-V_{CR1}).$$

(12)

Therefore, during this time, the inverter outputs a bus voltage of  $3V_{de}$  or  $4V_{de}$  as shown in Fig. 5.

In Fig. 5, during the time  $t_4 < t \le t_5$ , the switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  are driven by the gate-source voltage  $VGS_{L13}$ ,  $VGS_{L15}$ ,  $VGS_0$ ,  $VGS_1$  and  $VGS_1'$ , the other switches are turned on or off. Fig. 4(e) and (f) present the switched alternately output states, while the states of switches  $S_{L13}$ ,  $S_{L15}$ ,  $S_0$ ,  $S_1$  and  $S_1'$  alternated. In Fig. 4(f), the capacitor C is charged in parallel with the source  $V_{dc}$ , the capacitor  $C_{L1}$  and  $C_{R1}$  participate in discharge. the output bus voltage  $V_{bus}$  can be derived as

$$V_{bus} = V_A - V_B = V_{dc} + V_{CL1} - (-V_{CR1}).$$

(13)

In this scenario, the output bus voltage of the proposed inverter is  $4V_{dc}$  or  $5V_{dc}$ , which are depicted in Fig. 5.

While  $t_5 < t \le t_6$ , the switches  $S_0$ ,  $S_1$  and  $S_1'$  are driven by the gate-source voltage  $VGS_0$ ,  $VGS_1$  and  $VGS_1'$ , respectively. The states of other switches are shown in Fig. 5. It can be seen from Fig. 4(f) and (g), while the switches  $S_0$ ,  $S_1$  and  $S_1'$  alternately switch states, the output states of proposed inverter are switched alternately. In addition, in Fig. 4(g), the capacitor C,  $C_{L1}$  and  $C_{R1}$  in the discharge circuit participates in the output of the inverter and the output bus voltage  $V_{bus}$  can be calculated by

$$V_{bus} = V_A - V_B = V_{dc} + V_C + V_{CL1} - (-V_{CR1}).$$

(14)

In this case,  $5V_{dc}$  or  $6V_{dc}$  output bus voltage can be acquired, which is presented in Fig. 5.

While  $t_6 < t \le t_{11}$ , the operating state of the inverter is from state F to state A. It can be seen from Table I that the operating state of the capacitor  $C_{L1}$  in the positive half cycle is consistent with the operating state of the capacitor  $C_{R1}$  in the negative half cycle, the operating state of the capacitor  $C_{L1}$  in the negative half cycle is consistent with the operating state of the capacitor  $C_{R1}$  in the positive half cycle, and the states of the switches  $S_{L1n}$ and the switches  $S_{R1n}$  (n = 1, 2, ..., 5) are consistent when the inverter output levels have opposite polarities. Therefore, the operating principle of the negative half cycle of the inverter is similar to that of the positive half cycle. The switching state of the inverter in one cycle is summarized in Table I, where the capacitance state is also given.

#### E. Modulation Strategy

There are many modulation strategies used in multilevel inverters. In this paper, sinusoidal pulse width modulation (SPWM) is used in a 13-level inverter as shown in Fig. 3. For a single-phase z-level inverter ( $z \ge 3$ , odd number), it is necessary z-1 carrier waves is compared with a sine-modulated wave. As

shown in Fig. 5, the proposed 13-level inverter needs 12 carrier waves  $e_k$  (k = 1, 2, ..., 12) with amplitude  $A_c$  and the same frequency and phase, which is required to be compared to sine-modulated wave  $e_s$  with amplitude  $A_{ref}$ . The modulation index M ( $0 < M \le 1$ ) is defined as

$$M = \frac{A_{ref}}{6A_c} \,. \tag{15}$$

It can be known from the operating principle of the 13-level inverter that the proposed inverter requires 14 independent driving signals. In addition, the states of the switches  $S_{L1n}$  and the switches  $S_{R1n}$  (n = 1, 2, ..., 5) are consistent when the inverter output levels have opposite polarities. Therefore, the modulation difficulty of the proposed 13-level inverter is reduced.

As shown in Fig. 5, the sine-modulated wave is compared with each carrier wave separately. The high level is output when the sine-modulated wave is larger than the carrier waves, and the low level is output while the sine-modulated wave is smaller than the carrier waves. From this, a set of rectangular pulse signals is obtained. Twelve pulse signals generated by comparing the carrier wave with the sine-modulation wave, after logical combination, the switch driving signals shown in Fig. 5 can be obtained.

Fig. 4 Current flows in the proposed inverter. (a)  $V_{bus}=0$ , (b)  $V_{bus}=V_{dc}$ , (c)  $V_{bus}=2V_{dc}$ , (d)  $V_{bus}=3V_{dc}$ , (e)  $V_{bus}=4V_{dc}$ , (f)  $V_{bus}=5V_{dc}$ , (g)  $V_{bus}=6V_{dc}$ .

Fig. 5 SPWM modulation and corresponding gate pulses for 13-level inverter.

#### III. CAPACITANCE DETERMINATION AND LOSSES CALCU-LATION

#### A. Determination of Capacitance

The output voltage of the switched capacitor multilevel inverter is a combination of the power supply voltage and the capacitor voltage, and each capacitor has a voltage ripple during the discharge process. A larger voltage ripple will cause deterioration of the inverter efficiency and THD, so that the quality of the output voltage waveform is affected heavily.

In addition, the large voltage ripple caused by the continuous discharge of the capacitor will also damage the stability of the system. When the capacitor is charged in parallel with the charging circuit, an inrush current will be generated. A large inrush current will cause electromagnetic interference, and in severe cases, it will damage the switch. It can be seen from the charging operation of the capacitor that the inrush current is determined by the voltage difference (the difference between the rated charging voltage and the minimum voltage of the capacitor) and the internal resistance of the semiconductor device. Smaller voltage ripple helps to reduce the voltage difference, thereby suppressing the inrush current.

Therefore, it is necessary to choose a suitable capacitor. As expressed in Fig. 5, in the 13-level inverter,  $t_1$ , ...,  $t_5$ ,  $t_6$ , ...,  $t_{10}$  can be calculated by Eqs. (16) and (17), respectively

$$t_n = \frac{\sin^{-1}\left(\frac{n}{6}\right)}{2\pi f_{ref}},\tag{16}$$

$$t_{11-n} = \frac{\pi - \sin^{-1}\left(\frac{n}{6}\right)}{2\pi f_{ref}},$$

(17)

where  $f_{ref}$  is the output frequency of inverter, n = 1, 2, ..., 5.

It is known that the maximum time period for capacitor C to participate in discharge is  $(t_5, t_6)$ , during this time, the capacitor C is charged and discharged repeatedly. In the worst case, no charging term is given. Then this discharge period can be used to determine the optimal value of the capacitor under a given voltage ripple limit. the amount of charge  $Q_C$  discharged by the capacitor C can be computed as

$$Q_{C} = \int_{t_{5}}^{t_{6}} I_{bus} \sin\left(2\pi f_{ref} - \varphi\right) dt , \qquad (18)$$

where  $I_{bus}$  indicates the amplitude of the load current, and  $\varphi$  denotes the phase difference between the output voltage  $V_{bus}$  and the load current  $I_{bus}$ .

When the voltage ripple  $\Delta V_C (\Delta V_C \le 0.1 V_C)$  of the capacitor *C* is given, the optimal value of the capacitor *C* can be acquired by

$$C \ge \frac{Q_C}{\Delta V_C} \,. \tag{19}$$

The maximum time period for the capacitor  $C_{R1}$  to participate in the discharge is  $(t_3, t_8)$ . During this period, the capacitor  $C_{R1}$ is not charged, then the amount of charge  $Q_{CR1}$  released by the capacitor  $C_{R1}$  can be acquired by

$$Q_{CR1} = \int_{t_3}^{t_8} I_{bus} \sin(2\pi f_{ref} - \varphi) dt \,. \tag{20}$$

When the voltage ripple  $\Delta V_{CR1}$  ( $\Delta V_{CR1} \leq 0.1 V_{CR1}$ ) of the capacitor  $C_{R1}$  is given, the optimal value of the capacitor  $C_{R1}$  can be computed as

$$C_{R1} \ge \frac{Q_{CR1}}{\Delta V_{CR1}}.$$

(21)

Due to the symmetrical operation of the capacitors  $C_{L1}$  and  $C_{R1}$ , therefore, the values of capacitor  $C_{L1}$  can be calculated by utilizing the similar calculation formulas.

#### B. Calculation of Losses

In this section, the energy loss of the proposed inverter in the working state is calculated, including ripple losses, switching losses and conduction losses.

1) **Ripple Losses:** When the capacitor is running in parallel charging state, the voltage  $\Delta V_{Ci}$  difference between capacitor charging voltage and the capacitor terminal voltage will produce ripple losses  $P_{rip}$ , the ripple voltage of the capacitor can be derived as

$$\Delta V_{Ci} = \frac{1}{C_i} \int_{t_{n,i}}^{t_{m,i}} i_{Ci} dt , \qquad (22)$$

where  $i_{ci}$  denotes the current flowing through the *i*th capacitor in the discharge state,  $(t_{m,i}, t_{n,i})$  indicates the discharge time of the capacitor in the entire cycle. Therefore, the ripple losses of the entire period can be obtained by

$$P_{rip} = \frac{f_{ref}}{2} \sum_{i=1}^{3} C_i \Delta V_{Ci}^2.$$

(23)

2) *Switching Losses*: The switching losses can be estimated from the charging and discharging process of the parasitic capacitor in the switch. It is assumed that the parasitic capacitor is linear. When the switch  $S_i$  is in the off state, the voltage of the parasitic capacitor  $C_S$  is gradually charged from 0 to  $V_{CS,i}$ , and  $V_{CS,i}$  is approximately equal to the peak invert voltage  $V_{S,i}$  of the switch  $S_i$ . The PIV of each switch in the proposed 13-level inverter is given in Fig.3. When the switch is turned on, the stored charge of the parasitic capacitor is consumed in the form of heat by the internal resistance. In a switching cycle, the loss is calculated as

$$E_{\rm S,i} = C_{\rm S} V_{{\rm CS},i}^2 \,. \tag{24}$$

The loss of the switch during one cycle of inverter operation is

$$P_{\rm S,i} = C_{\rm S} V_{\rm S,i}^2 f_{\rm S,i} , \qquad (25)$$

where  $f_{S,i}$  is the switching frequency.

$$f_{{\rm S},i} = N_{{\rm S},i} f_{\rm ref} ,$$

(26)

where  $N_{S,i}$  is the number of switching times in one work cycle of the inverter. According to Fig. 4 and Fig. 5, the switch is repeatedly turned on and off in its working range. Therefore,  $N_{S,i}$  can be obtained by the following equation

$$N_{\rm S,i} = \frac{t_{\rm S,i} f_{\rm c}}{T_{\rm S} f_{\rm ref}},$$

(27)

where  $f_c$  is the carrier frequency,  $t_{S,i}$  is the operating time of the switch  $S_i$ , which can be obtained in Fig. 5.  $T_S$  is one cycle of the inverter. Therefore, the switching losses of the proposed 13-level inverter in one cycle can be estimated as

$$P_{\rm S} = 50 \sum_{i=1}^{17} C_{\rm S} V_{{\rm S},i}^2 t_{{\rm S},i} f_{\rm c} \,, \qquad (28)$$

3) **Conduction Losses:** During the conduction of the semiconductor device, energy losses occur due to the presence of parasitic impedance. The total parasitic impedance  $r_{eq}$  of the proposed inverter at various output voltages is presented in Table II, including the internal resistance  $r_{S}$  of the switch's conduction state, the internal resistance  $r_{D}$  of the diode con duction state, and the equivalent series resistance  $r_{ESR}$  of the capacitor.

As shown in Fig. 5, when  $0 < |e_s| \le A_c$ , the inverter alternately outputs 0 level and  $+V_{dc}$  level. While the inverter outputs 0 level, the capacitor *C* is charged in parallel with the source, and the current flows through the anti-parallel diode of the switch  $S_0$ , the diode *D* the switch  $S_1$ '. While the inverter outputs  $+V_{dc}$  level, current flows through 5 switches and 4 diodes. Therefore, the conduction losses  $P_{con1}$  in time  $0 < t \le t_1$  can be calculated by

TABLE II

EQUIVALENT PARASITIC IMPEDANCE OF EACH LEVEL

| Output Voltage Level (V <sub>bus</sub> ) | Total Parasitic Impedance $(r_{eq})$       |

|------------------------------------------|--------------------------------------------|

| 0                                        | $r_{\rm S}$ + $2r_{\rm D}$ + $r_{\rm ESR}$ |

| $\pm V_{ m dc}$                          | $5r_{\rm S}+4r_{\rm D}+r_{\rm ESR}$        |

| $\pm 2V_{ m dc}$                         | $8r_{\rm S}+4r_{\rm D}+3r_{\rm ESR}$       |

| $\pm 3 V_{ m dc}$                        | $7r_{\rm S}+3r_{\rm D}+2r_{\rm ESR}$       |

| $\pm 4V_{ m dc}$                         | $9r_{\rm S}+2r_{\rm D}+3r_{\rm ESR}$       |

| $\pm 5 V_{ m dc}$                        | $9r_{\rm S}+2r_{\rm D}+3r_{\rm ESR}$       |

| $\pm 6V_{ m dc}$                         | $10r_{\rm S}+3r_{\rm ESR}$                 |

$$P_{con1} = \int_{0}^{t_{1}} \left[ I_{bus} \sin \left( 2\pi f_{ref} t \right) \right]^{2} \\ \times \left[ (5r_{\rm S} + 4r_{\rm D} + r_{\rm ESR}) \frac{A_{ref} \sin \left( 2\pi f_{ref} t \right)}{A_{c}} \\ + \left( r_{\rm S} + 2r_{\rm D} + r_{\rm ESR} \right) \left( 1 - \frac{A_{ref} \sin \left( 2\pi f_{ref} t \right)}{A_{c}} \right) \right] dt \right]$$

(29)

During the period  $t_{10} < t \le t_{11}$ , the energy losses are the same as interval  $0 < t \le t_1$ . When  $A_c < |e_s| \le 2A_c$ , the inverter alternately outputs  $+V_{dc}$  level and  $+2V_{dc}$  level, and the equivalent impedance in the output path is given in Table II. The conduction losses  $P_{con2}$  during time  $t_1 < t \le t_2$  can be calculated by

$$P_{con2} = \int_{t_1}^{t_2} \left[ I_{bus} \sin\left(2\pi f_{ref}t\right) \right]^2 \\ \times \begin{bmatrix} (8r_{\rm S} + 4r_{\rm D} + 3r_{\rm ESR}) \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - A_c}{A_c} \\ + (5r_{\rm S} + 4r_{\rm D} + r_{\rm ESR}) \left(1 - \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - A_c}{A_c} \right) \end{bmatrix} dt$$

(30)

In the period  $t_9 < t \le t_{10}$ , the energy losses are the same as interval  $t_1 < t \le t_2$ . By utilizing the same analysis method, the conduction losses during the time periods  $t_2 < t \le t_3$  ( $t_8 < t \le t_9$ ),  $t_3 < t \le t_4$  ( $t_7 < t \le t_8$ ),  $t_4 < t \le t_5$  ( $t_6 < t \le t_7$ ) and  $t_5 < t \le t_6$  can be obtained by

$$P_{con3} = \int_{t_2}^{t_3} \left[ I_{bus} \sin\left(2\pi f_{ref}t\right) \right]^2 \\ \times \begin{bmatrix} (7r_{\rm S} + 3r_{\rm D} + 2r_{\rm ESR}) \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 2A_c}{A_c} \\ + (8r_{\rm S} + 4r_{\rm D} + 3r_{\rm ESR}) \left(1 - \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 2A_c}{A_c} \right) \end{bmatrix}_{dt}^{dt},$$

(31)

| TABLE III                                                                        |     |

|----------------------------------------------------------------------------------|-----|

| COMPARISON OF THE PROPOSED TOPOLOGY WITH A 13-LEVEL INVERTER AND A 9-LEVEL INVER | ΓER |

| Items    | $N_L$ | Ns  | $N_D$ | N  | PIV        | TSV        | $CF^*$ |      | - G* | H-bridge | Extended  |

|----------|-------|-----|-------|----|------------|------------|--------|------|------|----------|-----------|

| nems     | IVL   | 185 | IND   | Nc | $(V_{dc})$ | $(V_{dc})$ | 0.5    | 1.5  | 0.   | H-blidge | ability   |

| [18]     | 9     | 10  | 3     | 3  | 4          | 26         | 3.44   | 6.78 | 1.33 | Yes      | No        |

| [19]     | 9     | 8   | 3     | 3  | 4          | 23         | 3.06   | 6.06 | 1.33 | No       | No        |

| [20]     | 13    | 13  | 2     | 3  | 3          | 32         | 2.73   | 5.42 | 2    | No       | No        |

| [21]     | 13    | 10  | 4     | 4  | 6          | 33         | 2.88   | 5.88 | 1.5  | No       | No        |

| [22]     | 13    | 14  | 1     | 3  | 3          | 33         | 2.77   | 5.54 | 2    | No       | Not given |

| [29]     | 13    | 10  | 10    | 5  | 6          | 60         | 4.46   | 9.54 | 1.2  | Yes      | Yes       |

| [32]     | 13    | 34  | 0     | 12 | 3.5        | 25         | 4.63   | 6.83 | 0.25 | No       | Yes       |

| [35]     | 13    | 23  | 0     | 6  | 4          | 40         | 3.92   | 7.31 | 1    | No       | Yes       |

| Proposed | 13    | 17  | 1     | 3  | 2          | 31         | 2.88   | 5.42 | 2    | No       | Yes       |

TABLE IV

COMPARISON OF PARAMETERS BETWEEN THE PROPOSED TOPOLOGY AND TOPOLOGIES IN [30]-[35] WHEN OUTPUT LEVEL 2N+1

| Items                           | [30]                      | [31]            | [32]           | [33]                               | [34]          | [35]          | Proposed                |

|---------------------------------|---------------------------|-----------------|----------------|------------------------------------|---------------|---------------|-------------------------|

|                                 |                           |                 |                |                                    |               |               |                         |

| $N_{Switch}$                    | 2 <i>N</i> +2             | 3 <i>N</i> +2   | 6 <i>N</i> -2  | $4 + 8\log_2^{(N+2)/3}$            | 5 <i>N</i> -1 | 3 <i>N</i> +5 | $10\log_2^{N+2} - 13$   |

| NCapacitor                      | N                         | <i>N</i> -1     | 2N             | $4\log_2^{(N+2)/3}$                | <i>N</i> -1   | Ν             | $2\log_2^{N+2} - 3$     |

| NDiode                          | Ν                         | 0               | 0              | $4\log_2^{(N+2)/3}$                | 0             | 0             | 1                       |

| $G^*$                           | 1                         | N/(N-1)         | 0.25           | $N/\left(4\log_2^{(N+2)/3}\right)$ | N/(N-1)       | 1             | $N/(2\log_2^{N+2} - 3)$ |

| $\mathrm{TSV}(V_{\mathrm{dc}})$ | (N <sup>2</sup> +11N-4)/2 | 11 <i>N</i> -14 | $(N^2+3N-4)/2$ | (16N-4)/3                          | 5 <i>N</i> -1 | 7 <i>N</i> -2 | 5N                      |

| $\operatorname{PIV}(V_{dc})$    | Ν                         | Ν               | (N+1)/2        | (N+2)/3                            | 1             | 4             | (N+2)/4                 |

| H-bridge                        | YES                       | NO              | NO             | NO                                 | NO            | NO            | NO                      |

$$P_{con4} = \int_{t_3}^{t_4} \left[ I_{bus} \sin\left(2\pi f_{ref}t\right) \right]^2 \\ \times \begin{bmatrix} (9r_{\rm S} + 2r_{\rm D} + 3r_{\rm ESR}) \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 3A_c}{A_c} \\ + (7r_{\rm S} + 3r_{\rm D} + 2r_{\rm ESR}) \left(1 - \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 3A_c}{A_c} \right) \end{bmatrix}_{dt}^{dt},$$

(32)

$$P_{con5} = \int_{t_4}^{t_5} \left[ I_{bus} \sin\left(2\pi f_{ref}t\right) \right]^2 \\ \times \begin{bmatrix} (9r_{\rm S} + 2r_{\rm D} + 3r_{\rm ESR}) \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 4A_c}{A_c} \\ + (9r_{\rm S} + 2r_{\rm D} + 3r_{\rm ESR}) \left[ 1 - \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 4A_c}{A_c} \end{bmatrix} \end{bmatrix}_{dt},$$

(33)

$$P_{con6} = \int_{t_{5}}^{t_{6}} \left[ I_{bus} \sin\left(2\pi f_{ref}t\right) \right]^{2} \\ \times \begin{bmatrix} (10r_{\rm S} + 3r_{\rm ESR}) \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 5A_{c}}{A_{c}} \\ + (9r_{\rm S} + 2r_{\rm D} + 3r_{\rm ESR}) \left[ 1 - \frac{A_{ref} \sin\left(2\pi f_{ref}t\right) - 5A_{c}}{A_{c}} \right] \end{bmatrix} dt$$

(34)

It can be seen from Table I that the operation of the inverter in positive and negative half period is symmetrical. Thus, the conduction losses of the inverter in the two half periods are equal. Therefore, the conduction losses  $P_{total}$  of the inverter can be obtained by

$P_{total} = 2 f_{ref} \left( 2P_{con1} + 2P_{con2} + 2P_{con3} + 2P_{con4} + P_{con5} \right).$  (35) In summary, the power loss  $P_{Loos}$  of the proposed inverter can be calculated by

$$P_{Loos} = P_{rip} + P_{sw} + P_{total} .$$

(36)

Under different parameters, 13-level inverters have different losses. When the input voltage of the inverter is 25V and the load is 100  $\Omega$ , the ripple losses, switching losses and conduction losses loss can be estimated at 2.14 W, 0.49 W and 1.67 W. Under the current conditions, the output efficiency is 96.32%, and the actual measured efficiency is 95.4%. The measured efficiency is slightly lower than the estimated efficiency due to the existence of error, which is superior to the existing inverters [36-39].

### IV. COMPARISON BETWEEN THE PROPOSED TOPOLOGY AND OTHER SCMLI TOPOLOGIES

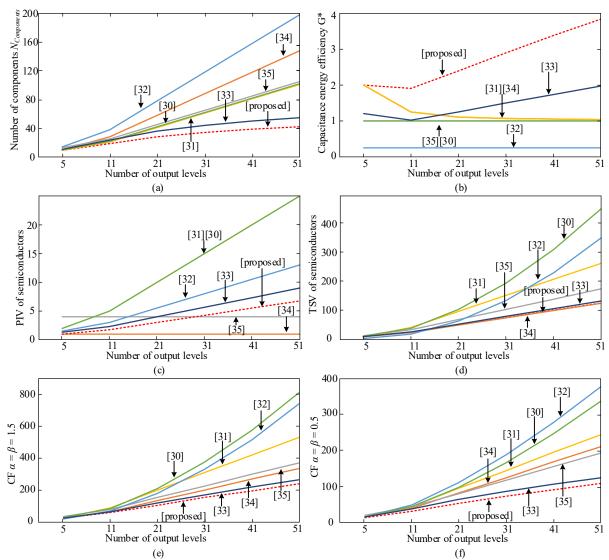

In this section, in order to effectively assess the advantages of the proposed topology in terms of reducing the number of components and reducing voltage stress, it is necessary to make a detailed comparison with the recently proposed similar topology from different perspectives. Here, two different schemes are designed to compare the topology at the output 13 levels and the output level 2N+1.

#### A Comparison of 13-Level Inverters and 9-Level Inverters

In order to evaluate the performance of the proposed inverter, a comparative study is conducted between the proposed 13level inverter and the existing solution, the comparative results are given in Table III. As shown in Table III, the main comparison parameters are the number of switches ( $N_S$ ), the number of diodes ( $N_D$ ), the number of capacitors ( $N_C$ ), the maximum PIV of switches and diodes, the TSV of switches and diodes, the use of H-bridge and extension capacity.

In order to achieve a fair comparison results at different output levels of the inverter, the capacitance energy efficiency  $G^*$  and the cost function  $CF^*$  are introduced.  $G^*$  is defined as the ratio of the output gain G to the number of capacitors ( $N_C$ ). The cost function  $CF^*$  represents the total cost of the inverter, as defined below

$$CF^* = \frac{\left(N_S + N_D + N_C + \alpha \times \frac{\text{TSV}}{V_{dc}} + \beta \times \frac{\text{PIV}}{V_{dc}}\right)}{N_L}, \quad (37)$$

where  $\alpha$  and  $\beta$  are the specific gravity coefficients, which indicate the significance of PIV and TSV. If the significance of PIV and TSV are greater than the number of switches, then both  $\alpha$ and  $\beta$  should be greater than 1. If the significance of PIV and TSV are less than the number of components, then  $\alpha$  and  $\beta$ should be less than 1. In Table III, the total cost of each inverter is given when  $\alpha = \beta = 0.5$  and  $\alpha = \beta = 1.5$ .

The topologies in [18] and [19] are 9-level inverters, which use 16 and 14 components respectively. As can be seen from the Table III, the maximum PIV of the 9-level inverter is  $4V_{dc}$ , which is higher than the proposed 13-level inverter. Although the proposed inverter uses more components, it has lower cost and higher capacitance energy efficiency. The 13-level inverter in [29] adopts H-bridge output bipolar level, and the inverter has a large PIV. The proposed topologies in [20] and [21] employ fewer components, but the topologies have a large PIV, which is not conducive to the application of inverters in medium-high voltage scenarios. In addition, the topologies proposed in [20]-[21] are fixed and without extensibility.

Compared with the topologies in [32] and [35], the proposed topology uses fewer components, and has a low cost and high capacitance energy efficiency. The topology in [22] uses 18 components, and needs less components than the proposed topology. But the maximum PIV of the components is  $3V_{dc}$ , while the proposed topology is only  $2V_{dc}$ . In addition, the proposed topology has lower TSV and extensibility.

In summary, the proposed 13-level inverter has higher capacitance energy efficiency and lower PIV. It can be seen from the comparison result of cost that when the significance of the number of components is greater than the voltage stress, the cost of the proposed topology is higher than the topologies in [20] and [22], and lower than the other topologies. When the significance of the number of components is less than the voltage stress, the proposed topology has the lowest cost. Therefore, the proposed topology has a good balance between the number of components and the voltage stress. In addition, the proposed topology has the ability to extend. Through the module extension, the proposed topology can output more levels and further reduce the cost of the inverter.

#### B Topology Comparison with Outputting 2N+1 Level

In this section, the proposed topology is compared with the topologies in [30]-[35]. When the inverter output level is 2N+1, the parameter calculation equations of the proposed topology and the topologies in [30]-[35] are summarized in Table IV. For the convenience of analysis, the topologies in the comparison are all based on the switched capacitor principle and can be extended. It can be seen from Table IV that the H-bridge is not needed when the proposed topology outputs bipolar levels. Therefore, the PIV of the semiconductors keep at a reasonable value when the proposed inverter outputs more levels.

Fig. 6 depicts the comparison of the proposed topology with other single-input switched capacitor multilevel topologies. Fig. 6(a) shows that the proposed topology uses the least number of components (including the number of switches, diodes, and capacitors) at the output level of 2N+1. The comparison results of capacitance energy efficiency are given in Fig. 6(b). It can be seen that the proposed topology has the maximum capacitance energy efficiency, and with the extension of the topology, the capacitance energy efficiency also increases. The larger capacitors to achieve higher boost gains and more levels, and further reducing the number of components used.

Fig. 6(c) and Fig. 6(d) are the comparison results of PIV and TSV for semiconductors, respectively. Although the PIV of the proposed topology is larger than the PIV of the topologies in [34] and [35], compared with the topologies in [35], the proposed topology has lower TSV. Furthermore, the TSV of the proposed topology is only one  $V_{dc}$  larger than the topology in [34].

In order to make the comparison of the topology fairer, the cost function *CF* is introduced to analyze the cost of the topology. The comparative analysis of the topology is carried out on

the basis of the same output level, therefore, the cost function CF is defined as

$$CF = \left(N_S + N_D + N_C + \alpha \times \frac{\text{TSV}}{V_{\text{dc}}} + \beta \times \frac{\text{PIV}}{V_{\text{dc}}}\right).$$

(38)

Fig. 6(e) and Fig.6(f) are the comparison results with specific gravity coefficients of 1.5 and 0.5, respectively. It can be seen that the proposed topology has the lowest cost in both cases, and the relationship between the voltage stress and the number of components is well balanced. Based on the above discussion, it can be concluded that the proposed topology has high capacitance energy efficiency and can output more levels using fewer components. Moreover, the strategy of H-bridge to realize the output voltage polarity conversion is not used, so that the PIV of the semiconductor can operate at a reasonable level and the topology has a low TSV. In terms of cost comparison, it proves that the proposed topology has better economic efficiency.

#### V SIMULATION AND EXPERIMENTAL RESULTS

#### A Simulation Results

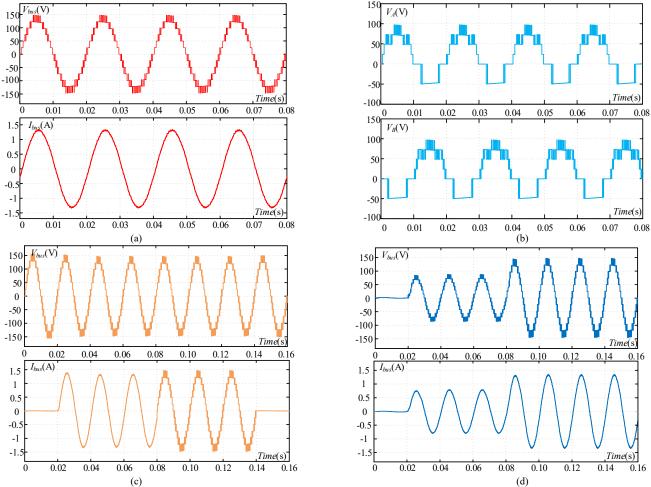

In order to validate the effectiveness of the proposed topology, extensive simulations are carried out on the 13-level inverter model. In the simulation, the input voltage is  $V_{dc}=25V$ , the output load is  $R_L=100\Omega+60$ mH, the modulation wave frequency is  $f_0=50$ Hz, the carrier frequency is  $f_a=2000$ Hz, and the modulation ratio M is 0.9. The simulation waveforms of the output voltage and load current are shown in Fig. 7 (a). It can be seen that the inverter outputs a 13-level voltage with the peak voltage is 150V. The output boost gain is 6, the load current is sinusoidal and lags the output voltage. Fig. 7 (b) shows the output voltage waveform of the inverter half-bridge. The peak voltage of the both half-bridges of the inverter is 100V, and the valley voltage is -50V, which is consistent with the theoretical analysis of the inverter output voltage.

Fig. 6 Comparison between the proposed topology and other SCMLI topologies with outputting 2N+1 level.

Fig. 7(c) shows the simulation waveforms of the voltage and current of the inverter under different loads. The resistive inductive load is set to  $100\Omega$  and 60mH, and the resistive load is set to  $100\Omega$ . It can be seen that the inverter switches from noload to resistive inductive load, and then switches to resistive load after three cycles. During this period, the inverter output voltage waveform is stable, and the current response is fast. Fig. 7(d) shows the current and voltage simulation waveforms when the inverter input voltage changes. The inverter input voltage is switched from zero to 15V, and then the input voltage rises to 25V. The load current presents a sinusoidal waveform and the angle lags behind the voltage.

#### **B** Experimental Results

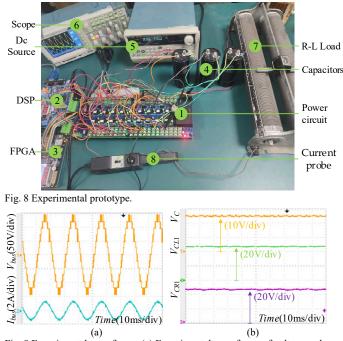

In order to further demonstrate the performance of the inverter, a small 13-level inverter experimental platform is built. The experimental parameters are given in Table V and the experimental prototype is shown in Fig. 8. According to equations (16)-(21), in the case of meeting the voltage ripple and experimental requirements, the minimum capacitance of capacitor *C* is estimated to be  $2111\mu$ F, and the minimum capacitance of capacitors  $C_{L1}$  and  $C_{R1}$  are  $1654\mu$ F. Considering the limitations of

TABLE V Experimental Parameters

| Items                         | Specifications  |  |  |  |  |

|-------------------------------|-----------------|--|--|--|--|

| Input voltage $V_{dc}$        | 15 V or 25 V    |  |  |  |  |

| Capacitor $C, C_{L1}, C_{R1}$ | 2200 μF         |  |  |  |  |

| Load resistor                 | 100 Ω or 200 Ω  |  |  |  |  |

| Load inductor                 | 15 mH           |  |  |  |  |

| Out frequency                 | 50 Hz or 100 Hz |  |  |  |  |

| Carry frequency               | 2000 Hz         |  |  |  |  |

| Power switches                | SPP20N60C3      |  |  |  |  |

| Power diodes                  | TLP250          |  |  |  |  |

the experimental equipment and a certain margin, in this experiment, the capacitor selects the design value of 2200  $\mu$ F.

In this part, the steady-state performance of the 13-level inverter is tested, and the output voltage, load current, and capacitor voltage waveform of the inverter are investigated. In order to check the load-bearing capacity of the inverter under complex operating conditions, several different experiments are designed. For instance, input voltage changes, output frequency changes, load changes, and modulation ratio changes.

Fig. 7 Simulation waveforms. (a) Simulation waveforms of voltage and current, (b) Simulation waveforms of the voltage output from the inverter halfbridge, (c) Simulation waveforms under different loads, (d) Simulation waveform under input voltage variation.

When the input voltage value of the inverter is 25V, the load resistance is 100 $\Omega$ , the load inductance is 15mH, and the modulation ratio *M* is 0.9, the inverter output voltage and load current waveforms are shown in Fig. 9 (a). It can be obtained that the inverter outputs a 13-level step voltage, the peak value of the output voltage is close to 150V, and a boost gain of 6 times is obtained. The experimental results are consistent with the simulation results, verifying the feasibility of the inverter. In addition, the load current is sinusoidal, and the ability of inverter to carry inductive loads is verified. Fig. 9 (b) presents the experimental waveform of the capacitor voltage, where the voltages of the capacitors *C*, *C*<sub>L1</sub> and *C*<sub>R1</sub> fluctuate within the allowable range of ripple, and the capacitor voltage achieves self-balancing.

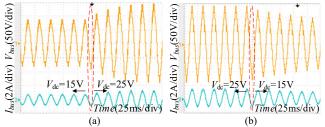

Fig. 10 depicts the waveforms of voltage and current when the input voltage of the inverter changing. In this scenario, the value of the total load is  $R_L$ =100Ω+15mH, the modulation ratio is 0.9 and the output frequency is set as 50Hz. It can be seen that during the process of inverter input voltage change, the number of inverter output levels and boost gain remain unchanged, and the load current varies with the amplitude of the output voltage. The change of input voltage was studied in the dynamic experiment. The corresponding change process is relatively smooth compared with the simulation results, which is caused by the large time constant of the capacitor charging circuit.

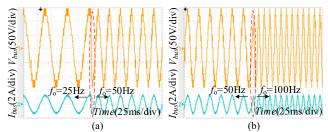

Fig. 11 presents the waveforms of voltage and current as the output frequency changes. In this case, the input voltage of the inverter is 25V, the value of the total load is  $R_L=100\Omega+15$ mH, the modulation ratio is set as 0.9. It can be seen that the amplitude of the output voltage and load current of the inverter remains unchanged when the output frequency changes, and the frequency change responds quickly. Therefore, it can be utilized in the complex conditions with frequency fluctuation.

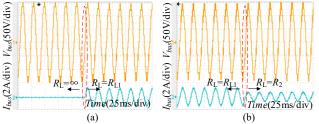

The waveforms of voltage and current under different loads are shown in Fig. 12. In this experiment, the input voltage is 25V, the modulation ratio is set to 0.9 and the frequency is set to 50Hz. In Fig. 12(a), the inverter is switched from no-load to load  $R_{L1}=100\Omega+15$ mH. It can be seen that the output voltage of the inverter remains unchanged and the load current quickly enters a stable state from 0. In Fig. 12 (b), the inverter load  $R_{L1}=100\Omega+15$ mH is switched to the load  $R_2=200\Omega$ . At this time, the load current decreases with the increase of impedance, and the stability of the inverter is excellent.

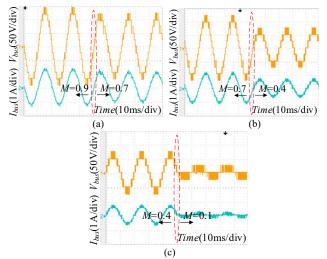

The waveforms of voltage and current under different modulation ratios are shown in Fig. 13. In this situation, the input voltage of the inverter is 25V, the value of the load is  $R_L=100\Omega+15$ mH, and the output frequency is set to 50Hz. As shown in Fig. 13(a)~(c), the output level and output voltage amplitude change with the modulation ratio. In Fig. 13(a), when the modulation ratio M=0.7, the inverter outputs 11 levels; in Fig. 13(b), when the modulation ratio M=0.4, the inverter outputs 7 levels; in Fig. 13(c), when the medium modulation ratio M=0.1, the inverter outputs 3 levels. Based on the above discussions, it can be concluded that the inverter can work at different modulation ratios, different boost requirements can be met, and the inverter load current follows better.

Fig. 9 Experimental waveforms. (a) Experimental waveforms of voltage and current, (b) Experimental waveforms of capacitor voltages.

Fig. 10 Experimental waveforms of voltage and current when the change of input voltage.

Fig. 11 Experimental waveforms of voltage and current when the change of output frequency.

Fig. 12 Experimental waveforms of voltage and current under different loads.

Fig. 13 Experimental waveforms of voltage and current under different modulation ratios.

#### VI. CONCLUSIONS

In this paper, an extended switched capacitor multilevel topology was proposed. The topology uses a single input and its extended structure has the ability to reverse polarity, thus not only the utilization of the H-bridge may be avoided, but also the peak inverse voltage of the semiconductors can be reduced. More importantly, the proposed topology owns a simple extended structure and inherent capacitor voltage self-balancing, which can effectively reduce the utilization of devices and manufacturing costs. To validate the performance of the proposed topology, the voltage ripple and losses of 13-level topology were calculated and analyzed. In addition, a comparative analysis of 13-level inverters is given. The comparison result proves that the proposed topology still has the advantage of reducing cost when outputting a low level. In the comparison of the extended topology, the proposed topology has the advantages of reducing devices, reducing the voltage stress of semiconductors, and reducing the cost of the topology compared with the existing topologies. Finally, the prototype of the 13-level inverter was built to verify the correctness and feasibility of the inverter. The extensive experimental results under various conditions demonstrated the efficacy of the proposed topology.

#### REFERENCES

- Ali J S M, Krishnasamy V. "An assessment of recent multilevel inverter topologies with reduced power electronics components for renewable applications," *Renew Sustain Energy Rev.*, vol. 82, pp. 3379-3399, Nov. 2017.

- [2] Goetz S M, Wang C, Li Z, Murphy D L K, Peterchev A V. "Concept of a distributed photovoltaic multilevel inverter with cascaded double Hbridge topology," *Int. J. Electr. Power Energy Syst.*, vol. 110, pp. 667-678, Mar. 2019.

- [3] Nageswara G, Rao P, Sangameswara, Raju K, Chandra, Sekhar. "Harmonic elimination of cascaded H-bridge multilevel inverter based active power filter controlled by intelligent techniques," *Int. J. Electr. Power Energy Syst.*, vol. 61, pp. 56-63, Oct. 2014.

- [4] Maheshwari R, Munk-Nielsen S, Busquets-Monge S. "Design of neutralpoint voltage controller of a three-level NPC inverter with small DC-link

capacitors," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1861-1871, May. 2013.

- [5] Humayun M, Khan M M, Muhammad A, Xu J, Zhang W. "Evaluation of symmetric flying capacitor multilevel inverter for grid-connected application," *Int. J. Electr. Power Energy Syst.*, vol. 115, pp. 1-17, Feb. 2020.

- [6] Marino C, Pierluigi G, Diego I, Santolo D, Andrea D P. "Extended operating range of PV module-level CHB inverter," *Int. J. Electr. Power Energy Syst.*, vol. 119, Jul. 2020.

- [7] U. Choi, J. Lee and K. Lee. "New modulation strategy to balance the neutral-point voltage for three-level neutral-clamped inverter systems," *IEEE Transactions on Energy Conversion*, vol. 29, no. 1, pp. 91-100, Mar. 2014.

- [8] Liu X, Qiu L, Fang Y, Ma J, Wu W, Peng ZH, et al. "Lyapunov-based f inite control-set model predictive control for nested neutral point-clamp ed converters without weighting factors," *Int. J. Electr. Power Energy S* yst., vol. 121, Oct. 2020.

- [9] Abdel hakim A, Mattarella P, Piazzi G. "Three-phase three-level flying capacitors split-source inverters: analysis and modulation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 6, pp. 4571-4580, Jun. 2017.

- [10] Humayun M, Khan M M, Hassan M U, Zhang W D. "Analysis of hybrid switches symmetric flying capacitor multilevel inverter based STAT-COM," Int. J. Electr. Power Energy Syst., vol. 131, Oct. 2021.

- [11] Rao G N, Raju P S, Sekhar K C, et al. "Harmonic elimination of cascaded H-bridge multilevel inverter based active power filter controlled by intelligent techniques," *Int. J. Electr. Power Energy Syst.*, vol. 61, Apr. 2014.

- [12] Yu Y, Zhang C. "Bifurcation analysis of cascaded H-bridge converter c ontrolled by proportional resonant- ScienceDirect," *Int. J. Electr. Power Energy Syst.*, vol. 125, Feb. 2021.

- [13] Ramkumar S, Kamaraj V, Thamizharasan S, Jeevananthan S. "A new se ries parallel switched multilevel DC-link inverter topology," *Int. J. Elec tr. Power Energy Syst.*, vol. 36, Mar. 2012.

- [14] Das M, Agarwal V. "Novel high-performance stand-alone solar pv system with high-gain high-efficiency DC–DC converter power stages," *IEEE Trans. Ind. Appl.*, vol. 51, no. 6, pp. 4718-4728, Nov. 2015.

- [15] Qi Q, Ghaderi D, Guerrero J M. "Sliding mode controller-based switche d-capacitor-based high DC gain and low voltage stress DC-DC boost co nverter for photovoltaic applications," *Int. J. Electr. Power Energy Syst.*, vol. 125, Feb. 2012.

- [16] Shen J, Jiu H, Wu J, Wu K. "Five-level inverter for renewable power ge neration system," *IEEE Transactions on Energy Conversion*, vol. 28, n o. 2, pp. 257-266, Jun. 2013.

- [17] Liu J, Wu J, Zeng J, Guo H. "A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2939-2947, Apr. 2017.

- [18] Singhneti S, Singh V. "A reduce device count nine level MLI using switched capacitors," 2020 First International Conference on Power, Control and Computing Technologies (ICPC2T), 2020.

- [19] Liu J F, Lin W J, Wu J L, Zeng J. "A novel nine-level quadruple boost inverter with inductive-load ability," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4014-4018, May 2019.

- [20] Sandeep N. "A 13-level switched capacitor-based boosting inverter," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 68, no. 3, pp. 998-1002, Mar. 2021.

- [21] Ye Y, Chen S, Wang X, Cheng W E. "Self-balanced 13-level inverter based on switched-capacitor structure and hybrid PWM algorithm," *IEEE Trans. Ind. Electron.*, vol. 68, no. 6, pp. 4827-4837, Jun. 2021.

- [22] Kim K M, Han J K, Moon G W. "A high step-up switched-capacitor 13level inverter with reduced number of switches," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 2505-2509, Mar. 2021.

- [23] Karama B, Barzegarkhoo R, Abrishamifar A, Samizadeh M. "A switched-capacitor multilevel inverter for high AC power systems with reduced ripple loss using SPWM technique," The 6th Power Electronics, Drive Systems & Technologies Conference (PEDSTC2015), Tehran, 2015.

- [24] Raman S R, Cheng K W E, Ye Y. "Multi-input switched-capacitor multilevel inverter for high-frequency AC power distribution," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5937-5948, Jul. 2018.

- [25] Shalchi Alishah R, Hosseini S H, Babaei E, Sabahi M, Zare A. "Extended high step-up structure for multilevel converter," *IET Power Electron.*,

vol. 9, no. 9, pp. 1894-1902, Mar. 2016.

- [26] Zamiri E, Vosoughi N, Hosseini S H, Barzegarkhoo R, Sabahi M. "A new cascaded switched-capacitor multilevel inverter based on improved series–parallel conversion with less number of components," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3582-3594, Jun. 2016.

- [27] Chen S, Ye Y, Hua T, Wang X. "Self-balanced switched-capacitor multilevel inverter with asymmetric double-wing structure," *Int. J. Electr. Power Energy Syst.*, vol. 133, pp. 1-10, Jun. 2021.

- [28] Hinago Y, Koizumi H. "A switched-capacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878-887, Feb. 2012.

- [29] Ye Y, Cheng K W E, Liu J, Ding K. "A step-up switched-capacitor multilevel inverter with self-voltage balancing," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6672-6680, Dec. 2014.

- [30] Khoun-Jahan H, Shotorbani A M, Abapour M, Zare K, Hosseini S H, Blaabjerg F, et al. "Switched capacitor based cascaded half-bridge multilevel inverter with voltage boosting feature," CPSS Transactions on Power Electronics and Applications, vol. 6, no. 1, pp. 63-73, Mar. 2021.

- [31] Siddique M D, Mekhilef S, Sanjeevikumar P, Memon M A, Kumar C. "Single phase step-up switched-capacitor based multilevel inverter topology with SHEPWM," *IEEE Trans. Ind. Appl.*, vol. 57, no. 3, pp. 3107-3119, Jun. 2020.

- [32] Lee S S, Lee K B. "Switched-capacitor-based modular T-type inverter (SC-MTI)," *IEEE Trans. Ind. Electron.*, vol. 68, no. 7, pp. 5725-5732, Jul. 2020.

- [33] Talooki M F, Rezanejad M, Khosravi R, Samadaei E. "A novel high stepup switched-capacitor multilevel inverter with self-voltage balancing," *IEEE Trans. Power Electron.*, vol. 36, no. 4, pp. 4352-4359, Apr. 2021.

- [34] Taghvaie A, Adabi J, Rezanejad M. "A self-balanced step-up multilevel inverter based on switched-capacitor structure," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 199-209, Jan. 2018.

- [35] Khenar M, Taghvaie A, Adabi J, Rezanejad M. "Multi-level inverter with combined T-type and cross-connected modules," *IET Power Electron.*, vol. 11, no. 8, pp. 1407-1415, Feb. 2018.

- [36] He L, Sun J, Lin Z, Cheng B. "Capacitor-voltage self-balance multilevel inverter with unequal amplitude carrier-based APODPWM" *IEEE Trans. Power Electron.*, vol. 36, no. 12, Jun. 2021.

- [37] Panda K P, Bana P R, Panda G. "A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source," *IEEE Trans. on Circuits and Systems II: Express Briefs*, vol. 67, no. 12, pp. 3192-3196, Dec. 2020.

- [38] Xu Z, Zheng X, Lin T, Yao J, Ioinovici A. "Switched-capacitor multilevel inverter with equal distribution of the capacitors discharging phases," *Chinese J. Electron.*, vol. 6, no. 4, pp. 42-52, Dec. 2020.

- [39] Liu J, Cheng K W E, Ye Y. "A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4219–4230, Aug. 2014.