# Gate bias voltage dependence of Cardiff admittance model in Ka-band GaAs pHEMTs

Alexander Baddeley, Ehsan Azad, Roberto Quaglia, James Bell, Paul Tasker

Centre for High Frequency Engineering

Cardiff University

Queen's Buildings, CF24 3AA, Cardiff, UK

Email: baddeleya@cardiff.ac.uk

Abstract—This paper analyzes the dependence vs. gate bias voltage of the coefficients of the Cardiff model in the admittance form. The load-pull measurement data used to extract the model, inclusive of input power sweep, is taken on a GaAs pseudomorphic high electron mobility transistor (pHEMT) at the frequency of 36 GHz. The gate bias is swept in class C and in class AB and a different set of coefficients is extracted at each bias point.

It is observed that the model coefficients can be fitted vs. bias using a linear function within the class C and class AB ranges. This allows to predict the model coefficients within a range of bias voltages with load-pull measurements at only a few bias points, significantly reducing the measurement effort. Using the predicted coefficients, the model shows a global error lower than -31 dB for the DC and fundamental output current.

#### I. INTRODUCTION

The use of millimeter-wave frequencies is gaining traction in a number of applications, ranging from ground to satellite communications, radar, and imaging, thanks to the good availability of bandwidth and the possibility to miniaturize circuits and antennas. The power amplifier (PA) remains the most critical component in the transmitter, heavily affecting the quality of the transmitted signal and the power consumption.

Advanced PA architectures, such as the Doherty PA [1], can be used to improve the performance for specific applications. However, they require a significant effort in the design that must rely on accurate device models that can predict the response over a range of operating conditions, especially bias voltage.

State function models, such as the Angelov model [2], can achieve great accuracy and are extremely versatile, but extracting them is a complex and lengthy operation, involving several characterization steps and a final validation by means of load-pull measurements. Alternatively, load-pull measurement results can be used directly in the design phase, but this is not trivial when designing advanced PA architectures. As an alternative bridging the two options, behavioural models can directly represent measured data in a simulator, allowing to simulate advanced PA architectures [3], and leading to a quicker turn-around between device samples availability and design compared to more complete models. An example of a behavioural model is the Cardiff model [4], which is based upon rigorous mathematical formulation supported by mixing theory.

Being a behavioural model, the Cardiff model requires the measurement domain to cover the possible application domain. Therefore, the model must be extracted on measurements at different gate bias voltages to ensure a valid model when designing advanced PAs. Finding a way to minimize the number of required measurements is therefore important in order to accelerate the model extraction procedure. The dependence of the Cardiff model vs. gate bias has been presented in [5], and parameters' fitting vs. gate bias was adopted to reduce the number of measurements needed. In this work, we apply a similar concept to the admittance form of the Cardiff model, i.e. based on voltage and current rather than power waves. The use of the admittance model is an important step forward since it is a preferred form of the model for having a closer link to the device physics, allowing in future to perform frequency and size scaling in a more accurate way than with a power wave-based model [6].

### II. MODEL

The Cardiff model is used in its admittance form with an order of 5 [7], expressing the output fundamental current as:

$$I_{21} = \underline{/V_{11}} \sum_{t=0}^{1} \sum_{r=0}^{1} \sum_{n=n_{min}}^{n_{max}} L_{2,1,x,m,n} |V_{11}|^{x} |V_{21}|^{m} Q_{21}^{n} \quad (1)$$

and the DC current as:

$$I_{20} = \sum_{t=0}^{1} \sum_{r=0}^{1} \sum_{n=n_{min}}^{n_{max}} L_{2,0,x,m,n} |V_{11}|^{x} |V_{21}|^{m} Q_{21}^{n}$$

(2)

where  $V_{11}$  is the fundamental input voltage,  $V_{21}$  is the fundamental output voltage, and  $Q_{21}$  is a unitary phasor with phase as the difference between output and input voltage. The coefficients m and x are calculated as:

$$\begin{cases}

m = |n| + 2r \\

x = |h - n| + 2t

\end{cases}$$

(3)

with h=1 for fundamental and h=0 for DC. The range of n is:

$$\begin{cases}

n_{\min} = -(mix - t - r) \\

n_{\max} = h + (mix - t - r)

\end{cases}$$

(4)

where  $mix = \lfloor \frac{5-h}{2} \rfloor$ . A model, i.e., a set of L coefficients (16 for  $I_{21}$  and 12 for  $I_{20}$ ), can be extracted for each bias point at which the load-pull measurements have been performed, using

a least-mean square algorithm since the model is linear in its parameters. The insertion of the input voltage in the model is due to the impossibility of performing a "voltage pull" on high frequency devices that would give a constant input voltage when sweeping the output voltage. Therefore, as explained in detail in [6], including the input voltage in the model and performing the load-pull characterization over a few dBs of input power solves this issue providing a sufficient variation of input voltage for the model to be fitted.

#### III. LOAD-PULL MEASUREMENTS

An active open-loop load-pull system was used for the measurements presented in this paper, see picture in Fig. 1.

Fig. 1. Active open-loop load-pull measurement set-up

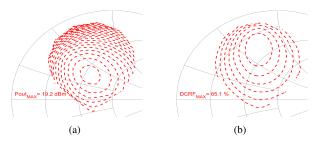

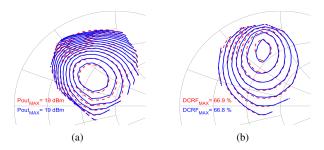

Fig. 2. Power (a) and DCRF (b) measured contours at  $V_{\rm GG}$ =-0.4 V (class AB). 0.25 dBm and 5 % contours, respectively. Drive power of 15.6 dBm.

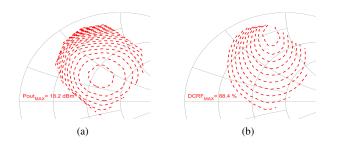

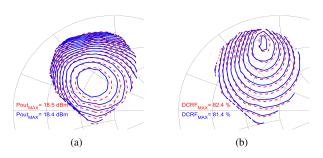

Fig. 3. Power (a) and DCRF (b) measured contours at  $V_{\rm GG}$ =-1.25 V (class C). 0.25 dBm and 5 % contours, respectively. Drive power of 17.7 dBm.

The device under test was placed on a probe station, and the measurement process driven by the Mesuro ALPS software, using the receivers and sources of a Rohde & Schwarz ZVA67 vector network analyzer. The driver and load-pull PAs are the RFLUPA28G42GA from RF-LAMBDA.

The load-pull measurements were conducted on a GaAs  $6x25\,\mu m$  pHEMT fabricated with the Qorvo QPHT09 process, at the frequency of  $36\,GHz$  and at the drain bias voltage of  $3.5\,V$ . The gate bias voltage was swept between  $-0.65\,V$  and  $-0.4\,V$ , with a step of  $50\,mV$ , for the class AB range, and between  $-1.25\,V$  and  $-1.0\,V$ , with a step of  $50\,mV$ , for the class C range. The power drive is swept on a  $6\,dB$  and  $3\,dB$  range in class AB and class C, respectively, and pushed to around  $1.5-2\,dB$  compression.

Fig. 2 and Fig. 3 show the measured output power and efficiency contours at  $V_{\rm GG}$ =-0.4 V and  $V_{\rm GG}$ =-1.25 V, respectively.

#### IV. FITTING OF COEFFICIENTS VS. BIAS POINT

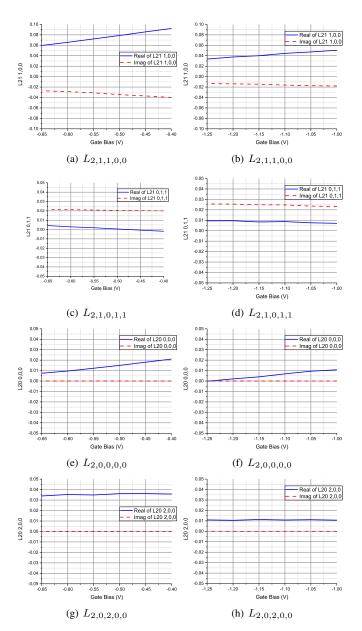

The extracted model coefficients can be plotted vs.  $V_{\rm GG}$ , and they all result to be very close to a linear relationship in both the class AB and C ranges. Fig. 4 shows some of the low order coefficients. For example,  $L_{2,1,1,0,0}$  represents the trans-admittance between input voltage and output current, and its real part is related to the trans-conductance of the device. Therefore, it makes sense for it to be increasing with bias voltage in both the class AB and class C ranges. On the other hand, its imaginary part is expected to be less dependent on the gate bias voltage.  $L_{2,1,0,1,1}$  is related to the output admittance of the device, and also shows only a loose dependence on gate voltage.

Having identified a linear trend vs. bias for the model coefficients, we can reduce drastically the number of bias points measured, and determine the coefficients at non-measured bias-points using a linear function fitting the measured points, that is in general expressed as:

$$\begin{cases}

L_{2,1,x,m,n}(V_{GG}) = m_{1,x,m,n}V_{GG} + q_{1,x,m,n} \\

L_{2,0,x,m,n}(V_{GG}) = m_{0,x,m,n}V_{GG} + q_{0,x,m,n}

\end{cases} (5)$$

where m is the slope coefficient and q is a reference gate voltage. These approximations are valid within defined  $V_{\rm GG}$  ranges.

To prove that this method is effective, we use the coefficients at the extremes of the class AB and C ranges as data points for the model extraction, and determine the values of m and q. Then, we calculate the model at any bias points not used in the model extraction using (5) and validate it against the measurements at that bias point. For class AB, we use the measurements at  $V_{\rm GG}$ = $-0.65\,\rm V$  and  $V_{\rm GG}$ = $-0.4\,\rm V$  for the model extraction, while for class C we use  $V_{\rm GG}$ = $-1.25\,\rm V$  and  $V_{\rm GG}$ = $-1\,\rm V$ .

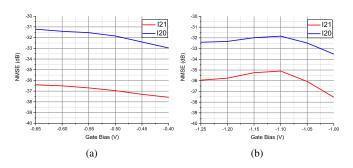

The validation is performed at all the other points measured, and the resulting normalised mean square error (NMSE) for fundamental and DC output current is reported in Fig. 5.

Fig. 6 and Fig. 7 show the measured vs. modelled output power and efficiency contours for  $V_{\rm GG}$ = $-0.5\,\rm V$  and  $V_{\rm GG}$ = $-1.1\,\rm V$ , respectively. The good agreement shown is related to the very low NMSE obtained when modelling the output DC and fundamental currents. It is important to remark that the measured data at these bias points was not used to extract the models, hence this is a proper validation of the model accuracy.

Fig. 4. Some of the extracted coefficients vs.  $V_{\rm GG}$  in the class AB (left column) and class C (right column) ranges.

Fig. 5. Model accuracy in terms of NMSE vs. gate bias voltage, for the class AB model (a) and the class C model (b). The model has been extracted at the extremes of the voltage ranges only, and the models within the ranges are extracted by linearly fitting the coefficients.

Fig. 6. Power (a) and DCRF (b) contour comparison between modelled (blue solid) and measured (red dashed) at  $V_{\rm GG}$ =-0.5 V. 0.25 dBm and 5% contours, respectively. Drive power of 15.6 dBm.

Fig. 7. Power (a) and DCRF (b) contour comparison between modelled (blue solid) and measured (red dashed) at  $V_{\rm GG}$ =-1.1 V. 0.25 dBm and 5% contours, respectively. Drive power of 17.7 dBm.

#### V. CONCLUSION

The paper has shown that the Cardiff admittance model coefficients for a millimetre-wave GaAs pHEMT can be linearly interpolated vs. gate bias voltage within class AB and class C ranges. This opens the possibility of applying frequency and periphery scaling. More work will be required to identify a method to extend the admittance model across class AB and C ranges and a larger input drive dynamic range.

# ACKNOWLEDGMENT

The authors would like to thank Qorvo Inc. for providing the transistor samples.

## REFERENCES

- [1] V. Camarchia et al., "The Doherty Power Amplifier: Review of Recent Solutions and Trends," *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 2, pp. 559-571, Feb. 2015.

- [2] I. Angelov et al., "A new empirical nonlinear model for HEMT and MES-FET devices," *IEEE Transactions on Microwave Theory and Techniques*, vol. 40, no. 12, pp. 2258-2266, Dec. 1992.

- [3] J. Louro et al., "New Transistor Behavioral Model Formulation Suitable for Doherty PA Design,", *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 4, pp. 2138-2147, April 2021.

- [4] H. Qi et al., "Nonlinear Data Utilization: From Direct Data Lookup to Behavioral Modeling," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 6, pp. 1425-1432, June 2009.

- [5] E. M. Azad et al., "Gate Bias Incorporation into Cardiff Behavioural Modelling Formulation," 2020 IEEE/MTT-S International Microwave Symposium (IMS), 2020, pp. 420-423.

- [6] M. R. Moure et al., "Direct extraction of an admittance domain behavioral model from large-signal load-pull measurements," 2017 IEEE MTT-S International Microwave Symposium (IMS), 2017, pp. 1057-1060.

- [7] M. R. Moure et al., "A Systematic Investigation of Admittance Domain Behavioral Model Complexity Requirements," 2018 IEEE MTT-S Latin America Microwave Conference (LAMC 2018), 2018, pp. 1-4.