# GaN-based Single-phase Differential PV Inverters

Rajesh Rajamony

Department of Engineering

Cardiff University

This dissertation is submitted for the degree of

Doctor of Philosophy

2021

#### Acknowledgements

I am deeply thankful to Almighty God for His amazing grace and blessings, which have kept me from the beginning of my life until now.

I would like to express my gratitude to my supervisors Dr. Wenlong Ming and Prof. Nick Jenkins for their time, guidance, and continuous support throughout the duration of my PhD studies. Special thanks to Dr. Sheng Wang for his considerable help during the later stages of my research.

I would like to acknowledge the financial support received through the studentship from the School of Engineering, Cardiff University. I also acknowledge the funding received from SRS Works Ltd.

I am thankful for the opportunity to work in the Knowledge Transfer Partnership (KTP) project with SRS Works Ltd. It was a great pleasure and an invaluable experience for my career to work with the academic and industrial partners of the project. I also acknowledge the funding received through KTP during my candidacy.

I would like to acknowledge all of the help that I received from Dr. Karolina Rucinska during the writing stages of the research. I would like to thank all members of the Smart Grid research group, the Power Electronics/HVDC research group, and the CIREGS group at Cardiff University for their engaging discussions and suggestions regarding my research.

Finally, I would like to acknowledge the support of my family, especially my parents love and prayers.

#### **Abstract**

Differential PV inverters have the benefits of second-order ripple elimination and leakage current suppression. Therefore, the need for additional components such as switch, inductor, capacitor, and transformer to achieve the power decoupling function and galvanic isolation can be avoided. In recent years, GaN devices used to improve the performance of differential PV inverters, which have the advantages of high switching frequency, high operating temperature, and high operating voltage. However, using GaN devices cannot guarantee better performance of inverters because the GaN device performance depends on the design parameters, such as switching frequency and operating temperature. To fully utilise the benefits of the GaN device, the design challenges and the complex trade-offs between components associated with inverters need to be addressed. Therefore, this thesis investigates impacts of GaN devices-based single-phase differential PV inverters with the aim to optimise inverter efficiency, power density, and cost using systematic design and control approaches.

In single-phase differential inverters, active power decoupling methods are often aimed to reduce the total capacitance as much as possible, which sacrifices the overall efficiency and volume of the inverter. To address that, a trade-off analysis of all the active and passive components of the GaN-based differential buck inverters is developed through detailed mathematical modelling. Then, a multi-objective optimisation method based on geometric programming is presented to optimise the efficiency and power density. The design method is based on power loss and volume of the inverter by considering the dominant design parameters. As a result, the maximum limit of design trends can be obtained, which gives more freedom to choose the best design.

The aforementioned multi-objective optimisation methods require extensive mathematical models and more system information to find an optimal design. It increases the computational complexity, needs multiple conditions to eliminate unwanted solutions, and requires more time to choose the optimal design. Therefore, an ANN-based multi-objective design method

is developed to improve accuracy and reduce computational burdens. A buck-type differential inverter is used to verify the ANN-based design method in both simulation and experiment.

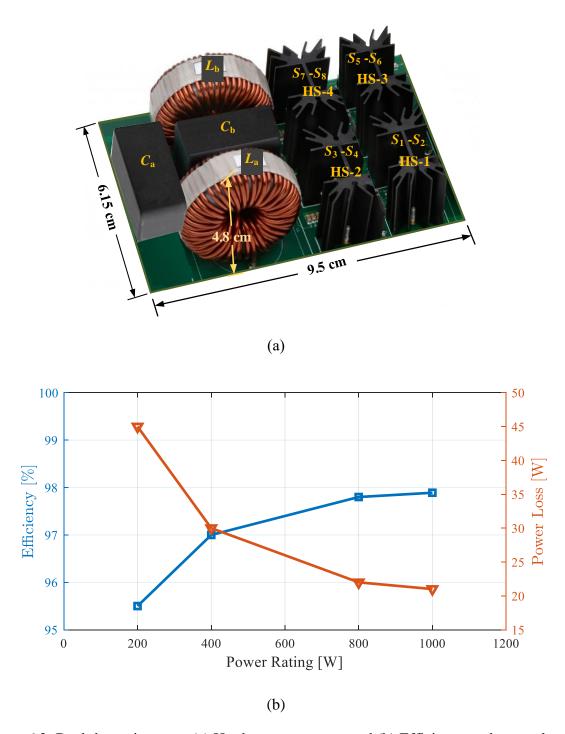

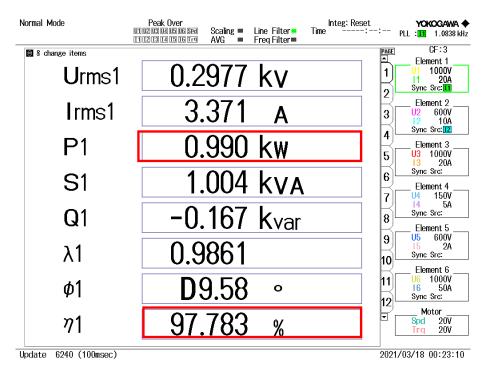

The previous two studies are based on buck-type differential inverters, which need an additional front-end DC-DC converter for solar PV application to meet the wide voltage requirements. This inverter requires an additional hardware controller, reduces efficiency and power density, and increases cost. Single-stage inverters are widely popular in industrial and commercial applications because of their higher efficiency and simple control. A novel single-stage buck-boost inverter topology based on GaN devices is proposed, simulated, and experimentally verified the performances. It has been observed that the maximum efficiency of the prototype is 97.89%, the power density is improved to 3.5kW/dm³ and the components cost of the prototype is £136.16.

## **Contents**

| Conte   | nts  |                                                       | v    |

|---------|------|-------------------------------------------------------|------|

| List of | Figu | res                                                   | ix   |

| List of | Tabl | es                                                    | xiii |

| List of | Abbi | reviations                                            | XV   |

| List of | Sym  | bols                                                  | xvii |

| Chapte  | er 1 | Introduction                                          | 1    |

| 1.1     | Bac  | kground                                               | 1    |

| 1.2     | Res  | search Objectives                                     | 3    |

| 1.3     | The  | esis Outline                                          | 4    |

| 1.4     | Cor  | ntributions of the Research Work                      | 6    |

| 1.5     | Lis  | t of Publications                                     | 7    |

| Chapte  | er 2 | Literature Review                                     | 8    |

| 2.1     | Intr | oduction                                              | 8    |

| 2.2     | Sin  | gle-phase Inverter                                    | 8    |

| 2.      | 2.1  | Grid-connected Controller                             | 10   |

| 2.      | 2.2  | Stand-alone Controller                                | 11   |

| 2.3     | DC   | -link Second-order Ripple                             | 11   |

| 2.      | 3.1  | Effects of Second-order Ripple                        | 12   |

| 2.4     | Pov  | wer Decoupling Methods                                | 13   |

| 2.      | 4.1  | Series Power Decoupling Methods                       | 14   |

| 2.      | 4.2  | Parallel Power Decoupling Methods                     | 15   |

| 2.      | 4.3  | Differential Inverters with Power Decoupling Function | 19   |

| 2.5     | WE   | 3G Devices in Power Electronics                       | 23   |

| 2.      | 5.1  | SiC-based Single-phase Inverters                      | 25   |

| 2.      | 5.2  | GaN-based Single-phase Inverters                      | 25   |

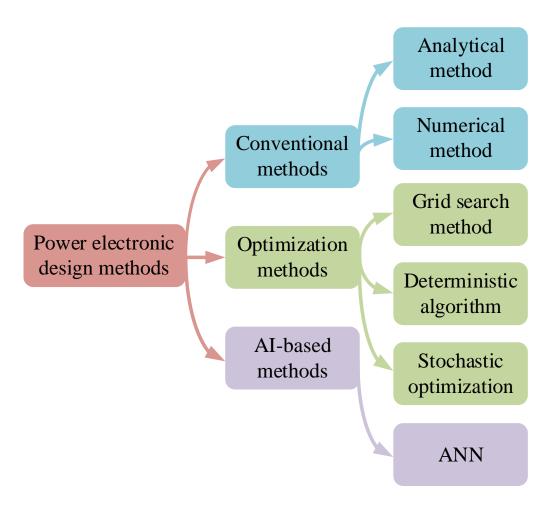

| 2.6     | Des  | sign Methods of Power Electronic Inverters            | 27   |

| 2.      | 6.1  | Conventional Methods                                  | 29   |

| 2.      | 6.2  | Optimisation Methods                                  | 30   |

| 2.      | 6.3  | AI-based Methods                                      | 31   |

| 2.7                 | Sun  | nmary                                                                                       | 32   |

|---------------------|------|---------------------------------------------------------------------------------------------|------|

| Chapter<br>Decoupl  |      | Design and Control of Single-phase Differential Buck Inverters for Po                       |      |

| 3.1                 | Intr | oduction                                                                                    | 33   |

| 3.2                 | Mo   | delling of Power Loss and Volume of the Buck Inverter                                       | 34   |

| 3.2.                | .1   | Power GaN FET                                                                               | 35   |

| 3.2.                | .2   | Output Inductors                                                                            | 37   |

| 3.2.                | .3   | Power Decoupling Capacitors                                                                 | 38   |

| 3.2.                | .4   | Heat sinks                                                                                  | 39   |

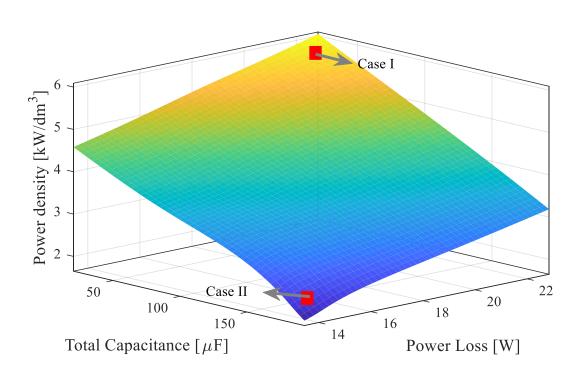

| 3.3                 | Tra  | de-offs Between the Decoupling Capacitance, Power Loss and Power Density                    | 7.39 |

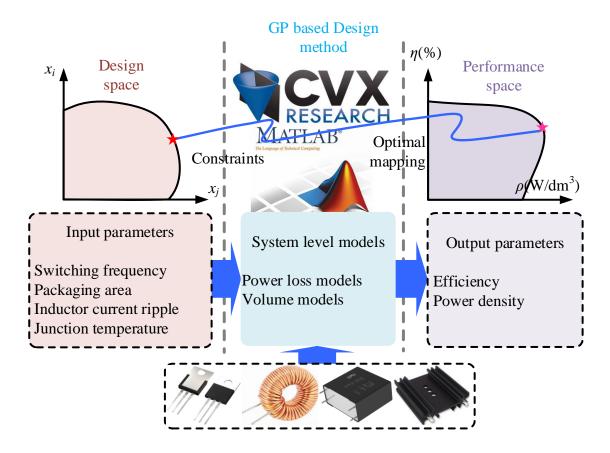

| 3.4                 | Mu   | lti-objective Design Using GP                                                               | 42   |

| 3.5                 | Cor  | ntrol of Differential Buck Inverter                                                         | 44   |

| 3.5.                | .1   | Output Voltage Controller                                                                   | 45   |

| 3.5.                | .2   | Inductor Current Controllers                                                                | 46   |

| 3.5.                | .3   | DC-link Ripple Controller                                                                   | 48   |

| 3.6                 | Res  | ults and Discussions of the GP-based Design                                                 | 49   |

| 3.6.                | .1   | Performance Evaluation                                                                      | 50   |

| 3.6.                | .2   | Experimental Verification                                                                   | 53   |

| 3.7                 | Sun  | nmary                                                                                       | 54   |

| Chapter<br>Single-p |      | A Fast and Accurate Artificial Intelligence-based Design Method Differential Buck Inverters |      |

| 4.1                 | Intr | oduction                                                                                    | 55   |

| 4.2                 | Ove  | erview of ANN-based Design Method                                                           | 56   |

| 4.3                 | Stru | acture of the ANN for the Proposed Design                                                   | 56   |

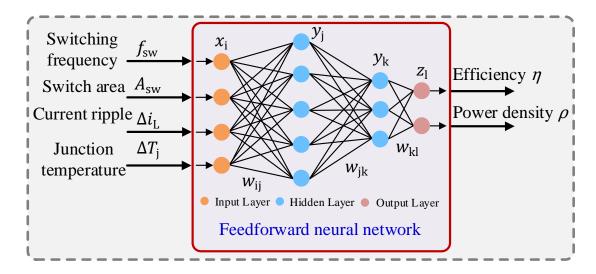

| 4.3.                | .1   | Input Layer                                                                                 | 58   |

| 4.3.                | .2   | Hidden Layer                                                                                | 58   |

| 4.3.                | .3   | Output Layer                                                                                | 59   |

| 4.4                 | Tra  | ining the Network                                                                           | 59   |

| 4.4.                | .1   | Feed-forward Computation                                                                    | 60   |

| 4.4.                | .2   | Back-propagation to the Output Layer                                                        | 60   |

| 4.4.                | .3   | Back-propagation to the Hidden Layer                                                        | 61   |

| 4.4.                | .4   | Updating Weights                                                                            | 61   |

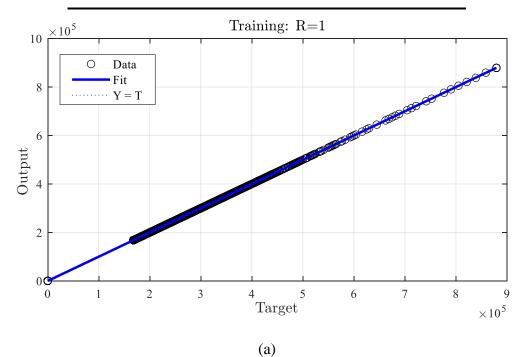

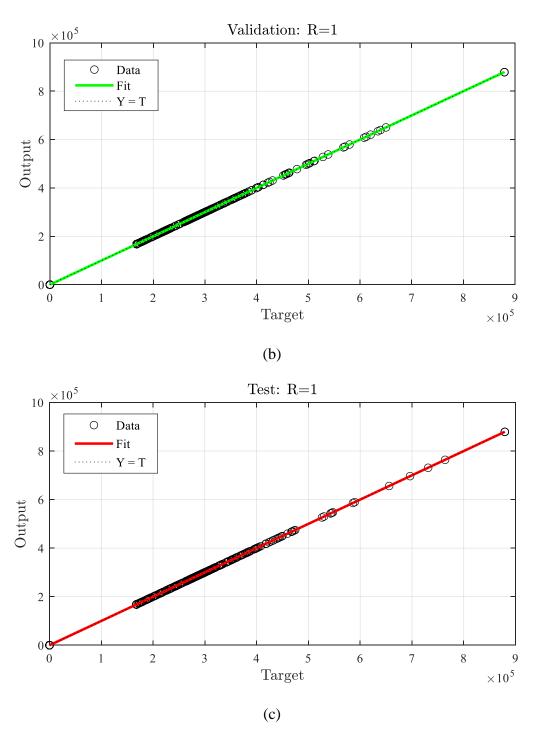

| 4.5                 | Res  | ults and Discussions of the ANN-based Design                                                | 62   |

| 4.5.                | .1   | Performance Evaluation                                                                      | 62   |

| 4.5.                | .2   | Comparison of ANN with Exiting Design Methods                                               | 68   |

| 4.5.                | .3   | Comparison of Computational Time                                                            | 69   |

| 4.5.                | .4   | Experimental Verification                                                                   | 70   |

| 1.5.                |      | 1                                                                                           |      |

| 4.6               | Sui  | nmary                                                                        | 74  |

|-------------------|------|------------------------------------------------------------------------------|-----|

| Chapte<br>boost I |      | A High Efficiency and High-Power Density Design for Single-Sential Inverters | _   |

| 5.1               |      | roduction                                                                    |     |

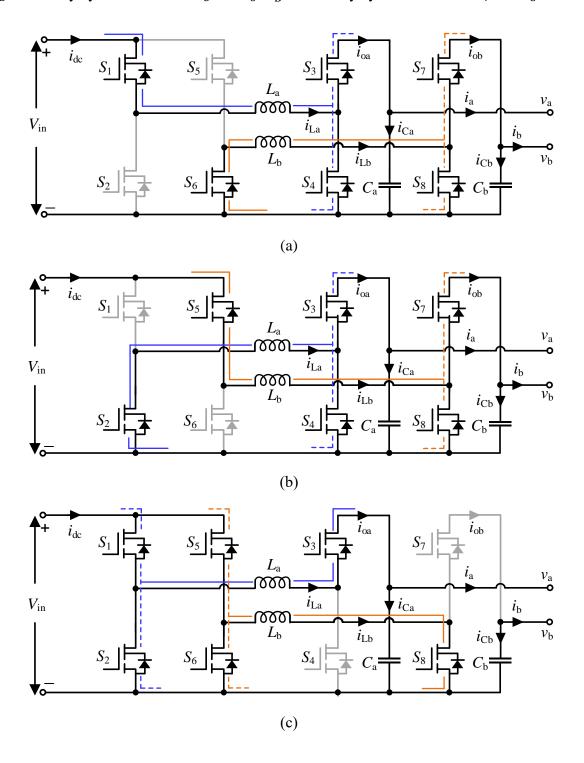

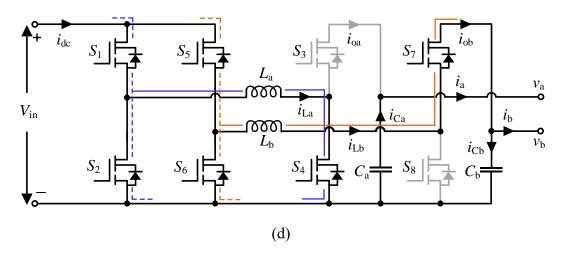

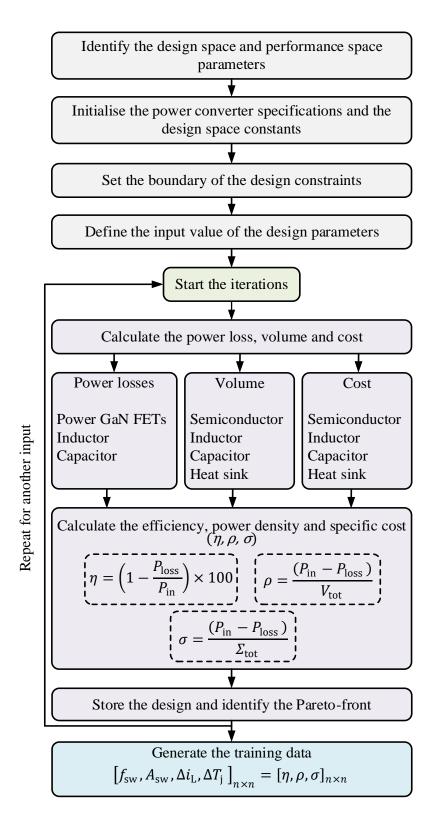

| 5.2               | Ov   | erview of the Proposed Buck-boost Differential Inverter                      | 77  |

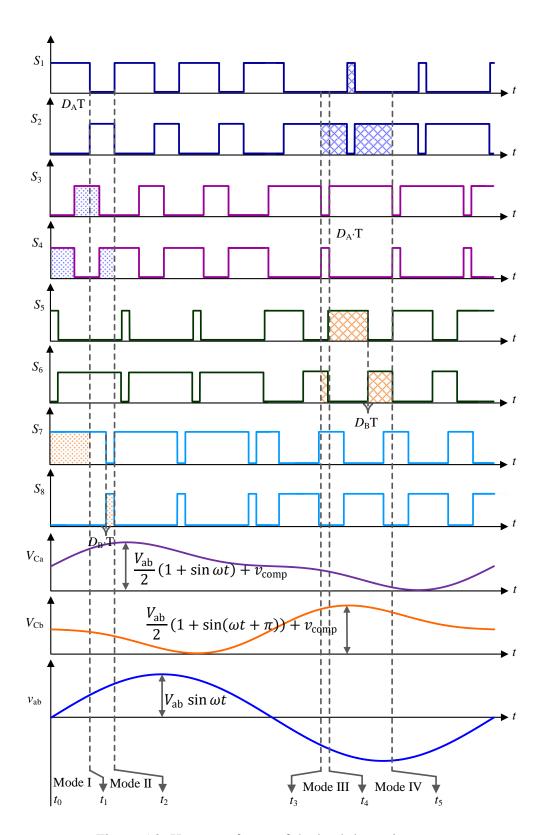

| 5.3               |      | eration of the Buck-boost Inverter                                           |     |

| 5.                | 3.1  | Mode of Operation                                                            | 78  |

| 5.4               | Mo   | odelling of Power Loss, Volume, and Cost of the Buck-boost Inverter          | 82  |

| 5.                | 4.1  | Power GaN FETs                                                               | 82  |

| 5.                | 4.2  | Output Inductors                                                             | 85  |

| 5.                | 4.3  | Power Decoupling Capacitors                                                  | 85  |

| 5.                | 4.4  | Heat Sinks                                                                   | 86  |

| 5.5               | Sel  | ection of Components                                                         | 87  |

| 5                 | 5.1  | Voltage and Current Stress of the GaN FETs                                   | 87  |

| 5                 | 5.2  | Selecting the Inductors                                                      | 88  |

| 5                 | 5.3  | Selecting the Capacitors                                                     | 89  |

| 5.6               | AN   | IN-based Design Approach                                                     | 90  |

| 5.                | 6.1  | Training the Network                                                         | 90  |

| 5.7               | Des  | sign of the Controllers                                                      | 93  |

| 5.8               | Res  | sults and Discussions of Buck-boost Inverter                                 | 94  |

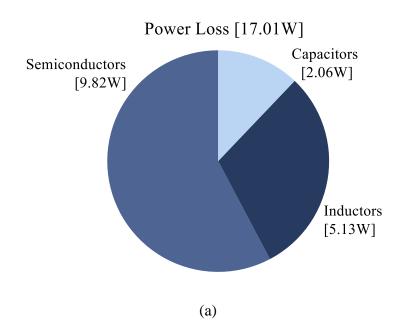

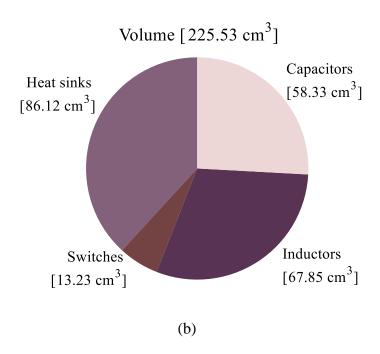

| 5.                | 8.1  | Performance Evaluation                                                       | 94  |

| 5.                | 8.2  | Simulation Verifications                                                     | 100 |

| 5.9               | Sui  | nmary                                                                        | 103 |

| Chapte            | er 6 | <b>Experimental Verifications of Buck-boost Differential Inverters.</b>      | 105 |

| 6.1               | Inti | roduction                                                                    | 105 |

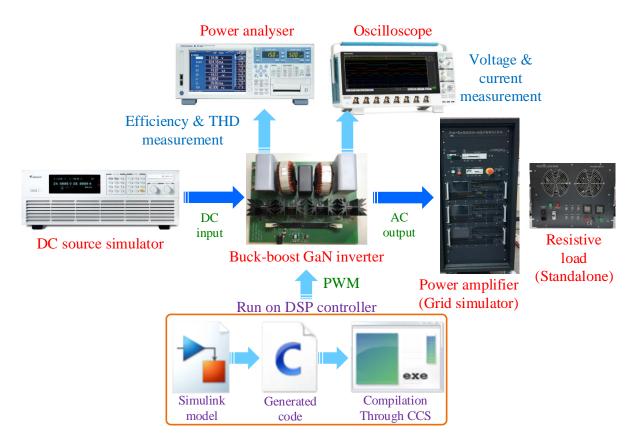

| 6.2               | Ov   | erview of Experimental Systems                                               | 105 |

| 6.3               | Exp  | perimental Verification of Stand-alone Systems                               | 107 |

| 6.4               | Exp  | perimental Verification of Grid-connected Systems                            | 111 |

| 6.5               | Top  | pology Comparison                                                            | 116 |

| 6.6               | Sui  | nmary                                                                        | 117 |

| Chapte            | er 7 | Conclusion and Future Work                                                   | 119 |

| 7.1               | Inti | roduction                                                                    | 119 |

| 7.                | 1.1  | Design and Control of Single-phase Differential Buck Inverters               | 119 |

| 7.                | 1.2  | Fast and Accurate Design of Single-phase Inverters                           | 120 |

| 7.                | 1.3  | High-efficiency and High-power Density Design of PV Inverters                | 121 |

| 7.2               | Fut  | ure Work                                                                     | 121 |

| Refere            | nces |                                                                              | 123 |

| Append | dix A GaN FETs Data                                  | A-1 |

|--------|------------------------------------------------------|-----|

| Append | dix B Buck-boost Inverter Power Decoupling Method    | B-1 |

| B.1    | Second-order Ripple Compensation Voltage Calculation | B-1 |

## **List of Figures**

| Figure 1.1: Contribution of renewable energy sources to electricity generated                                  | 2    |

|----------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2: Installed micro-generation capacity.                                                               | 2    |

| Figure 2.1: Conventional single-phase inverter: (a) Topology, and (b) Control scheme                           | 9    |

| Figure 2.2: Concepts of power decoupling methods.                                                              | 13   |

| Figure 2.4: Single-phase inverter with series power decupling.                                                 | 15   |

| Figure 2.5: Single-phase inverter with parallel power decupling.                                               | 16   |

| Figure 2.6: (a) Concepts of power decoupling method in differential inverters, and (b) To of DC-DC converters. |      |

| Figure 2.7: Comparison of Si, SiC and GaN semiconductors properties.                                           | 24   |

| Figure 2.8: Trade-off between the performance parameters.                                                      | 28   |

| Figure 2.9: Design method of power electronic converters.                                                      | 29   |

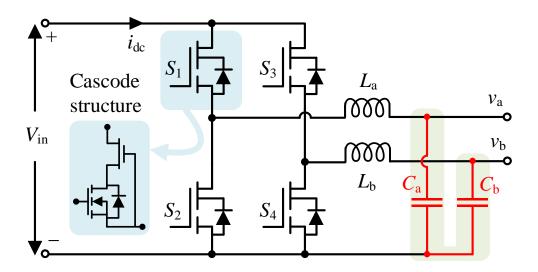

| Figure 3.1: Single-phase differential buck inverter with power decoupling function                             | 34   |

| Figure 3.2: Relationship between total capacitance vs. inverter power loss vs. power den                       | •    |

| Figure 3.3: Overview of multi-objective design using GP-based design method                                    | 44   |

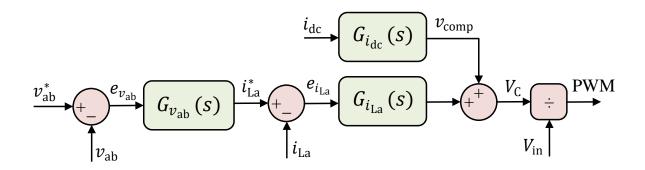

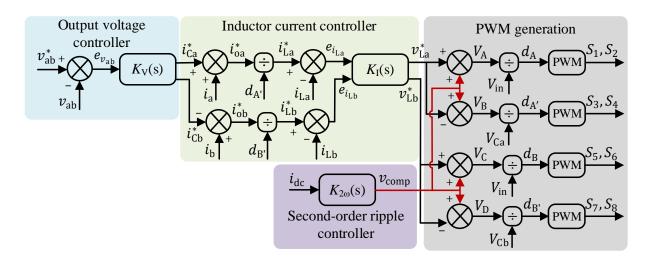

| Figure 3.4: Control scheme of the inverter.                                                                    | 45   |

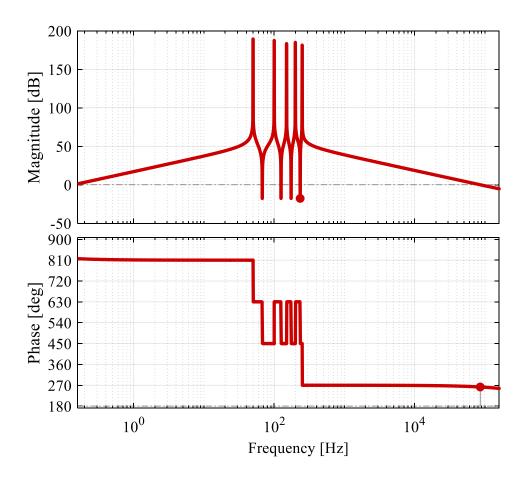

| Figure 3.5: Bode diagram of the open loop linearised system <i>ev</i> ab to <i>v</i> ab                        | 46   |

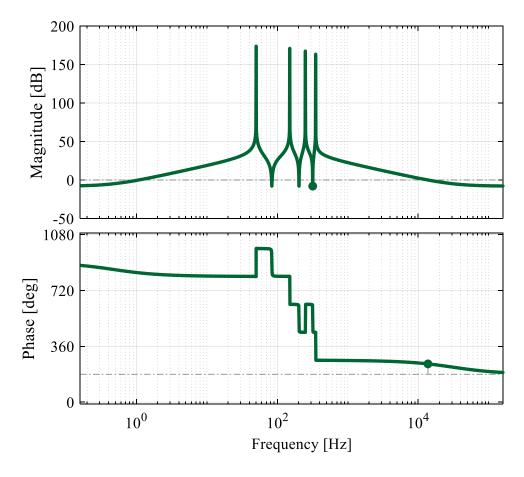

| Figure 3.6: Bode diagram of the open loop linearised system <i>ei</i> La to <i>i</i> La                        | 47   |

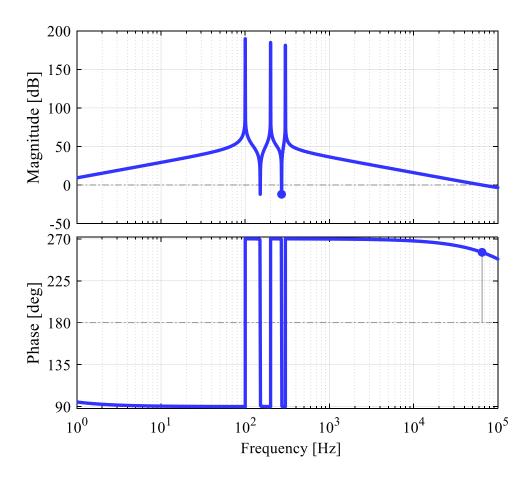

| Figure 3.7: Bode diagram of the open loop linearised system <i>ei</i> dc to <i>i</i> dc                        | 48   |

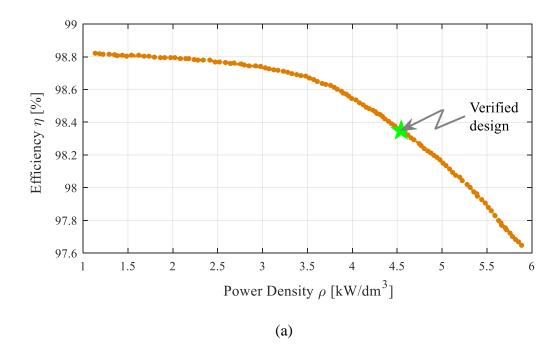

| Figure 3.8: Efficiency vs. Power density: (a) Geometric program, and (b) Numerical model.                      |      |

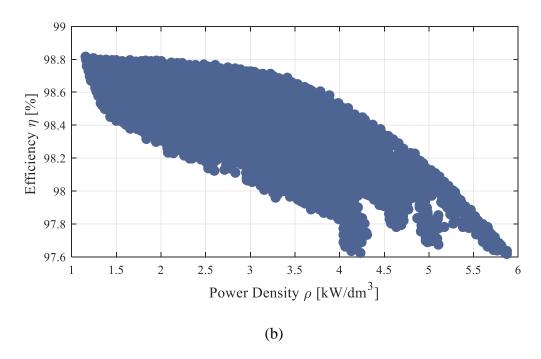

| Figure 3.9: Results of GP: (a) Power loss, and (b) Volume.                                                     |      |

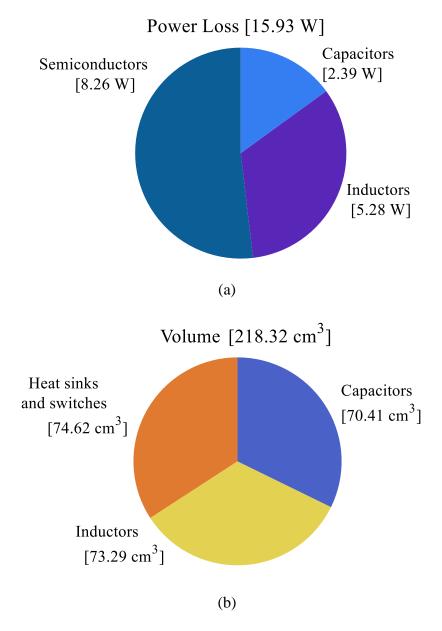

| Figure 3.10: Differential buck inverter: (a) Hardware prototype, and (b) Efficiency and ploss.                 | ower |

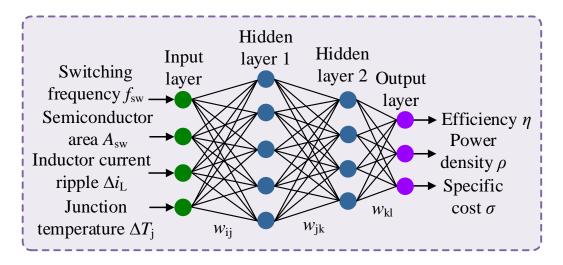

| Figure 4.1: An overview of ANN for proposed design method.                                                     | 57   |

| Figure 4.2: Structure of the ANN for the proposed design approach                                              | 58   |

| Figure 4.3: Regression of the network: (a) Training (b) Validation and (c) Testing                             | 64   |

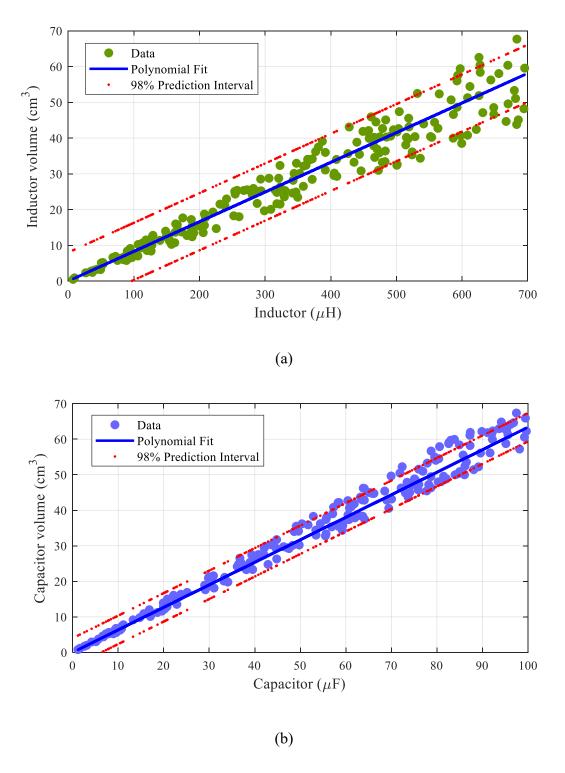

| Figure 4.4: Box volume of: (a) Inductor and (b) Capacitor.                                                     | 65   |

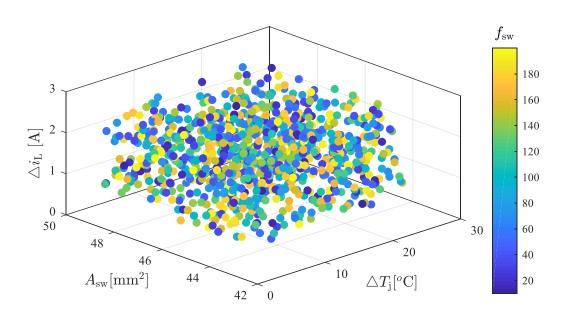

| Figure 4.5: Input datasets were used to train, validate, and test the neural network                           | 67   |

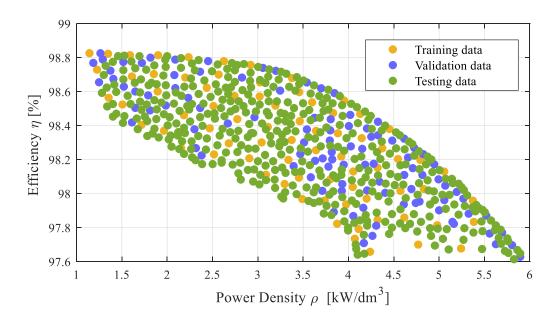

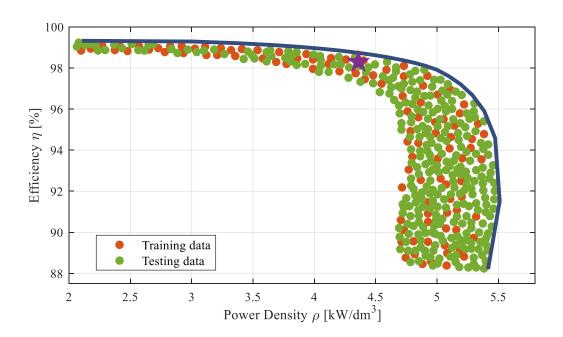

| Figure 4.6: Efficiency vs. Power density of the ANN-based design approach                                      | 67   |

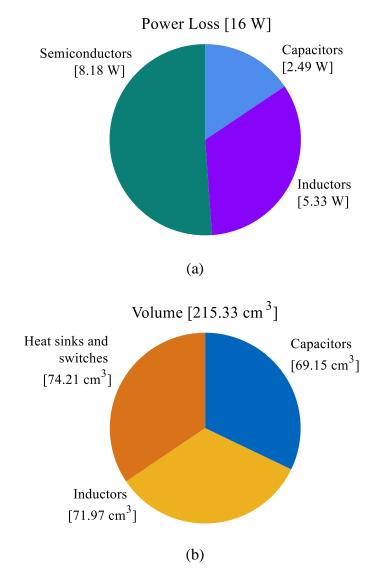

| Figure 4.7: Results of ANN: (a) Power loss, and (b) Volume                                                                                                                                                                                                  |

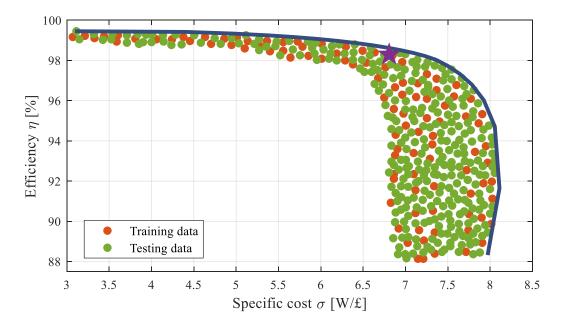

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

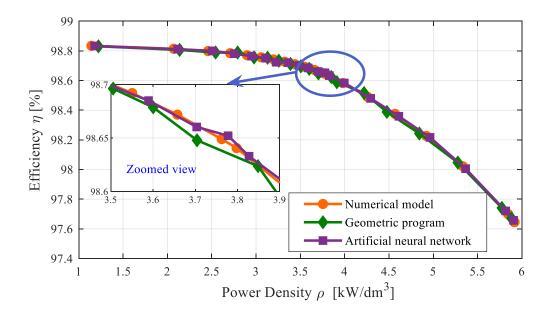

| Figure 4.8: Comparison of performance boundary against different methods69                                                                                                                                                                                  |

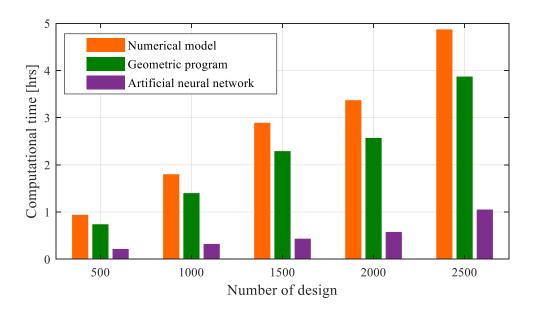

| Figure 4.9: Comparison of computational time against different methods                                                                                                                                                                                      |

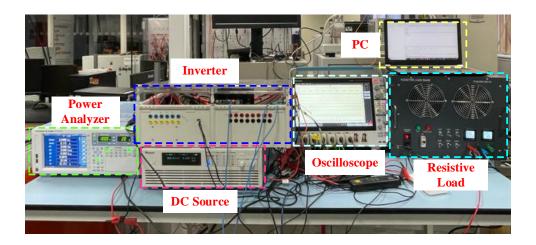

| Figure 4.10: Experimental setup of a differential buck inverter                                                                                                                                                                                             |

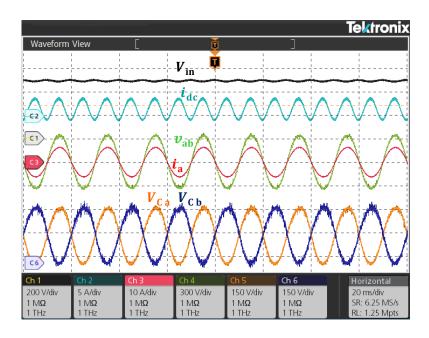

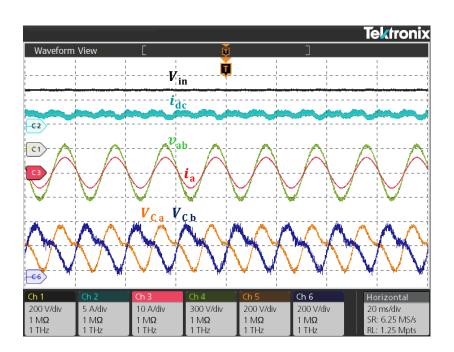

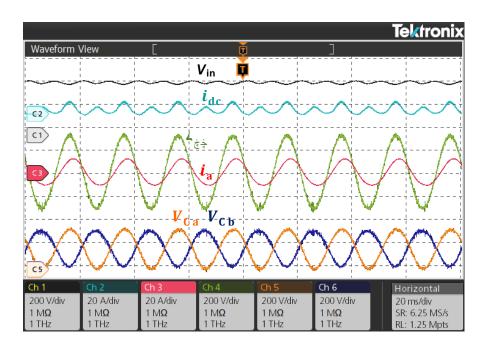

| Figure 4.11: Steady-state waveforms at 1kW without a second-order ripple controller ( $V_{in}$ : 200V/div, $i_{dc}$ : 5A/div $i_a$ : 10A/div, $v_{ab}$ : 300V/div, $V_{ca}$ , $V_{cb}$ : 150V/div)71                                                        |

| Figure 4.12: Steady-state waveforms at 1kW with second-order ripple controller ( $V_{in}$ : 200V/div, $i_{dc}$ : 5A/div $i_a$ : 10A/div, $v_{ab}$ : 300V/div, $V_{ca}$ , $V_{cb}$ : 200V/div)                                                               |

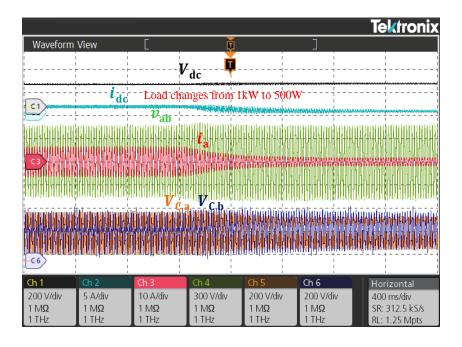

| Figure 4.13: Experimental results when the load changes from 1kW to 500W ( $V_{in}$ : 200V/div, $i_{dc}$ : 5A/div $i_a$ : 10A/div, $v_{ab}$ : 300V/div, $V_{ca}$ , $V_{cb}$ : 200V/div)                                                                     |

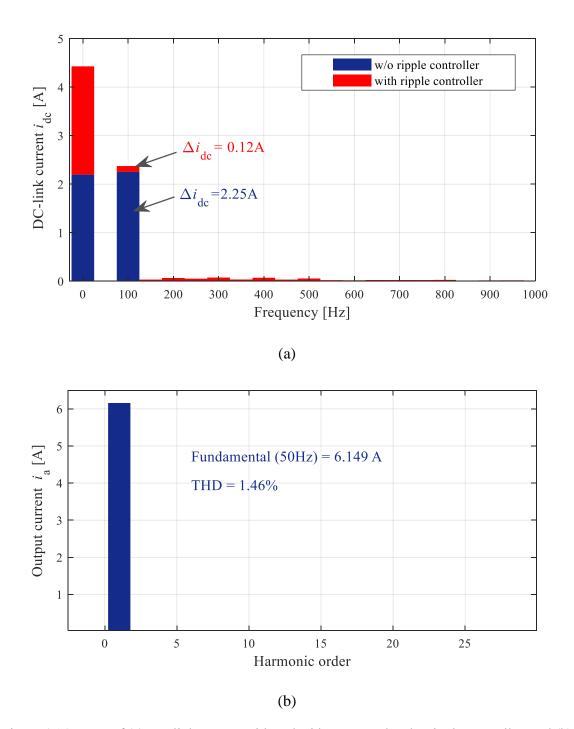

| Figure 4.14: FFTs of (a) DC-link current with and without second-order ripple controller, and (b) Output current                                                                                                                                            |

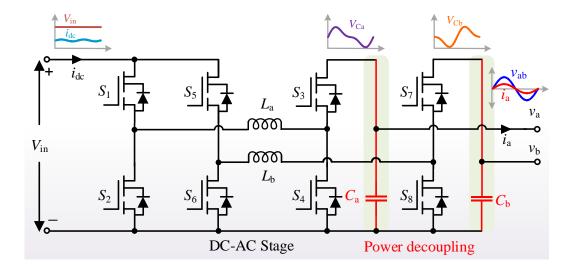

| Figure 5.1: Single stage buck-boost inverter topology                                                                                                                                                                                                       |

| Figure 5.2: Key waveforms of the buck-boost inverter                                                                                                                                                                                                        |

| Figure 5.3: Mode of operation of the inverter: (a) Mode I, (b) Mode II, (c) Mode III, (d) and Mode IV                                                                                                                                                       |

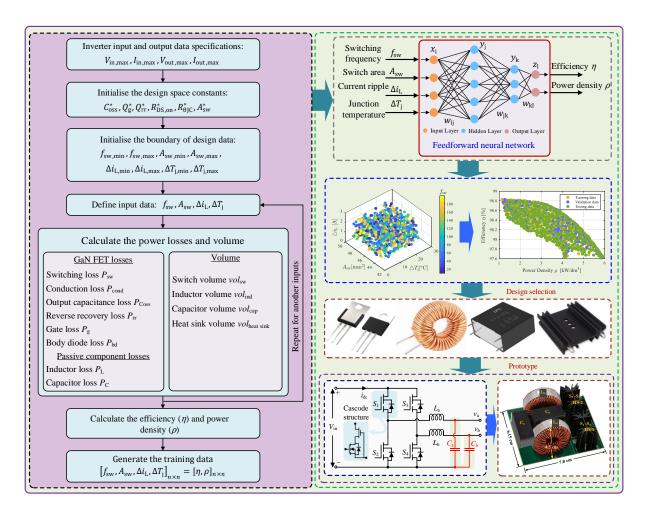

| Figure 5.4: Flow diagram of the proposed design approach                                                                                                                                                                                                    |

| Figure 5.5: Structure of the ANN for the proposed design approach92                                                                                                                                                                                         |

| Figure 5.6: Control diagram of the buck-boost inverter                                                                                                                                                                                                      |

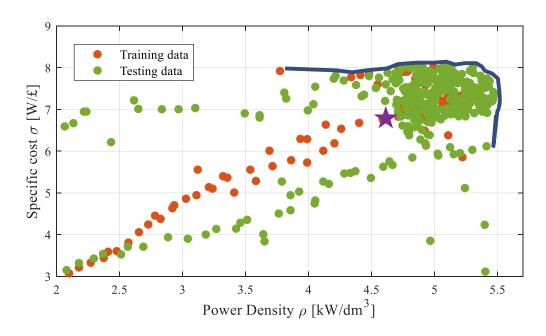

| Figure 5.7: Efficiency vs. Power density of the buck-boost inverter96                                                                                                                                                                                       |

| Figure 5.8: Efficiency vs. Specific cost of the buck-boost inverter96                                                                                                                                                                                       |

| Figure 5.9: Specific cost vs. Power density of the buck-boost inverter97                                                                                                                                                                                    |

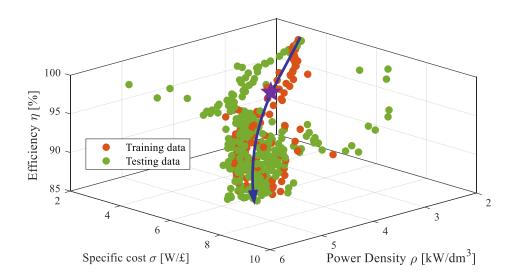

| Figure 5.10: Efficiency vs. Specific cost vs. Power density of the buck-boost inverter98                                                                                                                                                                    |

| Figure 5.12: Simulation results of the buck-boost inverter without second-order ripple controller.                                                                                                                                                          |

| Figure 5.13: Simulation results of the buck-boost inverter with second-order ripple controller.                                                                                                                                                             |

| Figure 5.14: Comparison of the second-order ripple on the DC-link current103                                                                                                                                                                                |

| Figure 6.1: Overview of the experimental systems                                                                                                                                                                                                            |

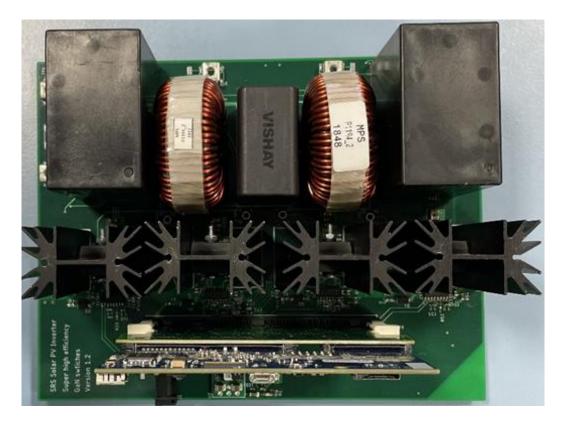

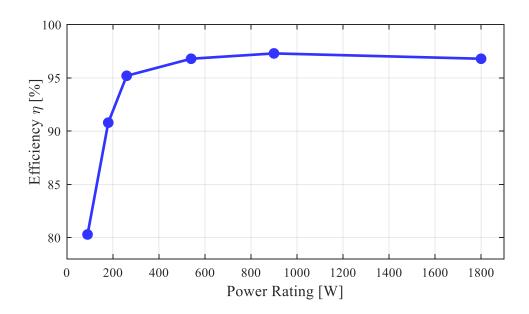

| Figure 6.2: Buck-boost inverter: (a) Hardware prototype, and (b) Efficiency and power loss.                                                                                                                                                                 |

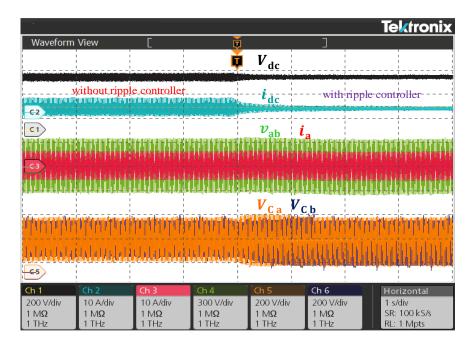

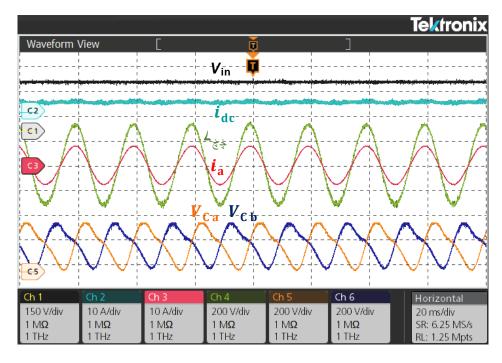

| Figure 6.3: Experimental results of the standalone system at 1kW before and after enabling second-order ripple controller ( $V_{\rm in}$ : 200V/div, $i_{\rm dc}$ , $i_{\rm a}$ : 10A/div, $v_{\rm ab}$ : 300V/div, $V_{\rm ca}$ , $V_{\rm cb}$ : 200V/div) |

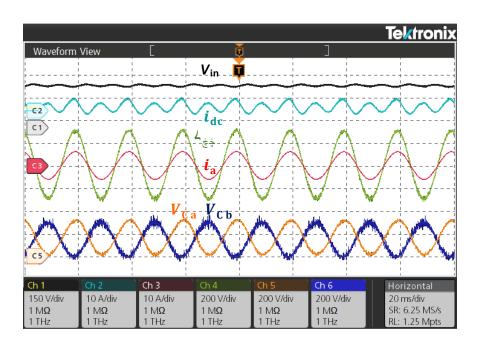

| Figure 6.4: Experimental results of the standalone system at 1kW without second-order ripple controller ( $V_{in}$ : 150V/div, $i_{dc}$ , $i_{a}$ : 10A/div, $v_{ab}$ , $V_{ca}$ , $V_{cb}$ : 200V/div)                                                     |

| Figure 6.5: Experimental results of the standalone system at 1kW with second-order ripple controller ( $V_{in}$ : 150V/div, $i_{dc}$ , $i_a$ : 10A/div, $v_{ab}$ , $V_{ca}$ , $V_{cb}$ : 200V/div)                                                          |

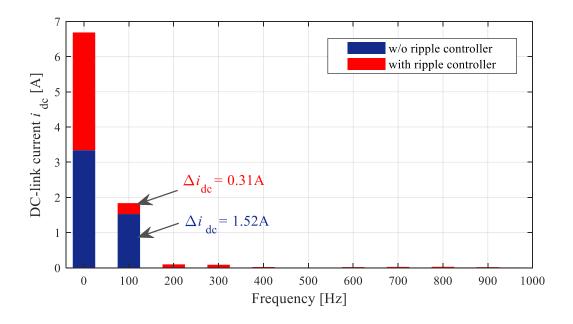

| Figure 6.6: FFTs of the DC-link current with and without second-order ripple111                                                                                                                                                                             |

| Figure 6.7: Prototype of the buck-boost inverter (1.8kW)                                                                                                                                                                                                    |

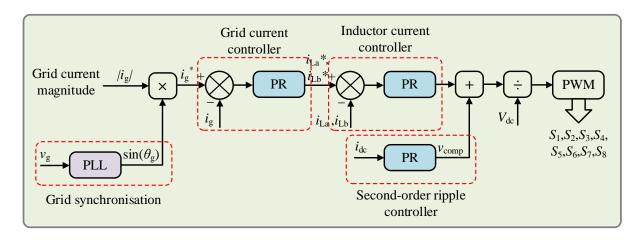

| Figure 6.8: Grid-connected controller for a buck-boost inverter.                                                                                                                                                                           | 113 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

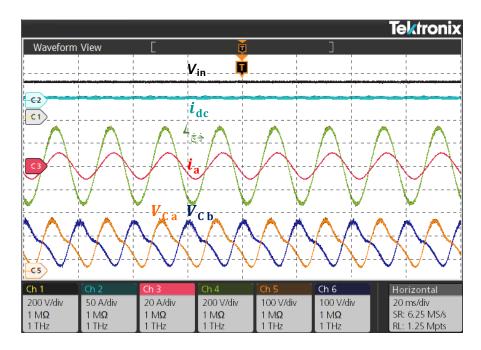

| Figure 6.9: Experimental results for a grid-connected system at 1.8kW without a second-order ripple controller ( $V_{in}$ : 200V/div, $i_{dc}$ , $i_{a}$ : 20A/div, $v_{ab}$ , $V_{ca}$ , $V_{cb}$ : 200V/div)                             |     |

| Figure 6.10: Experimental results for a grid-connected system at 1.8kW with a second-or ripple controller ( $V_{in}$ : 200V/div, $i_{dc}$ : 50A/div $i_a$ : 20A/div, $v_{ab}$ : 200V/div, $V_{ca}$ , $V_{cb}$ : 100V/div.                  | v). |

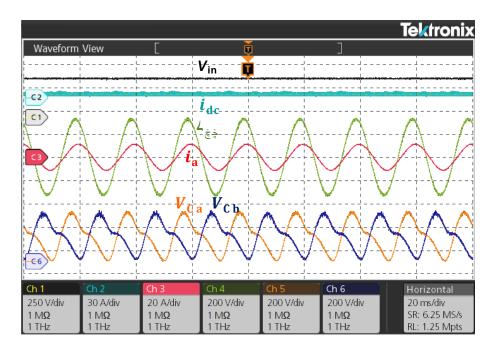

| Figure 6.11: Experimental results for a grid-connected system at 1.8kW with a second-or ripple controller ( $V_{\rm in}$ : 250V/div, $i_{\rm dc}$ : 30A/div, $i_{\rm a}$ : 20A/div, $v_{\rm ab}$ , $V_{\rm ca}$ , $V_{\rm cb}$ : 200V/div) |     |

| Figure 6.12: Maximum efficiency of the buck-boost inverter.                                                                                                                                                                                | 115 |

| Figure 6.13: Efficiency of grid-connected inverters.                                                                                                                                                                                       | 116 |

## **List of Tables**

| Table 2.1: Summary of the power decoupling methods               | 22  |

|------------------------------------------------------------------|-----|

| Table 3.1: Design constraints of the GP method                   | 49  |

| Table 3.2: Coefficients of inductor and capacitor volume         | 50  |

| Table 4.1: Design parameters of the ANN method                   | 63  |

| Table 5.1: Design constraints of the inverter                    | 95  |

| Table 5.2: Cost coefficients of the components                   | 95  |

| Table 5.3: Simulation parameters of the buck-boost inverter      | 100 |

| Table 6.1: Experimental device and type                          | 107 |

| Table 6.2: Comparison of existing buck-boost inverter topologies | 116 |

| Table A.1: Characteristics of the GaN FETs.                      | A-1 |

### **List of Abbreviations**

AC - Alternating Current

AI - Artificial Intelligence

ANN - Artificial Neural Network

CCS - Code Composer Studio

DC - Direct Current

FET - Field-effect transistor

FFT - Fast Fourier Transform

GA - Genetic Algorithm

GaN - Gallium Nitride

**GP** - Geometric Programming

kW - Kilowatts

MPPT - Maximum Power Point Tracking

MW - megawatt

PI - Proportional Integral

PLL - Phase-Locked Loop

PR - Proportional-Resonant

PSO - Particle Swarm Optimisation

PV - Photovoltaic

PWM - Pulse-width Modulation

RMS - Root Mean Square

Si - Silicon

SiC - Silicon-carbide

THD - Total Harmonic Distortion

TI - Texas Instrument

UK - United Kingdom

UPS - Uninterruptible Power Supply

VAT - Value-added tax

WBG - Wide-Bandgap

## **List of Symbols**

Switch area  $A_{sw}$ Output capacitance of GaN FET  $C_{oss}$ Second-order ripple power frequency  $f_{2\omega}$  $f_{\rm sw}$ Switching frequency  $G_{i_{dc}}(s)$ Second-order ripple controller  $G_{i_{1,a}}(s)$ Inductor current controller  $G_{v_{ab}}(s)$ Output voltage controller Second-order ripple current component  $i_{\rm comp}$  $I_{\mathsf{g}}$ Peak value of injected grid current  $I_{RMS,C}$  RMS current flow through the capacitor Proportional gain  $k_P$ Integral gain  $k_I$ Fundamental resonant control gain  $k_r$ *h*-order resonant controller gain  $k_{rh}$ Bode diode loss  $P_{\rm bd}$  $P_{\rm cap}$ Capacitor power loss

$P_{\rm cond}$

Conduction loss

P<sub>const</sub> Constant power

$P_{C_{oss}}$  Output capacitor loss

*P*<sub>D</sub> Power dissipated by GaN FET

$P_{\rm g}$  Gate loss

$P_{\rm ind}$  Inductor power loss

$P_{\rm rr}$  Reverse recovery loss

$P_{\rm sw}$  Switching loss

*P*<sub>out</sub> Output power of the inverter

$p_{\rm r}$  Second-order ripple power

$Q_{\rm g}$  Gate charge

*R* Fitness value

$R_{\rm DS,on}$  ON-state resistance of GaN FET

$R_{\theta \text{CS}}$  Thermal resistance from case to mounting surface

$R_{\theta IC}$  Thermal resistance of junction-to-case

Target value

$tan \delta$  Capacitor loss factor

$t_{\rm CR}$  Current rise time of GaN FET

$t_{\rm CF}$  Current fall time of GaN FET

$t_{\rm rr}$  Reverse recovery time

$t_{\rm VR}$  Voltage rise time of GaN FET

$t_{\rm VF}$  Voltage fall time of GaN FET

$V_{\rm dc}$  DC-link voltage

$V_{\rm g}$  Peak value of grid voltage

$V_{\rm GS}$  Gate-source voltage

vol<sub>cap</sub> Capacitor volume

$vol_{\text{heat sink}}$  Heat sink volume

$vol_{ind}$  Inductor volume

$vol_{sw}$  Volume of switch

$V_{\theta SA}$  Volumetric resistance

Y Output value

$\Delta V_{\rm dc}$  DC-link voltage peak-to-peak ripple

$\Delta i_{\rm L}$  Inductor current ripple

$\Delta T_i$  Change in junction temperature

$\omega_0$  Angular frequency

$\varphi$  Phase angle

$\Sigma_{\text{switch}}$  Cost of switch

$\Sigma_{inductor} \quad \ Cost \ of \ inductor$

$\Sigma_{capacitor}$  Cost of capacitor

$\Sigma_{heat \, sink}$  Cost of heat sink

## **Chapter 1 Introduction**

#### 1.1 Background

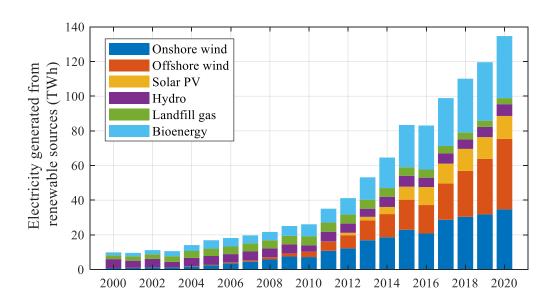

Renewable energy is a fast-growing source of energy. It contributes significantly to generation capacity and, when integrated with other sources of energy, renewables can help to meet global energy needs. In the United Kingdom (UK), the contribution of renewable energy sources to electricity generation increased by 13% between 2019 and 2020 [1]. Figure 1.1 shows the contribution of renewable energy sources to electricity generated. Among the renewable energy sources, solar energy is one of the most reliable and it plays an important role in the UK generation mix. In Figure 1.1, it can be seen that generation from solar photovoltaic (PV) increased by 4.6% in this period. In the first quarter of 2021, the installed capacity of solar PV was 175 megawatt (MW) and the total UK solar capacity will be expected to increase 2,711MW by 2023 [2] and [3]. Furthermore, solar PV can be installed in a wide variety of locations, such as roofs top, commercial and industrial properties and on the ground.

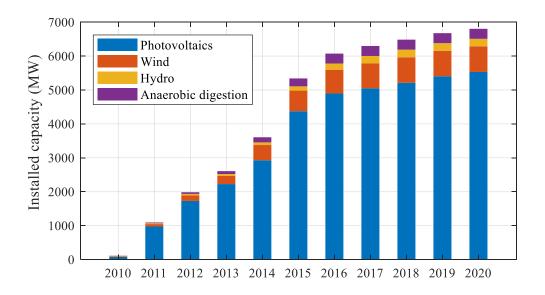

Small-scale solar PV systems have drawn attention because they enable domestic customers and businesses to independently generate electricity. Figure 1.2 shows the annual installation capacity of micro-generation in the UK. From 2016 to 2020, almost all of the newly installed micro-generation capacity was solar PV [1]. According to the Solar Trade Association (trading as Solar Energy UK since April 2021), around 900,000 British homes have installed solar PV panels [3]. Despite the end of the feed-in-tariff in April 2019 and the increase in value-added tax (VAT) for solar installations, the market continues to grow. According to GreenMatch [3], 2,375 new sub-4 kilowatt (kW) solar panel installations were approved in June 2021.

2 Introduction

Figure 1.1: Contribution of renewable energy sources to electricity generated.

Figure 1.2: Annual installation of micro-generation capacity.

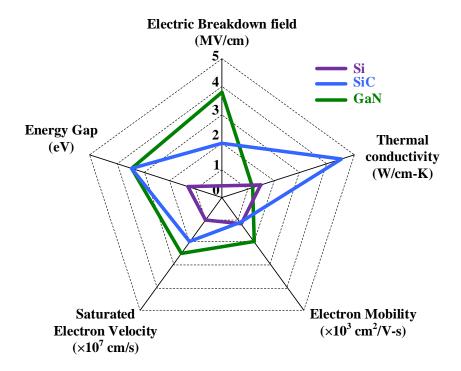

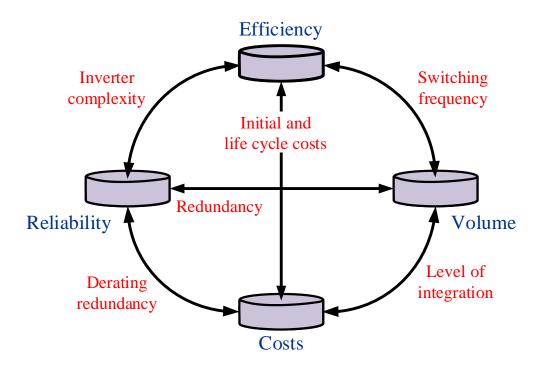

Power electronic inverters are a key component of solar PV systems, and they are used to interface the PV to the grid, extract the maximum power from PV panels, and maintain high quality output. Solar panel efficiency is very low, they can only convert 15% to 22% of solar energy into actual electricity [4]. Therefore, the solar PV inverter should be high efficiency to

reduces the system's power losses. Moreover, power density, cost and reliability are the other key factors to improve the overall system performance. Therefore, power electronics research has focused on developing a PV inverter with high efficiency, power density, reliability, and reduced cost.

The performance of PV inverters has improved in three ways: 1) new inverter topologies have been developed, 2) control methods have advanced, and 3) wide bandgap (WBG)-based semiconductor devices have been used. Furthermore, innovative topologies that provide higher efficiency and reduce the number of components [5] have been developed. Different control methods have been investigated to extract the maximum power from the PV panels [6]. WBG semiconductor devices have superior properties than Silicon (Si)-based semiconductors devices [7] and [8]. However, the design challenges of inverter topologies and the impacts of integration of WBG devices have led to trade-offs being made between the system components. Therefore, there is a clear need to address the design challenges and the impacts of WBG devices in PV inverter topologies.

#### 1.2 Research Objectives

This thesis investigates a Gallium Nitride (GaN)-based single-phase differential inverter for PV applications. Compared to many other PV inverter topologies, the differential inverter can reduce second-order ripple power and leakage current without adding extra active or passive components. Optimal design and control methods were employed to fully utilise the benefits of GaN devices and solve the challenges associated with single-phase inverters. The main objectives of this research are to:

- ◆ Investigate the single-phase buck-type differential GaN inverter to understand the trade-off between the power decoupling capacitance, power loss, and power density. In addition, a detailed modelling approach needs to be developed to realise the tendency of performance parameters.

- ◆ Design a control scheme to eliminate the second-order ripple using the active power decoupling method. Besides, a systematic approach to be required to select the optimal control parameters.

4 Introduction

◆ Investigate a simple and efficient design method to select the optimal components for the inverter. The optimal design needs to be identified with more accurate and less computation complexity.

- ◆ Identify a single-phase differential GaN inverter without increasing the power loss, volume, and cost. Transfer the knowledge of efficient design methods to design the identified final inverter topology.

- Performance of the design, control methods and the inverter topologies need to be ensured by conducting simulation and experimental studies.

#### 1.3 Thesis Outline

#### Chapter 2: Literature Review

This chapter reviews the existing inverter topologies and identifies their limitations and research gaps. The single-phase inverter topology and the inherent challenges are overviewed. Different types of power decoupling methods are reviewed, and their benefits in solving the second-order ripple problem are discussed. In addition, the WBG-based single-phase inverters are reviewed, and the design challenges are discussed. Then, different design methods are reviewed, and the need for the optimal design method is discussed.

Chapter 3: Design and Control of Single-phase Differential Buck Inverters for Power decoupling

This chapter presents the design and control methods of a GaN-based single-phase inverter. The differential buck-type inverter is used as an example to explore the benefits of active power decoupling functions. A mathematical model is developed for all the active and passive components of the inverter. The Geometric Programming (GP) method is presented to identify the optimal design parameters. The controller's design is then discussed in detail. The design method is implemented in MATLAB, and the trade-offs between efficiency and power density are analysed. The performance of the design method is verified using a 1kW prototype.

1.3 Thesis Outline 5

Chapter 4: Artificial Intelligence-based Fast and Accurate Design Method for Single-phase Differential Buck Inverters

An Artificial Neural Network (ANN)-based design method is presented to reduce the computational burdens and improve accuracy. The performance and computational time of the ANN-based design method are compared with the numerical model and GP-based design method. The outcome of the design method is experimentally verified by designing a buck-type of differential inverter. Using the experimental setup, the performance of the inverter is evaluated both without and with using a power decoupling controller.

Chapter 5: High-efficiency and High-power Density Design of a Single Stage Buck-boost Differential Inverter

In this chapter, a single-stage buck-boost differential inverter is presented. The operating principle and mathematical modelling of the inverter are explained. An ANN-based optimal design method is used to select the active and passive components. The structure of the controller is presented, and the detailed operation is explained. The inverter design method and the controller are implemented in MATLAB/Simulink. The efficiency, power density and specific cost are examined to verify the performance.

#### Chapter 6: Experimental Verifications of Buck-boost Differential Inverters

A laboratory prototype is built to verify the experimental performance of the buck-boost inverter. The experiments are conducted in both standalone and grid-connected systems. The results are verified both with and without using the power decoupling function. The efficiency and Total Harmonic Distortion (THD) responses are obtained to validate the effectiveness of the inverter. The benefits of the proposed topology are compared with the existing inverter topologies.

6 Introduction

#### Chapter 7: Conclusions and Future Work

This chapter presents the conclusion and summary of the thesis. Some recommendations for future work are also listed.

#### 1.4 Contributions of the Research Work

The contributions of this thesis are as follows:

- ◆ Developed a mathematical model of a single-phase buck-type GaN inverter to understand the trade-off between the power decoupling function, power loss and efficiency. Formulated and implemented a multi-objective design method using GP to select an optimal inverter design while considering the second-order ripple. Design a control scheme for the selected optimal inverter design. Experimentally validated the design method.

- ◆ Developed an ANN-based multi-objective design method to reduce the repeated use of mathematical models and computational complexity. Compared the results with existing design methods, such as numerical model and GP method. Verified the accuracy and computational time for different designs. Validated the results with a laboratory prototype.

- ◆ Presented a single-stage GaN-based buck-boost inverter to achieve a wide voltage range and power decoupling functions. Developed a multi-objective design approach to optimise the efficiency, power density and component costs. A detailed description of the operation and component selections is presented. The performance is studied using simulation and experimental results. Standalone and grid-connected tests are conducted to verify the inverters performance.

1.5 List of Publications 7

#### 1.5 List of Publications

#### **Journal Papers**

a) **R. Rajamony**, S. Wang, R. Navaratne and W. Ming, "Multi-Objective Design of Single-Phase Differential Buck Inverters with Active Power Decoupling," IEEE Open Journal of Power Electronics, vol. 3, pp. 105-114, 2022.

b) Rajesh Rajomony, Wenlong Ming, Sheng Wang," Artificial Neural Networks-based Multi-Objective Design Methodology for Wide-bandgap Power Electronics Converters" (To be submitted)

#### **Conference Papers**

- a) R. Rajamony, W. Ming and S. Wang, "Artificial Neural Networks based Multi-Objective Design Approach for Single-phase Inverters," 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), 2020, pp. 409-416.

- b) **R. Rajamony** and W. Ming, "Improved Hold-Up Time for WBG-based Single-Phase Converters," 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 2019, pp. 1-9.

## **Chapter 2 Literature Review**

#### 2.1 Introduction

A literature review of single-phase inverter with power decoupling and design methods is presented. The operating principle and the second-order ripple challenges are discussed. The concept of power decoupling functions and different types of active and passive power decoupling methods are presented. The benefits of differential inverters and their second-order ripple elimination capabilities are reviewed. The advantages of WBG devices and the application for power converter design are discussed. Finally, the challenges associated with power converter design and different design methods are reviewed.

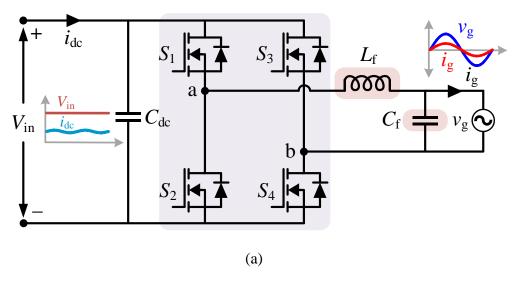

#### 2.2 Single-phase Inverter

Figure 2.1 shows the topology and control scheme of a single-phase inverter [9-11]. This inverter consists of four switches. The switch devices  $S_1$ ,  $S_2$  and  $S_3$ ,  $S_4$  are operated in complement to achieve a sinusoidal output voltage. The switches are connected with an anti-parallel diode to protect them from a reverse current, which the switching device turns OFF. The positive cycle of the output voltage is generated when the switches  $S_1$ ,  $S_4$  are ON, and  $S_2$ ,  $S_3$  are OFF. Similarly, the negative cycle of the output voltage is generated when the switches  $S_1$ ,  $S_4$  are OFF, and  $S_2$ ,  $S_3$  are ON. The output filter inductor  $L_f$  and capacitor  $C_f$  are used to remove the switching harmonics and produce a pure sinusoidal output voltage.

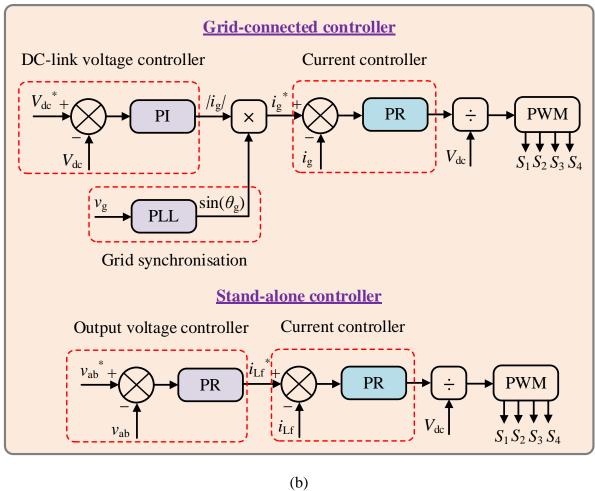

Two type control schemes can be used: a grid-connected controller [10] and a standalone controller [11]. Figure 2.1 (b) shows the control structure of grid-connected and standalone controllers. These are voltage-current closed loop controllers, which is one of the most popular control schemes. These controllers are developed using the well-known Proportional-

Figure 2.1: Conventional single-phase inverter: (a) Topology, and (b) Control scheme.

10 Literature Review

Integral (PI) and Proportional-Resonant (PR) controllers. When compared to the PI controller, the PR controller with a harmonic compensator can provide good performance in terms of accurate tracking and fast dynamic response. The transfer functions of the PI and PR controllers [12] are represented as,

$$G_{\rm PI}(s) = k_{\rm P} + \frac{k_{\rm I}}{s}$$

(2.1)

$$G_{PR}(s) = k_P + \sum_{r=1,3.5,...} \frac{k_{rh}s}{s^2 + (h\omega_0)^2}$$

(2.2)

where  $k_P$  is the proportional gain,  $k_I$  is the integral gain,  $k_r$  is the fundamental resonant control gain,  $k_{rh}$  is the control gain for h-order resonant controller and  $\omega_0$  is the fundamental frequency. Adding harmonic compensators with appropriate gain can efficiently decrease the harmonics at the corresponding resonant points

#### 2.2.1 Grid-connected Controller

Grid-connected inverters are mainly used for renewable energy applications, such as solar PV systems, wind energy systems, and fuel cells. A grid-connected controller is used to control the inverters for such applications, which consists of a Direct Current (DC) link voltage controller, grid synchronisation and current controller. The DC-link controller is designed by a PI controller to regulate the voltage from a variable DC-source. The output of the DC-link controller is the magnitude of the grid current  $|i_g|$ . The reference grid current  $i_g^*$  is generated by multiplying the output of the DC-link controller  $|i_g|$  and the output of the Phase-locked loop (PLL)  $\sin(\theta_g)$ . PLL is used to synchronise the phase angle of reference grid current  $i_g^*$  to the grid voltage  $v_g$ . The advantages of PLL include the better rejection of grid harmonics, notches, and other kind of disturbances. Hence, the quality of the current injected into the grid can be improved [13]. The current controller is designed based on PR controllers, which has responsibilities for the power quality issues and current protection of the inverter. The harmonics order r is selected based on the need for grid current quality.

#### 2.2.2 Stand-alone Controller

Standalone inverters are mainly used for applications, such as uninterruptible power supply (UPS), and storage systems. The standalone controller is used to control the inverters for these applications. The standalone controller consists of the output voltage controller and current controller. The voltage and current controllers are designed using a PR controller. The voltage controller controls the output voltage  $v_{ab}$  of the inverter based on the reference voltage  $v_{ab}^*$ . Normally, the reference voltage is equal to the grid voltage, and it can be changed in some applications. The output of the voltage controller is the reference current flow through the inductor  $i_{Lf}^*$ . The current controller is designed by the PR controller, which has the responsibility to protect the current of the inverter. The compensator of the current control is designed based on the need for harmonic elimination.

#### 2.3 DC-link Second-order Ripple

Figure 2.1(a) shows the topology of a single-phase inverter. The output voltage and current of single-phase inverter are given as,

$$v_{\rm g} = V_{\rm g} \sin(\omega t) \tag{2.3}$$

$$i_{\rm g} = I_{\rm g} \sin(\omega t + \varphi) \tag{2.4}$$

where,  $V_g$  and  $I_g$  are the peak values of the grid voltage and injected grid current.  $\omega$  is the angular frequency and  $\varphi$  is the phase difference between the voltage and current. Generally, the instantaneous power of DC and Alternating Current (AC) sides must be equal. However, the inherently unbalanced nature of single-phase systems causes the ripple power which creates the mismatch between the DC and AC power. To understand this point more clearly, the instantaneous power at the DC side can be written as,

$$p_{\rm dc} = p_{\rm g} = v_{\rm g} i_{\rm g}$$

(2.3)

$$p_{\rm dc} = V_{\rm g} \sin(\omega t) I_{\rm g} \sin(\omega t + \varphi)$$

12 Literature Review

$$= \frac{V_g I_g}{2} (\cos(\omega t - \omega t - \varphi) - \cos(\omega t + \omega t - \varphi))$$

$$p_{dc} = \frac{V_g I_g}{2} \cos \varphi - \frac{V_g I_g}{2} \cos(2\omega t - \varphi)$$

$$P_{const} = \frac{V_g I_g}{2} \cos \varphi \quad \text{and} \quad p_r = -\frac{V_g I_g}{2} \cos(2\omega t - \varphi)$$

$$p_{dc} = P_{const} + p_r \tag{2.4}$$

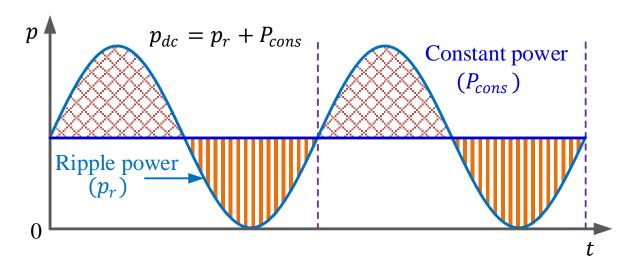

where,  $P_{\rm const}$  is the constant power and  $p_{\rm r}$  is the ripple power. From equation (2.4), the instantaneous DC power consists of constant power  $P_{\rm const}$  and ripple power  $p_{\rm r}$ . The frequency of the ripple is twice  $2\omega$  the line frequency.

#### 2.3.1 Effects of Second-order Ripple

In solar PV applications, the second-order ripple shifts the operating point from the maximum power point during Maximum Power Point Tracking (MPPT) operations [14–16]. In fuel cells, the second-order ripple causes fuel starvation and stress on the membrane of the fuel cell [17] and [18]. In battery systems, the second-order ripple increases the battery temperature, affecting the electrodes, increasing the voltage/current stress and reducing efficiency [19] and [20]. The second-order ripple can be reduced by choosing an adequate DC-link capacitor. The DC-link capacitance  $C_{\rm dc}$  can be calculated [21] as,

$$C_{\rm dc} = \frac{P_{\rm out}}{\omega V_{\rm dc} \Delta V_{\rm dc}} \tag{2.5}$$

where,  $P_{\text{out}}$  is the output power,  $V_{\text{dc}}$  is the DC-link voltage and  $\Delta V_{\text{dc}}$  is the peak-to-peak ripple. From equation (2.5), a large value of the DC-link capacitance can reduce the peak-to-peak ripple. Electrolytic capacitors are widely used in the DC-link of single-phase inverters because of their lower cost. However, electrolytic capacitors reduce the efficiency, power density and reliability of the inverter [22] and [23]. Film capacitors can be used instead, which have a much longer lifetime [24]. However, film capacitors cannot directly replace electrolytic capacitors because of their large volume and high cost [25]. Consequently, power

decoupling methods are used to reduce the size of the DC-link capacitance and the effects of second-order ripple [26] and [27].

#### **2.4 Power Decoupling Methods**

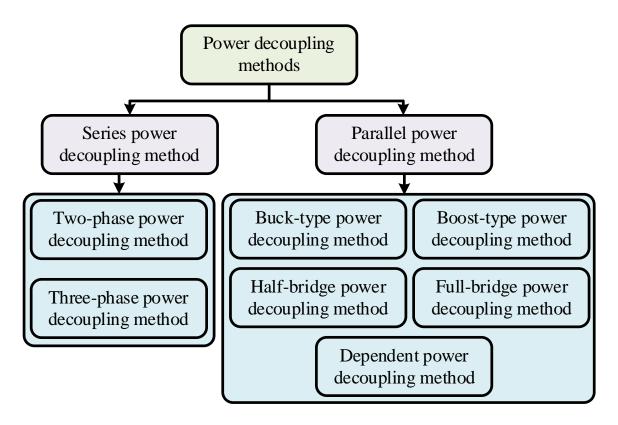

Figure 2.2 shows the concepts of the power decoupling. The inverter requires constant power  $P_{\rm const}$  and eliminates the ripple power  $p_{\rm r}$  from the DC-link power  $p_{\rm dc}$ . The main objective of the decoupling method is to divert the ripple power  $p_{\rm r}$  from the DC-link capacitor into an auxiliary circuit. The auxiliary circuit is developed using active or passive components. Hence, small-sized, and long lifetime film capacitors can be used. The power decoupling method can be categorised into an active decoupling method [28] and a passive decoupling method [29]. In active power decoupling methods, the auxiliary circuit is made using switches, inductors, and capacitors, which needs an additional control method to control the active devices. The passive power decoupling methods use an inductor and capacitors. Based on the configurations of the auxiliary circuit, the power decoupling methods are categorised into series and parallel. Figure 2.3 gives an overview of the series and parallel power decoupling methods. The details of series and power decoupling methods are reviewed in more detail in the following sections.

Figure 2.2: Concepts of power decoupling.

14 Literature Review

Figure 2.3: Overview of different power decoupling methods.

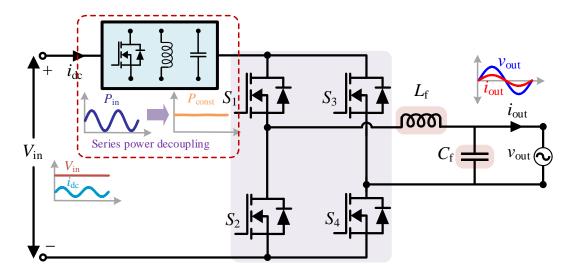

#### **2.4.1 Series Power Decoupling Methods**

Figure 2.4 shows a single-phase inverter with series power decoupling methods. The series power decoupling method is developed by adding active and passive components between the DC-source and inverter. When the DC-link current flows through the power decoupling circuit, the second-order ripple power is diverted into the storage components of the decoupling circuit. To extract the second-order ripple components, the decoupling circuit can be controlled using appropriate control methods. Hence, the current that flows through the inverter will only have the DC-components.

Figure 2.4: Single-phase inverter with series power decoupling.

In [30] and [31], a series power decoupling method has been presented to reduce the DC-link capacitance. The voltage ripple in the DC-link capacitor was compensated by connecting a two-phase series voltage source converter in the DC-bus line. The need for a sizeable DC-link capacitor was reduced using this decoupling method, which allows a long lifetime film capacitor to be used. In [32], the same power decoupling method was used for a grid-tie solar PV inverter to reduce a low voltage ripple. The two-phase method was effective in terms of reducing the second-order ripple. However, the series voltage source converter requires a slightly higher value capacitor to reduce the ripple completely. Therefore, a three-phase power decoupling method was introduced in [21] and [33] to reduce the need for extra capacitors without compensating performance of low ripple elimination. This method can achieve an 89% reduction of the DC-link capacitance.

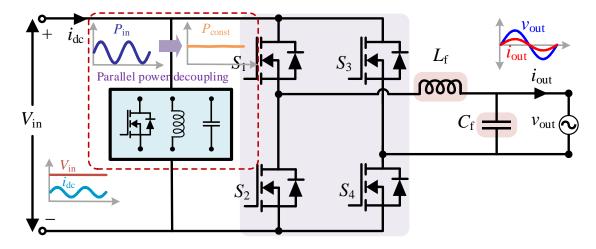

#### 2.4.2 Parallel Power Decoupling Methods

Figure 2.5 shows a single-phase inverter with parallel power decoupling methods. The parallel power decoupling method is developed by connecting active and passive components across the positive and negative terminal of the DC-bus line. Using appropriate control methods, the second-order ripple power is diverted into the storage components of the decoupling circuit. The current that flows through the inverter will only have the DC-

16 Literature Review

components, which reduces the losses that are caused by the ripple power. The parallel power coupling methods are configured in different types, such as buck, boost, half-bridge and full-bridge converters.

Figure 2.5: Single-phase inverter with parallel power decupling.

#### **Buck Type Power Decoupling**

In [34], a bidirectional buck-type DC-DC converter-based active power decoupling method was introduced to reduce the effect of ripple power. The bidirectional active power decoupling circuit was integrated into the DC-bus line of the inverter. In [35], a buck-type active power decoupling method was used in a boost inverter to reduce the effects of low-frequency ripples for fuel-cell applications. In [36] and [37], the same power decoupling method was used in a buck-boost inverter to improve the performance of fuel cells. Using these methods, the need for large DC-link capacitors was prevented, and the performance was verified using simulation and experimental results. The performance of the buck-type active power decoupling method was investigated without using any additional magnetic components for PV applications in [38]. The decoupling method was reduced the second-order ripple on the DC-link current by 90.2% and achieved the maximum efficiency of 96%. In addition, in [39] and [40], the low-frequency oscillation of modular multilevel converter was eliminated using the buck-type power decoupling method. This substantially reduced the submodule voltage ripple and the total capacitance.

#### **Boost Type Power Decoupling**

The boost-type active power decoupling method is commonly used to reduce the second-order ripple by injecting continuous compensation current into the DC-link. The decoupling capacitor voltage of this method is relatively high, and hence this decoupling function is suitable for application with lower DC-link voltage. In [41] and [42], a boost-type parallel power decoupling approach was used to enhance the power generation of the PV systems. The elimination of the low-frequency ripple helped to operate the PV module close to the maximum power and enhance the efficiency of these systems. In [24], the control performance of the boost-type decoupling method was investigated using a virtual capacitance controller and DC-link voltage controller. The performance of the controller was evaluated in module integrated PV inverters and low-frequency oscillation was eliminated.

Continuous operation of the boost-type active power decoupling function increases the power loss of PV power conversion systems. To address this problem, in [43] the authors presented a partial power decoupling technique to improve the inverters efficiency over a wide power output range. A detailed power loss model was developed to identify the factors that reduce the system efficiency. The trade-off between the power decoupling functions and the overall efficiency was then studied. This approach was verified through experimental results and the improvement of conversion efficiency was validated.

In [44], a virtual capacitor-based boost-type active low-frequency ripple control method was introduced to build integrated PV applications. Using an integrator compensator, the virtual capacitor concept was added into the control loop. The virtual capacitor-based control method achieved better ripple control over the low frequencies. The component selection of boost-type active power decoupling is more important to achieve high-power density. Therefore, the procedure to select the passive components was investigated in [45] and [46] for a switched boost inverter. Using this method, the low-frequency ripple on the inductor current and the capacitor voltage of the switched boost inverter were reduced.

#### **Buck-boost Type Power Decoupling**

The buck- and boost-type active power decoupling methods are only beneficial for applications where the decoupling capacitor voltage is lower or higher than the DC-link voltage. To overcome this limitation, a buck-boost converter-based active power decoupling method was investigated in [47]. Using this method, the average decoupling capacitor voltage was controlled based on the variation of the DC-link voltage. In addition, the low-frequency ripple on the DC-link eliminated the need for total capacitance.

#### Half-bridge Type Power Decoupling

The half-bridge-based active power decoupling method is used to reduce low-frequency and high-frequency ripples. In [17], the half-bridge-based decoupling method was used to improve the stack efficiency and durability of fuel cells. A symmetrical half-bridge with split capacitor was introduced in [48] and [49] to eliminate the low-frequency oscillation and the need for large passive components. Using this method, a ten times reduction in the total capacitance was achieved and the converter output was regulated using small DC-link capacitors [50].

These active power decoupling methods required additional active and passive components. However, adding more active devices increases the control complexity and the component costs. Therefore, independent active power decoupling methods are widely used to reduce the number of control devices. In [51], a symmetrical half-bridge-based dependent active power decoupling topology was presented that had only used two switches and one small filtering inductor, while DC-link capacitors were used to absorb the ripple power. In [52] and [53], an improved active power decoupling was introduced that used two split capacitors to store the low-frequency ripple. Consequently, the need for active devices is avoided and the current stress of the switches is reduced.

# Full-bridge Type Power Decoupling

In [54] and [55], the full-bridge converter-based parallel active power decoupling circuit was introduced to buffer the ripple current and minimise the DC-link capacitance. The full-bridge converter was connected across the DC-bus line. In [56] and [57], a smaller capacitor was connected in series with the full-bridge compensator to reduce the effects of the DC-link

voltage ripple. The full-bridge parallel ripple compensator reduced the volume of the protype by 16% compared to the conventional ripple elimination method, while the efficiency of the inverter was reduced by around 1%. A comparison study of the same full-bridge decoupling compensator was presented in [58] and the results were verified using an experimental study.

### **Dependent Power Decoupling**

The dependent power decoupling method has been formulated using either active or passive components. In [59], an active power decoupling was formed using the one arm of a H-bridge circuit with one additional switch, diode, and an energy storage inductor. The need for a storage inductor of the half-bridge circuit was eliminated by adding two diodes in DC-bus line. The voltage stress of the decoupling circuit was reduced to half that of the DC-link voltage in [60]. A three-phase leg decoupling method was presented in [61–63], which used two additional switches and an auxiliary capacitor to store the ripple energy. In [64–66], another topology was introduced that used only one auxiliary capacitor and no additional switches. The auxiliary capacitor stored the low-frequency ripples, and an independent control scheme was presented to achieve the power decoupling functions. The performance of the decoupling methods was verified using simulation and experimental results.

# 2.4.3 Differential Inverters with Power Decoupling Function

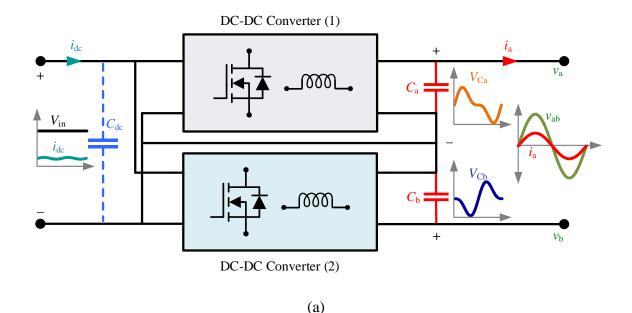

Differential inverters can achieve an active power decoupling function without adding extra active or passive components, which avoids the need for additional control. This has been classified into the buck, boost, or buck-boost inverters, which are developed using two identical DC-DC converters [67]. The output capacitor of the DC-DC converters is used for the power decoupling function. The inductor and capacitor filter the switching frequency, and no dedicated output filter is required to produce a pure sinusoidal output. Figure 2.6 shows the concepts of the power decoupling method in differential inverters, and DC-DC converters are used to develop the differential inverters.

In [29], a buck-type inverter was used to reduce the ripple from the DC-link using a decoupling control method. Consequently, the amplitude of second-order ripple in the DC-link current was reduced by more than seven times. The same inverter was used for grid-

connected PV applications by applying a common-mode conducting loop to reduce the leakage current caused by parasitic capacitance and to minimise the second-order pulsating power. It was confirmed that ground leakage current and the pulsating power problems are solved without adding extra active components [68]. The mismatch of the decoupling capacitors of differential buck inverters was resolved using a comprehensive common-mode control [69].

In [70], a waveform control-based ripple mitigation method was introduced for a boost-type inverter to eliminate the instability in the fuel-cell system. In [71] and [72], the waveform control method was improved using rule-based and feed-back current controllers for boost inverter-based grid-connected battery storage systems. In [73], an energy-based power decoupling control method was introduced for a buck-boost inverter to mitigate the second-order ripple in the input DC current. Consequently, the low-frequency ripple was eliminated. This enables film capacitors to be used instead of electrolytic capacitors. Although the efficiency and power density of the differential inverters are not considered while reducing the size of the decoupling capacitors, in practice they are the essential parameters that need to be considered.

Figure 2.6: (a) Concepts of power decoupling method in differential inverters, and (b) Types of DC-DC converters.

Table 2.1 summarises the power decoupling methods. This summary is given based on the types of power decoupling, power rating, number of components used to develop the power decoupling, efficiency, power density and the method's features. Series power decoupling can be achieved in two ways: two-phase and three-phase methods. Many additional components are required to develop series power decoupling. Meanwhile, parallel decoupling methods have many different configurations. Among them, buck and full-bridge type decoupling methods are more efficient when compared to the other methods. In addition, the dependent decoupling methods minimised the number of active components. However, this

method also requires passive components. The use of additional components reduces the efficiency and power density of the overall system. In contrast, differential inverters do not require any additional components to achieve active power decoupling. Therefore, a differential inverter is a good option for a single-phase inverter with power decoupling functions.

Table 2.1: Summary of the power decoupling methods

| Decoupling                             | Reference | Power  | Additional | components                     | Efficiency | Volume               | Features                                          |

|----------------------------------------|-----------|--------|------------|--------------------------------|------------|----------------------|---------------------------------------------------|

| method                                 |           | rating | Active     | Passive                        |            |                      |                                                   |

| Two-phase<br>power<br>decoupling       | [30]      | 600W   |            |                                | -          | -                    | -Independent operation                            |

|                                        | [31]      | 3kW    | 4 Switches | 2 Inductors                    | -          | -                    | -Additional control                               |

|                                        | [32]      | 2kW    |            | 2 Capacitors                   | -          | -                    | required                                          |

| Three-phase                            | [33]      | 2kW    |            | 2 Inductors                    | 95%        | -                    | -No impact on the DC-<br>link voltage             |

| power<br>decoupling                    | [21]      | 2kW    | 6 Switches | 2 Capacitors                   | 95%        | $0.6~\mathrm{dm^3}$  | C                                                 |

| Buck type<br>power<br>decoupling       | [34]      | 15kW   | 2 Switches | 1 Inductor vitches 1 Capacitor | 93.2%      | 11.4 dm <sup>3</sup> | -Independent operation                            |

|                                        | [35]      | 1kW    |            |                                | 82%        | -                    | -Additional control                               |

|                                        | [36]      | 1.2kW  |            |                                | -          | -                    | required -Good option for high power rating       |

|                                        | [37]      | 1.2kW  |            |                                | 88%        | -                    |                                                   |

|                                        | [38]      | 1kW    |            |                                | 96%        | $0.42~\mathrm{dm^3}$ |                                                   |

|                                        | [39]      | 1kW    |            |                                | 97.13%     | $19.6 \text{ dm}^3$  |                                                   |

|                                        | [40]      | 5kW    |            |                                |            | -                    |                                                   |

| Boost type                             | [41]      | 110 W  |            |                                | -          | -                    | -Independent operation                            |

| power<br>decoupling                    | [42]      | 110 W  | 2 Switches | 1 Inductor                     | 90.5%      | -                    | -Additional control                               |

|                                        | [24]      | 4kW    |            |                                | 97.4%      | -                    | required                                          |

|                                        | [43]      | 1kW    |            | 1<br>Compositor                | 93.25%     | -                    | -Good option for high power rating                |

|                                        | [44]      | 2kW    |            | Capacitor                      | -          | -                    | -Higher voltage stress on power decoupling        |

|                                        | [45]      | -      |            |                                | -          | -                    |                                                   |

|                                        | [46]      | 250W   |            |                                | 91.8%      | -                    |                                                   |

| Buck-boost<br>type power<br>decoupling |           |        | 2 Switches | 1 Inductor                     | -          |                      | -Flexible control of decoupling capacitor voltage |

|                                        | [47]      | 1kW    |            | 1 Capacitor                    |            | -                    |                                                   |

|                                        | [17]      | 5kW    |            |                                | 92.4%      | -                    | -Independent operation                            |

|                                        | [48]      | 1kW    | 2 Switches | 1 Inductor                     | -          | -                    | -Additional control                               |

|                       | [49]       | 1kW   |            | 2 Capacitors | -     | -             | required                                        |

|-----------------------|------------|-------|------------|--------------|-------|---------------|-------------------------------------------------|

| Half-bridge           | [50]       | 1.5kW |            |              | -     | -             | -Two energy storage                             |

| type power            | [51]       | 1kW   | 2 Switches | 1 Inductor   | 95.8% | -             | capacitors are used for active power decoupling |

| decoupling            |            |       |            | 2 Capacitors |       |               | -Good option for high                           |

|                       | [52]       | 1kW   | -          | 1 Inductor   | 95%   | -             | power rating                                    |

|                       | [53]       | 1kW   |            | 2 Capacitors | 96%   | _             |                                                 |

| Full-bridge           | [55]       | 600 W | 4 Switches | 1 Inductor   | _     | -             | -Independent operation                          |

| type power            | . ,        |       |            | 1 Capacitor  |       |               | -Additional control                             |

| decoupling            | [56]       | _     | 4 Switches | 2 Inductors  | _     | _             | required                                        |

|                       | [57]       | 2kW   |            | 2 Capacitors | 94%   | $0.5 \; dm^3$ | -Good option for high                           |

|                       | [58]       | 2 kW  | 4 Switches | 1 Inductor   | 98.9% | _             | power rating                                    |

|                       | į <u>j</u> |       |            | 2 Capacitors |       |               |                                                 |

|                       | [59]       | 200W  | 1 Switch   | 1 Inductor   | -     | -             |                                                 |

|                       |            |       | 1 Diode    |              |       |               |                                                 |

|                       | [60]       | 1kW   | 2 Switches | 2 Capacitors | _     | _             | -Dependent operation                            |

| Dependent             |            |       | 2 Diodes   | •            |       |               | -Additional control not                         |

| decoupling            | [61]       | 4kW   | 2 Switches | 1 Capacitor  | _     | _             | required                                        |

|                       | [63]       | _     | 2 Switches | 1 Inductor   | 92.7% | _             | -Good option for high                           |

|                       | . ,        |       |            | 1 Capacitor  |       |               | power rating                                    |

|                       | [64]       | _     |            | •            | _     | _             |                                                 |

|                       | [65]       | 1kW   | _          | 1 Capacitor  | 91.5% | _             |                                                 |

|                       | [66]       | 540W  |            | •            | 94%   | _             |                                                 |

|                       | [29]       | 1kW   |            |              | 92.5% | -             | -Dependent operation                            |

| Differential          | [68]       | 500W  | _          | _            | 96%   | _             | -Additional control not                         |

| inverter              | [69]       | 800W  |            |              | -     | <u>-</u>      | required                                        |

| type power decoupling | [70]       | 170W  |            |              | 84%   | _             | - Additional components                         |

| accoupling            | [71]       | 20W   |            |              | -     |               | are not required                                |

|                       | [72]       | 20W   |            |              |       |               | -Good option for high power rating              |

|                       | [72]       | 400W  |            |              | 88%   |               | power runing                                    |

|                       | [/3]       | 400 W |            |              | 0070  |               |                                                 |

# 2.5 WBG Devices in Power Electronics

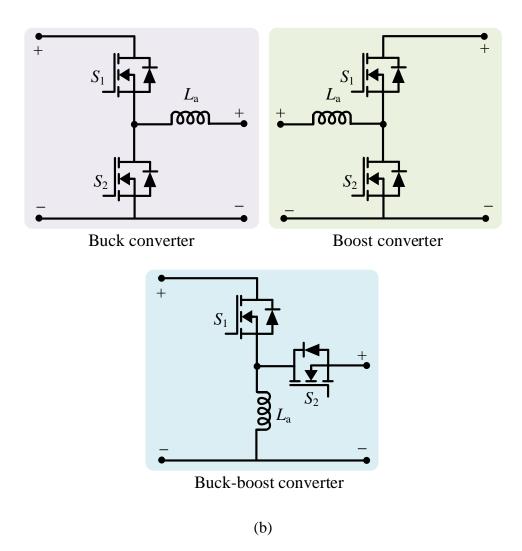

The power decoupling method of a single-phase inverter always has a trade-off between efficiency and power density. The benefits of WBG devices are enabling to improve the efficiency and power density by reducing the power loss and volume of the inverter. WBG

devices, such as Silicon Carbide (SiC) and GaN, have superior electrical properties for power electronics than conventional Si (as shown in Figure 2.7). The electrical properties have been characterised by the electric field, energy gap, electron velocity, electron mobility, and thermal conductivity [74]. These electric properties enable the WBG devices to operate at high voltage, high temperature, and high switching frequency.

Power switches based on WBG semiconductors have better switching and conduction performance over a wide range of temperatures than Si-based devices. For instance, they have faster switching speed, lower switching losses, higher breakdown voltages and higher operating temperatures. Therefore, WBG devices are considered to be promising solutions for high-efficient power electronic converter designs. In single-phase inverters, the WBG devices SiC and GaN provide a performance improvement over Si under wide load, temperature and switching frequency conditions. When comparing the switching performance of the three technologies, the GaN device has the best performance and provides high efficiency at high-frequency applications [75].

Figure 2.7: Comparison of Si, SiC and GaN semiconductors properties.

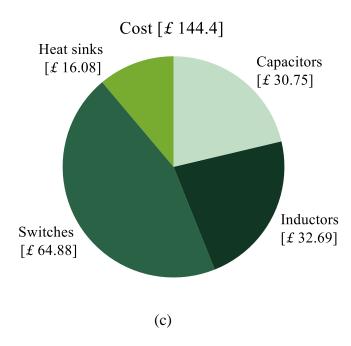

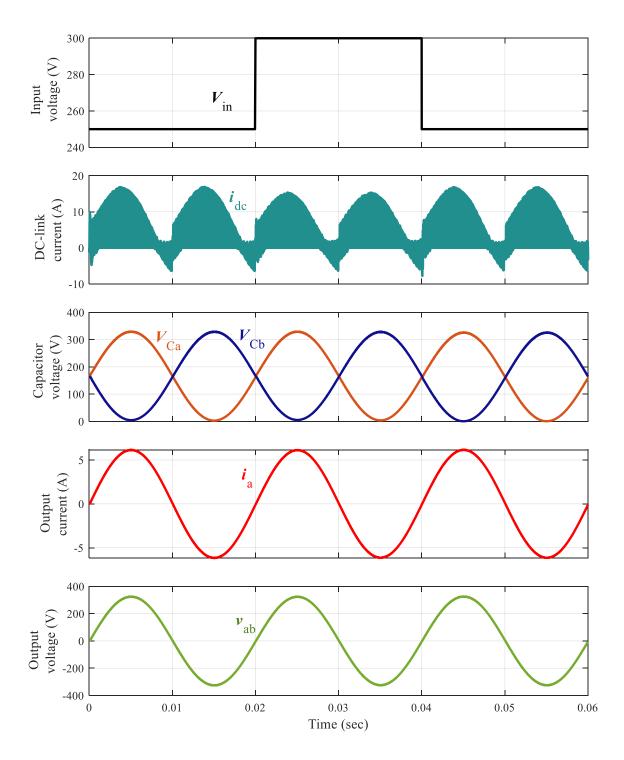

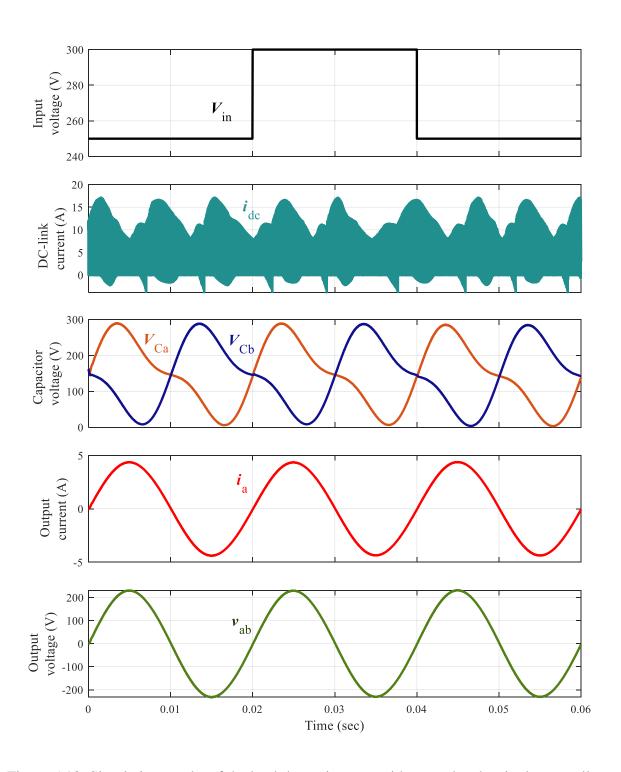

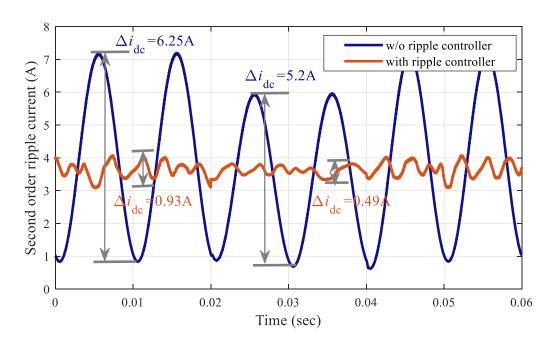

# 2.5.1 SiC-based Single-phase Inverters