بسمرالله الرحمن لرحب

# GaN HEMT Based Technology Development for Millimetre Wave Applications

by

**Moath Alathbah**

A thesis submitted in the fulfilment of the degree of Doctor of Philosophy

in

**Electrical and Electronic Engineering**

at

The School of Engineering, Cardiff University, Wales, The United Kingdom

June 2022

### ABSTRACT

High Electron Mobility Transistors (HEMTs) based on Gallium Nitride (GaN) and grown on Silicon (Si) substrates are emerging as one of the most promising candidates for high-power, switching-speed, low-losses, cost-effectiveness, and high-frequency Integrated Circuits (ICs) applications operating at microwave and millimetre frequencies (3-300 GHz). As silicon approaches its theoretically expected limitations, enhancements in energy efficiency of silicon power electronics are becoming less significant. Due to a unique combination of features that offer higher power density per unit area, compared to Si, GaN transistors are alternatives for the next generation of power electronics. Because GaN can be processed on current Si process lines employing GaN-on-Si heteroepitaxy, the industrial shift to GaN is also cost effective.

In GaN HEMTs devices, the mesa structure is a three-dimensional device structure that is conventionally created by traditional dry etching methods applied to establish device-isolation used for GaN-based transistor technologies. As a result, this leads to significant leakage currents which have an immense influence on the device's noise performance and breakdown voltages. In this thesis, a novel technique designed to establish a device-isolation in GaN HEMTs is proposed to overcome mesa etch concerns such as sidewall profile, common gate discontinuity and gate leakage originated from a gate direct contact with twodimensional electron gas (2DEG). The proposed method requires a miniature extension of the mesa to deposit the gate-feed to ensure a fully planar gate formation. As a result, this reduced the gate leakage by an order of magnitude. However, since the gate-feed is situated on an active layer with a very low resistance due to a relatively larger length in comparison with the actual gate, the gate became conductive above pinch-off point and gate leakage increased. Consequently, a dielectric is deposited below the gate-feed to counter the arising problem which led to an increase in the drain leakage at the off-state due to a substantial dielectric thickness. This can be prevented using methods such as atomic layer deposition for a denser yet a shallower (a few nm) dielectric deposition below the gate feed. Finally, the proposed structure will allow a deeper etch of the active layer for heat management purposes while keeping the integrity of the gate metal intact. Leakage currents reduction of unity A/mm were attained, which are equivalent to those obtained using the more sophisticated and costly ion implantation process. Additionally, a small-signal-model was developed to evaluate the behavior of the GaN HEMT devices with respect to the high frequency operation and the parasitic associated with it. The process began with the extraction of the extrinsic elements using various methods followed by the extraction of the intrinsic parameters.

Finally, novel GaN Schottky barrier diodes (SBDs) with multi-channel trenches positioned below the anodes to reduce the turn-on voltage caused by the reduction of the diode barrier height due to the direct contact to the 2DEG. To compete with existing III-V technologies, GaN-based SBDs with low reversecurrent leakage ( $I_S$ ), low onset voltage ( $V_{ON}$ ), high switching speed ( $R_{ON}$ ), high reverse-breakdown ( $V_B$ ) voltage, and high cutoff frequency ( $f_c$ ) are mainly essential to be considered. Conventional GaN-based SBD DC and RF performance, when fabricated using LR-Si substrates, is still constrained by their significant V<sub>ON</sub>, RF leakage, and switching losses. Methods such as recessed anode, dual-channel field-effect rectifier, regrowth cathodes, and dual-filed plates have been employed to suppress these problems. In this work, a cost-effective RF AlGaN/GaN SBDs on LR-Si structure is developed utilizing the technique of multi-channel and trenches below anodes, which is completely compatible with III-V THz monolithic integrated circuit (THz-MIC) technology. The newly designed devices outperformed traditional SBDs in terms of switching loss, turn-on characteristics, ideality factor ( $\eta_n$ ), and cutoff frequency, with R<sub>ON</sub> = 0.97  $\Omega$ .mm,  $V_{ON}$  = 0.84 V,  $V_B$  > 30V,  $\eta_n$  = 1.69, and  $f_c$  = 600 GHz. These outcomes are attributed to the direct contact acquired between the Schottky anode and the 2DEG channel occurring at the sidewalls of the trenches due to multi-mesa, as well as the precise design geometries utilized to limit substrate coupling effects.

### ACKNOWLEDGMENT

أولا, الحمد والشكر والثناء لله الرحن الرحيم الملك القدوس السلام المؤمن المهيمن العزيز الجبار المتكبر الخالق البارئ المصور الغفار القهار الوهاب الرزاق الفتاح العليم القابض الباسط الخافض الرافع المعز المذل السميع البصير الحكم العدل اللطيف الخبير الحليم العظيم الغفور الشكور العلي الكبير الحفيظ المُقيت الحسيب الجليل الكريم الرقيب المجيب الواسع الحكيم الودود المجيد الباعث الشهيد الحق الوكيل القوي المتين الولي الحميد الحصي المبدئ المعيد الحي المميت الحي القيوم الواجد الماجد الباعث الشهيد الحق الوكيل القوي المتين الولي الحميد الطاهر الباطن الوالي المميت الحي القيوم الواجد الماجد الواحد الصمد القادر المقتدر المقدم المؤخر الأول الاخر الظاهر الباطن الوالي المعالي البر التواب المنتقم العفو الرؤوف مالك الملك ذو الجلال والاكرام المقسط الجامع الغني المانع الضار النافع النور الهادي البديع الباقي الوارث الرشيد الصبور. فالفضل يعود له وحده من قبل ومن بعد. والصلاة والسلام على خاتم النبيين.

الشكر لحكومة المملكة العربية السعودية على دعمها المادي لجميع تكاليف البحث لتحضير الدكتوراه في مجال الهندسة الكهربائية والالكترونية لتطوير التقنية في حقل الاتصالات اللاسلكية.

Thanks to Prof. Khaled Elgaid and Prof. Paul Tasker for giving me the opportunity to conduct my PhD research under their supervision at Cardiff University. Also, thanks to Dr. Abdalla Eblabla for his useful GaN technology discussions and Dr. Roberto Quaglia for his assistance with RF measurements and the overall setup of the auto-prober measurement system.

Thanks also extended to Prof. David Wallis for providing the GaN epi-layers materials for this project.

Additionally, thanks to Dr. Arathy Varghese and my PhD fellow researchers Zehao Wu, Seyed Ghozati, Arthur Collier and Wesley Sampson in our group for their encouragement and support. Thank you, and good luck with your own PhD journey.

## **PUBLICATIONS**

#### Journal articles:

- <u>M. Alathbah</u>, and K. Elgaid, "Miniature Mesa Extension for a Planar Submicron Gate Formation," *IEEE Electron Device Lett.*, accepted with minor revision (ID: EDL-2022-03-0363).

- A. Eblabla, X. Li, <u>M. Alathbah</u>, Z. Wu, J. Lees, and K. Elgaid, "Multi-Channel AlGaN/GaN Lateral Schottky Barrier Diodes on Low-Resistivity Silicon for Sub-THz Integrated Circuits Applications," *IEEE Electron Device Lett.*, vol. 40, no. 6, pp. 878–880, 2019, Doi: 10.1109/LED.2019.2912910.

#### **Conference papers:**

- <u>M. Alathbah</u>, A. Eblabla and K. Elgaid, "Frequency Doubler Based on a Lateral Multi-Channel GaN Schottky Barrier Diode for 5G Technology," 2020 13th International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM), Smolenice, Slovakia, 2020, pp. 14-18, Doi: 10.1109/ASDAM50306.2020.9393861.

- <u>M. Alathbah</u>, A. Eblabla and K. Elgaid, "Novel Slotted mmWave CPW Branch Line Coupler for MMIC and Sub-THz Applications," *2020 13th International Conference on Advanced Semiconductor Devices and Microsystems* (ASDAM), Smolenice, Slovakia, 2020, pp. 111-114, Doi: 10.1109/ASDAM50306.2020.9393863.

- A. Eblabla, <u>M. Alathbah</u>, Z. Wu, J. Lees and K. Elgaid, "Membrane Supported GaN CPW Structures for High-frequency and High-power Applications," *2019 IEEE Asia-Pacific Microwave Conference (APMC)*, Singapore, Singapore, 2019, pp. 1179-1181, Doi: 10.1109/APMC46564.2019.9038731.

# TABLE OF CONTENTS

| Abstra  | act     |                                                                 | i    |

|---------|---------|-----------------------------------------------------------------|------|

| Ackno   | wledgr  | nent                                                            | iii  |

| Public  | ations. |                                                                 | iv   |

| Table   | of Cont | ents                                                            | v    |

| List of | Tables  | 5                                                               | ix   |

| List of | Figure  | °S                                                              | X    |

| 1.      | Introd  | uction                                                          | 1    |

|         | 1.1.    | GaN Technology: An Overview                                     | 1    |

|         | 1.2.    | History of GaN Technology Advancement                           | 6    |

|         | 1.3.    | GaN Future Forecast                                             | 6    |

|         | 1.4.    | Current Research Challenges                                     | 8    |

|         | 1.5.    | Research Aim                                                    | 10   |

|         | 1.6.    | AIGaN/GaN RF HEMTs Literature Review                            | 10   |

|         | 1.7.    | Thesis Structure                                                | 13   |

| 2.      | GaN H   | EMTs Theoretical Background and Characterisation                | . 14 |

|         | 2.1.    | Polarisations in AlGaN/GaN Heterostructure                      | 14   |

|         |         | 2.1.1. Spontaneous Polarisation                                 | 15   |

|         |         | 2.1.2. Piezoelectric Polarisation                               | 16   |

|         |         | 2.1.3. HEMT Structure Engineering via AlGaN/GaN Polarisations . | 16   |

|         |         | 2.1.4. 2DEG Sheet Density Simulation                            | 20   |

|         | 2.2.    | GaN-HEMT Growth Basics                                          | 22   |

|         |         | 2.2.1. Molecular Beam Epitaxy                                   | 22   |

|         |         | 2.2.2. Metal Organic Chemical Vapor Deposition                  | 23   |

|         | 2.3.    | Standard Substrates for GaN-HEMT                                | 24   |

|         |         | 2.3.1. Silicon                                                  | 25   |

|         |         | 2.3.2. Silicon Carbide                                          | 26   |

|         | 2.4.    | Epitaxial Layers of GaN-based HEMT                              | 26   |

|         |         | 2.4.1. Nucleation                                               | 27   |

|         |         | 2.4.2. Graded Buffer                                            | 29   |

|         |         | 2.4.3. Channel                                                  | 29   |

|         |         | 2.4.4. Spacer                                                   | 30   |

|    |       | 2.4.5.             | Barrier     |                                                | 31   |

|----|-------|--------------------|-------------|------------------------------------------------|------|

|    |       | 2.4.6.             | Cap Laye    | er                                             | 31   |

|    | 2.5.  | GaN H              | EMT Cont    | acts                                           | 32   |

|    |       | 2.5.1.             | Ohmic Co    | ontacts                                        | 32   |

|    |       | 2.5.2.             | Schottky    | Contacts                                       | 34   |

|    |       | 2.5.3.             | Drain/Sou   | urce Ohmic Electrode Characterisation          | 34   |

|    | 2.6.  | Operat             | ional Princ | iples of HEMT and Characterisation Parameters  | 36   |

|    | 2.7.  | High F             | requency (  | Dperation                                      | 41   |

|    | 2.8.  | Small S            | Signal Circ | uit Model                                      | 46   |

|    | 2.9.  | Large              | Signal Cha  | racteristics                                   | 50   |

| 3. | GaN H | IEMT F             | abricatio   | n Techniques and Process                       | . 53 |

|    | 3.1.  | Materia            | al Growth a | and Design                                     | 53   |

|    | 3.2.  | Lithogr            | aphy        | -                                              | 56   |

|    |       | 3.2.1.             | Photolithe  | ography                                        | 56   |

|    |       | 3.2.2.             | E-beam l    | ithography                                     | 57   |

|    | 3.3.  | Metalliz           | zation and  | Lift-Off                                       | 57   |

|    |       | 3.3.1.             | Evaporat    | ion                                            | 58   |

|    |       | 3.3.2.             | Metal Lift  | -Off Process                                   | 59   |

|    | 3.4.  | Rapid <sup>·</sup> | Thermal A   | nnealing                                       | 62   |

|    | 3.5.  | Etching            | j           |                                                | 62   |

|    |       | 3.5.1.             | Reactive    | Ion Etch                                       | 63   |

|    |       | 3.5.2.             | Inductive   | ly Coupled Plasma                              | 63   |

|    | 3.6.  | Dielect            | ric Deposit | ion                                            | 65   |

|    | 3.7.  | Substra            | ate Prepar  | ation                                          | 65   |

|    | 3.8.  | Layout             | Design an   | d Fabrication Process                          | 65   |

|    |       | 3.8.1.             | Alignmen    | t Markers                                      | 66   |

|    |       | 3.8.2.             | Ohmic Co    | ontacts                                        | 68   |

|    |       | 3.8.3.             | Device Is   | olation                                        | 70   |

|    |       | 3.8.4.             | Dielectric  | Passivation and Insulation                     | 72   |

|    |       | 3.8.5.             | Schottky    | Contact Formation                              | 73   |

|    |       | 3.8.6.             | Probing E   | Bond-Pads, Field Plates and Transmission Lines | 74   |

| 4. | Passi | ve and             | Active De   | evices For GaN on Si                           | . 77 |

|    | 4.1.  | Coplan             | ar Transm   | ission Lines                                   | 77   |

|    |       | 4.1.1.             | Coplanar    | Transmission Lines Theory and Design           | 77   |

|    |       | 4.1.2.             | CPW Tra     | nsmission Lines on Si and SiC Substrates       | 80   |

|    |       | 4.1.3.             | RF Beha     | vior on GaN-on-LR Si Substrate                 | 81   |

|    |       |                    | 4.1.3.1.    | CPW Lines S-Parameters                         | 81   |

|    |       |                    | 4.1.3.2.    | CPW Lines Propagation Analysis                 | 86   |

|    |       | 4.1.3.3. Telegrapher's Equation and RLGC Model                  | 89   |

|----|-------|-----------------------------------------------------------------|------|

|    |       | 4.1.3.4. CPW Lines Substrate Comparison                         | 93   |

|    |       | 4.1.3.5. RF Leakage PCM                                         | 95   |

|    | 4.2.  | MIM Capacitors                                                  | 99   |

|    |       | 4.2.1. MIM Capacitors Theory and Design                         | 99   |

|    | 4.3.  | MMIC Planar Meander Inductor                                    | 104  |

|    |       | 4.3.1. MMIC Inductor Theory and Design                          | 104  |

|    |       | 4.3.2. Meander Inductor RF Performance                          | 105  |

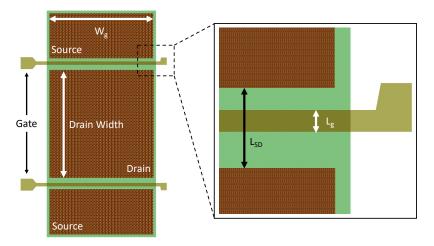

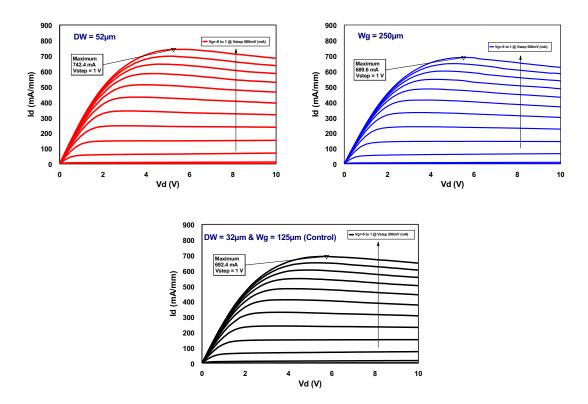

|    | 4.4.  | GaN HEMT Device Dimensions Analysis                             | 107  |

|    |       | 4.4.1. Growth of the Material                                   | 107  |

|    |       | 4.4.2. Device Process and Layout Definitions                    | 108  |

|    |       | 4.4.3. Measurements and Discussion                              | 109  |

|    | 4.5.  | Conclusion                                                      | 116  |

| 5. | The E | ffect of Miniature Mesa Extension for a Planar Submicron        | Gate |

|    | Form  | ation                                                           | 118  |

|    |       |                                                                 |      |

|    | 5.1.  | Review of Isolation Approaches                                  |      |

|    | 5.2.  | Gate-feed on a Miniature Mesa-Extension for a Planar Structure. |      |

|    |       | 5.2.1. Growth of the Material                                   |      |

|    |       | 5.2.2. Device Process                                           |      |

|    |       | 5.2.3. Design of the Proposed Devices                           |      |

|    |       | 5.2.4. Leakage Current & Device Isolation                       |      |

|    | 5.3.  | 5.2.5. DC and RF Performance                                    |      |

|    |       |                                                                 |      |

| 6. | GaN I | HEMT Small Signal Modelling                                     | 134  |

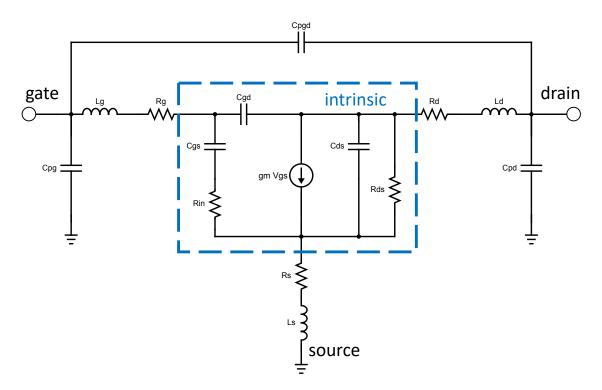

|    | 6.1.  | HEMT 16-Element Model                                           | 134  |

|    | 6.2.  | Extrinsic Parameters Extraction                                 | 135  |

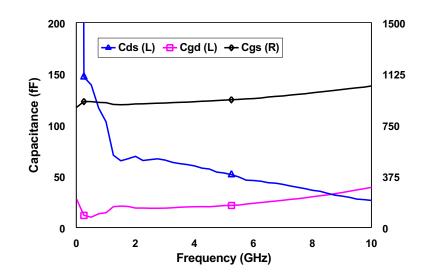

|    |       | 6.2.1. Parallel Capacitances                                    | 135  |

|    |       | 6.2.1.1. Open Structure                                         | 135  |

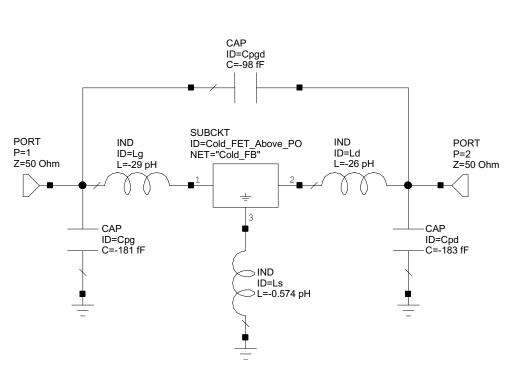

|    |       | 6.2.1.2. Cold-FET below Pinch-off                               | 137  |

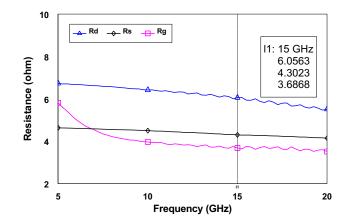

|    |       | 6.2.2. Series Inductances and Resistances                       | 140  |

|    |       | 6.2.2.1. Short Structure                                        | 141  |

|    |       | 6.2.2.2. Cold-FET above Pinch-off                               | 143  |

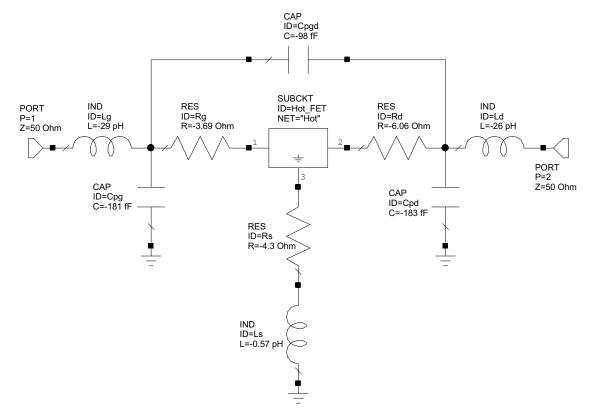

|    | 6.3.  | Intrinsic Parameters Extraction (Hot-FET)                       | 144  |

|    | 6.4.  | Summary                                                         | 152  |

| 7. | Nove  | GaN Schottky Barrier Diodes                                     | 153  |

|    | 7.1.  | SBD Theory                                                      | 154  |

|    | 7.2.  | Nonlinearities and Harmonics in SBD                             | 159  |

|    | 7.3.                | Series Resistance and Capacitance                                                                                       | 160     |

|----|---------------------|-------------------------------------------------------------------------------------------------------------------------|---------|

|    | 7.4.                | SBD Characterization                                                                                                    | 164     |

|    | 7.5.                | Reverse Breakdown Voltage                                                                                               | 166     |

|    | 7.6.                | Varactors in Frequency Convertors                                                                                       | 167     |

|    | 7.7.                | Layout and Design                                                                                                       | 169     |

|    | 7.8.                | Novel Trenched-Anode SBDs                                                                                               | 170     |

|    |                     | 7.8.1. DC Characteristics                                                                                               | 173     |

|    |                     | 7.8.2. RF Behavior and Small Signal Model                                                                               | 176     |

|    | 7.9.                | Summary                                                                                                                 | 179     |

|    |                     |                                                                                                                         |         |

| 8. | Conc                | lusions and Future Work                                                                                                 | 180     |

| 8. | <b>Conc</b><br>8.1. | Iusions and Future Work                                                                                                 |         |

| 8. |                     |                                                                                                                         | 180     |

| 8. |                     | Novel Planar Gate Formation                                                                                             |         |

| 8. |                     | Novel Planar Gate Formation<br>8.1.1. Summary and Key Findings                                                          | 180<br> |

| 8. | 8.1.                | Novel Planar Gate Formation<br>8.1.1. Summary and Key Findings<br>8.1.2. Future Research                                |         |

| 8. | 8.1.                | Novel Planar Gate Formation<br>8.1.1. Summary and Key Findings<br>8.1.2. Future Research<br>Novel Multi-trenched Diodes |         |

# LIST OF TABLES

| <b>Table 1.1.</b> Physical parameters comparison of epitaxial GaN layers in comparison with other materials at 300 K [4], [5]                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2. Various figures of merits for different material in comparison with GaN5                                                                               |

| Table 1.3. Literature review of the state-of-the-art GaN RF-HEMT devices         10                                                                               |

| Table 2.1. GaN epilayer common growth substrates and their key properties [116]25                                                                                 |

| Table 2.2. Work function of various metals for Schottky [125]                                                                                                     |

| Table 3.1. VdP parameters and measurements of GaN on Si used in this project55                                                                                    |

| Table 3.2. TLM structure contact resistance and length transfer70                                                                                                 |

| Table 3.3. Bond pads and CPW lines process    74                                                                                                                  |

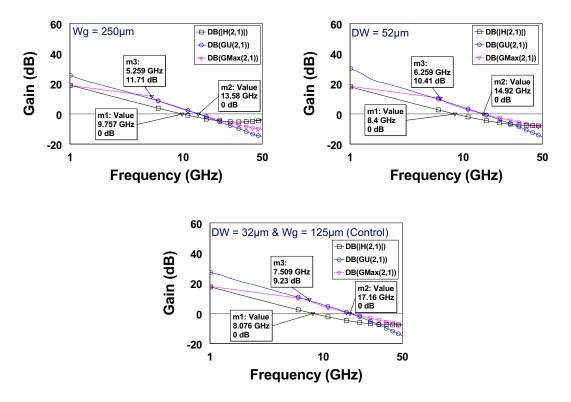

| <b>Table 4.1.</b> Summary of DC and RF parameters of HEMT with different device dimensions                                                                        |

| <b>Table 4.2.</b> Dimension scaled HEMT devices small-signal model parameters biased at $V_d$ =4.5 V and $V_g$ = -2.5V with an RF power injection level at -20dBm |

| Table 5.1. Parameters of HEMT with different gate formations         132                                                                                          |

| <b>Table 5.2.</b> HEMT small-signal model parameters biased at $V_d$ =4.5 V and $V_g$ = -2.5V withan RF power injection level at -20dBm                           |

| <b>Table 6.1.</b> HEMT small-signal model parameters biased at $V_d$ =4.5 V and $V_g$ = -2.5V withan RF power injection level at -20dBm                           |

| Table 7.1. Dimensions of the fabricated devices    173                                                                                                            |

| Table 7.2. The SBD small signal model and I-V extracted key parameters                                                                                            |

# LIST OF FIGURES

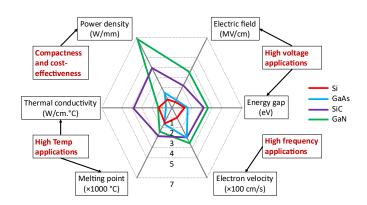

| Figure 1.1. Summary of GaN against Si, GaAs and SiC properties with the corresponding advantages and applications                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

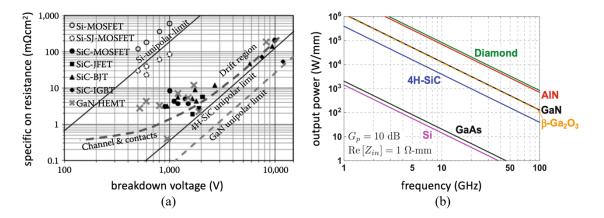

| <b>Figure 1.2.</b> Specific on resistance as a function of breakdown voltage (a) and output power density as a function of frequency (b) for various materials, [4], [10], respectively  |

| <b>Figure 1.3.</b> GaN market forecast split by the type of applications for 2025 and (b) by device types and region for year 2027, [18], [19], respectively                             |

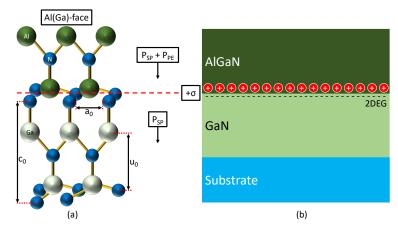

| <b>Figure 2.1.</b> Crystal structure of Ga-face AlGaN/GaN (a), the induced polarizations and their directions in AlGaN/GaN Heterostructure (b)15                                         |

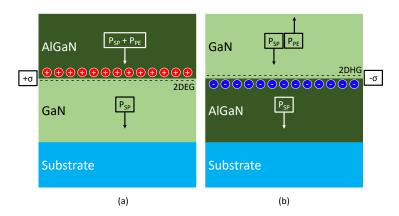

| <b>Figure 2.2.</b> Polarisation's direction and charge density ( $\sigma$ ) polarity with respect to AlGaN tensile strain (a) vs GaN compressive strain (b) in a Ga-face heterostructure |

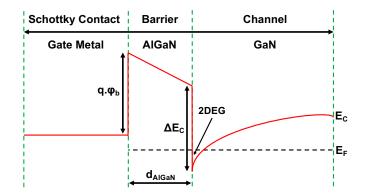

| Figure 2.3. AIGaN/GaN heterostructure HEMT band diagram19                                                                                                                                |

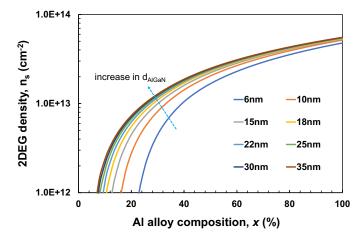

| <b>Figure 2.4.</b> 2DEG sheet carrier concentration as a function of AI composition factor, <i>x</i> , of AI <sub>x</sub> Ga <sub>1-x</sub> N22                                          |

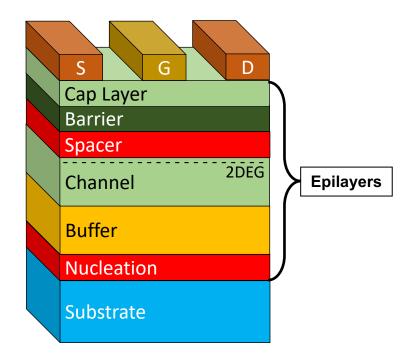

| Figure 2.5. Basic HEMT device and wafer structure27                                                                                                                                      |

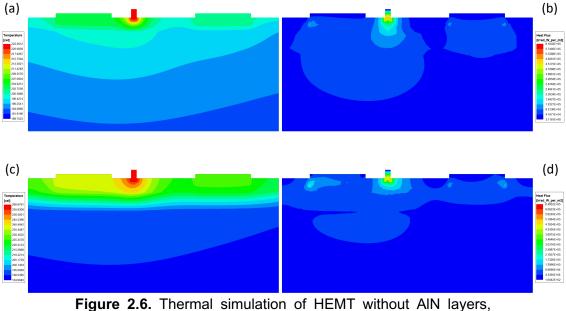

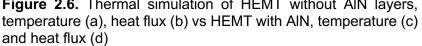

| <b>Figure 2.6.</b> Thermal simulation of HEMT without AIN layers, temperature (a), heat flux (b) vs HEMT with AIN, temperature (c) and heat flux (d)                                     |

| Figure 2.7. Temperature distribution profile from top to bottom of the GaN/Si wafers .29                                                                                                 |

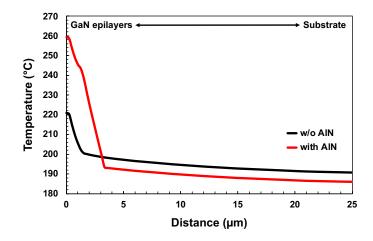

| Figure 2.8. AIGaN/AIN/GaN HEMT (a) energy band diagram and (b) 2DEG sheet concentration [120]30                                                                                          |

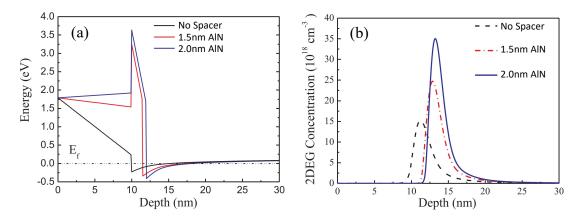

| Figure 2.9. 2DEG sheet carrier concentration as a function of the GaN Cap layer31                                                                                                        |

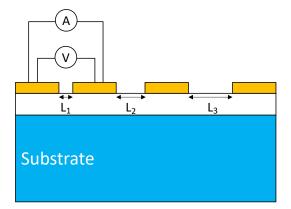

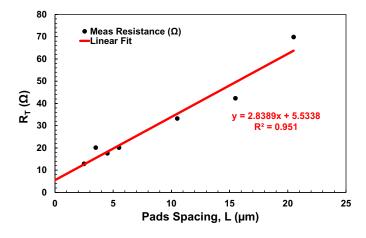

| Figure 2.10. Ohmic contact resistance LTLM setup                                                                                                                                         |

| Figure 2.11. Measured total resistance as a function of gap spacing35                                                                                                                    |

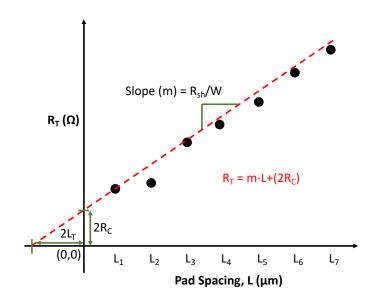

| Figure 2.12. AIGaN/GaN HEMT biasing configuration and the output <i>I-V</i> characteristics                                                                                              |

| <b>Figure 2.13</b> . TCAD AlGaN/GaN HEMT simulation 2D layout with a device width of 125 μm40                                                                                            |

| Figure 2.14. $I_{ds}$ -V <sub>ds</sub> family curves of a TCAD simulated 125 $\mu$ m device of AlGaN/GaN HEMT and the transfer characteristics40                                         |

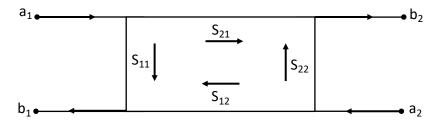

| Figure 2.15. Two-port network S-parameters41                                                                                                                                             |

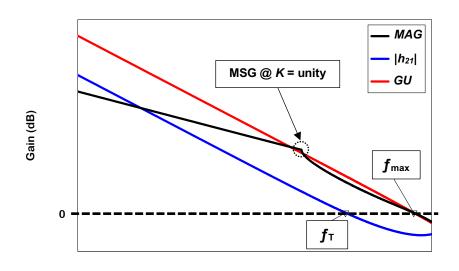

| <b>Figure 2.16.</b> MAG, $ h_{21} $ and <i>GU</i> as a function of operating frequency in log format44                                                                                   |

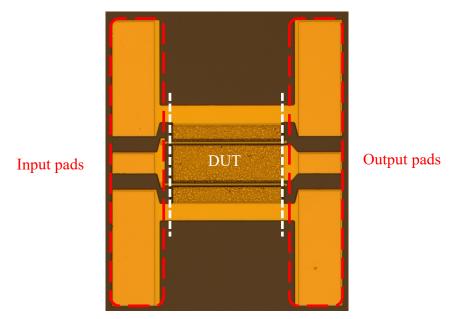

| Figure 2.17. DUT and the input and output CPW pads45                                                                                                                                     |

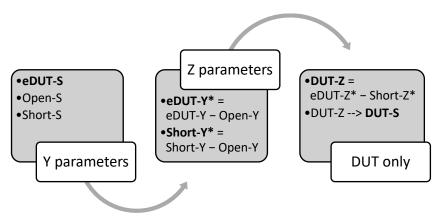

| Figure 2.18. RF measurements CPW pads de-embedding process flow45                                                                                                                        |

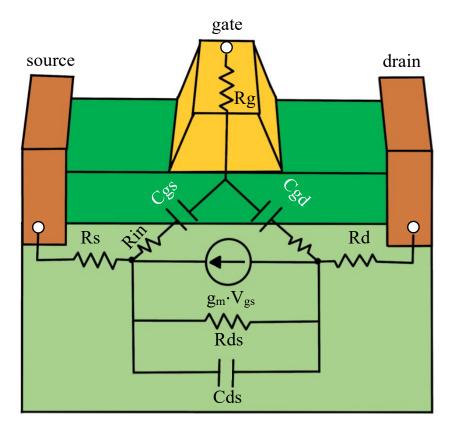

| Figure 2.19. GaN HEMT device cross-section with the electrical network superimposed on the diagram                                                                                       |

| Figure 2.20. AIGaN/GaN HEMT's small signal model47                                                                                                                                       |

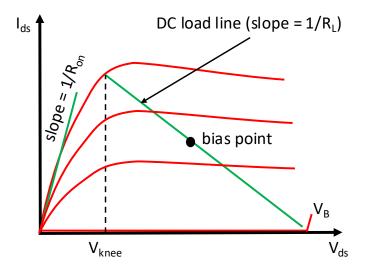

| Figure 2.21. AIGaN/GaN HEMT output I-V characteristics with class-A power amplifier DC load line                                                                                         |

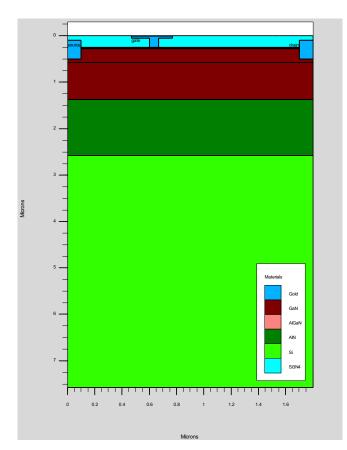

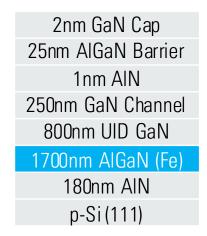

| Figure 3.1. GaN on Si wafer structure used in this project for HEMTs. <i>Epi layer of the shown structure was designed by Prof. David Wallis</i> 54                                      |

| Figure 3.2. Gated VdP test structure                                                                                                                                                     |

| Figure 3.3. VdP structure after processing mesa etch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

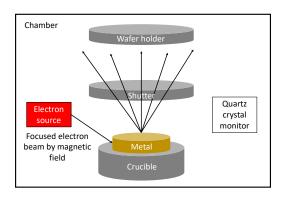

| Figure 3.4. Electron beam evaporation metallisation tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

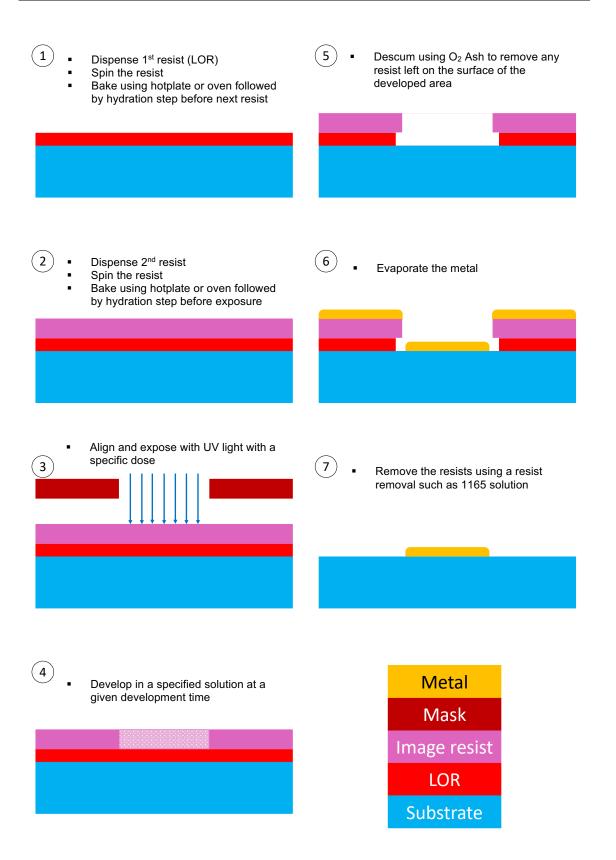

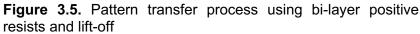

| Figure 3.5. Pattern transfer process using bi-layer positive resists and lift-off61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 3.6. Material-etch process schematic diagram64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

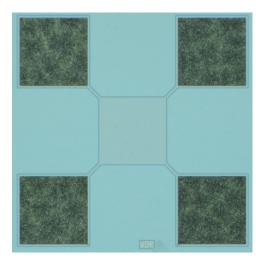

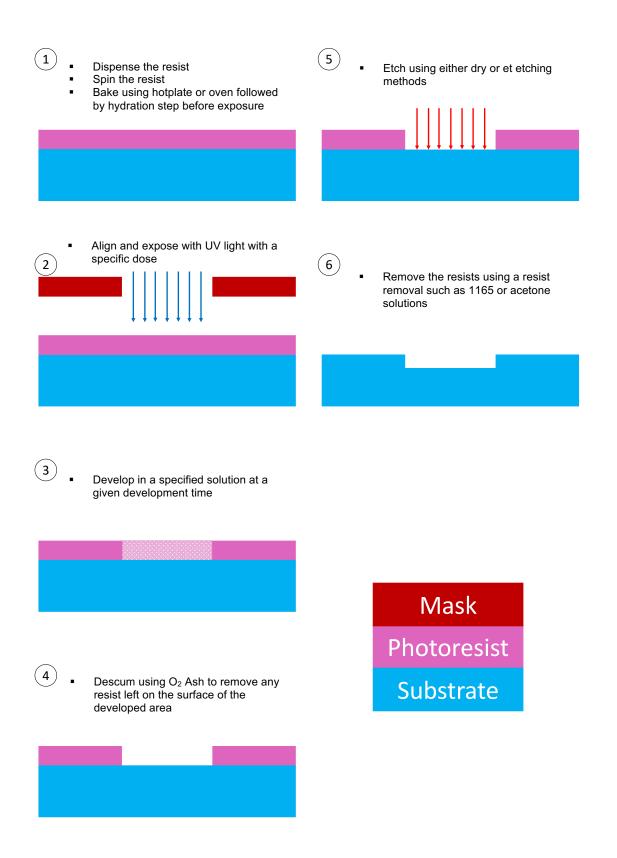

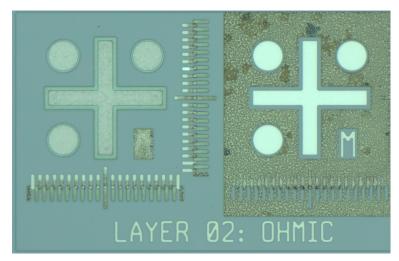

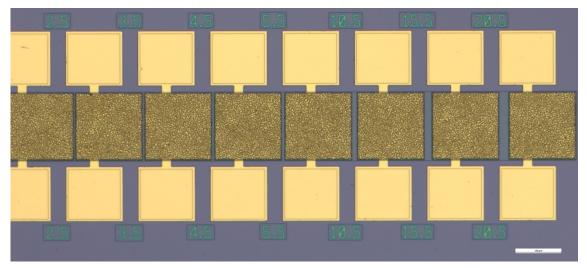

| Figure 3.7. Full mask layout of devices and PCMs66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

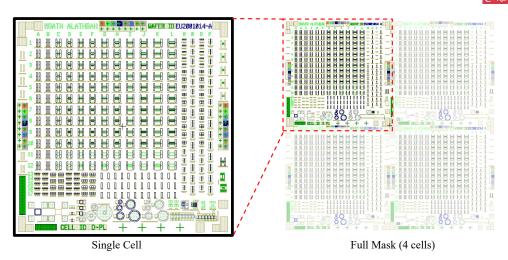

| Figure 3.8. Alignment markers for photolithography, e-beam and vernier for post-<br>process alignment inspection67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

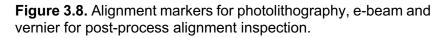

| <b>Figure 3.9.</b> Post-ohmic microscopic image of alignment markers, shown < 0.5µm alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3.10. Conventional LTLM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3.11. Ohmic contact measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

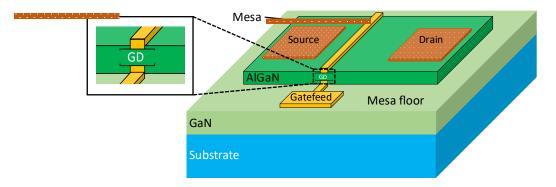

| Figure 3.12. Over-etched mesa with gate discontinuity (GD)71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

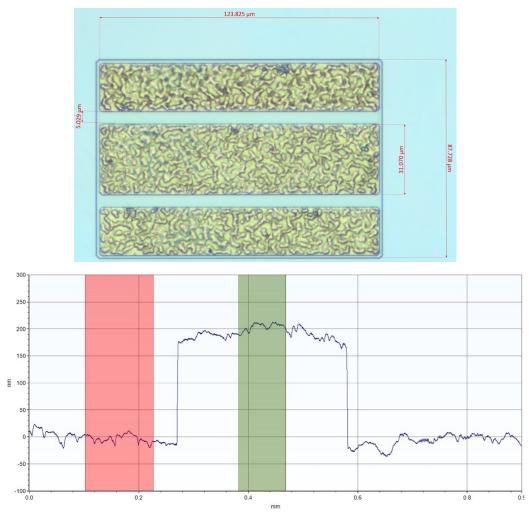

| Figure 3.13. HEMT device after 200nm mesa etch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

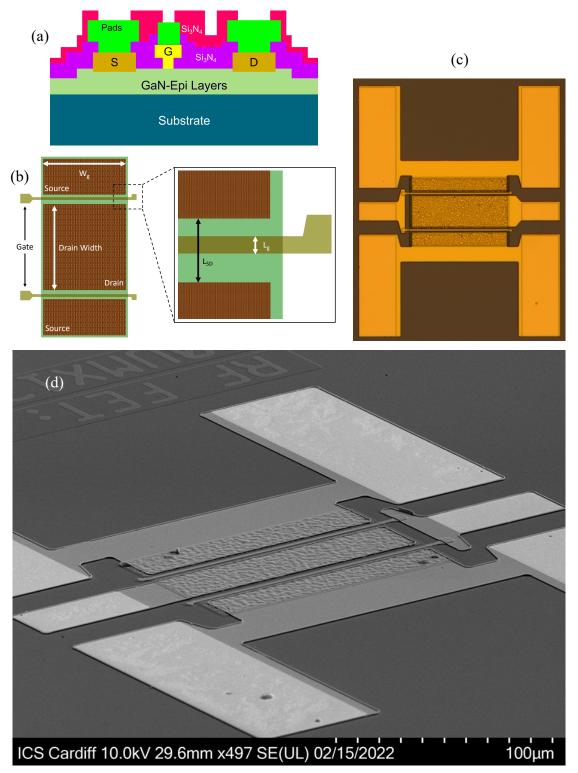

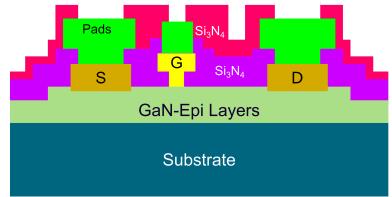

| <b>Figure 3.14.</b> HEMT cross-section view (a), layout geometry definitions (b), microscopic image of HEMT with bond pads in a CPW environment (c) and a SEM image (d)76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

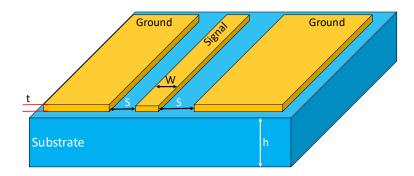

| Figure 4.1. Coplanar transmission line geometry    77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

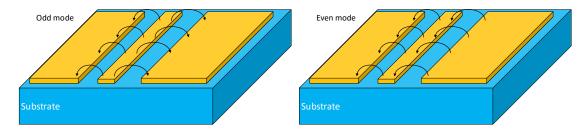

| Figure 4.2. Odd and even modes are supported by CPW78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

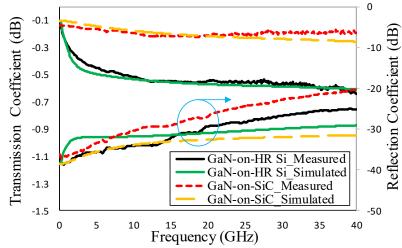

| Figure 4.3. Measured and simulated S-parameters of the fabricated CPW lines and simulated transmission coefficient for CPW on GaN-on-HR Si and SiC81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

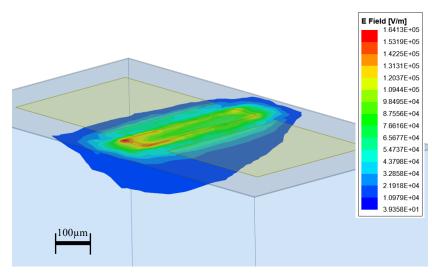

| Figure 4.4. CPW electromagnetic simulation with electric field distribution within the substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

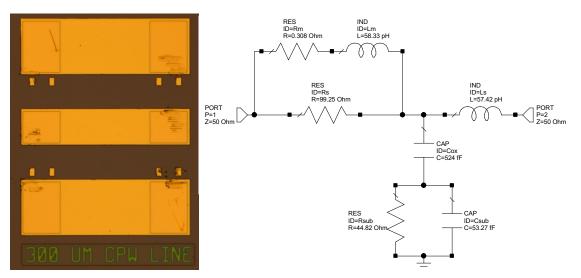

| Figure 4.5. CPW equivalent circuit model and microscopic image of the CPW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| transmission line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| transmission line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

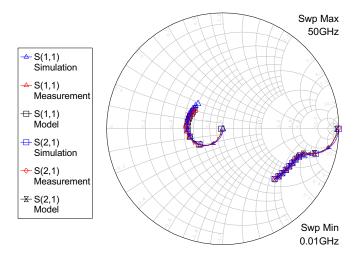

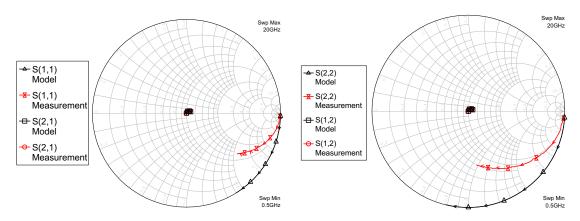

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>Figure 4.6.</b> S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

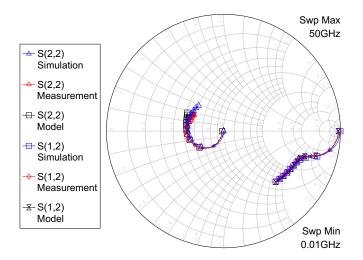

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled<br>300μm CPW line.84Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled<br>300μm CPW line.84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

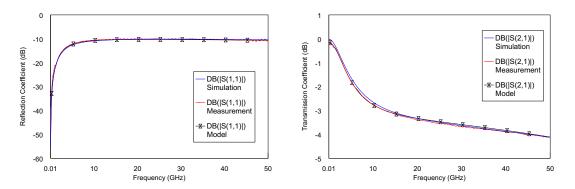

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on       85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

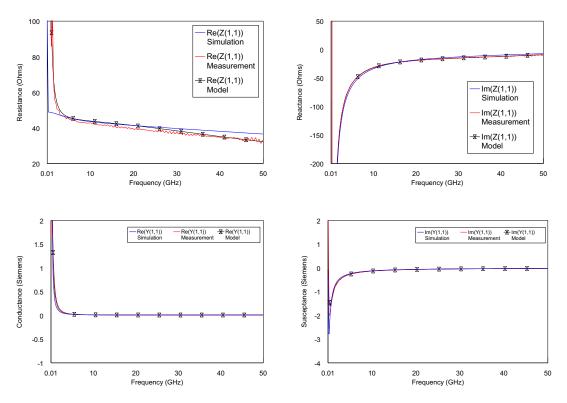

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

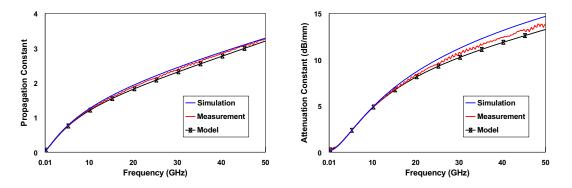

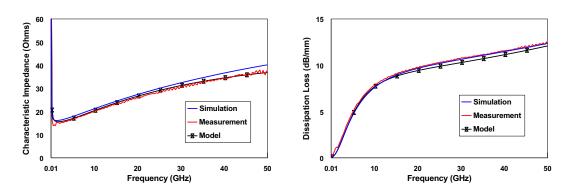

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86         Figure 4.10. Propagation constant and attenuation of CPW.       88         Figure 4.11. Characteristic impedance and dissipation losses of CPW transmission line       80                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86         Figure 4.10. Propagation constant and attenuation of CPW.       88         Figure 4.11. Characteristic impedance and dissipation losses of CPW transmission line 88                                                                                                                                                                                                                                                                                                                                               |

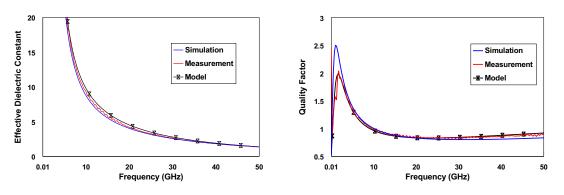

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86         Figure 4.10. Propagation constant and attenuation of CPW.       88         Figure 4.11. Characteristic impedance and dissipation losses of CPW transmission line 88       88         Figure 4.12. Effective dielectric constant and quality factor of CPW lines.       89         Figure 4.13. Single conductor with current flows and magnetic (H) and electric (E) fields       80                                                                                                                              |

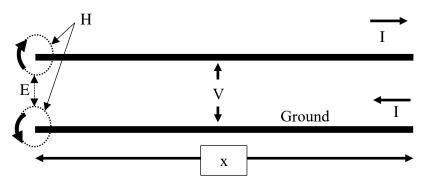

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86         Figure 4.10. Propagation constant and attenuation of CPW.       88         Figure 4.11. Characteristic impedance and dissipation losses of CPW transmission line       88         Figure 4.12. Effective dielectric constant and quality factor of CPW lines.       89         Figure 4.13. Single conductor with current flows and magnetic (H) and electric (E) fields patterns.       90         Figure 4.14. Telegrapher's equation representation of a short section of the conductor       90               |

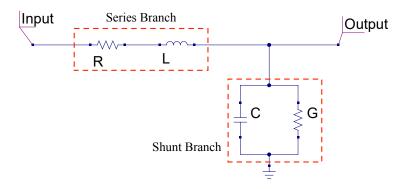

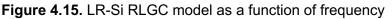

| Figure 4.6. S11 and S21 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.7. S22 and S12 smith chart plot of the simulated, measured, and modelled 300µm CPW line.       84         Figure 4.8. Reflection and transmission coefficients of CPW.       85         Figure 4.9. Resistance, reactance, conductance, and susceptance of the CPW line on LR-Si substrate.       86         Figure 4.10. Propagation constant and attenuation of CPW.       88         Figure 4.11. Characteristic impedance and dissipation losses of CPW transmission line       88         Figure 4.12. Effective dielectric constant and quality factor of CPW lines.       89         Figure 4.13. Single conductor with current flows and magnetic (H) and electric (E) fields patterns.       90         Figure 4.14. Telegrapher's equation representation of a short section of the conductor interconnect.       91 |

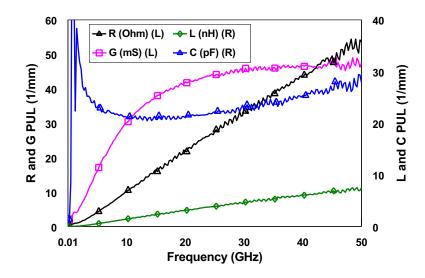

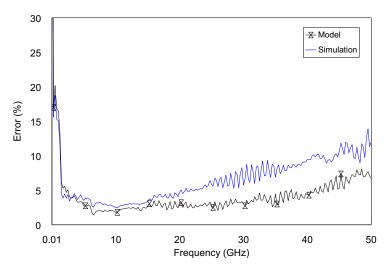

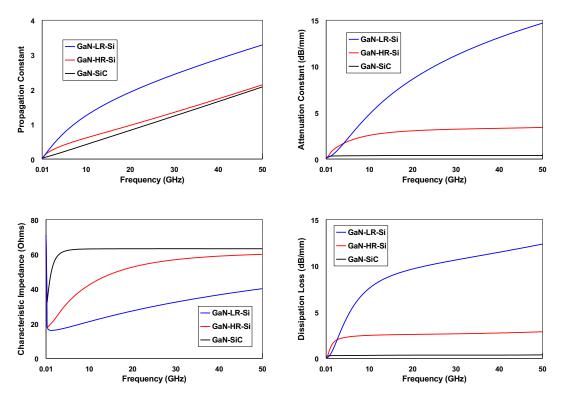

| Figure 4.18. RLGC model evaluation as a function of frequency for various substrates                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

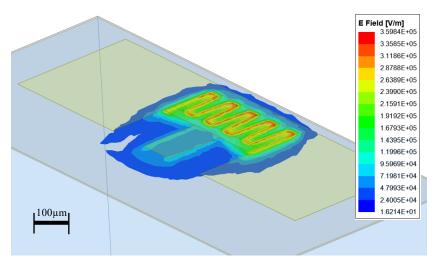

| <b>Figure 4.19.</b> RF leakage PCM electromagnetic simulation with electric field distribution within the substrate                                                                                                                                          |

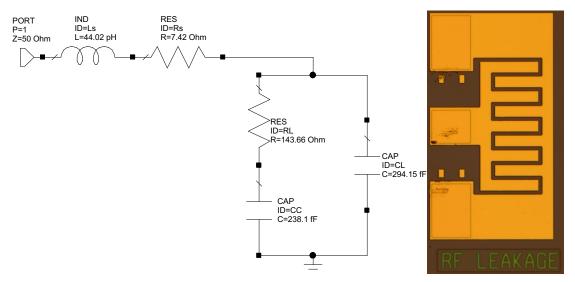

| Figure 4.20. RF leakage PCM circuit model for GaN-on-LR Si and the microscopic image                                                                                                                                                                         |

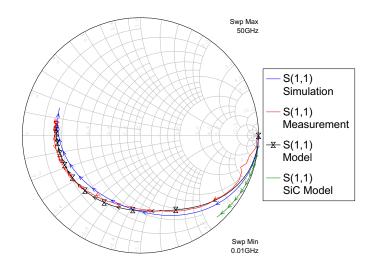

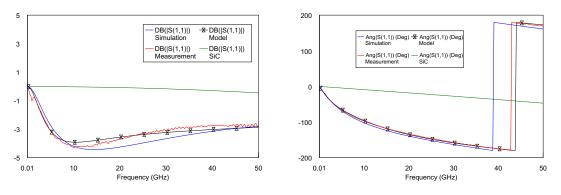

| Figure 4.21. S11 for RF leakage PCM97                                                                                                                                                                                                                        |

| Figure 4.22. Magnitude and phase of the RF Leakage PCM reflection coefficient97                                                                                                                                                                              |

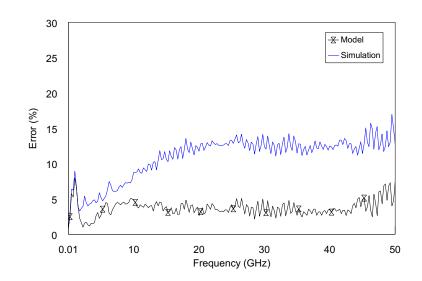

| Figure 4.23. Error between simulation/model and the fabricated RF leakage PCM structure                                                                                                                                                                      |

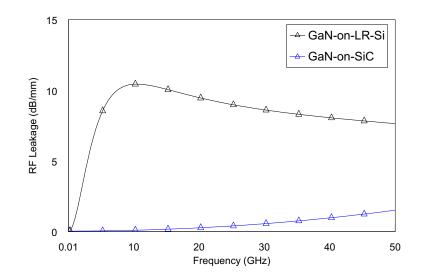

| Figure 4.24. RF leakage in (dB/mm) for GaN on Si and SiC                                                                                                                                                                                                     |

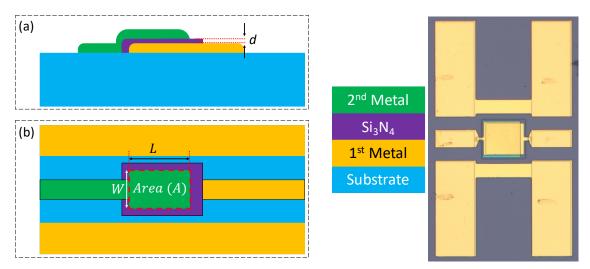

| Figure 4.25. Cross-section side view (a), top view layout (b) of a MIM series capacitor and a microscopic image                                                                                                                                              |

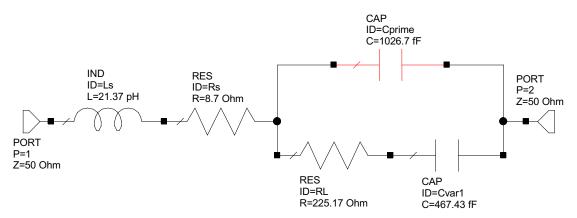

| Figure 4.26. Small-signal circuit model of the fabricated series MIM capacitors101                                                                                                                                                                           |

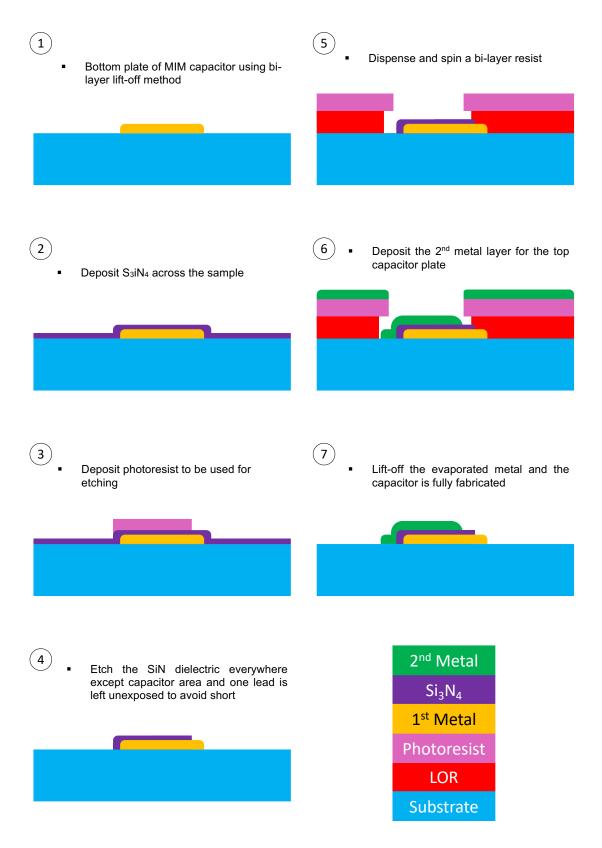

| Figure 4.27. MIM capacitor fabrication process                                                                                                                                                                                                               |

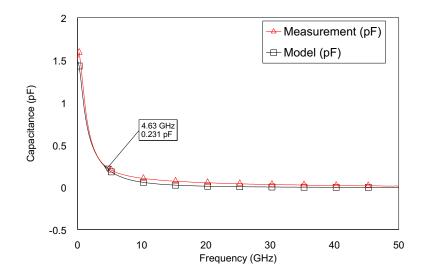

| <b>Figure 4.28</b> . Capacitance of a 50×50µm <sup>2</sup> series-MIM-capacitor103                                                                                                                                                                           |

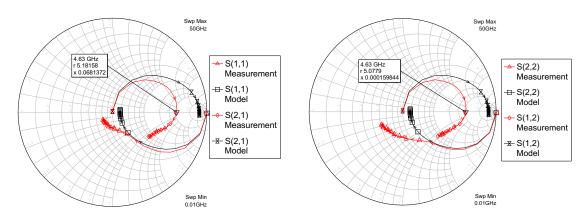

| <b>Figure 4.29.</b> Smith chart for 50×50µm <sup>2</sup> series-capacitor                                                                                                                                                                                    |

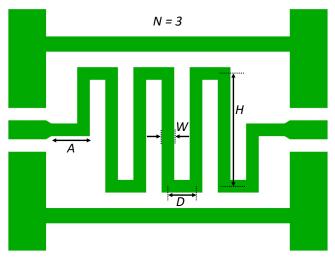

| Figure 4.30. Top view of a meander inductor layout                                                                                                                                                                                                           |

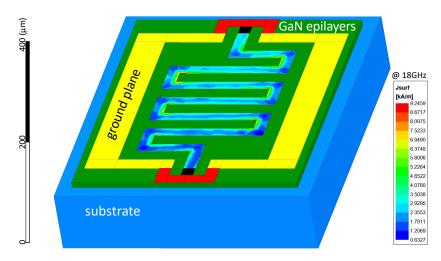

| Figure 4.31. Meander inductor 3D electromagnetic simulation                                                                                                                                                                                                  |

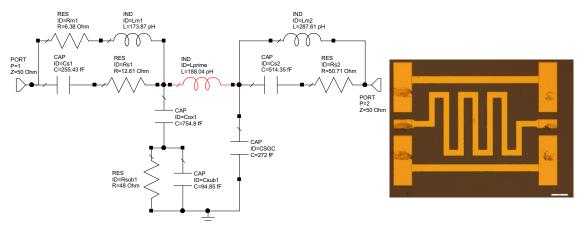

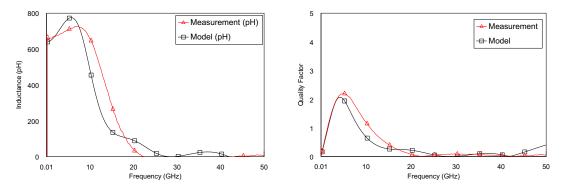

| Figure 4.32. Planar MMIC inductor circuit model and a microscopic image of the inductor                                                                                                                                                                      |

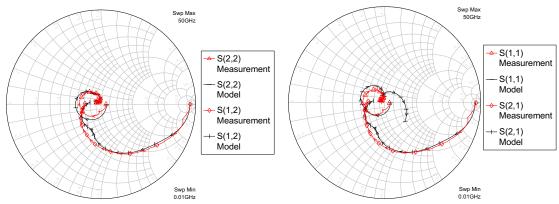

| Figure 4.33. Smith chart of the fabricated and model meander                                                                                                                                                                                                 |

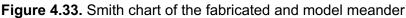

| Figure 4.34. Inductance and quality factor                                                                                                                                                                                                                   |

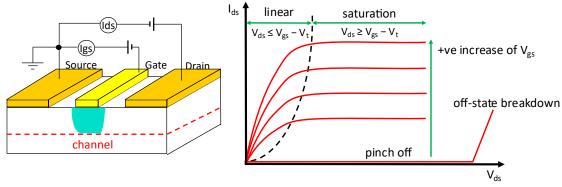

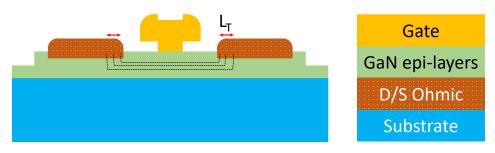

| Figure 4.35. Cross-section view of the HEMT fabricated in this project including field plates and 3 layers of $Si_3N_4$ passivation                                                                                                                          |

| Figure 4.36. GaN HEMT layout and device geometry definitions                                                                                                                                                                                                 |

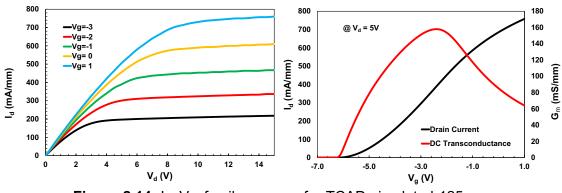

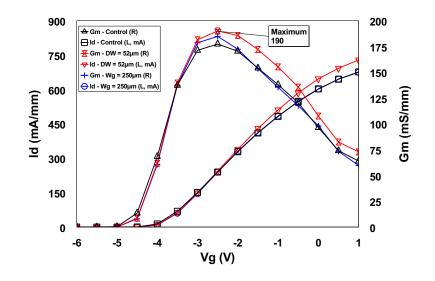

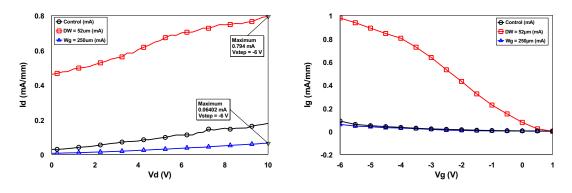

| Figure 4.37. I-V family curves of 2-finger with different $W_g$ and DW110                                                                                                                                                                                    |

| Figure 4.38. The transfer characteristics and the DC transconductance at $V_{ds}$ = 4.5V and $V_{gs}$ = -3V                                                                                                                                                  |

| <b>Figure 4.39.</b> Drain current ( $I_d$ ) and gate leakage ( $I_g$ ) at $V_g$ = -6V $V_d$ = 4.5V, respectively                                                                                                                                             |

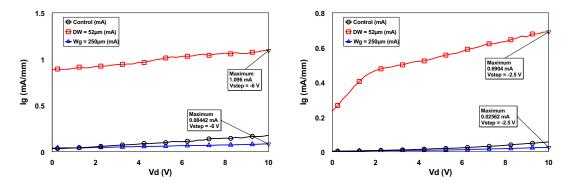

| Figure 4.40. Gate leakage as a function of drain bias with a gate voltage of -6V (left) and -2.5V (right)                                                                                                                                                    |

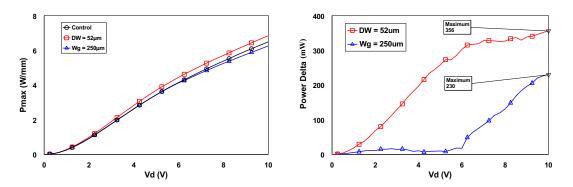

| <b>Figure 4.41.</b> Power exhibited by the devices at $V_g = 1.0V$                                                                                                                                                                                           |

| Figure 4.42. Current transport (dotted lines) between ohmic contacts and semiconductors in GaN HEMTs                                                                                                                                                         |

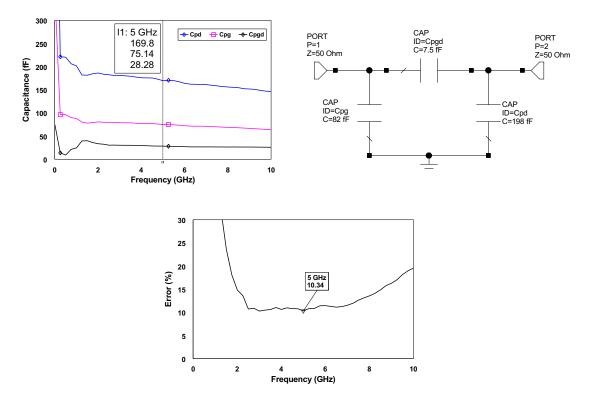

| <b>Figure 4.43.</b> GU, H21 and G <sub>MAX</sub> gains as a function of log frequency in GHz after pads de-embedding                                                                                                                                         |

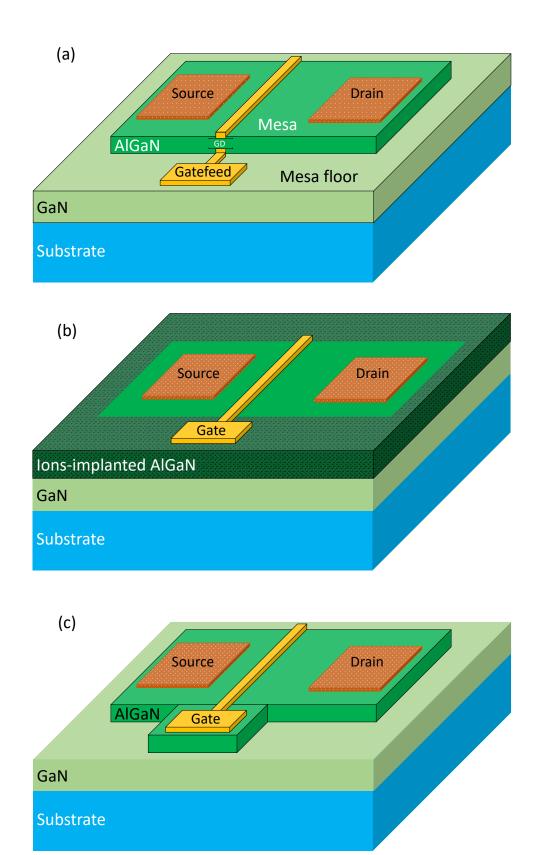

| <b>Figure 5.1.</b> Device isolation, (a) conventional mesa, (b) ion implantation, and (c) proposed planar device with a gate-feed on a miniature mesa-extension                                                                                              |

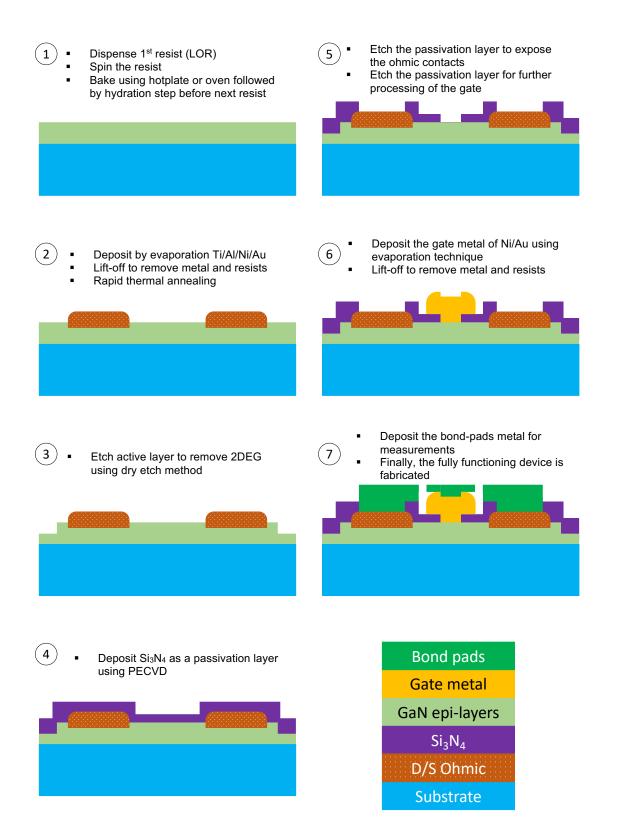

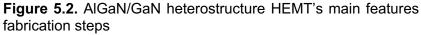

| Figure 5.2. AlGaN/GaN heterostructure HEMT's main features fabrication steps123                                                                                                                                                                              |

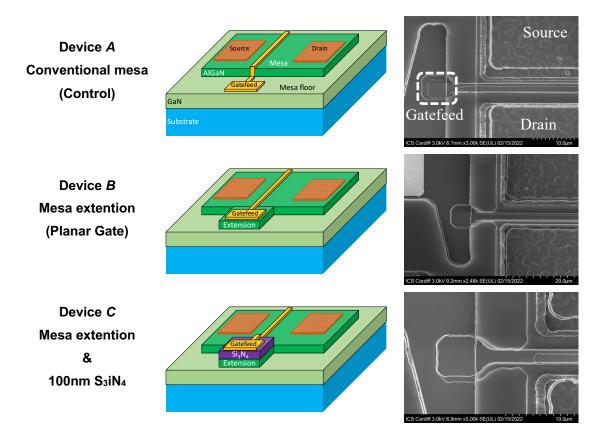

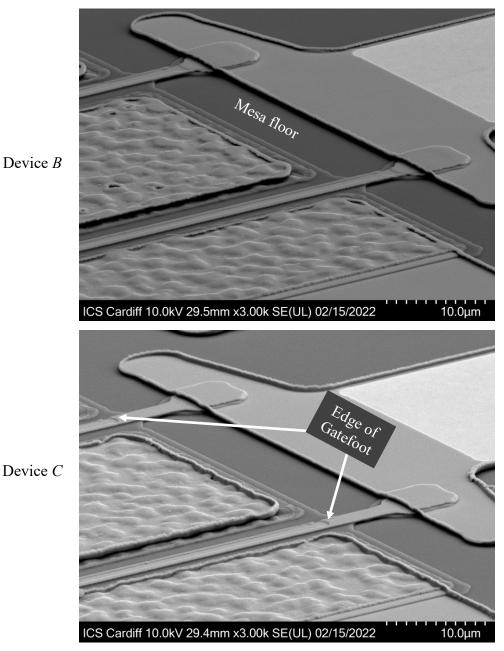

| <b>Figure 5.3.</b> 3D cross-section view and bird's-eye view SEM images of the proposed and control devices, all devices are passivated with $Si_3N_4$ but only the gate of device <i>C</i> is affected by its presence hence it is shown in the demo graphs |

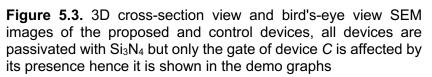

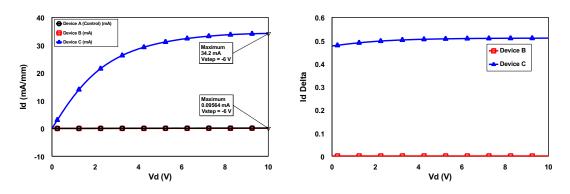

| <b>Figure 5.4.</b> Gate leakage in (a) cold mode where biasing is applied only to the gate contact and (b) hot mode where biasing is applied to both the gate and the drain contacts |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.5. Gate leakage as a function of drain bias, below and above pinch-off (a) and (b) respectively                                                                             |

| Figure 5.6. Drain leakage below pinch-off gate bias                                                                                                                                  |

| <b>Figure 5.7.</b> SEM images of device <i>B</i> (planar, mesa extension) and <i>C</i> (+100nm $Si_3N_4$ elevation)                                                                  |

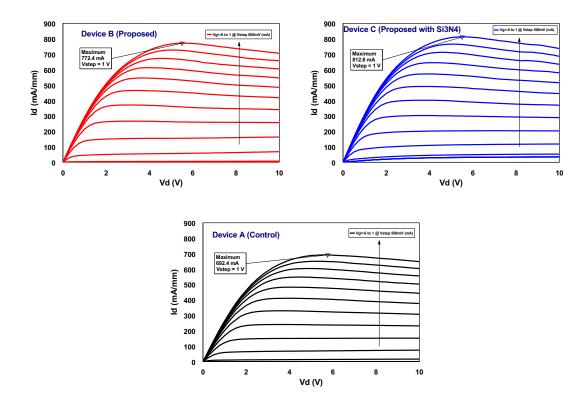

| Figure 5.8. I-V family curves of 2-finger 125µm wide device129                                                                                                                       |

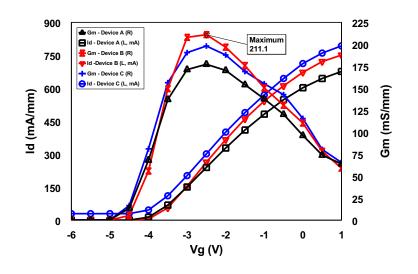

| Figure 5.9. The transfer characteristics and the DC transconductance                                                                                                                 |

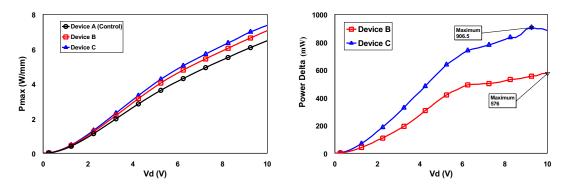

| <b>Figure 5.10.</b> Power exhibited by the devices at $V_g = 1.0V$                                                                                                                   |

| <b>Figure 5.11.</b> GU, H21 and G <sub>MAX</sub> gains as a function of log frequency in GHz after pads de-embedding                                                                 |

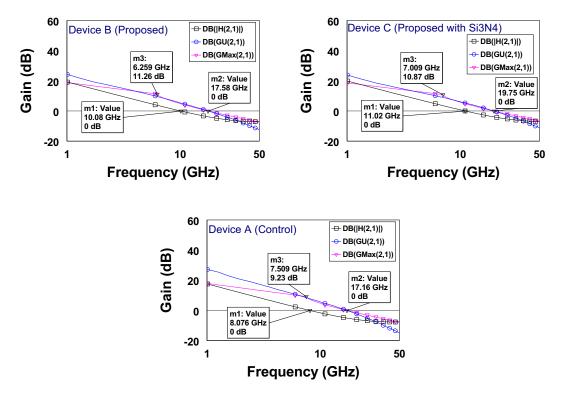

| Figure 6.1. Small-signal-model parameters extraction process                                                                                                                         |

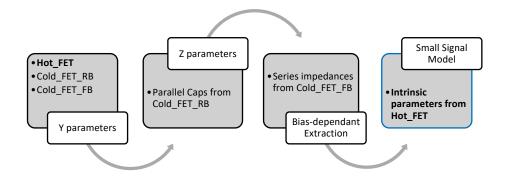

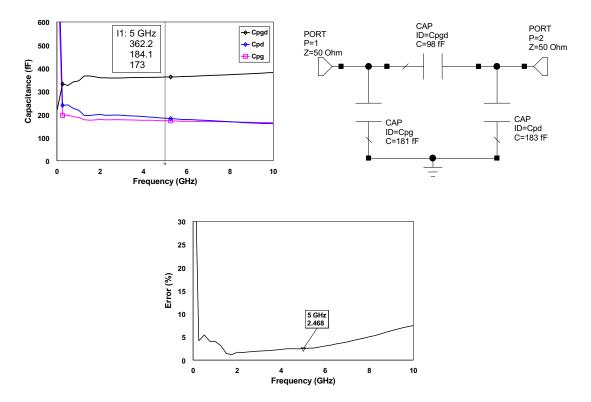

| Figure 6.2. Calculated parallel capacitance, small signal model and the error percentage between them                                                                                |

| Figure 6.3. Smith chart of the fabricated and model of the open137                                                                                                                   |

| <b>Figure 6.4.</b> Parallel capacitance measured at -8Vg and 0Vd, small signal model and the error percentage between them                                                           |

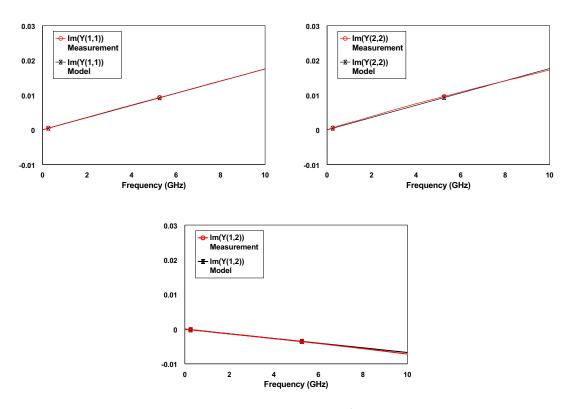

| <b>Figure 6.5.</b> Imaginary admittance (in $\Omega^{-1}$ ) of the HEMT in a reverse-bias and a cold-FET mode                                                                        |

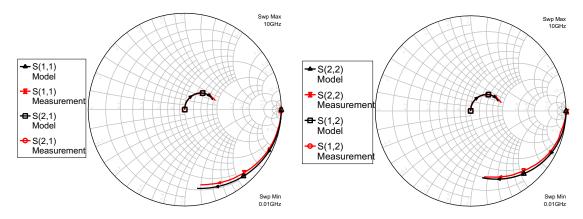

| Figure 6.6. Smith chart of the fabricated and model of the HEMT in a reverse-bias and a cold-FET mode                                                                                |

| Figure 6.7. S-parameters of the fabricated and model of the HEMT in a reverse-bias and a cold-FET mode                                                                               |

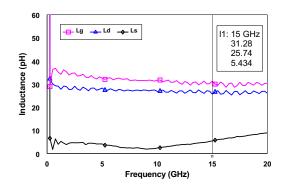

| Figure 6.8. Series inductances from short circuit structure                                                                                                                          |

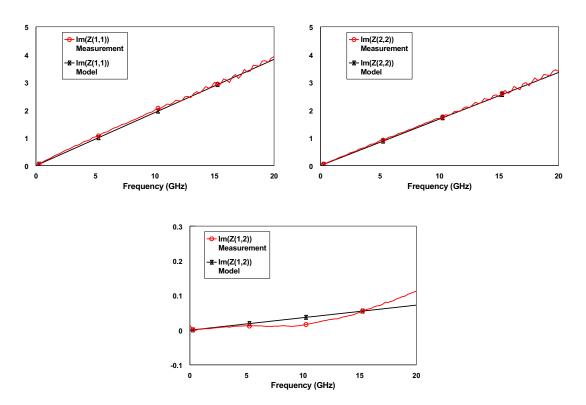

| <b>Figure 6.9.</b> Imaginary impedance (in $\Omega$ ) of the short test fixture                                                                                                      |

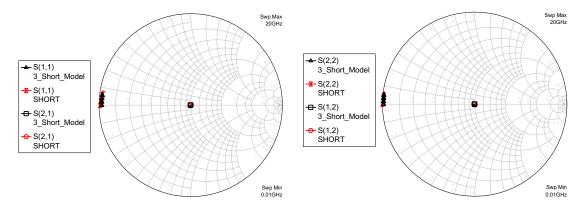

| Figure 6.10. Smith chart S-parameters of the short test fixture                                                                                                                      |

| Figure 6.11. De-embedding the extrinsic reactive impedances                                                                                                                          |

| Figure 6.12. Series resistances from cold-FET in a forward-bias                                                                                                                      |

| Figure 6.13. De-embedding the extrinsic components                                                                                                                                   |

| <b>Figure 6.14.</b> Intrinsic parallel capacitances between the device three terminals at obtained at $V_d$ =4.5 V and $V_g$ = -2.5V                                                 |

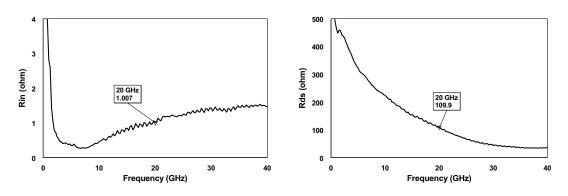

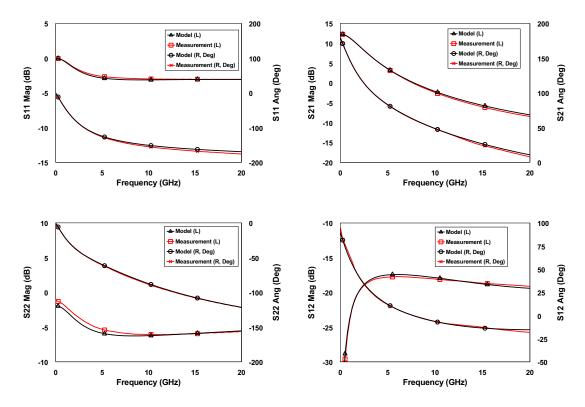

| Figure 6.15. Input and output resistances                                                                                                                                            |

| <b>Figure 6.16.</b> RF transconductance of 2-finger HEMT DW = 32µm and Wg = 125µm 147                                                                                                |

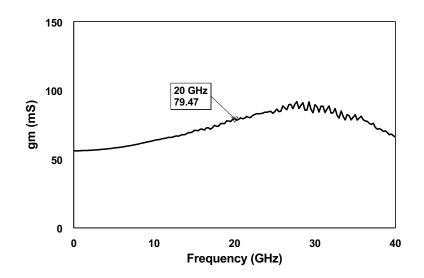

| <b>Figure 6.17.</b> Fabricated 2-finger HEMT small signal model obtained at $V_d$ =4.5 V and $V_g$ = -2.5V post-optimisation                                                         |

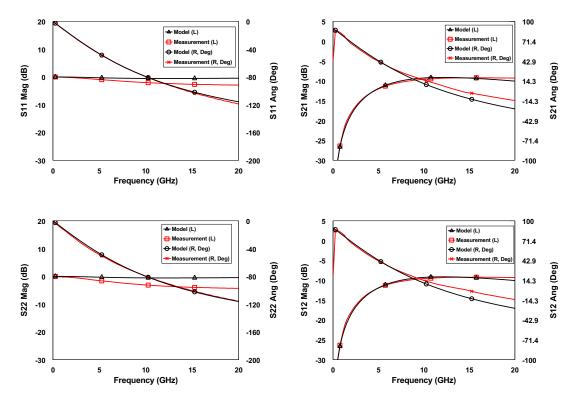

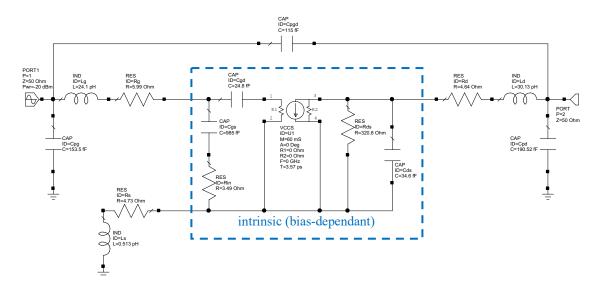

| Figure 6.18. S-parameters of a HEMT small signal model vs measurement in magnitude and phase                                                                                         |

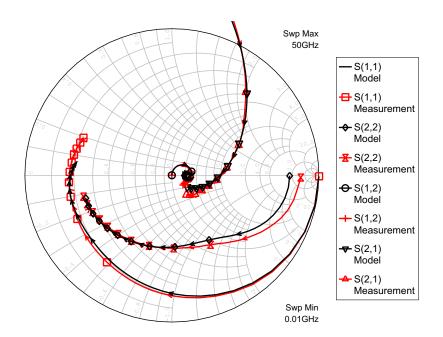

| Figure 6.19. HEMT small signal model vs measurement S-parameters                                                                                                                     |

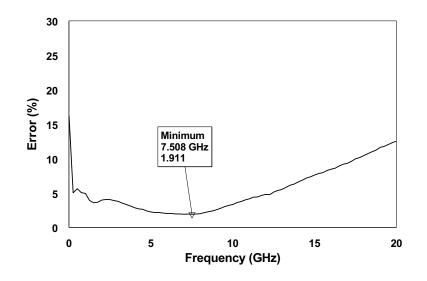

| Figure 6.20. Error percentage between the model and measurement data                                                                                                                 |

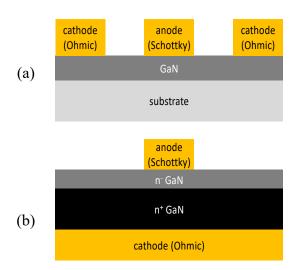

| Figure 7.1. Lateral (a) and vertical (b) structures GaN-based SBDs154                                                                                                                |

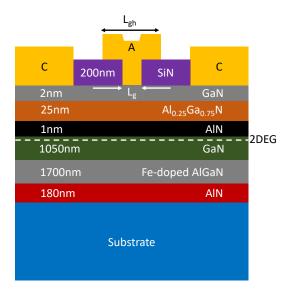

| Figure 7.2. Cross-section view of the fabricated SBDs and the GaN epilayers155                                                                                                       |

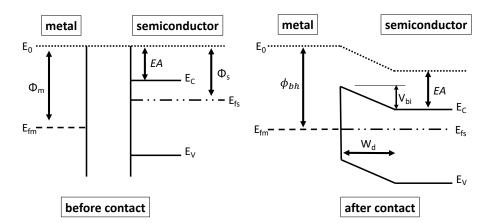

| Figure 7.3. Energy band diagram of a Schottky barrier before and after contact156                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

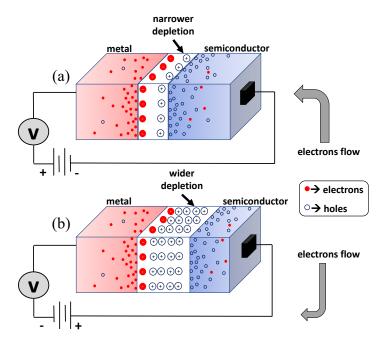

| <b>Figure 7.4.</b> Schottky diode mode of operation as a function of the applied potential, (a) forward (varistor) and (b) reverse (varactor)158                                                              |

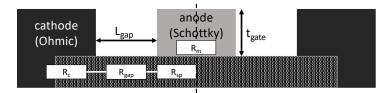

| Figure 7.5. Physical representation of the resistive origin in SBD                                                                                                                                            |

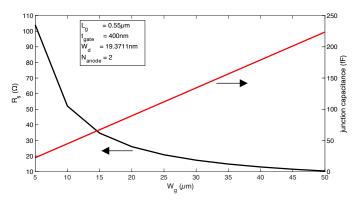

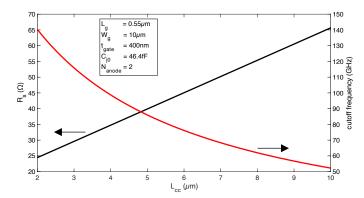

| Figure 7.6. The SBD series resistance and cutoff frequency as a function of its width                                                                                                                         |

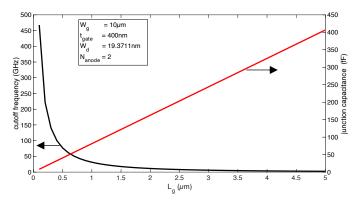

| Figure 7.7. The SBD series resistance and cutoff frequency as a function of the cathode-<br>cathode distance         164                                                                                      |

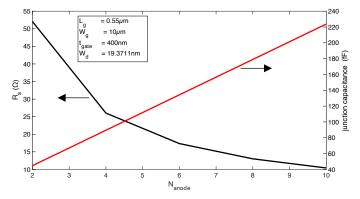

| Figure 7.8. The SBD junction capacitance and cutoff frequency as a function of its length                                                                                                                     |

| Figure 7.9. The SBD series resistance and capacitance as a function of the number of anode fingers                                                                                                            |

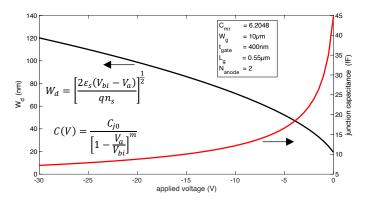

| Figure 7.10. Junction capacitance and depletion width as a function of the reversed applied voltage                                                                                                           |

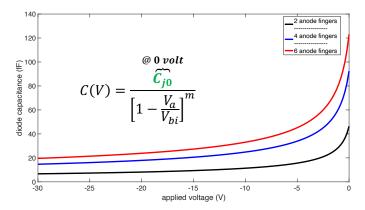

| Figure 7.12. The SBD capacitance as a function of the applied reversed voltage for a different finger-number                                                                                                  |

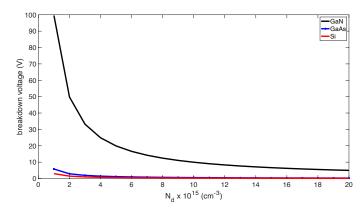

| Figure 7.13. The SBD breakdown voltage as a function of the doping density or electron concentration                                                                                                          |

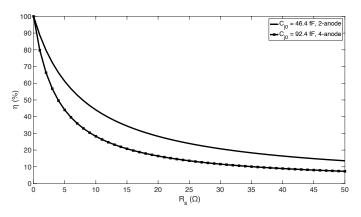

| Figure 7.14. The SBD conversion efficiency as a function of its series resistance168                                                                                                                          |

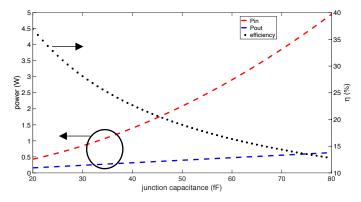

| Figure 7.15. The SBD conversion efficiency and input/output power as a function of its junction capacitance                                                                                                   |

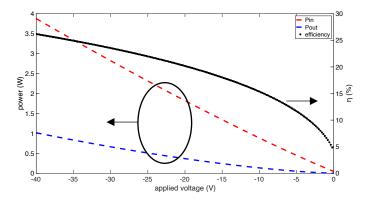

| Figure 7.16. The SBD conversion efficiency and input/output power as a function of the applied voltage                                                                                                        |

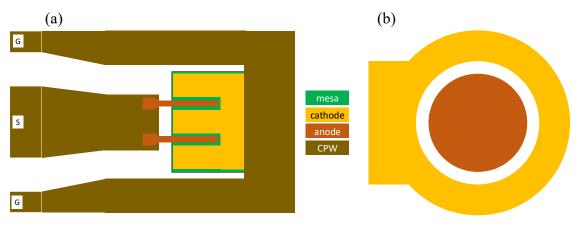

| <b>Figure 7.17.</b> The actual layouts for (a) the embedded 2-anode (2-finger) RF SBD in CPW environment and (b) large area circular DC diode                                                                 |

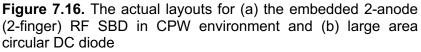

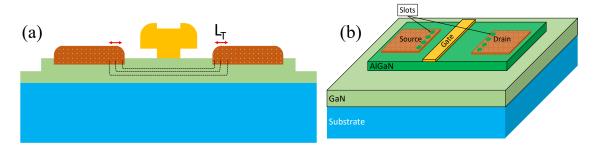

| <b>Figure 7.18.</b> (a) Cross-sectional view, (b) scanned-electron microscope (SEM) image, and (c) top-view of the multi-channel SBDs, and (d) Cross-sectional representation of the tri-anode along line AA' |

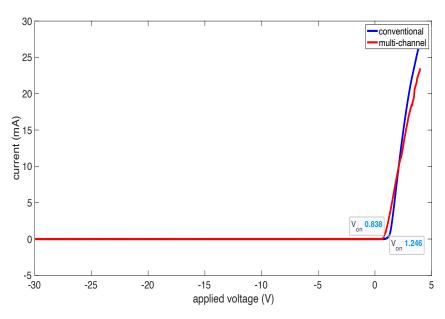

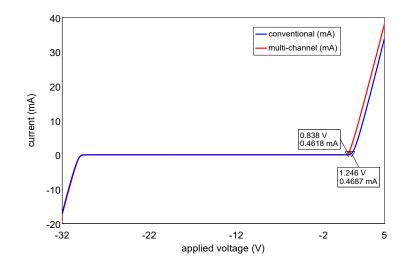

| Figure 7.19. Conventional and multi-channel SBDs /-V curves                                                                                                                                                   |

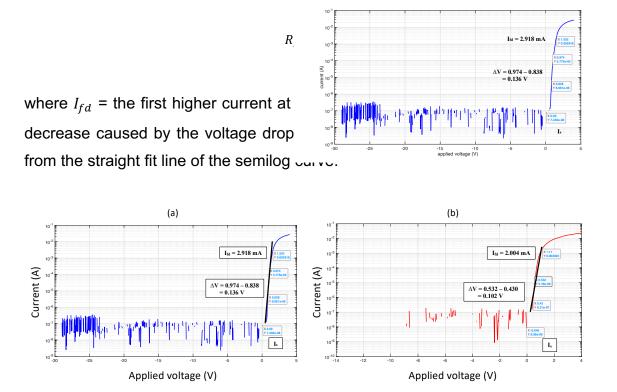

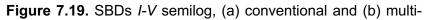

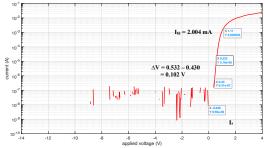

| Figure 7.20. SBDs <i>I-V</i> semilog, (a) conventional and (b) multi-channel                                                                                                                                  |

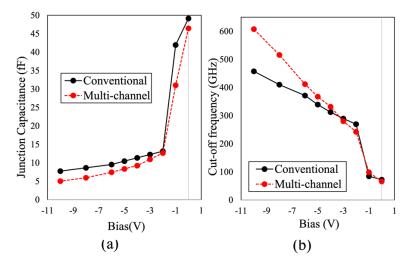

| <b>Figure 7.21.</b> <i>C-V</i> measurement of the 90 µm diameter circular Schottky diode, (a) capacitance and (b) corresponding cutoff frequency                                                              |

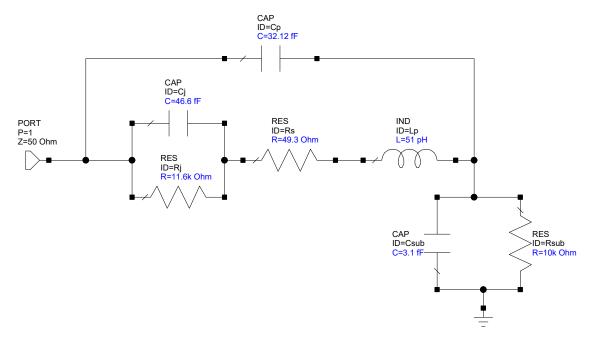

| Figure 7.22. Multi-channel SBD small signal model177                                                                                                                                                          |

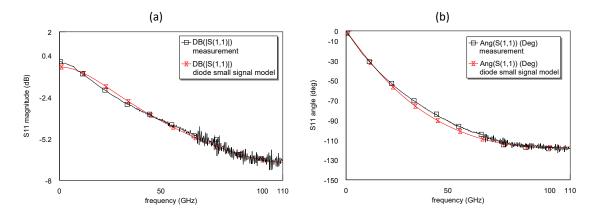

| Figure 7.23. Magnitude (a) and phase (b) of the return loss, measurement vs model                                                                                                                             |

| Figure 7.24. I-V curves of the conventional and multi-channel SBDs models                                                                                                                                     |

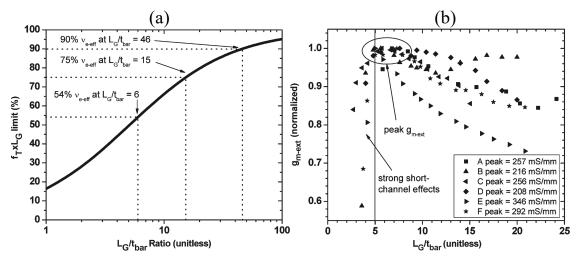

| <b>Figure 8.1.</b> Aspect ratio limitations effects on (a) v <sub>eff</sub> and (b) g <sub>m</sub> [174]181                                                                                                   |

| Figure 8.2. (a) transfer length region and (b) the proposed future work                                                                                                                                       |

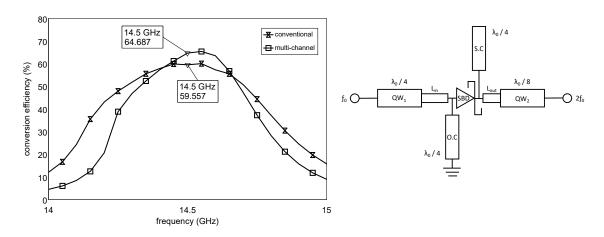

| <b>Figure 8.3.</b> A conventional/multi-channel SBDs-based frequency multiplier simulation conversion efficiency comparison (left) and the circuit block diagram (right)                                      |

## **1.** INTRODUCTION

In this chapter, an overview of the gallium nitride (GaN) HEMT based technology with the justification of this project and its application was given. Previous stateof-the-art AlGaN/GaN devices were provided as well. Finally, a summary and the main objectives of this project were also mentioned.

#### 1.1. GaN Technology: An Overview

Since the invention of the first solid state transistor in the mid of the last century, silicon has been exclusively the prime semiconductor for electronic devices. However, recently, silicon has reached its maximum practical and theoretical capabilities, especially in high power and high frequency applications. Therefore, with these limitations posed by silicon, alternatives are needed to meet the market demand of technological advancement in semiconductor industry. This has led to the shift of interest toward material with wide bandgap of III-V technologies such as gallium arsenide (GaAs), gallium nitride (GaN), and indium phosphide (InP), which allowed the application of high electron mobility transistor (HEMT) to emerge. III-V based HEMTs exhibited high electron mobility, due to inherit characteristic of current transport via majority carries as supposed to minority carries in silicon, which translated to operation at a smaller wavelength and higher frequency. On the other hand, wider bandgap has led to higher output power and more power density allowing for smaller size circuit with better performance. GaN is the most attractive among the III-V group and it is a direct bandgap with a band energy of 3.4 eV, which categorises it to be a wide-bandgap, WBG, material (2.0 < WBG < 4.0 eV [1]). Although GaN emerged around 1930, a synthesis done by Johnson et al., [2], the first GaN-based transistor fabricated on sapphire substrate, was only demonstrated in 1993 by Khan et al. as detailed in [3]. Due to GaN's superior electrical properties such as electron velocity, energy gap, breakdown electric field and power density, GaN is emerging as the future semiconductor replacing silicon in electronics.

**Figure 1.1.** Summary of GaN against Si, GaAs and SiC properties with the corresponding advantages and applications