# Active Control of Medium-Voltage Cascaded Three-level Neutral-Point-Clamped Converters

Jinlei Chen School of Engineering Cardiff University

A thesis submitted for the degree of *Doctor of Philosophy* December 2022

## Acknowledgement

The PhD study now comes to an end luckily with lots of fruitful learnings and findings. I have gained and developed a lot during this period of time, which is invaluable for the rest of my life.

Firstly, I would like to express my sincere gratefulness to my main supervisor Dr. Wenlong Ming. He gave me a lot of insightful training during my research and helped me find the ideas and methods of doing research. His rigorous academic attitude and selfless work spirit have set a good example for my future career development.

I would like to express my great thankfulness to my co-supervisors Prof. Nick Jenkins and Prof. Carlos Ugalde-Loo. They gave me a lot of encouragement, and meanwhile, gave me a lot of suggestions worth thinking about in depth, which are very helpful for my future life.

I thank all the friends and colleagues that gave me help on either life or work during this time. In particular, I would like to thank Dr. Sheng Wang, Dr. Peng Yang and Miss Chen Li for their great help on my work.

I would like to thank Cardiff University for providing me the opportunity of study. I would also like to thank the projects FLEXIS, DEDSO and Supergen Energy Networks Hub for their funding on my research.

Finally, I would like to express my sincere thankfulness to my parents and all other family members. It is your warmth, encouragement and help that give me the love, courage and willpower to overcome one difficulty after another.

### Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made only in accordance with instructions given by the Author and lodged in the Library of Cardiff University. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested with the author, subject to any prior agreement to the contrary, and may not be made available for use by third parties without his written permission, which will prescribe the terms and conditions of any such agreement.

#### Abstract

Three-Level Neutral-Point-Clamped (3L-NPC) converters have been widely used in the highpower motor drives. In recent years, a novel cascaded 3L-NPC converter has been developed and adopted in the ANGLE-DC project – a 30 MVA MVDC link demonstration project in North Wales, UK. This cascaded configuration provides exceptional waveform quality, modular design and a cost-effective solution to MVDC applications.

Although the control strategy for a single 3L-NPC converter has been well established, control of the cascaded 3L-NPC converter is still under-researched. The potential challenges to control strategy design arising from their cascaded connections need to be specifically explored. In particular, due to the series DC connection, the voltage imbalance across 3L-NPC submodules (SMs) may occur and influence the system stability. This issue may occur in converter stations where power is controlled in either point-to-point or multi-terminal systems. Beyond the electric characteristic, thermal characteristic is also vital to the performance of system. Thermal imbalance of 3L-NPC SMs may occur in a cascaded 3L-NPC converter even the voltage and power are equally shared, which poses great challenges to the system reliability.

To address aforementioned challenges, this thesis developed suitable control schemes for the cascaded 3L-NPC converter system and demonstrated their operation using a 30 kVA MVDC testbed based on the real ANGLE-DC project. The DC voltage imbalance was analysed through a small-signal model-based approach. Two DC voltage balancing methods with and without communications were presented. The PI-based method can automatically switch to the droop-based method upon failures of communication. The DC voltage imbalance of the cascaded 3L-NPC converter is further investigated in a three-terminal MVDC network in consideration together with the interactions of control characteristics between different converter stations and the power control accuracy. Then suitable control scheme was proposed. Multiple crossovers due to the interactions are avoided while DC voltage balance and power control accuracy are achieved as well. To mitigate the thermal imbalance, a thermal sharing controller was superposed on the DC voltage balancing controller to regulate the active and reactive power of each SM according to their individual junction temperatures. The thermal stresses are hence equally shared in presence of mismatched component parameters and cooling system failures. The effectiveness of presented methods in the thesis has been verified in MATLAB/Simulink simulation and experimentally validated.

| Acknowledgementi                                              |

|---------------------------------------------------------------|

| Copyrightii                                                   |

| Abstractiii                                                   |

| Contentsiv                                                    |

| List of Figuresxii                                            |

| List of Tablesxiii                                            |

| Nomenclaturexiv                                               |

| 1. Introduction1                                              |

| 1.1 Background2                                               |

| 1.1.1 Renewable Energy Collection and Integration2            |

| 1.1.2 Development of MVDC Distribution Networks               |

| 1.1.3 Development of MVDC Converters                          |

| 1.2 Research Motivation                                       |

| 1.2.1 Demonstration of an MVDC converter9                     |

| 1.2.2 Stability Analysis of Cascaded 3L-NPC Converters9       |

| 1.2.3 Multiple Crossovers in a Multi-terminal MVDC System10   |

| 1.2.4 Reliable Operation Considering the Thermal Conditions10 |

| 1.3 Objectives and Contributions of the Thesis10              |

| 1.4 Thesis Outline12                                          |

| 1.5 List of Publications14                                    |

| 2. Literature Review                                          |

| 2.1 Topologies of MVDC Converters16                           |

| 2.1.1 Cascaded DC/AC Converters16                             |

| 2.1.2 Cascaded DC/DC Converters                               |

| 2.2 Control of Cascaded MVDC Converters23                     |

| 2.2.1 Voltage and Power Balancing Control23                   |

#### Contents

| 2.2.2 Decentralized Control with Multiple Droop Characteristics            |    |

|----------------------------------------------------------------------------|----|

| 2.2.3 Active Thermal Control                                               |    |

| 2.3 Summary                                                                |    |

| 3. Laboratory demonstration of a Cascaded 3L-NPC Converter                 |    |

| 3.1 Introduction                                                           |    |

| 3.2 Hierarchical Control Design of the System                              |    |

| 3.2.1 Switching-level Control                                              |    |

| 3.2.2 Converter-level Control                                              |    |

| 3.2.3 Application-level Control                                            | 40 |

| 3.3 Configuration of the MVDC Testbed                                      | 41 |

| 3.3.1 Laboratory-scale Testbed with Cascaded 3L-NPC Converters             | 41 |

| 3.3.2 Signal Measurement and Hardware Protection                           | 42 |

| 3.3.3 Communication                                                        | 43 |

| 3.4 Simulation and Experimental Validation                                 | 44 |

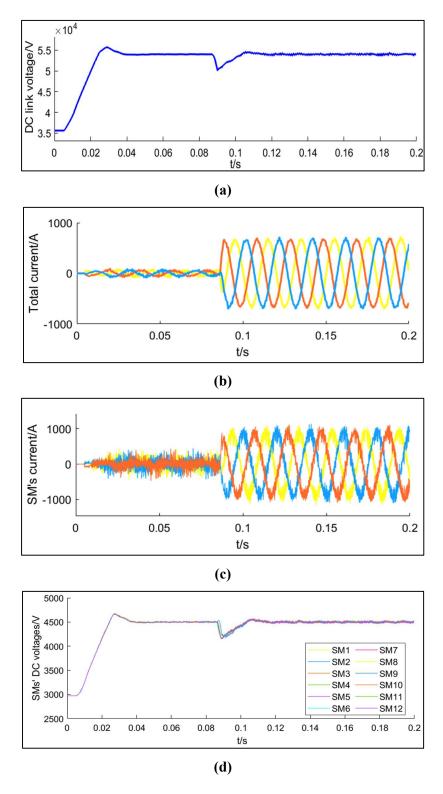

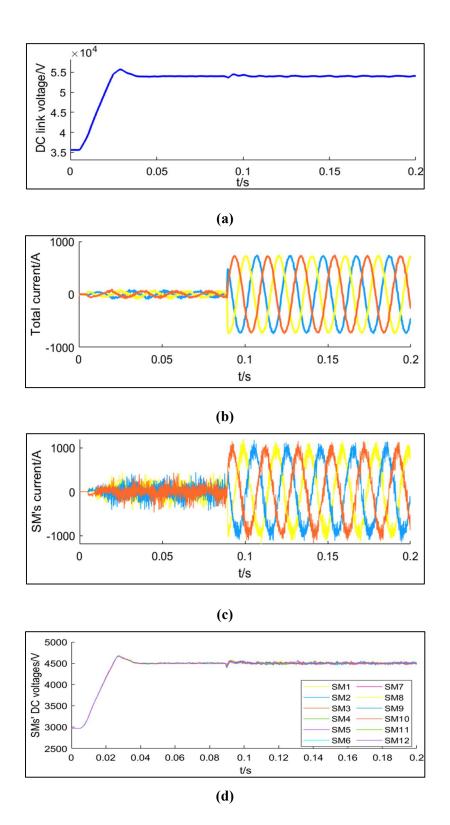

| 3.4.1 Simulation Results                                                   | 44 |

| 3.4.2 Experimental Results                                                 | 47 |

| 3.5 Summary                                                                |    |

| 4. Active DC Voltage Balancing Control for Submodules of a Cascaded 3L-NPC | 1  |

| Converter                                                                  |    |

| 4.1 Introduction                                                           | 55 |

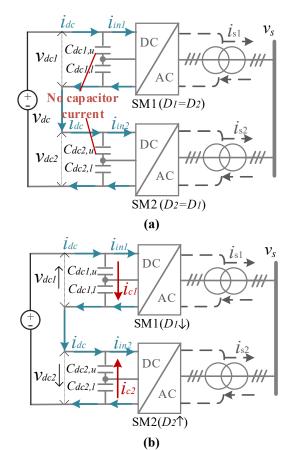

| 4.2 Analysis of DC Voltage Imbalance                                       | 55 |

| 4.2.1 Physical Mechanism of DC Voltage Imbalance                           | 55 |

| 4.2.2 Analysis based on the Small-signal Model                             | 57 |

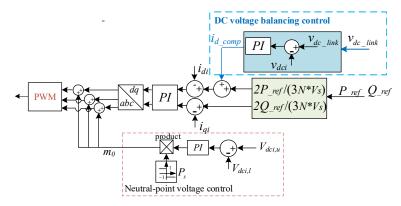

| 4.3 Voltage Balancing Control Methods                                      | 61 |

| 4.3.1 PI based Control with Communication                                  | 61 |

| 4.3.2 Inverse-droop based Control without Communication                    | 62 |

| 4.3.3 Hybrid Control combining PI and Inverse-droop based Control          | 68 |

| 4.4.1 Simulation Results71                                                              |

|-----------------------------------------------------------------------------------------|

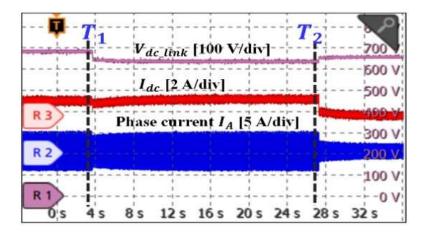

| 4.4.2 Experimental Results72                                                            |

| 4.5 Summary77                                                                           |

| 5. Decentralized Control for Multi-terminal Cascaded 3L-NPC Converter Systems           |

| Considering Multiple Crossovers79                                                       |

| 5.1 Introduction                                                                        |

| 5.2 Decentralized Control with Multiple-slope Characteristics in Cascaded 3L-NPC        |

| Converters                                                                              |

| 5.2.1 Configuration                                                                     |

| 5.2.2 Multiple crossovers due to interactions between Different Control Characteristics |

|                                                                                         |

| 5.2.3 Analysis of Power and Voltage drifts in Multiple Cross                            |

| 5.3 Presented Decentralized Control Scheme                                              |

| 5.3.1 Decentralized Control Schematic84                                                 |

| 5.3.2 Droop Gain Selection                                                              |

| 5.3.3 Design of Secondary Power Compensator                                             |

| 5.4 Simulation and Experimental Validation92                                            |

| 5.4.1 Simulation Results92                                                              |

| 5.4.2 Experimental Results95                                                            |

| 5.5 Summary                                                                             |

| 6. Active Thermal Sharing Control for Submodules of a Cascaded 3L-NPC Converter         |

|                                                                                         |

| 6.2 Active Thermal Sharing Control Method101                                            |

| 6.2.1 Thermal Sharing Control Loop                                                      |

| 6.2.2 Power Losses of Semiconductors                                                    |

|                                                                                         |

| 6.3 Thermal Control Capability Analysis10           | )6 |

|-----------------------------------------------------|----|

| 6.3.1 Thermal Control Limitation10                  | )6 |

| 6.3.2 Junction Temperature Reference Calculation10  | )7 |

| 6.3.3 Thermal Management by Power Adjustment10      | )8 |

| 6.4 Modelling and Controller Parameter Design11     | 10 |

| 6.4.1 Small-signal Model of the System11            | 10 |

| 6.4.2 Controller Parameter Tuning11                 | 3  |

| 6.5 Simulation and Experimental Validation11        | 4  |

| 6.5.1 Simulation Results11                          | 4  |

| 6.5.2 Experimental Results11                        | 9  |

| 6.6 Summary12                                       | 24 |

| 7. Conclusions and Future Work12                    | 25 |

| 7.1 Conclusions                                     | 26 |

| 7.2 Future Work                                     | 28 |

| 7.2.1 Bypass Operation under Fault Conditions12     | 28 |

| 7.2.2 Disturbance-observer based Adaptive Control12 | 28 |

| Appendix A                                          | 29 |

| Appendix B                                          | 30 |

| References                                          | 31 |

#### **List of Figures**

Figure 1.1. Shares of electricity generation by fuel.

Figure 1.2. Renewable electricity generation by technology in each UK nation.

Figure 1.3. The most important driving forces for the development of DC power distribution.

Figure 1.4. Collector grid topologies for a PV application: (a) MVAC collector grid; (b) MVDC collector grid.

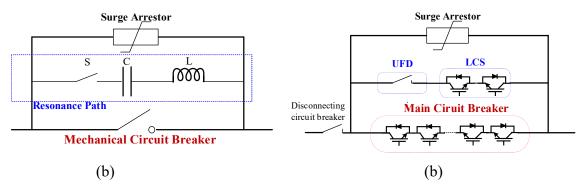

Figure 1.5. DC circuit breakers: (a) LC resonance circuit breaker; (b) Hybrid circuit breaker.

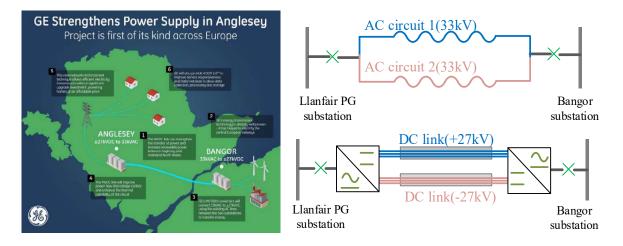

Figure 1.6. MVDC operation in the ANGLE-DC project: (a) MVDC circuit from Anglesey to Bangor (mainland North Wales); (b) conversion of existing double AC circuit to DC for MVDC operation.

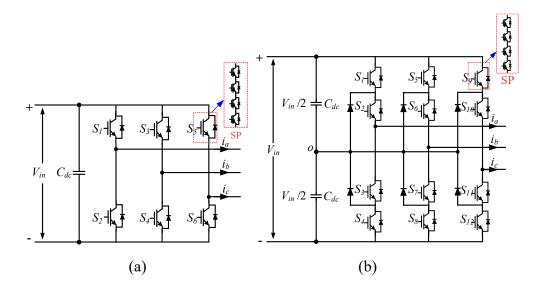

Figure 1.7. SP based 2L-VSC and 3L-NPC VSC: (a) 2L-VSC; (b) 3L-NPC VSC.

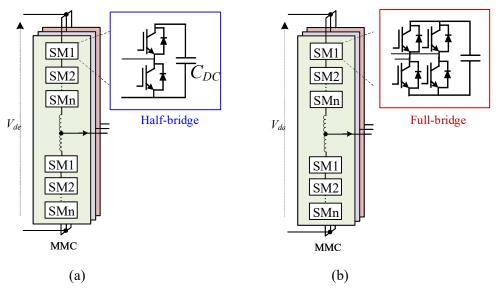

Figure 2.1. MMC topologies: (a) half-bridge; (b) full-bridge.

Figure 2.2. AC voltage waveforms of the MMC.

Figure 2.3. Current flow paths under SPG faults: (a) half-bridge; (b) full-bridge.

Figure 2.4. Cascaded 3L-NPC converters.

Figure 2.5. Single DC/DC converters: (a) DAB converter; (b) LLC resonant converter.

Figure 2.6. Modular configuration of the DC/DC converters: (a) ISOP connection; (b) ISOS connection.

Figure 2.7. MMC based DC/DC converters.

Figure 2.8. High step-ratio RMMC: (a) transformer-coupled RMMC; (b) transformer-less RMMC.

Figure 2.9. Low step-ratio RMMC.

Figure 2.10. PWM based voltage balancing control.

Figure 2.11. Nearest level modulation with sorting method for voltage balancing.

Figure 2.12. Common-duty control for DC/DC converters.

Figure 2.13. Input voltage sharing control for DC/DC converters.

Figure 2.14. Fully modularized control method for DC/DC converters.

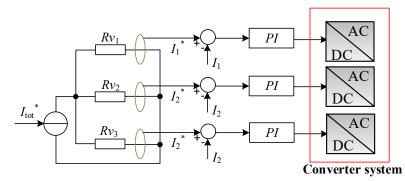

Figure 2.15. Current sharing control for DC/DC converters.

Figure 2.16. Decentralized voltage sharing control.

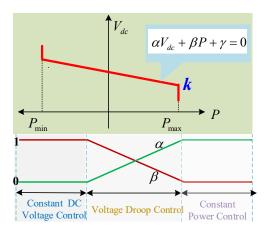

Figure 2.17. Control characteristics in power versus voltage (P - Vdc) droop. (a) Conventional droop cure with a single droop slope. (b) Improved droop curve with multiple droop slopes.

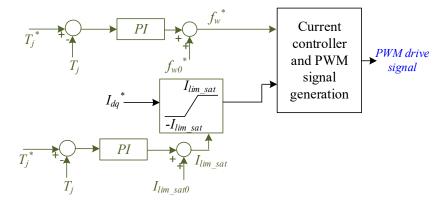

Figure 2.18. Thermal control by regulating the switching frequency and saturation of current controller.

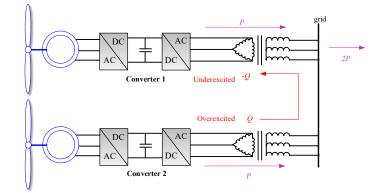

Figure 2.19. Thermal control by injecting circulating reactive power.

Figure 2.20. Power routing control strategy.

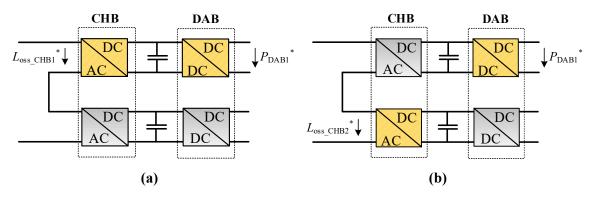

Figure 2.21. Thermal stresses in cascaded CHB-DAB converters.

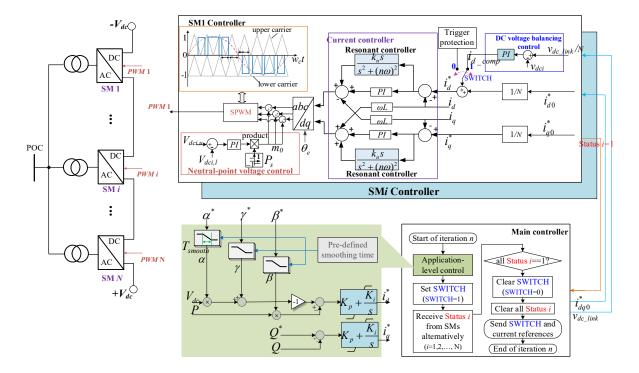

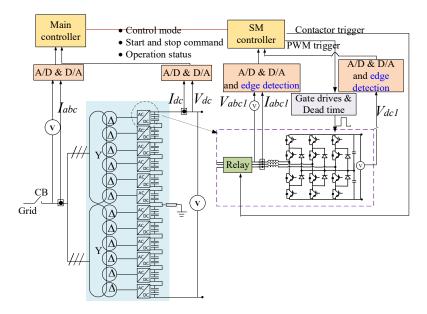

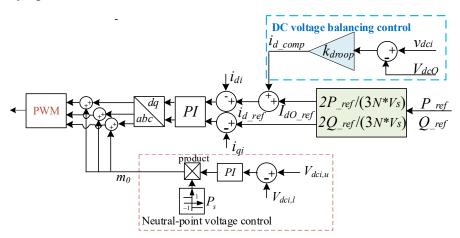

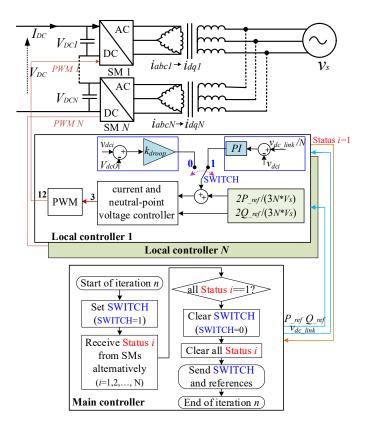

Figure 3.1. Control schematic of the cascaded 3L-NPC converters.

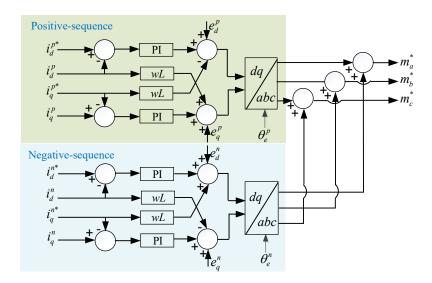

Figure 3.2. Dual current controller for positive and negative sequence control.

Figure 3.3. Control schematic of the cascaded 3L-NPC converters.

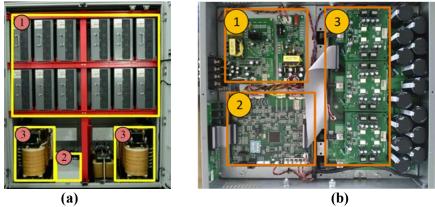

Figure 3.4. Laboratory scaled MVDC platform: (a) back-to-back cascaded 3L-NPC converter; (b) connection between the converter and a power amplifier.

Figure 3.5. Internal structure of the MVDC station and each SM. (a) MVDC station: 1) twelve 3L-NPC SMs, 2) high-level main controller, and 3) isolation transformers. (b) Each SM: 1) power supply to the microcontroller, 2) DSP28335 controller board, and 3) three-phase IGBT power modules.

Figure 3.6. Signal measurement and hardware protection diagram.

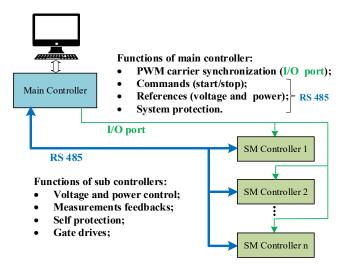

Figure 3.7. Communication diagram.

Figure 3.8. Step reference change of the active power under unit power factor: (a) DC link voltage; (b) Total AC current; (c) Current of SM 1; (d) SMs' DC voltages.

Figure 3.9. Step reference change of the reactive power under zero power factor: (a) DC link voltage; (b) Total AC current; (c) Current of SM 1; (d) SMs' DC voltages.

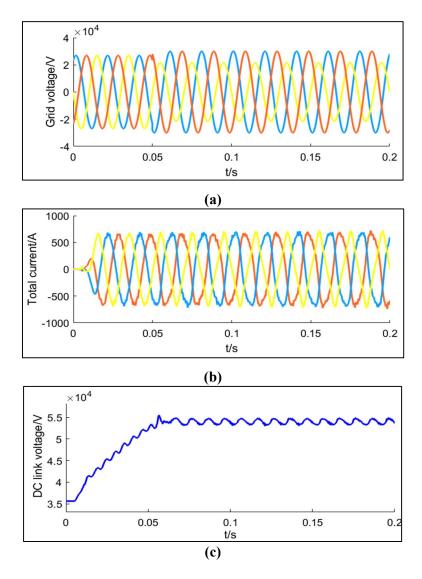

Figure 3.10. Performance under unbalanced grid voltage with 20% negative-sequence voltage. (a) Grid voltage; (b) Total AC current; (c) DC link voltage.

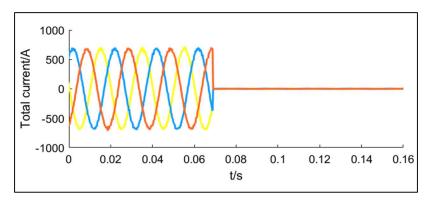

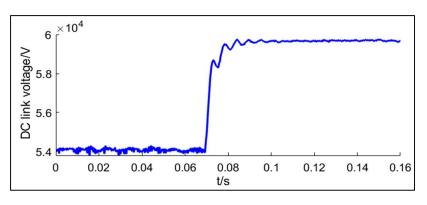

Figure 3.11. Droop control under fault conditions. (a) Total AC current; (b) DC link voltage.

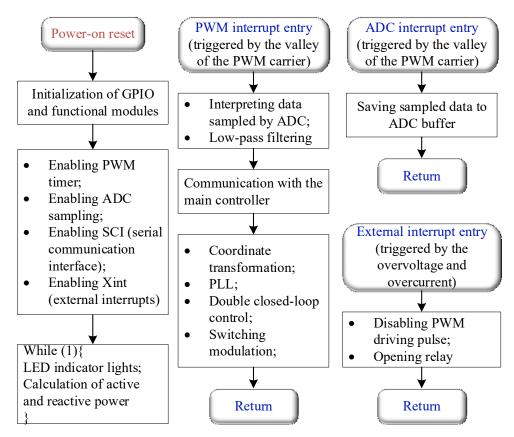

Figure 3.12. Flow chart of the DSP28335 code.

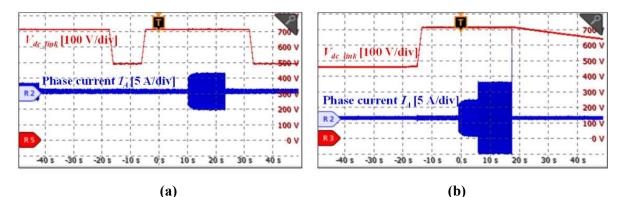

Figure 3.13. Start-up and shutdown procedures: (a) normal condition; (b) overcurrent condition.

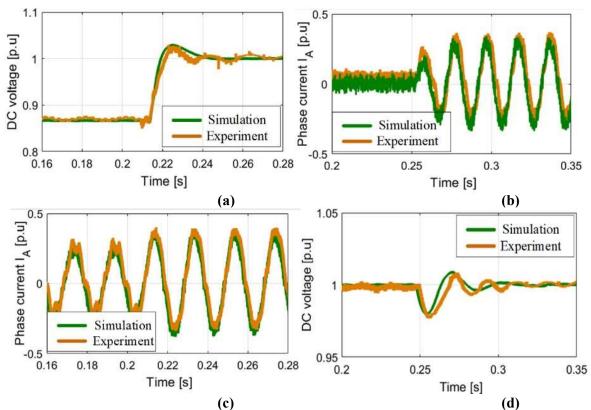

Figure 3.14. Comparison of simulation and experimental results of reference stepchanges: (a) DC voltage reference change; (b) power reference change; (c) load current upon reference changes in DC voltage; (d) DC voltage upon reference change in power.

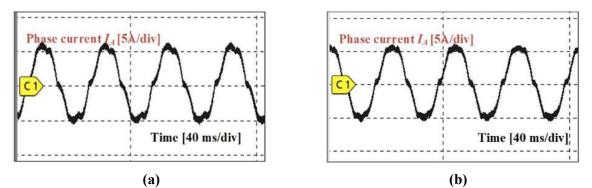

Figure 3.15. Phase-A current waveforms: (a) without resonant controllers in place; (b) including resonant controllers to mitigate 5th and 7th order harmonics.

Figure 3.16. Control mode transitions.

Figure 4.1. Cascaded 3L-NPC converter circuit.

Figure 4.2. Equivalent DC circuit for equal current sharing in each SM.

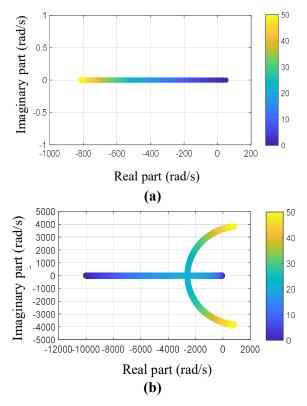

Figure 4.3. Root locus of dominant poles (obtained by solving equation (7)) for different power operating conditions. (a) P changes and Q = 0. (b) Q changes and P = 0.

Figure 4.4. PI-based voltage balancing controller with communication.

Figure 4.5. Neutral-point voltage waveforms: (a) waveforms without DC voltage balancing control; (b) waveforms with DC voltage balancing control.

Figure 4.6. Equivalent DC circuit with PI controller.

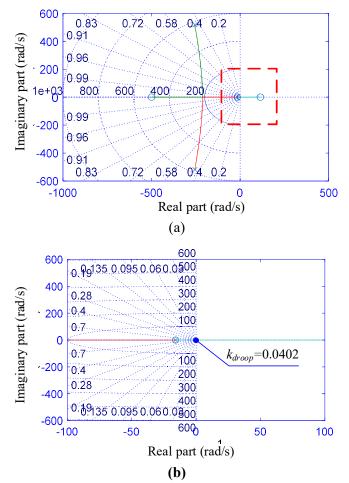

Figure 4.7. Root locus of dominant poles (obtained by solving equation (4-16)) with increasing  $k_{pudc}$  under PI controller. (a) Positive power flow. (b) Negative power flow.

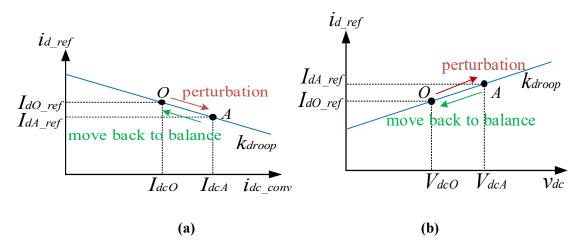

Figure 4.8. Droop curves for voltage balancing control. (a)  $i_{dc\_conv} - i_d^*$  curve. (b)  $v_{dc} - i_d^*$  curve.

Figure 4.9. Inverse-droop based voltage balancing controller.

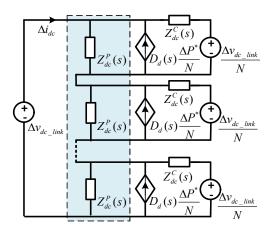

Figure 4.10. Equivalent DC circuit with inverse-droop controller.

Figure 4.11. Root locus of dominant poles (obtained by solving equation (4-19)) with increasing  $k_{droop}$  under inverse-droop controller. (a) Positive power flow. (b) Negative power flow.

Figure 4.12. Root locus of dominant poles (obtained by solving equation (15)) with increasing values of m, with  $k_{pudc} = 25$  and  $k_{droop} = 10$ .

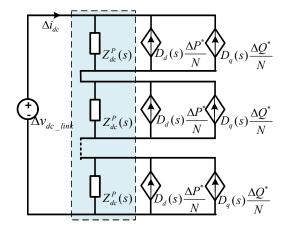

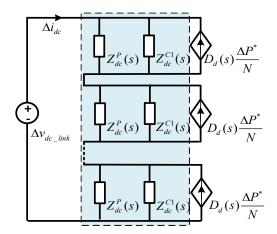

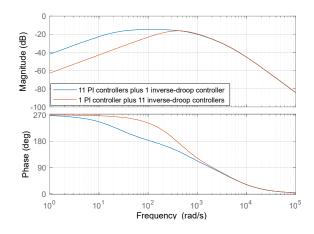

Figure 4.13. Bode diagram of  $G_d(s) = \frac{\Delta v_{dci}(s) - \Delta v_{dcj}(s)}{\Delta v_{dc_{link}}(s)}$ .

Figure 4.14. Overall control structure combing both control loops.

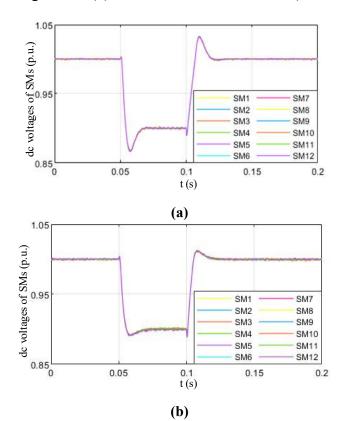

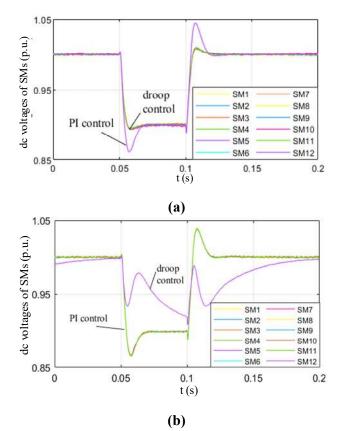

Figure 4.15. DC voltages of SMs 1 to 12. (a) with PI-based control. (b) with inversedroop based control.

Figure 4.16. DC voltages of SMs 1 to 12 for a hybrid control structure. (a) 1 PI controller plus 11 inverse-droop controllers. (b) 1 inverse-droop controller plus 11 PI controllers.

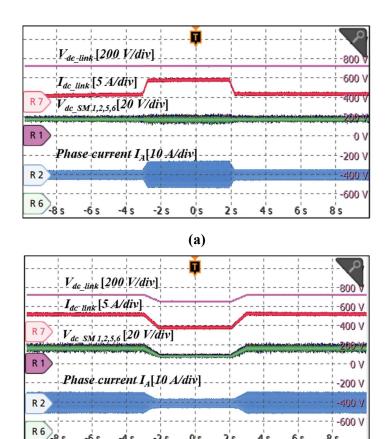

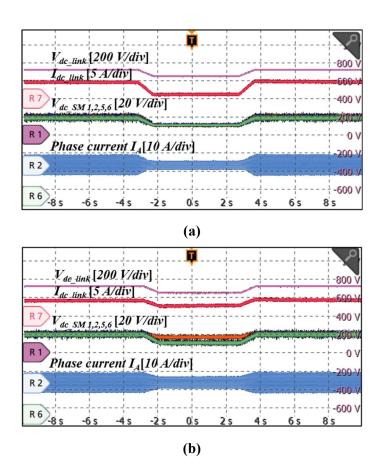

Figure 4.17. Operation with PI-based DC voltage balancing controllers. Results for: (a) active power reference change; (b) DC link voltage reference change.

Figure 4.18. Operation when communication is lost.

Figure 4.19. Operation with droop-based DC voltage balancing controllers. Results for: (a) active power reference change; (b) DC link voltage reference.

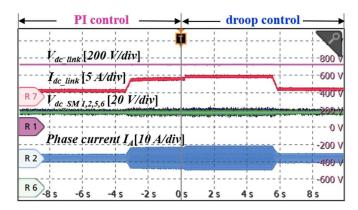

Figure 4.20. Operation with hybrid DC voltage balancing control methods. (a) one PIbased controller and seven inverse-droop based controllers. (b) seven PI-based controllers and one inverse-droop based controller.

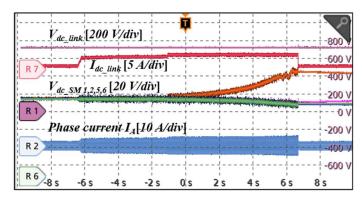

Figure 4.21. Waveforms under mode transition.

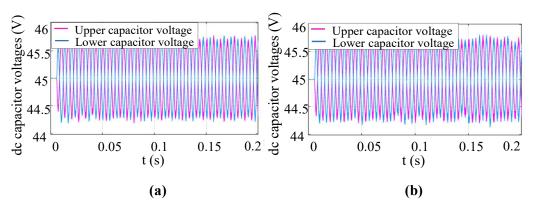

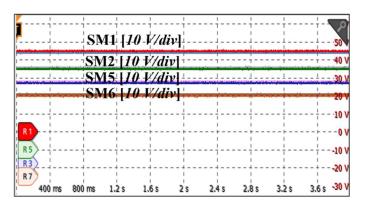

Figure 4.22. Upper and lower DC voltage waveforms of SM1,2,5,6 under DC voltage balancing control.

Figure 4.23. Upper and lower DC voltage waveforms of SM1,2,5,6 under DC voltage balance and imbalance.

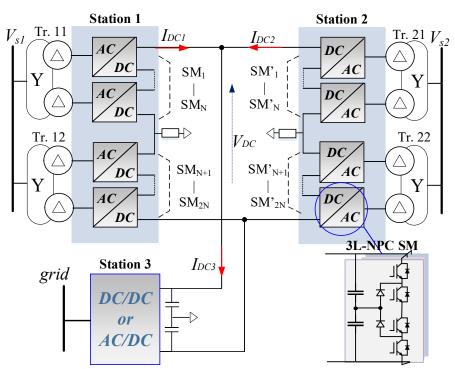

Figure 5.1. Cascaded 3L-NPC converter based three-terminal MVDC link.

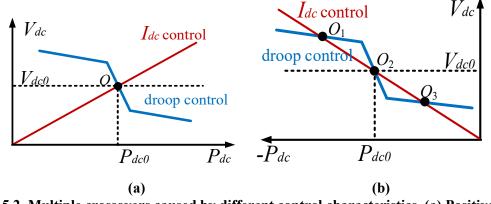

Figure 5.2. Multiple crossovers caused by different control characteristics. (a) Positive power flow condition. (b) Negative power flow condition.

Figure 5.3. Power and voltage drifts under a disturbance. (a) The case under a DC current disturbance. (b) The case under a DC voltage disturbance.

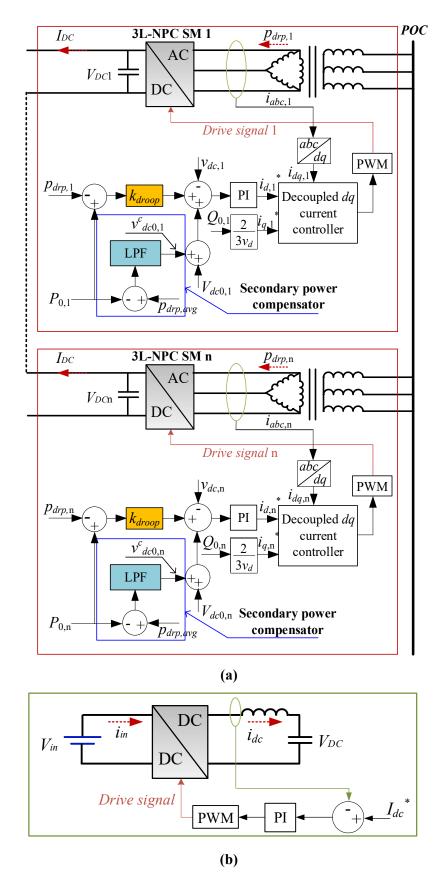

Figure 5.4. The decentralized control schematic of the system.

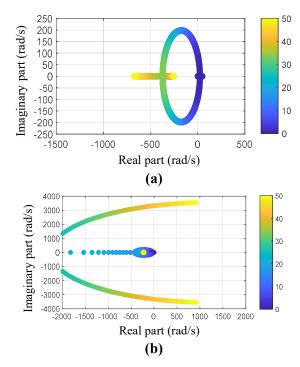

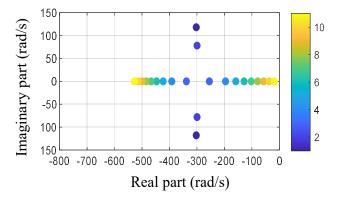

Figure 5.5. Closed-loop poles' trajectories in equation (5-10) as  $k_{droop}$  increases. (a) Dominant poles' trajectories. (b) Zoom-in view of dominant poles' trajectories.

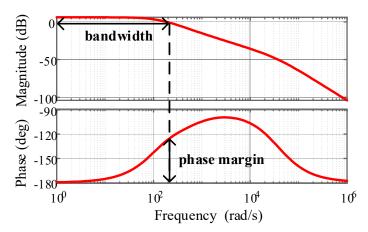

Figure 5.6. Open-loop Bode diagram of equation (5-10) when  $k_{droop} = 0.023$ .

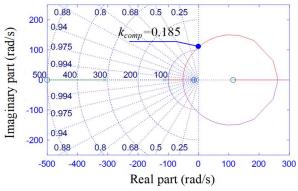

Figure 5.7. Closed-loop poles' trajectories in equation (5-18) as  $k_{comp}$  increases.

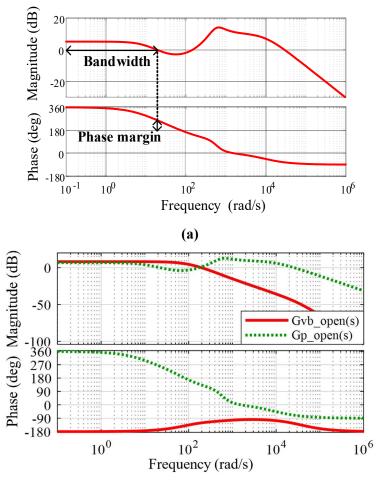

Figure 5.8. Open-loop Bode diagram of equation (5-18) with  $k_{comp} = 0.085$  and  $\tau = 0.1$ .

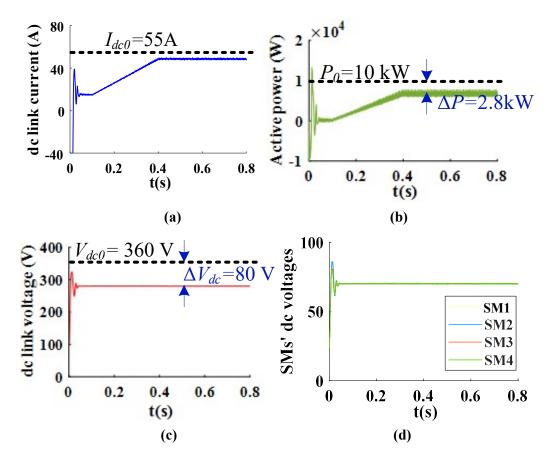

Figure 5.9. Multiple crossovers when  $k_{droop}$  is 0.06. (a) DC current. (b) total power. (c) DC link voltage. (d) SMs' DC voltages.

Figure 5.10. No multiple crossovers when  $k_{droop}$  is 0.023. (a) DC current. (b) total power. (c) DC link voltage. (d) SMs' DC voltages.

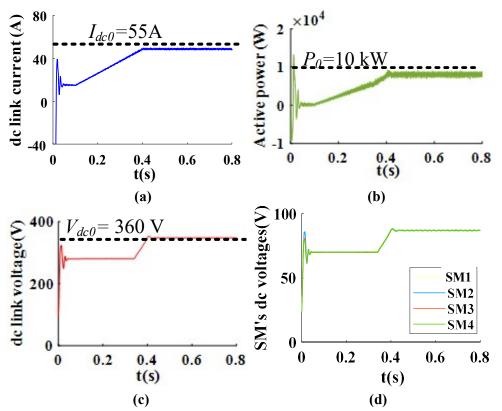

Figure 5.11. Power drift without using secondary power compensating controller. (a) DC current. (b) total power. (c) DC link voltage. (d) SMs' DC voltages.

Figure 5.12. Improved power control accuracy with using secondary power compensating controller. (a) DC current. (b) total power. (c) DC link voltage. (d) SMs' DC voltages.

Figure 5.13. Three-terminal MVDC configuration consisting of two cascaded 3L-NPC converter stations and a DC power supply.

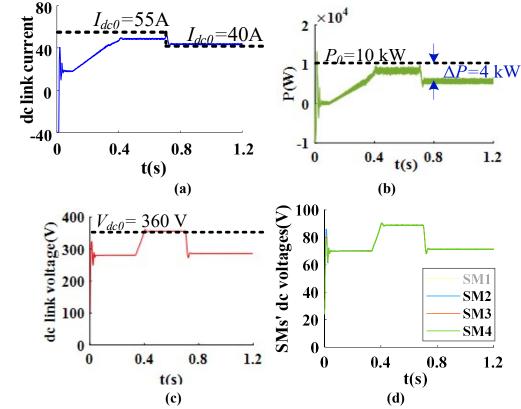

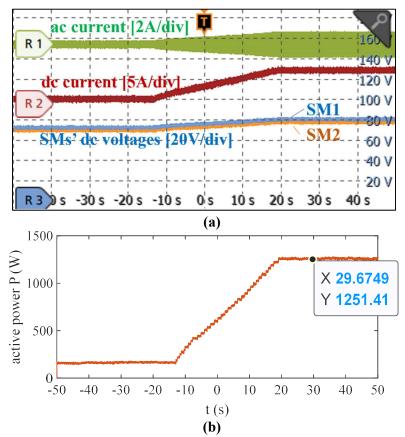

Figure 5.14. Waveforms when  $k_{droop}$  is set to 0. 36. (a) Currents and DC voltages. (b) Output power from DC power supply.

Figure 5.15. Waveforms when  $k_{droop}$  is set to 0.072. (a) Currents and DC voltages. (b) Output power from DC power supply.

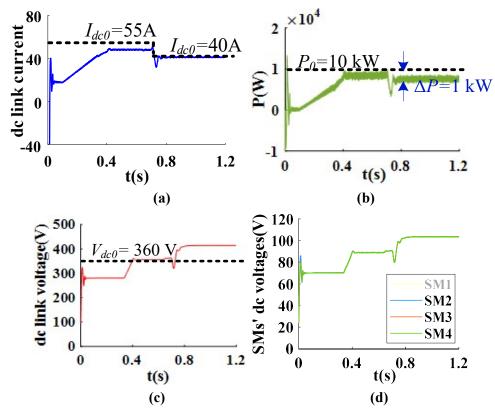

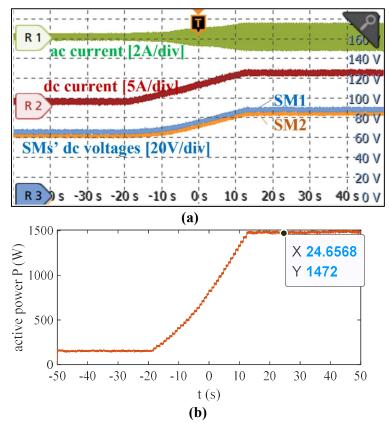

Figure 5.16. Waveforms under DC current change, with and without secondary power compensator. Figure 16. (a) Currents and DC voltage. (b) Output power from DC power supply.

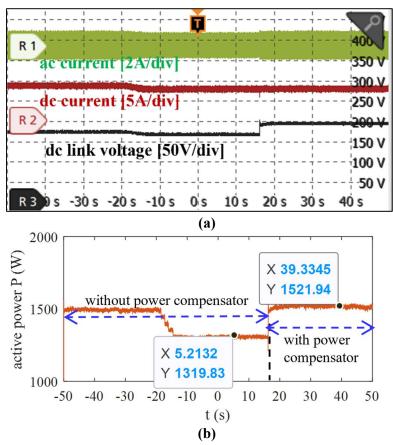

Figure 6.1. Thermal sharing control schematic of the MVDC system with N cascaded SMs.

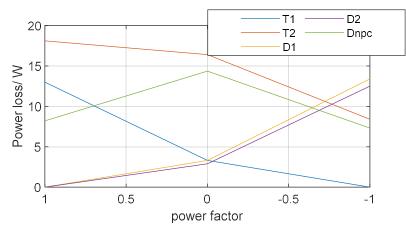

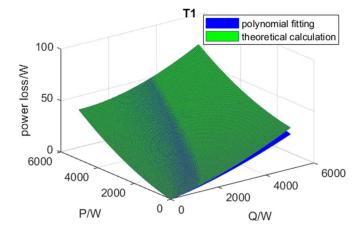

Figure 6.2. Power loss distribution at different power factors.

Figure 6.3. Comparison of power losses between theoretical analysis and polynomial fitting.

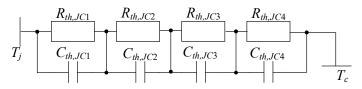

Figure 6.4. Thermal impedance network.

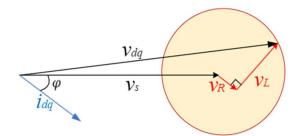

Figure 6.5. Phasor diagram of the converter voltage.

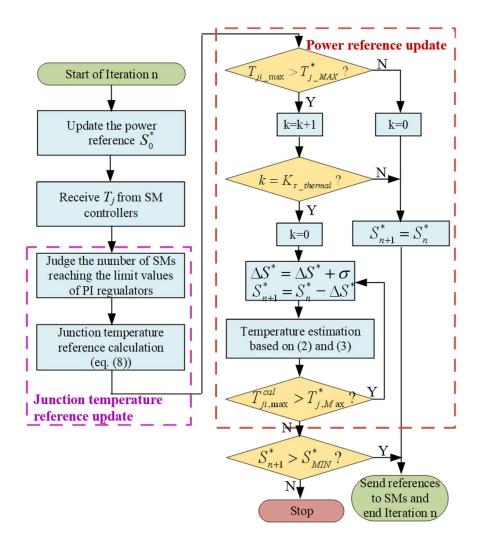

Figure 6.6. Thermal management inside the main controller.

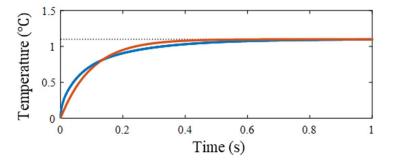

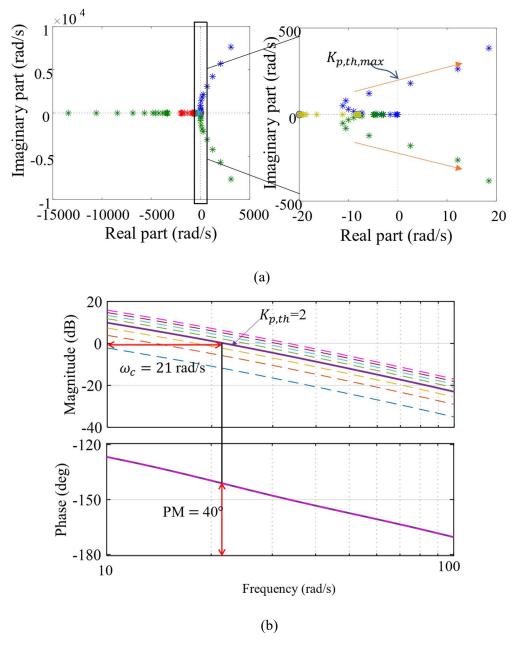

Figure 6.7. Bode plot of  $G_{\delta,th}(s)$  with different  $K_{P,th}$ .

Figure 6.8. Results without using thermal sharing control.

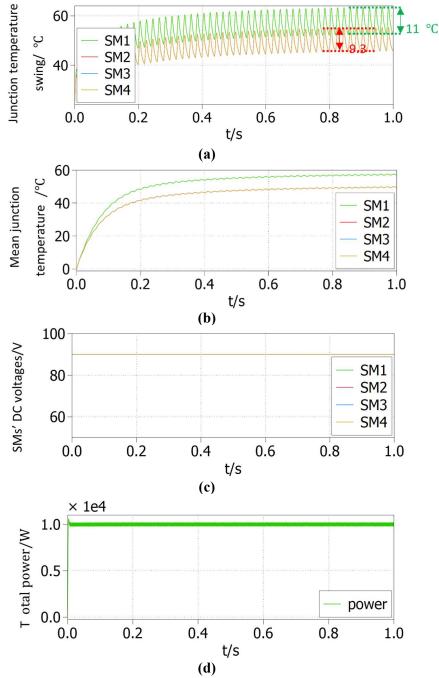

Figure 6.9. Results with using thermal sharing control.

Figure 6.10. Results under maximum thermal control capability (temperature reference is the mean value of the four SMs).

Figure 6.11. Results under maximum thermal control capability (temperature reference is the mean value of the remaining SMs except for SM1).

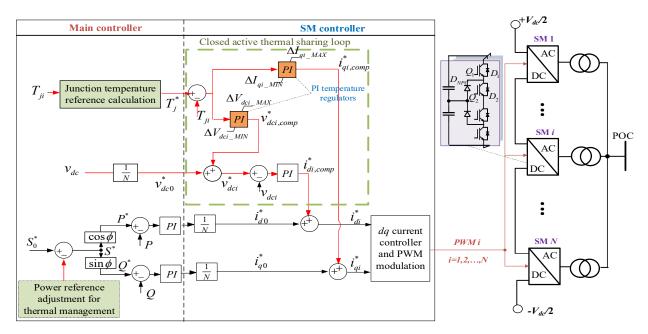

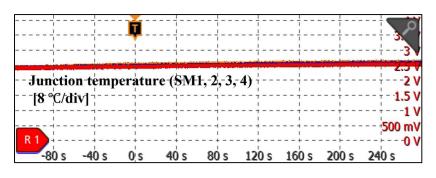

Figure 6.12. Junction temperatures of SMs without thermal sharing control (the fan of SM1 is at 60% rated speed and the others at 100% rated speed): (a) junction temperatures of SMs; (b) SM and total AC current and DC voltage (the bottom plot shows a zoomed-in view).

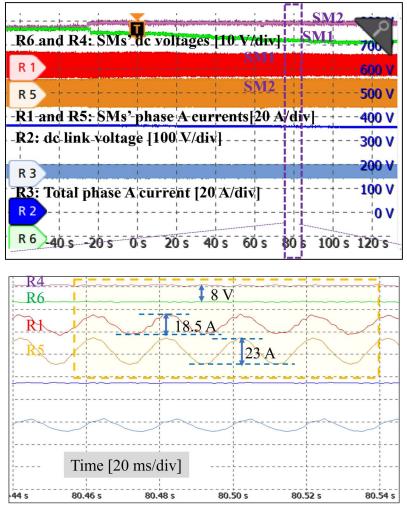

Figure 6.13. Junction temperatures of SMs with thermal sharing control (same thermal conditions as in Figure 6.12): (a) junction temperatures of SMs; (b) SM and total AC current and DC voltage (the bottom plot shows a zoomed-in view).

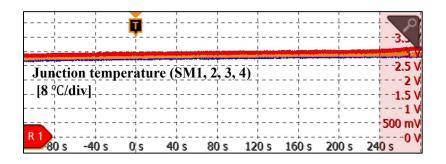

Figure 6.14. Junction temperatures of SMs with thermal sharing control (the fan of SM1 is at zero speed and the others at 100% rated speed): (a) junction temperatures of SMs; (b) SM and total AC current and DC voltage (the bottom plot shows a zoomed-in view).

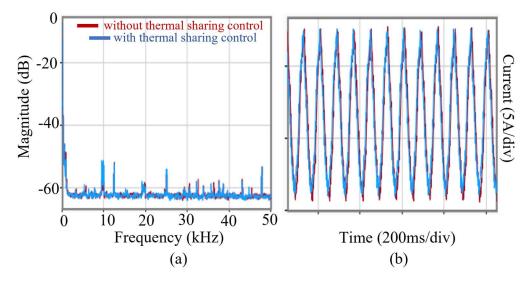

Figure 6.15. FFT analysis of AC harmonics with and without thermal sharing control.

#### **List of Tables**

TABLE 2.1. Characteristics Comparison of Multi-level VSCs at Different DC Voltage

Levels.

TABLE 3.1. Parameter Comparison between the ANGLE-DC Configuration and theExperimental Testbed.

TABLE 3.2. Per unit Values of Control Parameters.

TABLE 5.1. Parameter of IGBT Module F3L75R07W2E3\_B11.

Table 5.2. Average power loess of devices in a fundamental period.

### Nomenclature

| Alternative-Current Circuit Breaker      | ACCB    |

|------------------------------------------|---------|

| Carrier Disposition-based Sinusoidal PWM | CD-SPWM |

| Cascaded H-Bridge                        | CHB     |

| Dual Active Bridge                       | DAB     |

| Distributed Generator                    | DG      |

| Direct-Current Circuit Breaker           | DCCB    |

| Discontinuous Pulse-Width Modulation     | D-PWM   |

| Full-Bridge                              | FB      |

| High-Voltage Direct-Current              | HVDC    |

| High-Voltage Alternative -Current        | HVAC    |

| Half-Bridge                              | HB      |

| High-Frequency                           | HF      |

| Input-Series-Output-Parallel             | ISOP    |

| Input-Series-Output-Series               | ISOS    |

| Input Voltage Sharing                    | IVS     |

| Low-Voltage Direct-Current               | LVDC    |

| Low-Voltage Alternative -Current         | LVAC    |

| Medium-Voltage Direct-Current            | MVDC    |

| Medium-Voltage Alternative-Current       | MVAC    |

| Multi-Terminal Direct-Current            | MTDC    |

| Modular Multilevel Converter             | MMC     |

| Model Predictive Control                 | MPC     |

| Output Current Sharing                   | OCS     |

| Photovoltaic                             | PV      |

| Power Electronic Building Block          | PEBB    |

| Pulse-Width Modulation                   | PWM     |

| Phase-Locked Loop                        | PLL     |

| Quasi-Square-Wave                        | QSW     |

| Quasi-Two-Level                          | Q2L     |

|                                          |         |

| Resonant Modular Multilevel DC/DC Converter R | RMMC  |

|-----------------------------------------------|-------|

| Return on Investment R                        | ROI   |

| Sub-Synchronous Resonance S                   | SSR   |

| Single-Phase-to-Ground S                      | SPG   |

| Submodule                                     | SM    |

| Sinusoidal PWM S                              | SPWM  |

| Space-Vector PWM S                            | SVPWM |

| Switch Position S                             | SP    |

| Three-Level Neutral-Point-Clamped 3           | L-NPC |

| Total cost of the ownership T                 | ГСО   |

| Voltage Source Converter V                    | VSC   |

# Chapter 1

# Introduction

This chapter introduces the background, motivation, objectives, and contributions of this thesis. An outline of the thesis is also provided.

#### 1.1 Background

In response to the growing demand for decarbonization and the implementation of net-zero policies, renewable energy technologies have experienced rapid advancements. Distributed generators and energy storage devices are increasingly being integrated into distribution networks. However, their successful integration necessitates precise and flexible control over power flow. Medium-voltage direct-current (MVDC) technology has emerged as a recent development that offers improved controllability of power flows, enhanced power transfer capabilities, and better control over network voltages. These advancements are made possible through the utilization of MVDC converters. Despite these advancements, the control and operation of MVDC converters remain areas of ongoing research. In-depth understanding of these aspects is crucial to ensure the safety and desired performance of MVDC operations.

#### **1.1.1 Renewable Energy Collection and Integration**

Renewable sources, such as wind and solar power, are gradually replacing conventional gas and petrol as clean energy alternatives. This shift not only contributes to carbon reduction targets but also helps mitigate the energy crisis by reducing reliance on non-renewable resources.

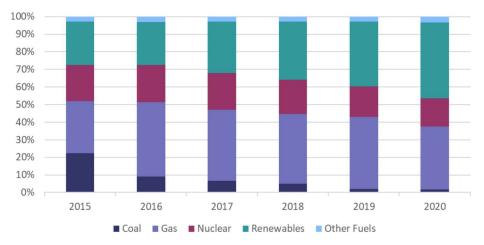

In recent years, the United Kingdom has witnessed a significant surge in renewable electricity generation and capacity, driven by its commitment to achieving net zero carbon emissions by 2050. Figure 1.1 illustrates the percentage share of UK's electricity generation during the period of 2015-2020.

Figure 1.1. Shares of electricity generation by fuel [1].

For the first time in the recorded data series, renewable sources surpassed fossil fuels in their contribution to electricity generation in 2020. The proportion of renewable energy rose significantly, accounting for 43.1% of the total UK generation.

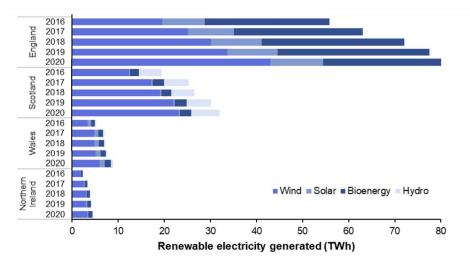

Figure 1.2 displays the distribution of renewable electricity generation by technology across different UK nations. It is evident that England and Scotland are the primary regions with concentrated renewable energy generation. In England, wind, solar, and bioenergy are the dominant sources, whereas in Scotland, wind, hydro, and bioenergy play a major role. Wind generation stands out prominently in both nations. As part of its commitment to achieving net zero carbon emissions by 2050, the UK plans to increase its offshore wind generation capacity to 40 GW by 2030, thereby surpassing 50 GW of overall wind capacity.

Figure 1.2. Renewable electricity generation by technology in each UK nation [2].

However, with the large-scale renewable energies and loads being integrated, the power quality and reliability may become concerned issues. These require suitable power distribution technology in place to participate in power transmission and regulation.

#### **1.1.2 Development of MVDC Distribution Networks**

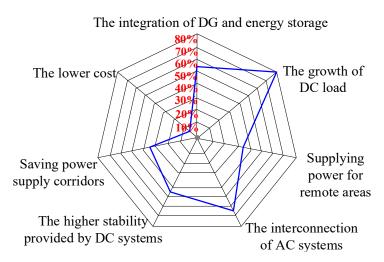

Motivated by external and internal driving forces, the MVDC has become an important enabling technology in distribution networks. Figure 1.3 shows the distribution of the driving forces.

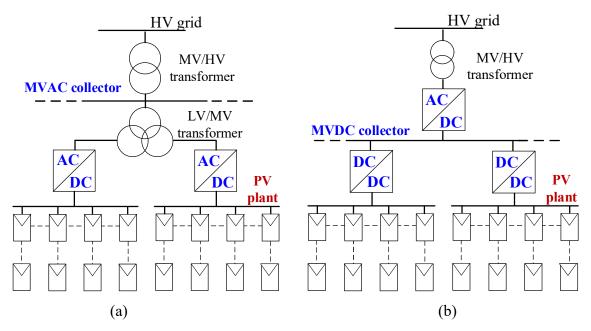

For external driving forces, the integration of distributed generators (DGs) and energy storage and growth of DC loads are two stimulating factors. Take an example of the solar photovoltaic (PV) integration (see Figure 1.4). In the conventional scheme in Figure 1.4(a), the low-voltage DC (LVDC) generated by different groups of PV panels are first transformed to low-voltage AC (LVAC) through DC/AC converters. Then, a multi-winding transformer is used to boost the LVAC to Medium-Voltage Alternative-Current (MVAC). Therefore, the power from different groups of PVs are collected by the MVAC grid. To make connection with the grid at high voltage, a MV-to-HV transformer can be used. The alternative option using the MVDC collection is shown in Figure 1.4(b). As can be seen, The DC/DC converters collect the PV plants and connect to the MVDC grid, instead of the MVAC grid. For the connection between MVDC and HVDC grids, an MV-level DC/AC converter acts as the interface together with a booster transformer. In the conventional AC circuit, capacitive effect causes higher leakage currents through the insulation material of a cable, so that less load current will be delivered to the end user. Also, ccompared with the AC circuit, DC operation has better controllability on the AC voltage regulation by using power electronic converters. Thus DC operation has larger power supply capacity than traditional AC operation [3]. Also, as the skin effect, proximity effect and eddy current effect are reduced in DC system, the efficiency can be improved. For example, Skin effect occurs in conductors carrying high frequency AC currensts where the current tends to concentrate towards the surface of the conductor, reducing the effective crosssectional area available for the current. This results in increased resistance and power loss in the conductor. Another external driving force is the growth of DC loads. As more and more loads are naturally supplied by DC, the transformation of DC to AC can be avoided compared with the traditional MVAC distribution.

Figure 1.3. The most important driving forces for the development of DC power distribution (the percentage represents the weight of each factor) [3].

For internal driving forces, the MVDC can provide better performance of the power and voltage regulation. The main advantages include: the power and voltage control become more flexible as the AC grids at the DC terminals can be independently controlled regardless of the

mismatches of frequency, phase angle and voltage magnitude; the fault at one AC grid can be avoided to propagate to another side, thus improving the stability of the system; the power quality can be improved since the VSC can be used as the active power filter and reactive power compensator such as the STATCOM.

Figure 1.4. Collector grid topologies for a PV application: (a) MVAC collector grid; (b) MVDC collector grid [4].

The MVDC technology mainly includes stability analysis and control of MVDC power electronics, reliability evaluation and DC protection.

As large-scale distributed generators (DGs) and loads are integrated into the grid, the system's stability is impacted, primarily due to a reduction in system inertia. As more power electronic based devices are replacing the synchronous generators, the inertia provided by the synchronous generators is decreasing. The adverse impact is that the system transient and dynamic stability are influenced, thus the system is more susceptible to the disturbance of the grid frequency and voltage [5]. Also, as more DC links are integrated, the interactions between DC and AC system may pose concern of stability. The DC fault may propagate to AC side, and in this case, the voltage and frequency support from the MVDC link will be lost, thus leading to potential instability. Another stability issue is associated with the power electronic converters themselves. As more power electronic converters are connected in series or parallel, the interactions between converters may influence the system robustness. The stability issue requires detailed system modeling and a suitable control scheme. In addition, the coordinated control in the multi-terminal DC (MTDC) systems also attract attention. The voltage and

frequency supporting are supposed to be jointly undertaken by the parallel-connected DGs. The commonly used method is the droop-based control, where there is no centralized controller with communication. When suffering from a failure in one converter station, the others can still take over the power and voltage regulation. Besides, the grid-forming control in island operation, robustness of the power electronic converters and suppressing of the sub-synchronous resonance (SSR) are also attracting attentions from both academia and industry.

System reliability is another important branch. Mass penetration of DGs puts more power components at risk of damage. A key technique is reliability evaluation. The failure rate prediction model is established first. Then, the failure probability and lifetime can be evaluated through analytical and simulation methods. The Monte Carlo simulation is a widely used method due to its suitability for large and complex systems. How to improve computation efficiency is an existing challenge.

For the DC protection, the DC circuit breaker (DCCB) is an under-researched topic. For the conventional AC circuit breaker (ACCB), it takes approximately 40-100 ms until the current is interrupted after receiving the operating command signal from a controller [6]. However, the non-zero crossing of currents during DC faults brings design difficulty to the DCCB. For DC current interruption, it is necessary to intentionally create current zero points. The resonancetype breaker can create a zero crossing of current using an LC resonance circuit (see Figure 1.5(a)). The mostly adopted option is the hybrid type as shown in Figure 1.5(b). The power semiconductor and mechanical switches are used together, where the power semiconductors are used to rapidly interrupt the fault current and the mechanical switches to withstand high voltage difference between lines. Although the technologies of existing HVDC DCCBs are applicable for MVDC applications, the design and selection of MV DCCBs still require special attention to ensure that they are reliable, safe, and can withstand the specific challenges associated with MVDC systems [7], [8]. One of the challenges is the lower voltage level at which MV DCCBs operate. This means that their design and testing must be specific to the voltage level, taking into account the necessary insulation and switching requirements. Additionally, the smaller size of MV DCCBs compared to HV DCCBs can be a challenge, as they need to fit all necessary components within a compact design while still ensuring reliability and safety. Furthermore, compared to HV DCCBs, MV DCCBs are less commonly used and may have limited availability in the market. This may pose a challenge in sourcing and maintaining these components.

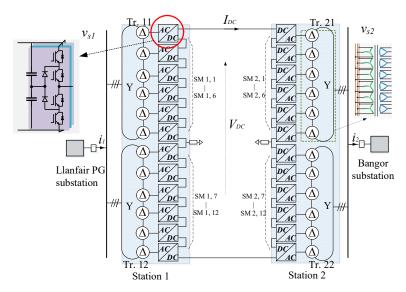

To date, limited practical MVDC links have been built [9]–[12]. At Eagle Pass (Texas, USA), a  $\pm$ 16-kV voltage source converter (VSC)-based DC link was built in 2003 to interconnect two distribution networks [9]. At Tangjiawan (Zhuhai, China), a three-terminal  $\pm$ 10-kV MVDC project was trialed in 2018 [10]. At Exebridge (Southwest England, U.K.), through the Network Equilibrium project, a "Flexible Power Link" consisting of two back-to-back VSCs was constructed in 2014 to connect two 33-kV distribution networks [11]. In North Wales, U.K., the ANGLE-DC project was launched in 2017 to adapt an MVAC circuit for MVDC operation. The ANGLE-DC is the first trial of an MVDC link in the Great Britain (GB) electrical power system. It is a demonstration project that enhances the power transfer capacity and thermal capability between the island of Anglesey and Bangor in North Wales by converting an AC transmission corridor into DC operation (see Figure 1.6).

Figure 1.5. DC circuit breakers: (a) LC resonance circuit breaker; (b) Hybrid circuit breaker.

Figure 1.6. MVDC operation in the ANGLE-DC project: (a) MVDC circuit from Anglesey to Bangor (mainland North Wales) [12]; (b) conversion of existing double AC circuit to DC for MVDC operation.

This conversion allows an increased volume of renewable generation to flow mainland from Anglesey without exceeding the thermal limits of existing assets. By converting an existing twin AC circuit at 33 kV to  $\pm 27$  kV DC, the power transfer capacity between the island of

Anglesey and Bangor (mainland) can be increased by more than 23%, enabling a more distributed generation to be connected on the island [12].

#### **1.1.3 Development of MVDC Converters**

The power electronic converter is the key enabler for the MVDC technology. The conventional 2L-VSC and 3L-NPC converter can be selected as the MVDC converter candidates. However, as a single IGBT cannot be able to withstand a high voltage, the IGBT devices are always connected in series to make up a device group, which is named as switch position (SP) [20]. The SP in the bridge arm is shown in Figure 1.7(a) and (b). An issue faced by this configuration is that if one device in the group is damaged, the whole converter will malfunction. From the perspective of the reliability, the power electronic building blocks (PEBBs) are used as the constituent components of converters. Each PEBB is a standardized and modularized submodule (SM), which can be bypassed and easy to maintain in fault conditions. The PEBB-based converter is preferred due to its exceptional waveform quality, compact, and modular design [20]. Such types of converters include input-series-output-parallel (ISOP) and input-series-output-series (ISOS) DC/DC converters. Detailed discussions and comparisons regarding the PEBB-based converter topologies are given in Chapter 2.2.

Figure 1.7. SP based 2L-VSC and 3L-NPC VSC: (a) 2L-VSC; (b) 3L-NPC VSC.

#### **1.2 Research Motivation**

As discussed in Section 1.1.2, the stability issue resulting from use of power electronic converters is of concern to DNOs. The mass quantities of power electronic devices influence the system reliability, thus leading to large times of maintenance and reduction of the system lifetime. Also, the number of existing MVDC demonstration project is limited, which provides limited lessons and experience to DNOs. The control and operation scheme for MVDC converters are not yet well developed.

Compared with MMCs, cascaded 3L-NPC converters use mature technologies employed for MV motor drives and, in addition, have a relatively low cost and a small footprint [21]. As practical applications are often price-driven, cascaded 3L-NPC converters thus represent an attractive alternative for real projects. For instance, such a converter topology was adopted in the recent ANGLE-DC project, which provides a 30 MVA MVDC transmission corridor in North Wales, UK, between Bangor and Anglesey [12]. The cascaded 3L-NPC converter system consists of *N* three-phase individual SMs. The DC terminals of the SMs are connected in series to build a medium-voltage (MV) level DC voltage, and the AC sides are connected in parallel. An isolation transformer with six windings is used for isolation at AC side. The challenges exhibited in the cascaded 3L-NPC converters are listed below.

#### 1.2.1 Demonstration of an MVDC converter

There are two main challenges encountered when operating an MVDC link based on cascaded 3L-NPC converters. The first one is how to design a suitable control system to achieve a desired performance. As control methods are always topology-dependant and as the cascaded 3L-NPC converter is a novel topology, suitable control methods are still under research. The second one is how to develop an experimental demonstrator to de-risk the practical operation of the MVDC system, as techniques employed in engineering projects should be tested offline before being applied into real applications. Although there are previous efforts assessing the performance of the converter system, most work has been conducted through computer simulations [6], [12] and [14].

#### 1.2.2 Stability Analysis of Cascaded 3L-NPC Converters

A special issue exhibited by cascaded 3L-NPC converters is DC voltage imbalance. As the DC terminals of Submodules (SMs) are connected in series, their shared DC voltages may be different. This may cause SM overvoltage and, potentially, an unstable system operation [15]. Although there are publications addressing the control of a single 3L-NPC converter, the DC

voltage imbalance within SMs of such converter has yet to be investigated and methods for balancing the DC voltages in a cascaded 3L-NPC converter have not been found in public resources. For MMCs, DC voltage imbalance may be also exhibited, but it is attributed to an unbalanced energy distribution in the SMs' capacitors during a fundamental period as these are plugged in and out in an alternating fashion. Since the cause for DC voltage imbalance is different, transferring control methods from MMCs to cascaded 3L-NPC converters to relieve this problem should be done with care.

#### 1.2.3 Multiple Crossovers in a Multi-terminal MVDC System

As more renewable energies integrated into the MVDC networks, the point-to-point system may be expanded to a multi-terminal system. This may pose additional challenges beyond voltage imbalance to the cascaded converters. As the converter stations in the multi-terminal system will adopt different control strategies and hence exhibit different control characteristics, multiple potential operating points (named crossovers) may arise due to the interactions between different control characteristics so that the power and voltage will drift from the original setting points [16], [17]. This may cause overvoltage or overcurrent, and hence a failure in the system. The influence of multiple crossovers on the control of cascaded 3L-NPC converters need to be explored.

#### **1.2.4 Reliable Operation Considering the Thermal Conditions**

Reliability have become an important criterion of performance and posed a great challenge to the design and control of power converters. Fifty-five percentage of power device failures is caused by abnormal thermal conditions [18]. High mean temperatures and temperature fluctuations can cause fatigue of package materials of semiconductors, thus leading to damages such as bond wire lift-off and solder crack. For the cascaded MVDC converters, thermal stresses among SMs are practically non-identical due to the mismatched component parameters and individual cooling system conditions of each SM, even though the SMs work at even loading or voltage sharing control. The lifetime of converter systems is determined by the first failed SM. As the temperature imbalance may cause premature damages to certain SMs, the system lifetime will then decrease [19].

#### **1.3 Objectives and Contributions of the Thesis**

The objectives and contributions of this work are outlined as:

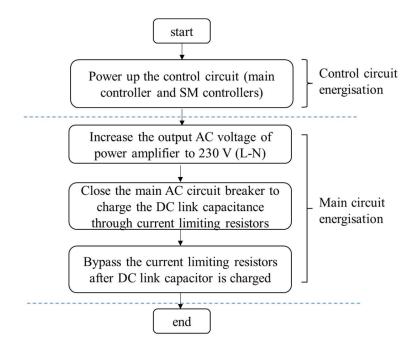

- Demonstrate the operation of a cascaded 3L-NPC converter-based MVDC link fitted with suitable control schemes. System operation is verified, step-by-step, following a hierarchical approach going from switching level to application level. For completeness, the communication and hardware protection schemes are discussed as well. A 30-kW laboratory scaled MVDC testbed is used to experimentally validate simulation results obtained using MATLAB/Simulink. This testbed has been down-scaled from the ANGLE-DC project, with similar per unit values as those employed in the real system. Using the experimental testbed, a number of simulation scenarios are experimentally verified including the start-up/shut-down procedure of the converter system, steady-state and dynamic performance of DC voltage and power control loops, and transitions between different control modes.

- Analyse the cause of DC voltage imbalance across SMs within a cascaded 3L-NPC • converter and present voltage balancing control methods to address this issue, with and without communication. It is revealed that the DC voltage imbalance may occur due to the inversely proportional relationship between the incremental DC voltage and duty cycle within an SM when under power control. This cause is further confirmed by analysing the system model, where each SM is represented as an equivalent impedance as viewed from the DC input terminal. Under DC voltage imbalance, there is an unstable system pole located at the right-half of the s-plane. Two balancing control methods are presented to shift the location of system poles and, hence, to mitigate the DC voltage imbalance: 1) a PI-based control method that requires communication with a central controller and 2) a communication-less inverse-droop-based control method. The communication-dependent PI-based method can achieve a precise balancing control of DC voltages and decoupling from the power controller. Upon loss of communication, the PI-based method is replaced by the inverse-droop-based method to prevent an interruption in system operation.

- Investigate the multiple crossovers due to the interaction between constant  $I_{dc}$  and  $P-V_{dc}$  droop control in the cascaded 3L-NPC converter based three-terminal MVDC system. The mechanism of the power and voltage drifts caused by the multiple crossovers are first analysed. It is found that the normal operating point is unstable in the condition of multiple crossovers. Then, the droop gain is suitably selected considering both the situation of multiple crossovers and DC voltage balancing performance, with another secondary power compensator being employed to guarantee

the power flow accuracy. Therefore, the multiple crossovers are avoided, and meanwhile, the DC voltage balancing, and power control accuracy are ensured. The presented solution has been experimental validated through a three-terminal MVDC testbed based.

Present the thermal sharing control of the cascaded 3L-NPC converter to balance the ٠ thermal stresses among SMs. A thermal sharing control loop was superposed on the typical current controller within each SM to regulate the active and reactive power according to individual SMs' junction temperatures, with the high-level main controller used to control the total power and calculate the temperature reference. The thermal control capability of this topology was discussed. Considering the thermal control capability, the main controller is used to manage the thermal conditions of the system by monitoring the temperature of each SM. On the one hand, the main controller modifies the temperature references once the outputs of SM's thermal PI regulators reach the upper or lower boundary. On the other hand, even though thermal sharing control is implemented, power semiconductors still have risks of exceeding the maximum allowable temperature in the event of extreme heating conditions. In this case, the converter would be blocked for protection. System modelling and controller parameter design were then presented in detail. The effectiveness of the presented method has been experimentally validated in the cascaded 3L-NPC converters.

#### **1.4 Thesis Outline**

The rest of this thesis is organized as follows:

**Chapter Two** provides a literature review of state-of-art research on MVDC converters. Different converter topologies of the cascaded DC/DC and DC/AC converters are studied. In particular, the performance of MMCs and cascaded 31-NPC converter are compared regarding the cost, efficiency and reliability. Finally, the control of cascaded converters is briefly reviewed. Two unique issues resulting from using such a type of converter, DC voltage thermal imbalance are pointed out. The corresponding control methods in previous works have also been reviewed.

**Chapter Three** presents hierarchical control strategy for the basic operation of the cascaded 3L-NPC converters. A high-level main controller with communication is used to send references and commands to converter SMs. The application control loops are included in the

main controller, while the switching-level and converter-level control loops are embedded in the SMs. With the use of a developed MVDC testbed, a series of scenarios were adopted to experimentally verify simulation studies conducted in MATLAB/Simulink.

**Chapter Four** presents the analysis and mitigation methods for DC voltage imbalance across cascaded 3L-NPC converter SMs. The mechanism of the voltage imbalance is given, followed by an in-depth small-signal model-based analysis. Then, two DC voltage balancing methods are presented, with communication and without communication. For completeness, the hybrid control structure considering partial SMs fitted with communication and others with without communication is discussed. The transition between these two control methods is also given. The effective of the presented method is experimentally validated.

**Chapter Five** presents the control scheme to eliminate multiple crossovers due to interactions between different converter stations, and meanwhile, to ensure the DC voltage balancing within cascaded 3L-NPC converters. This is achieved by suitable controller parameter design. In addition, a secondary power compensator is presented to ensure the power control accuracy. The effectiveness of the method has been validated through a three-terminal MVDC testbed.

**Chapter Six** presents an active thermal sharing control to improve the reliable operation of the cascaded converter. The structure of the thermal sharing control loop is presented, with a main controller used to send references. Based on the intrinsic characteristic of the cascaded topology, the thermal control capability is investigated. With a detailed system model, the gain of the thermal controller is suitable selected. The decoupling between the thermal sharing control and the output power control is also theoretically derived. The analyses and the control methods are verified in both PLECS simulation and experimental tests.

**Chapter Seven** presents the conclusions drawn, main findings and recommendations for future work.

### **1.5 List of Publications**

#### Journal Paper

- [1] J. Chen, W. Ming, C. E. Ugalde Loo, S. Wang and N. Jenkins, "Analysis and Mitigation of DC Voltage Imbalance for Medium-Voltage Cascaded Three-level Neutral-Point-Clamped Converters," *IEEE Trans. Power Electron*, vol. 37, no. 4, pp. 4320-4336, Apr 2022.

- [2] J. Chen, S. Wang, J. Liang, R. Navaratne and W.Ming, "Decentralized Control for Multi-terminal Cascaded Medium-Voltage Converters Considering Multiple Crossovers," *IEEE Trans. Power Delivery*, early access.

- [3] J. Chen et *al.*, "Demonstration of Converter Control Interactions in MMC-HVDC Systems", *Electron.*, vol. 11, no. 2, 2022.

- [4] J. Chen, S. Wang, C. E. Ugalde Loo and, J. Liang, I. Lüdtke, W. Ming, "Active Thermal Sharing Control of a Cascaded Three-Level Neutral-Point-Clamped Converter", *IEEE Trans. Power Electron*, under review.

#### **Conference** Paper

- J. Chen, W. Ming, C. E. Ugalde Loo and S. Wang, "Laboratory Demonstration of a Cascaded Three-Level Neutral-Point-Clamped Converter for Medium-Voltage DC Transmission," in *CIGRE Session*, Paris, Aug. 2022.

- [2] J. Chen, W. Ming, J. Liang, I. Ludtke and S. Wang, "Power Control Strategy for C3L-NPC converters considering thermal conditions," in *IEEE Conf. IECES 2023*, accepted.

- [3] W. Ming, J. Chen, J. Wu and J. Yu, "D-suite Technologies for Low-voltage Distribution Networks," in *Int. Conf. CIRED 2023*, accepted.

# **Literature Review**

This chapter presents a literature review on the technologies of the MVDC converters, including the topologies and control strategies for the cascaded medium-voltage DC/DC and DC/AC converters.

#### 2.1 Topologies of MVDC Converters

#### 2.1.1 Cascaded DC/AC Converters

The cascaded DC/AC converters used in the MVDC applications mainly include MMCs and cascaded 3L-NPC converters. To accommodate the MVDC operation, MMCs have been adapted from the HV level to the MV level and adopted in the previous projects. Apart from the MMCs, cascaded 3L-NPC have been recently used in the MVDC applications such as the ANGLE-DC project launched by Scottish Power Energy Networks (SPEN). Although both the types of converters were considered during the planning stage, the cascaded 3L-NPC converter was finally selected due to its low cost and since its performance meets all industry standards and requirement of UK's distribution system such as harmonic distortion, operating losses, reliability and availability[12], [13] and [20]. In [20], the cascaded 3L-NPC system was compared with an MMC-based configuration in terms of total cost of the ownership (TCO), return on investment (ROI), reliability (reflected as a B10 value which represents the time after which 10% of the components in a population of identical products or systems are expected to fail due to a specific type of failure mechanism. The larger B10 is, the longer the lifetime is expected) and efficiency. The main advantage using the 3L-NPC system is its significantly lower cost, although MMCs have slightly higher reliability and efficiency (e.g., for the ±27 kV DC voltage in Table 2.1, the efficiency and B10 of cascaded 3L-NPC converter are 98.26% and 1.04, compared to those of an MMC which are 5.91 and 99.13%, respectively). As such, the selection of the 3L-NPC converter topology can be seen a compromise among several measures. The detailed comparison provided in [20] is summarized in the Table 2.1.

According to Table 2.1, the TCO of a cascaded 3L-NPC converter is lower than the TCO of an MMC at any DC voltage level. For instance, for a  $\pm 27$  kV cascaded 3L-NPC the TCO is \$867,535, which is 17% lower than the cost of a  $\pm 27$  kV MMC (\$1045,470). This is mainly due to larger number of power devices (power semiconductors and passive devices) required in an MMC. Although the ROI of the cascaded 3L-NPC (ROI\_C3L-NPC=0.51) is slightly lower than that of the MMC (ROI\_MMC=0.64), this is due to the higher redundancy level in cascaded 3L-NPC converter. The ROI\_C3L-NPC will be higher than ROI\_MMC if the two types of converters are at the same redundancy level [20]. This economic benefit makes the cascaded 3L-NPC converter and very cost sensitive.

The cascaded 3L-NPC converter has a slightly lower efficiency and a reduced  $B_{10}$  life. For instance, at the ±27 kV DC voltage level, the efficiency and  $B_{10}$  life of the cascaded 3L-NPC converter are 98.26% and 1.04 years, compared with 99.13% and 5.91 years of MMC. Hence, for less cost sensitive applications requiring very high efficiency and  $B_{10}$  life, adoption of MMCs would be preferable.

TABLE 2.1. CHARACTERISTICS COMPARISON OF MULTI-LEVEL VSCS AT DIFFERENT DCVOLTAGE LEVELS.

| Voltage | Topologies                          | Efficiency<br>(%) | ROI          | Redundancy<br>(%) | ТСО                    | B <sub>10</sub> life<br>(years) |

|---------|-------------------------------------|-------------------|--------------|-------------------|------------------------|---------------------------------|

| ±10 kV  | Cascaded 3L-NPC<br>converter<br>MMC | 98.06<br>98.81    | 0.47<br>0.49 | 100<br>50         | 422,370<br>603,769     | 1.12<br>10.65                   |

| ±27 kV  | Cascaded 3L-NPC<br>converter<br>MMC | 98.26<br>99.13    | 0.51<br>0.64 | 83<br>22          | 867,535<br>1,045,470   | 1.04<br>5.91                    |

| ±50 kV  | Cascaded 3L-NPC<br>converter<br>MMC | 98.48<br>99.31    | 0.98<br>1.09 | 80<br>18          | 1,417,603<br>1,699,364 | 1.03<br>5.64                    |

The topologies of the MMCs are shown in Figure 2.1, including the half-bridge (HB) and fullbridge (FB) structures.

Figure 2.1. MMC topologies: (a) half-bridge; (b) full-bridge.

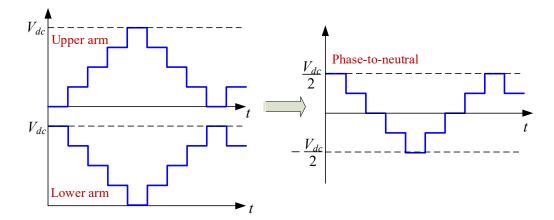

For the HB structure, each SM is a modularized HB two-level converter. The SMs switch on and off in turn during a fundamental period. This means that some SM capacitors are connected and meanwhile, the rest bypassed. The AC voltage waveforms of the upper and lower arms and the phase-to-neutral voltage are shown in Figure 2.2. As can be seen, the voltages at both arms are superposed with a DC offset, while phase angles of the AC components are complementary (see Figure 2.2(a)). The phase-to-neutral voltage is the difference between the upper and lower bridge arm voltages (see Figure 2.2(b)).

Figure 2.2. AC voltage waveforms of the MMC.

Compared with the FB option, the HB-MMC has lower power losses and capital cost due to the less used power semiconductors. However, the fault blocking capability of the HB-MMCs is inferior to the FB-MMCs. The HB-MMC does not have DC fault blocking capability, thus relies on AC or DC circuit breakers to isolate DC faults. Thyristors connected in anti-parallel to the SM terminals can be employed to bypass the short-circuit current and protect the freewheel diodes. However, this method does not isolate a DC fault and additional devices are required for fast fault isolation. To address the issues of DC faults, the FB-MMCs can be used for isolating the DC fault [22]. Also, considering the compromise between the DC fault blocking capability, power losses and cost, a hybrid structure comprising the HB and FB SMs were presented [23], [24].

Another fault issue is the single-phase-to-ground (SPG) short-circuit, which is also significant although the probability of occurrence is low [25]–[27]. The valve-side SPG faults in bipolar HB-MMCs will lead to grid-side nonzero-crossing currents and overvoltage of the SM capacitors in upper arms of converters. The grid-side AC circuit breaker (ACCB) may have difficulty in interrupting such nonzero-crossing fault currents. The upper arm overvoltage may

damage the SM capacitors and threaten the insulation of the converter. In Figure 2.3(a), when the SPG fault occurs, all IGBTs will be blocked. However, SM capacitors in the upper arms of the two non-faulted phases will be charged through the anti-parallel diodes during every negative half-cycle of the valve-side post-fault AC voltages. Also, due to the free-wheeling effect of diodes and the small resistance in the current paths, the currents flow through the lower arms in the two non-faulted phases are always positive. However, the nonzero-crossing fault currents can be avoided if the FB-MMCs are used. Figure 2.3(b) shows the current flowing path of a FB-MMC in case of the SPG fault. It can be seen that the upper bridge arms still encounter the overvoltage due to the charging of the upper DC capacitors. However, the current does not flow through the lower arms in the two non-faulted phases since all the diodes in the lower arms will be reversed-biased. Thus, there is no DC offset of the fault current and ACCB can be used to interrupt the connection between the converter and grid sides. Therefore, FB-MMCs are more suitable to be used in the situation where isolation of AC and DC faults are required.

Figure 2.3. Current flow paths under SPG faults: (a) half-bridge; (b) full-bridge.

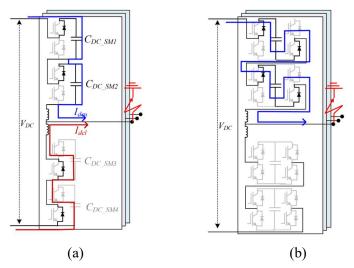

The cascaded 3L-NPC converters are another promising option for the MVDC application. The MVDC link in ANGLE-DC is based on two controllable VSC stations, as shown in Figure 2.4. For each converter station at the end of the DC circuit of the MVDC link, twelve DC series-connected 3L-NPC SMs are installed to build up the DC voltage to  $\pm 27$  kV. Sets of six SMs are connected with six-winding isolation transformers (see Tr.ij in Figure 2.4). The isolation transformer is with a vector group connection of Yd11, where the high-voltage (primary) winding is star-connected, and the low-voltage (secondary) winding is delta-connected with a 30-degree lead. A grounding resistor is connected in shunt at the midpoint of the cascaded SMs

to achieve a bipolar operation. Similar to the MMCs, in the case of SPG faults in the AC side of a SM, the SM's DC capacitor will be charged, which causes the overvoltage of this SM. The fault will be more severe when it occurs at the SM closest to the DC link as the capacitor will be charged to the DC link voltage [6]. A measure to address this is adding a thyristor branch in parallel with the DC terminal of each SM to discharge the capacitor, and meanwhile, the AC circuit breakers of both side converter stations are cut off to eliminate the fault current [6].

Figure 2.4. Cascaded 3L-NPC converters [12].

#### 2.1.2 Cascaded DC/DC Converters

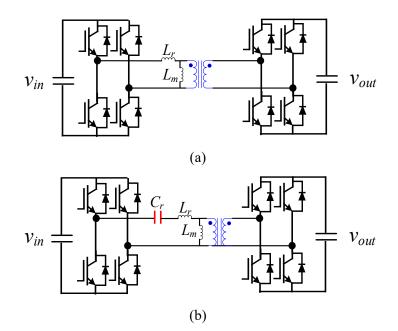

The cascaded DC/DC converters are mainly categorized as the modular configuration based and MMC based types [28] –[31]. The basic constituent submodule of the modular configuration-based type is a full-bridge dual active bridge (DAB) converter or an LLC resonant converter which consists of two inductances and a capacitor [32]. As shown in Figure 2.5, both types of converters comprise two full-bridge converters, two DC capacitors, a seriesconnected inductor (and an additional series-connected capacitor for the LLC resonant converter), and a high-frequency (HF) transformer. The HF transformer provides the required galvanic isolation and voltage matching between two voltage levels. The HF transformer is used to deliver the HF square waves of AC voltage with tens of kilohertz from one side to another. Compared with the conventional transformer designed for the sinusoidal waves, the HF transformer has the advantage of low volume, light weight, low cost, and can also avoid voltage and current waveform distortion caused by the core saturation of LF transformers. Also, the soft-switching operation can be achieved in both types to reduce the power losses.

Figure 2.5. Single DC/DC converters: (a) DAB converter; (b) LLC resonant converter.

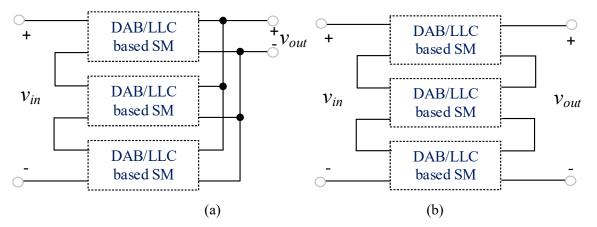

Individual DAB or LLC converters can be combined at will, to obtain different configurations of cascaded inverters. This is achieved by connecting individual SMs in parallel and series as needed. As shown in Figure 2.6, the general cascaded configurations include input-series-output-parallel (ISOP) and input-series-output-series (ISOS) [33]. The series connection is used for supporting a high DC link voltage while the parallel connection for withstanding a large current stress.

Figure 2.6. Modular configuration of the DC/DC converters: (a) ISOP connection; (b) ISOS connection [33].

Similar to the cascaded DC/AC converters, the SMs also need to be bypassed in fault conditions to ensure continuous operation. To achieve this, a thyristor-based protection circuit can be also paralleled with the DC capacitor to facilitate the bypassing operation upon failures of any SMs

[34]. [35] proposed a protection method and theoretically analysed the influence of bypassing operation on the dynamics of the fault and healthy SMs.

Although the DAB and LLC based modular configuration can achieve the high-power density, set against the advantage is the large potential differences between the primary and secondary sides, which places large stress on the insulation of the transformer windings and other components [36].

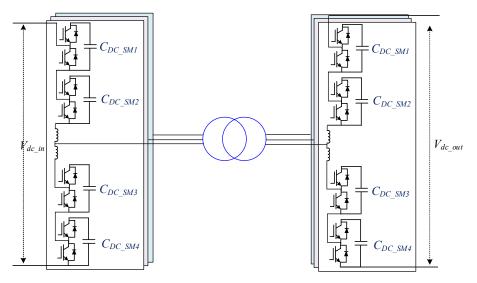

Another popular choice is using the MMC based front-to-front DC/DC converter (see Figure 2.7). Two half-bridge or full-bridge MMCs are combined to constitute the DC/DC converter. A medium-frequency transformer with several hundred hertz to several kilohertz can be used to reduce the transformer size, reactors and capacitors [37]. The soft switching can also be achieved for this type of converter. Another advantage is that the DC fault can be prevented from propagating from one side to the other side through suitable control. As traditional HF square modulation could raise high dv/dt in the transformer, the insulation will be affected. To this end, quasi-square-wave (QSW) and quasi-two-level (Q2L) operation were proposed to alleviate the high dv/dt [38]. However, due to the use of two sets of MMCs, the converter system becomes bucky and the volume is increased, thus reducing the power density.

Figure 2.7. MMC based DC/DC converters [37].

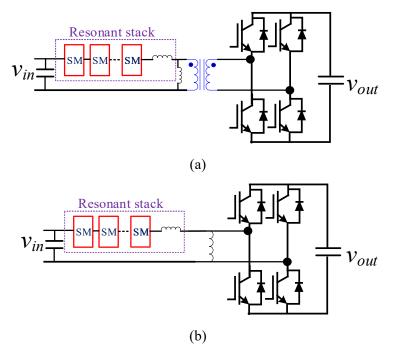

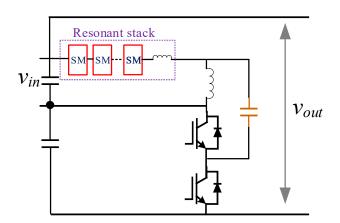

Additionally, the MMC based topology can be combined with the LLC resonant topology to form the resonant modular multilevel DC–DC converters (RMMCs) [39]– [41]. RMMCs inherit the advantages of both types of converters and are suitable for the high step-ratio and low step-ratio conversions. The high step-ratio conversion is usually adopted in the connection

between the MVDC and LVDC networks, while the low step-ratio conversion is applied in the connection between two MVDC networks with similar voltage levels. The basic RMMCs with high and low step-ratio are given in Figure 2.8 and Figure 2.9, respectively. The reader of interest to the evolution of the high step-ratio converter to the low step-ratio counterpart is referred to [41].

Figure 2.8. High step-ratio RMMC: (a) transformer-coupled RMMC; (b) transformer-less RMMC [41].

Figure 2.9. Low step-ratio RMMC [41].

## 2.2 Control of Cascaded MVDC Converters

#### 2.2.1 Voltage and Power Balancing Control

Similar to the general power electronic converters, the MVDC converters can control the active power and reactive power, and also are able to support voltage and frequency of the grid. The

MVDC converters can operate under grid following, grid forming and grid supporting control modes according to different applications[42], [43]. Among the control strategies, the technical challenges introduced by the cascaded topologies should be particularly focused. A common challenge for the cascaded converters such as the MMCs and cascaded DC/DC converters is the voltage imbalance across different SMs' capacitors. Without suitable control in place, the stability issue may arise.

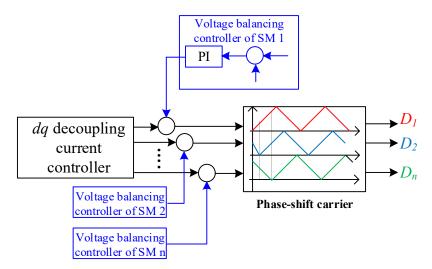

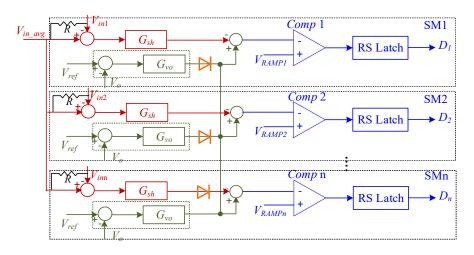

For MMCs, the PWM and nearest level modulation are commonly used. Capacitor voltage balancing control are different regarding the two modulation methods. The PWM methods include the phase disposition methods [44], [45] and phase shifts methods [46], [47]. The turnon and turn-off of each SM are determined by the comparison between the PWM carriers and the modulation wave. A PI based voltage balancing controller is superposed to the control variables generated by the current controllers to balance the voltage. The schematic is shown in Figure 2.10. In this scheme, the average voltage of each phase ( $\bar{v}_{cu}$ ) is compared with the voltage of the *m*<sup>th</sup> SM, the error goes to a PI controller and then generates a compensating control variable and the corresponding duty cycle  $D_i$ . Through this closed loop control, the DC voltage of each SM can trace the average value.

Figure 2.10. PWM based voltage balancing control.

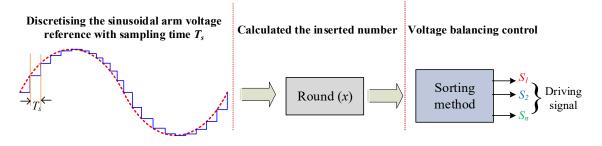

However, the PWM methods need a high switching frequency, and thus would lead to large power losses when the number of SMs increases. Hence, this method is not suitable for the high voltage applications where a great number of SMs are required. To address this challenge, the nearest level modulation was presented, and the sorting method was used to balance the SMs' voltages [48]–[50]. For nearest level modulation, the arm voltage reference is divided by the value of the capacitor voltage to calculate the desired voltage level. The voltage level decides how many SMs will be inserted as each SM generates one voltage level. As the calculated number may not be an integer, a rounding function is used to find the closest integer of the inserted number. A sorting method is then used to balance the capacitors' voltages. The principle of the sorting method is [48]:

- When the arm current charges the capacitors, the submodules with the lowest storage capacitor voltages will be switched on.

- When the arm current discharges the capacitors, the submodules with the highest storage capacitor voltages will be switched on.

The overall process is shown in Figure 2.11.

Figure 2.11. Nearest level modulation with sorting method for voltage balancing.

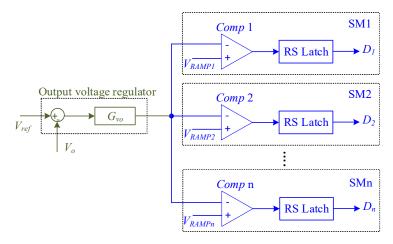

For the modular configuration based DC/DC converters, a three-loop control strategy using a dedicated input-voltage controller for ISOP connection was proposed in [51]. A simpler method which uses common-duty-ratio control was proposed in [52], where the duty ratio to all the converter modules connected in ISOP configuration is identical (see Figure 2.12). Thus, only a single closed control loop is enough. The voltage balance can be automatically achieved due to the common-duty-ratio control. However, the mismatched parameters among SMs may have adverse impact on the balancing performance. The voltage balancing performance is analysed by using both a small-signal averaged model and a steady-state DC model of the ISOP converter. It is hown that the sharing of input voltage is related to the mismatches in various parameters such as the leakage inductance, input capacitors and turn ratio of transformer.

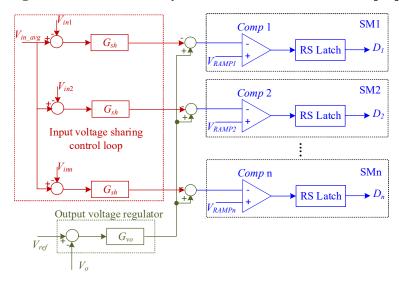

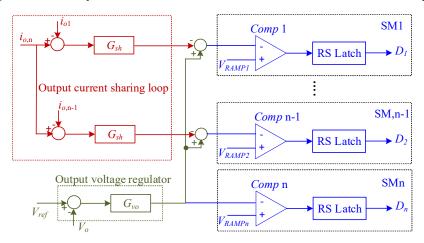

In order to improve the voltage balancing performance, the input voltage sharing (IVS) and output current sharing (OCS) loops are added [31], [53]. For the IVS method, the voltage sharing loop is embedded in each SM with a common output voltage controller, as shown in

Figure 2.13. Although the modularization has been greatly achieved, an external controller is still needed to coordinate the sharing control functions of the SMs, thus greatly compromising the flexibility of the system. In [15], a fully modularized method was proposed to make each SM able to operate in stand-alone mode. To achieve this, each SM has an own output voltage regulating loop. As there are mismatches in the voltage references and output voltage sampling coefficients of the modules, signal diodes should be used to ensure that only one output voltage regulating loop is active and regulates all the outputs of all modules. The proposed architecture is shown in Figure 2.14.

Figure 2.12. Common-duty control for DC/DC converters [52].

Figure 2.13. Input voltage sharing control for DC/DC converters [31].

The other sharing method named as the OCS is shown in Figure 2.15 [53]. With the control strategy, the duty cycles of modules with larger output currents will increase and the duty cycles of modules with smaller output currents will decrease, and finally to achieve OCS. As the output currents are equal, the input voltage balance is also achieved. Hence, altough the control

object is different with the IVS control, the final control effect of the two methods is the same. Another control alternative is the cross-feedback OCS-controlled method [54]. In this method, a voltage outer loop provides a common reference for the current loops of all SMs. The current feedback for a SM is not its own but the sum of currents of all other remaining SMs. However, with increase of the number of SMs, the control strategy will become complex due to the large amount of signal cables.

Figure 2.14. Fully modularized control method for DC/DC converters [15].

Figure 2.15. Current sharing control for DC/DC converters [53].

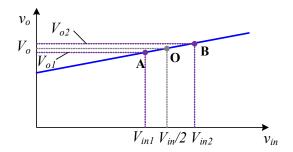

A common feature of the aforementioned methods is that a central controller is required to send the input voltage reference to the SMs. The system may malfunction upon the loss of the communication between the central controller and the SM controllers. To this end, the decentralized voltage balancing control methods were presented [55], [56]. The decentralized scheme is shown in Figure 2.16, where a  $V_0 - V_{in}$  inverse droop control is employed. Due to the droop characteristic, the operating point will move back to the original point during a perturbation in DC voltage. It can be seen that the larger the droop gain, the better the input voltage sharing accuracy. However, a larger droop gain leads to the deterioration of the system output voltage regulation performance. This trade-off between the input voltage sharing and the output voltage regulation performance was addressed in [57] by using another voltage shifting loop.

Figure 2.16. Decentalized voltage sharing control.

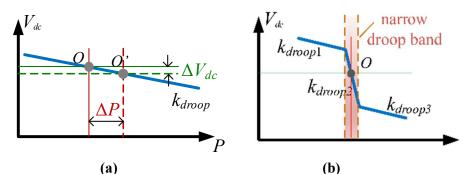

#### 2.2.2 Decentralized Control with Multiple Droop Characteristics

The decentralized control strategies are promising to be widely used in the MVDC systems [58]-[60]. The power feeding and voltage support can be automatically shared by power converters thus improving the voltage and power regulation, and meanwhile, decreasing the risk of system failures compared with the centralized control. Traditional decentralized control such as the power versus voltage droop method usually adopts a single droop slope [61]. Such control typically has a shallow droop (e.g. 5%) and thus acts like a voltage source more than a current source. In this case, the accuracy of power control is significantly impacted by any DC voltage disturbance. A slight DC voltage offset  $\Delta V_{dc}$  (e.g. caused by measurement errors of sensors) will cause a huge mismatch of power flow  $\Delta P$  as shown in Figure 2.17(a). Further increasing the slope of the droop will mitigate the inaccuracy but could lead to voltage instability in dynamic events (e.g. change of loads), which actually imposes greater threats to the MVDC systems.

Figure 2.17. Control characteristics in power versus voltage  $(P - V_{dc})$  droop. (a) Conventional droop cure with a single droop slope. (b) Improved droop curve with multiple droop slopes.

A popular solution to overcome this problem is to adopt multiple droop characteristics with one converter thus to precisely control the power while well stabilize the system in dynamic events. The control with multiple droop characteristics is shown in Figure 2.17(b). It features a narrow droop range (with a steep droop  $k_{droop}$ ) around the desired operating point [62]. Hence, the characteristic of the droop curve within this range is close to a current source. The power flow accuracy at dynamics is improved due to the less sensitivity of the high droop slope  $k_{droop2}$  to the voltage disturbance. If there is a large voltage or power change which exceeds the narrow band, the droop slope is changed to a smaller one ( $k_{droo}$  and  $k_{droop3}$ ), in order to support DC voltage.

Although the advantages of the multiple-slope based decentralized control have been reported in [63]-[65], the concerns of consequent adverse effects also arise. One of the adverse effects is the risk of multiple crossovers caused by the interactions between different converter stations and has been reported in limited resources such as [66], [69]. This may result in the shift of DC voltage and unintended power imbalances at converter stations. In [66], the multiple crossovers caused by the control characteristics was first discovered in a high-voltage direct-current (HVDC) link, where one converter station operated with constant power control and the other station with current versus voltage droop  $(I_{dc} - V_{dc})$  control. In [69], the multiple crossovers resulted from another typical control strategy- constant current and power versus voltage droop  $(P - V_{dc})$  control was studied. This type of control strategy has been widely used in the DC distribution networks where parts of converter stations are with droop control to regulate the DC voltage and the converters connected to renewable energies are with current control [70], [71]. The effects of multiple crossovers have been experimentally assessed through a MMC based HVDC link. Also, a guideline on how to select a suitable droop slope to avoid the multiple crossovers were given. However, the mechanism of the power and voltage drifts caused by the multiple crossovers remains unexplored. On the other hand, although multiple crossovers can be avoided by reducing the droop slope following the guideline in [69], this is in sacrifice of the narrow droop range - the power control accuracy at dynamics is decreased when the system is subjected to a perturbation in either DC voltage or current.

When the cascaded 3L-NPC converters adopt the multiple-slope based droop control, DC volatge balancing control should be properly designed in consideration together with the

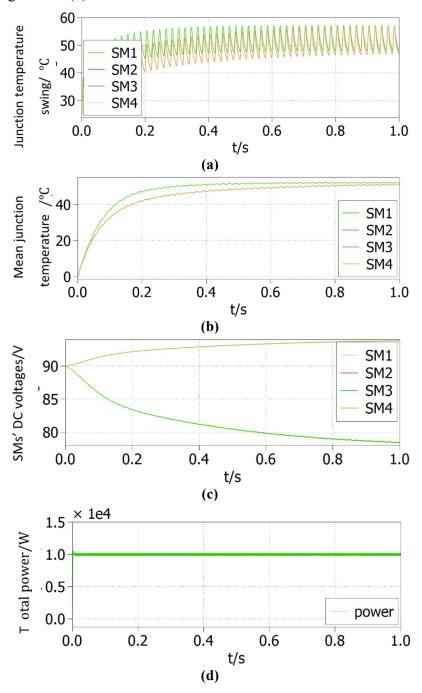

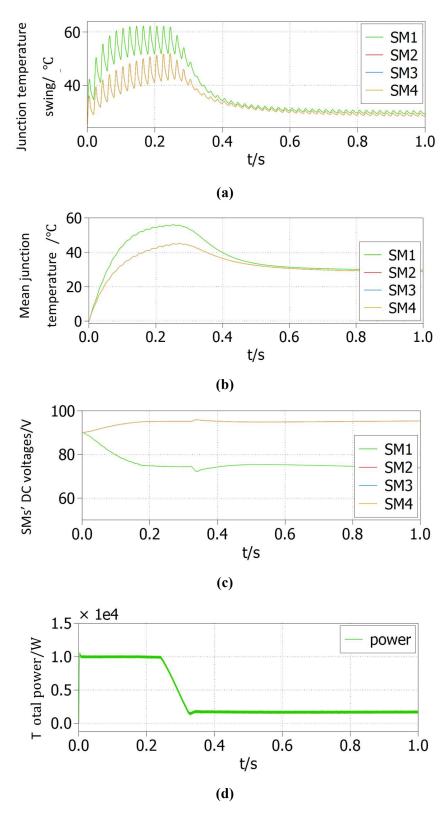

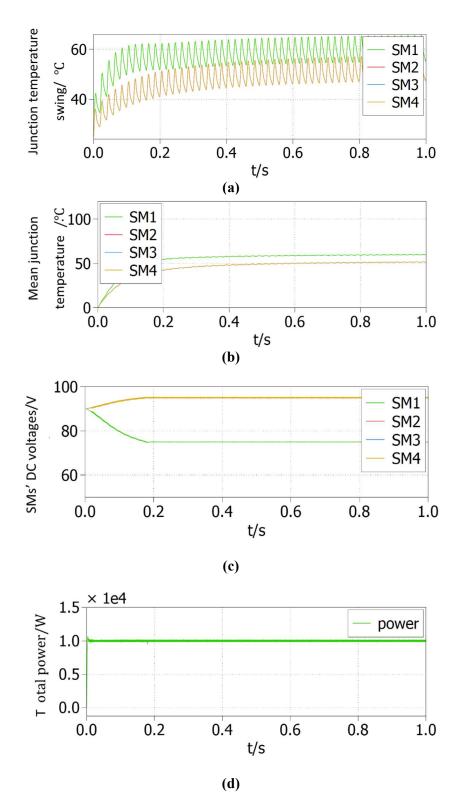

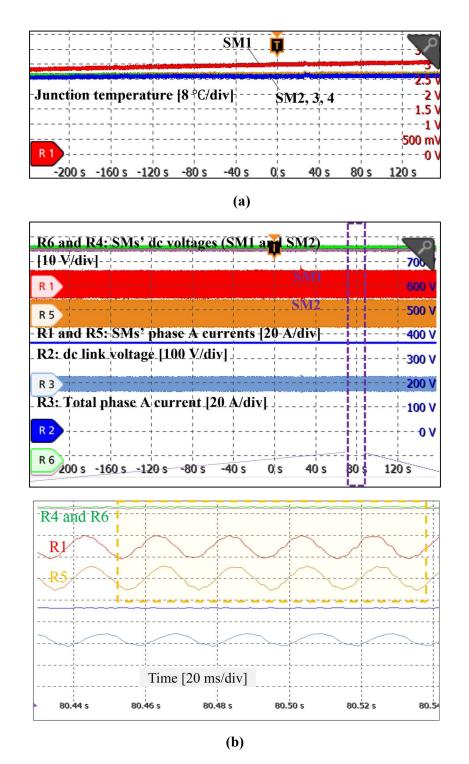

multiple crossovers and power control accuracy. In Figure 2.17, the smaller the slope is, the better the DC voltage balancing would be, but the power control accuracy will be affected.