# AlGaN/GaN Schottky Barrier Diode Technology for RF Application

Zehao Wu

School of Engineering

Cardiff University

This thesis is being submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

**Cardiff University**

August 2025

# Acknowledgements

I am deeply grateful to my supervisor, Professor Khaled Elgaid, for his unwavering support, invaluable guidance, and mentorship throughout the course of this research. His expertise and dedication have been instrumental in shaping the trajectory of this thesis.

My sincere thanks go to Dr. Abdalla Eblabla for his exceptional insights, invaluable discussions, and technical guidance. His contributions have been pivotal in enriching and refining this work.

I also extend my appreciation to Dr. Arathy Varghese for her insightful discussions, technical assistance, and constructive feedback. Her contributions have significantly contributed to the advancement of this research.

Heartfelt appreciation goes to my parents, Yuefeng Wu and Guiying Yan, for their constant encouragement, love, and understanding. Their unwavering belief in my abilities has been an enduring source of motivation and inspiration.

I extend my gratitude to all my colleagues and friends for their unwavering support, camaraderie, and enriching discussions that have illuminated my academic journey.

The completion of this thesis was made possible by the collective efforts and support of these exceptional individuals. I consider myself truly fortunate to have had them standing by my side.

# **Abstract**

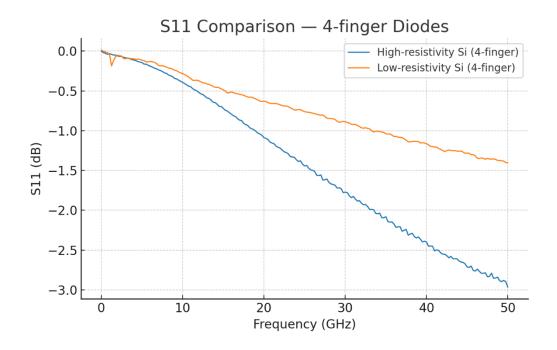

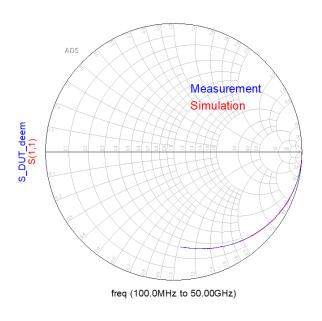

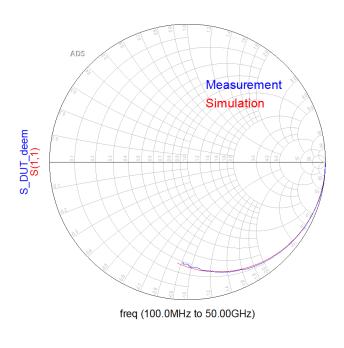

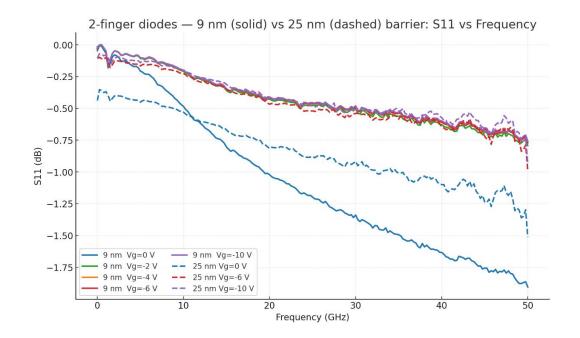

This thesis investigates AlGaN/GaN Schottky diodes on Si for Ka-band (26.5– 40 GHz) nonlinear front-ends. Device-level performance is governed by series/on resistance  $(R_s/R_{on})$ , junction capacitance  $(C_i)$ , and cut-off frequency  $(f_c)$ . Diodes with 2-/4-finger anodes were fabricated on high- and low-resistivity small-signal parameters were extracted from 100 MHz-50 GHz S-parameters using open/short de-embedding. Representative devices exhibit  $C_i \approx 15 \,\text{fF}$  at 0 V for a 2-finger high-resistivity sample, falling to  $\approx 6.9 \,\text{fF}$  at  $-10 \,\text{V}$ (~54% reduction). For a 25-nm/20%-Al barrier variant,  $f_c$  reaches ~163 GHz, providing ample Ka-band margin. Across 26.5-40 GHz, reverse bias consistently improves S11; under -10 V the high-resistivity substrate yields the best overall reflection. Extracted  $R_s$  spans ~46–102  $\Omega$  depending on layout and epilayer. These results demonstrate the suitability of the reported process and geometries for Ka-band mixers/multipliers and motivate leveraging reverse bias to trade  $C_j$  against impedance matching in circuit design.

# **Table of Contents**

| Chapter 1 Introduction                                         | 1  |

|----------------------------------------------------------------|----|

| 1.1 A brief history of GaN and Schottky diode                  | 4  |

| 1.2 Challenges and opportunities                               | 6  |

| 1.3 Market and industrial perspectives                         | 6  |

| 1.4 Research Aims and Objectives                               | 7  |

| 1.5 Thesis structure                                           | 8  |

| Chapter 2 AlGaN/GaN Schottky diode theory                      | 11 |

| 2.1 Material lattice mismatch and buffer layer                 | 12 |

| 2.2 2DEG formation                                             | 14 |

| 2.3 Metal-semiconductor contact                                | 18 |

| 2.3.1 Schottky contact                                         | 19 |

| 2.3.2 Ohmic contact                                            | 21 |

| 2.3.3 GaN cap layer                                            | 22 |

| 2.4 Schottky barrier diode operational principle               | 22 |

| 2.5 Schottky diode RF applications                             | 24 |

| 2.5.1 Mixer                                                    | 24 |

| 2.5.2 Multiplier                                               | 27 |

| 2.6 Conclusion                                                 | 28 |

| Chapter 3 AlGaN/GaN Schottky diode fabrication and measurement | 30 |

| 3.1 Introduction                                               | 30 |

| 3.2 Epilayer growth                                            | 30 |

| 3.2.1 MBE                                                      | 31 |

| 3.2.2 MOCVD                                                    | 31 |

| 3.3 Lithography                                                | 32 |

| 3.3.1 Photolithography                                         | 33 |

| 3.3.2 Electron beam lithography                                | 33 |

| 3.4 Etching                                                    | 34 |

| 3.4.1 Wet etching                                              | 35 |

| 3.4.2 Dry etching                                              | 36 |

| 3.5 Ohmic and schottky metal deposition                        | 39 |

| 3.5.1 Thermal evaporation                                                 | 39 |

|---------------------------------------------------------------------------|----|

| 3.5.2 Sputtering                                                          | 40 |

| 3.5.3 E-beam evaporation                                                  | 40 |

| 3.5.1 Lift-off technique                                                  | 42 |

| 3.6 Annealing                                                             | 43 |

| 3.7 Marker metal deposition                                               | 43 |

| 3.8 Diode fabrication flow                                                | 43 |

| 3.9 Device characterization                                               | 45 |

| 3.9.1 DC Current-Voltage (I-V) Measurements                               | 45 |

| 3.9.2 RF characterization                                                 | 46 |

| 3.10 On-wafer de-embedding                                                | 48 |

| 3.11 Conclusion                                                           | 51 |

| Chapter 4 Characterization of Diodes with Different Substrate Resistivity | 53 |

| 4.1 Introduction                                                          | 53 |

| 4.2 Wafer and substrate characteristics                                   | 55 |

| 4.3 Measurement result and parameters extraction                          | 57 |

| 4.4 Diode cut-off frequency                                               | 68 |

| 4.5 Diode RF performance under bias                                       | 69 |

| 4.6 Conclusion                                                            | 71 |

| Chapter 5 Effect of anode finger on device RF performance                 | 73 |

| 5.1 Introduction                                                          | 73 |

| 5.2 Epitaxial structure and design considerations                         | 74 |

| 5.3 Measurement and results                                               | 75 |

| 5.4 RF response to bias                                                   | 79 |

| 5.5 Conclusion                                                            | 81 |

| Chapter 6 Effect of AlGaN Layer on Device Performance                     | 83 |

| 6.1 Introduction                                                          | 83 |

| 6.2 DC measurement result                                                 | 84 |

| 6.3 RF characteristics                                                    | 88 |

| 6.4 Device response to bias                                               | 90 |

| 6.5 Conclusion                                                            | 93 |

| Chapter 7 Conclusion and future directions                                | 95 |

| 7.1 Conclusion                                                            | 95 |

| 7.2 Future directions           | 97  |

|---------------------------------|-----|

| References                      | 98  |

| Appendix A                      | 105 |

| Python code for SBH calculation | 105 |

# Chapter 1

# Introduction

Schottky barrier diodes (SBDs) have played a significant role in millimetre and sub-millimetre wave applications since the 20th century, owing to their capabilities in high-frequency operation, fast switching speed, and low forward voltage drop. Over the years, SBDs have undergone continuous advancements in materials, design, and fabrication techniques. Silicon (Si) has been the most commonly used semiconductor material, especially since Gordon Teal's development of the first commercial Silicon device in 1954 [1]. Si's widespread adoption is attributed to its abundance, low cost, and extensive availability worldwide. However, as the demand for higher power handling and operating frequencies grows, the limitations of current Si technology are becoming apparent. Intrinsic material characteristics, such as low breakdown voltage, low electron saturation velocity, and high resistance, have led Si technology to approach its theoretical limits [2]. There is a need for new materials that can surpass these barriers and further enhance device performance.

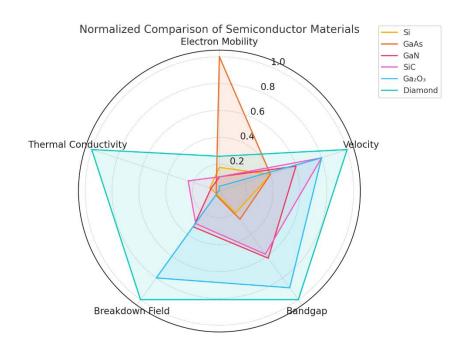

In contrast to Si technology, III-V compound semiconductor devices exhibit superior characteristics, including higher electron mobilities, which can significantly reduce device resistance. Table 1.1 presents a comparison of key parameters for Si, Gallium Arsenide (GaAs), Gallium Nitride (GaN), and the 2-dimensional electron gas (2DEG) formed at the Aluminium Gallium Nitride (AlGaN) and GaN heterojunction [3]. GaAs and GaN demonstrate higher electron mobility and a larger energy bandgap compared to Si, providing better power handling and potentially higher breakdown voltage.

Apart from electron mobility and saturated electron velocity, the energy bandgap of GaN is significantly larger than that of Si, enabling higher breakdown voltages and better power handling. To support the increasing demands of high-power and high-frequency systems, other wide bandgap materials such as Silicon Carbide (SiC), Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>), and Diamond have also drawn considerable attention in recent years. These materials offer a range of advantageous properties including high thermal conductivity, ultrawide bandgap, and superior breakdown fields.

Table 1.1 presents a comparison of key material parameters relevant to high-frequency Schottky diode applications. GaN offers a good trade-off between manufacturability (especially GaN-on-Si), power performance, and electron transport properties. Although Diamond exhibits exceptional thermal and electrical properties, its fabrication cost and integration challenges remain significant. Ga<sub>2</sub>O<sub>3</sub>, with an ultra-wide bandgap, shows promise for future generations of high-voltage devices, but its low thermal conductivity currently limits its RF potential.

Table 1.1 Main Parameters of Materials [3]

| Material          | Electron Mobility<br>(cm²/V·s) | Saturated<br>Electron<br>Velocity (×10 <sup>7</sup><br>cm/s) | Bandgap<br>(eV) | Breakdown<br>Field (MV/cm) | Thermal<br>Conductivity<br>(W/cm·K) | Wafer Size<br>(inch) | Remarks                                    |

|-------------------|--------------------------------|--------------------------------------------------------------|-----------------|----------------------------|-------------------------------------|----------------------|--------------------------------------------|

| Si                | 1500                           | 1.0                                                          | 1.12            | 0.3                        | 1.5                                 | Up to 12"            | Mature<br>technology,<br>low cost          |

| GaAs              | 8500                           | 1.0                                                          | 1.43            | 0.4                        | 0.5                                 | ≤ 6"                 | High mobility,<br>fragile                  |

| GaN               | 900                            | 1.5                                                          | 3.4             | 3.3                        | 1.3                                 | 6-8" (on Si)         | High<br>breakdown,<br>supports<br>2DEG     |

| SiC (4H)          | 900                            | 2.0                                                          | 3.2             | 3.0                        | 4.9                                 | ≤ 6"                 | Excellent<br>thermal<br>properties         |

| Ga₂O₃             | ~300                           | 2.0                                                          | 4.9             | >8.0                       | 0.1                                 | 2–4″ (lab<br>scale)  | Ultra-wide<br>bandgap, poor<br>thermal     |

| Diamond<br>(Bulk) | 2200                           | 2.5                                                          | 5.5             | ~10                        | 20                                  | <1" (lab<br>scale)   | Ideal material,<br>difficult to<br>process |

**Figure 1.1** Normalized comparison of key semiconductor material properties for high-frequency device applications

GaN, SiC, and Diamond show strong trade-offs between electron mobility, breakdown field, and thermal conductivity, with GaN offering the best balance for manufacturable RF diode platforms.

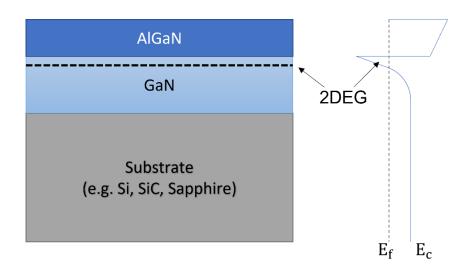

The discovery and investigation of the two-dimensional electron gas (2DEG) led to the development of a new class of semiconductor devices. The first transistor utilizing a 2DEG was reported in 1980, based on the AlGaAs/GaAs heterojunction, and was termed the high electron mobility transistor (HEMT) [4]. Compared to AlGaAs/GaAs devices, a major advantage of GaN is that a 2DEG can be spontaneously formed at the AlGaN/GaN interface due to strong spontaneous and piezoelectric polarization effects, without the need for intentional doping. This not only simplifies the epitaxial growth process and reduces cost, but also results in significantly higher electron mobility due to the absence of impurity scattering. As a consequence, AlGaN/GaN-based devices exhibit lower sheet resistance, higher current density, and superior high-frequency performance, making them highly suitable for RF and power applications.

Figure 1.2 Cross section of AlGaN/GaN heterojunction and band diagram

Figure 1.2 illustrates the cross-section of the basic AlGaN/GaN heterojunction and its band diagram. Band discontinuity occurs at the interface between two layers when materials with different band gaps are brought together. In the AlGaN/GaN scenario, a quantum well is formed, in which the 2DEG is trapped. Apart from the electron mobility, which has been described in Table 1.1, the 2DEG sheet electron density in AlGaN/GaN heterojunction is approximately  $10^{13}/\mathrm{cm}^2$ , which is also higher than AlGaAs/GaAs or other III-V materials (approximately  $10^{12}/\mathrm{cm}^2$ ) [5]. Details of AlGaN/GaN heterojunction and 2DEG will be discussed in chapter 2.

## 1.1 A brief history of GaN and Schottky diode

Gallium Nitride (GaN) is a wide-bandgap semiconductor material that has garnered significant attention and development since its discovery. The early research on GaN dates back to the 1970s; however, substantial progress in the growth and fabrication of high-quality GaN films and devices was not achieved until the 1990s.

In the early stages, GaN was primarily used in optoelectronic devices, such as light-emitting diodes (LEDs) and laser diodes, due to its ability to emit high-intensity blue light. The invention of the blue LED, which earned Isamu Akasaki, Hiroshi Amano, and Shuji Nakamura the Nobel Prize in Physics in 2014,

revolutionized the lighting industry and enabled the development of energyefficient white LED lighting.

As GaN technology advanced, its potential for high-power and high-frequency applications became evident. One of the most significant breakthroughs was the development of the AlGaN/GaN heterostructure, which allowed for the creation of 2DEG without the need for additional doping. This 2DEG-based AlGaN/GaN heterojunction became the foundation for high-electron-mobility transistors (HEMTs), enabling the creation of powerful and efficient RF amplifiers for wireless communication systems.

The Schottky diode, named after the German physicist Walter Schottky, is a type of metal-semiconductor junction diode that offers fast switching speeds and low forward voltage drop. Schottky diodes made with GaN materials exhibit excellent high-frequency characteristics due to the wide bandgap and high electron mobility of GaN. These attributes make GaN Schottky diodes well-suited for high-power and high-frequency applications, such as RF power amplifiers, microwave circuits, and radar systems.

The combination of GaN's superior material properties and the Schottky diode's advantageous characteristics has led to the development of GaN Schottky diodes for various RF applications. These diodes have found use in power electronics, wireless communication, satellite communication, and military radar systems, among others.

In recent years, ongoing research and advancements in GaN technology have continued to push the boundaries of semiconductor device performance. GaN-based devices are becoming increasingly prevalent in various applications, offering improved efficiency, power density, and reliability compared to traditional silicon-based devices.

## 1.2 Challenges and opportunities

Despite the significant progress in GaN Schottky diode technology, several challenges remain in realizing their full potential for RF applications. Some of the prominent challenges include:

High Cost of GaN Substrates: Despite the significant progress in GaN device development, the cost of bulk GaN substrates remains prohibitively high, restricting their large-scale deployment. Although GaN-on-Si and GaN-on-SiC technologies have emerged as more cost-effective alternatives, they suffer from challenges such as lattice mismatch, high dislocation density, and thermal expansion differences, which continue to limit device reliability and performance.

Epitaxial Growth and Material Quality: Achieving high-quality epitaxial growth of GaN layers on various substrates is critical for device performance. Controlling defects and dislocations during the growth process remains a challenge.

Thermal Management: GaN-based devices can generate a significant amount of heat during operation. Efficient thermal management techniques are required to ensure device reliability and long-term performance.

Despite these challenges, GaN Schottky diodes offer exciting opportunities for RF applications. Some of the key opportunities include:

Higher Power and Efficiency: GaN-based devices have the potential to handle higher power levels with lower losses, enabling more efficient and compact RF systems.

Wide Frequency Range: GaN Schottky diodes can operate over a wide frequency range, making them suitable for various RF applications, including 5G communication, radar, and satellite communication [6].

## 1.3 Market and industrial perspectives

The market for GaN-based devices, including Schottky diodes, has been rapidly expanding in recent years. The increasing demand for high-frequency and high-power devices in applications like wireless communication, automotive

electronics, and aerospace is driving the growth of the GaN semiconductor market.

The industrial perspective on GaN Schottky diodes for RF applications is highly positive. GaN-based devices have demonstrated superior performance characteristics, such as higher power density, wider bandwidth, and improved efficiency, compared to traditional silicon-based devices. As a result, industries involved in RF power amplifiers, wireless communication infrastructure, satellite communication, and radar systems are showing interest in adopting GaN Schottky diodes to enhance their products' performance.

## 1.4 Research Aims and Objectives

The objective of this thesis is to develop and optimise AlGaN/GaN Schottky barrier diodes (SBDs) on silicon substrates for microwave and millimetre-wave applications. Several GaN-on-Si structures have been designed and fabricated to investigate the influence of substrate resistivity, anode geometry, and epilayer structure on device performance. The AlGaN/GaN heterojunction was selected due to its strong 2DEG formation capability and the favourable intrinsic properties of GaN, such as wide bandgap and reasonable lattice compatibility with Si, which enables cost-effective large-area fabrication.

The aims of this research are threefold:

### 1. Optimisation of AlGaN epilayer structures

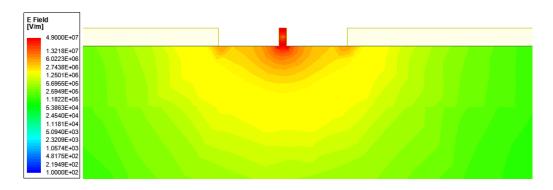

This work investigates the influence of AlGaN barrier thickness on diode performance. Two heterostructures with AlGaN thicknesses of 9 nm and 25 nm were selected and fabricated. These structures were designed to study the effect of barrier thickness on parameters such as junction capacitance, leakage current, and breakdown voltage. Silvaco TCAD simulations were used to assist the design phase by estimating electric field profiles and charge distribution across the heterostructure.

2. Design and fabrication of AlGaN/GaN Schottky diodes with different substrate resistivities

Devices were fabricated on both low-resistivity silicon ( $\rho$  < 0.03  $\Omega$ ·cm) and

high-resistivity silicon ( $\rho > 5000 \ \Omega \cdot cm$ ) substrates. This allowed a systematic

evaluation of substrate loss, coupling effects, and their impact on RF

performance metrics such as return loss and quality factor (Q). The

comparison between the two substrate types provides insights into substrate

selection for high-frequency applications.

3. Evaluation of anode geometry on device performance

Schottky diodes with varying anode geometries—specifically 2-finger and 4-

finger configurations—were designed and fabricated to study their impact on

series resistance, parasitic capacitance, and impedance matching. This

helped determine the influence of anode layout on both DC and RF

characteristics, and provided a basis for layout optimisation in future designs.

1.5 Thesis structure

The organization of the thesis is as follows:

Chapter 1: Introduction

This chapter provides an introduction to the research topic, "AlGaN/GaN

Schottky Barrier Diode Technology for RF Applications." It presents the

background of SBDs and their significance in high-frequency and high-power

applications. Additionally, it introduces the motivation for exploring GaN-based

diodes and the potential advantages they offer over conventional Si technology.

The research aims and objectives are clearly stated, outlining the focus of the

thesis and the areas of investigation.

Chapter 2: Theory of AlGaN/GaN Schottky Diode

8

In this chapter, the theoretical foundation of AlGaN/GaN Schottky diodes is explored in detail. It covers essential concepts such as the lattice mismatch of materials, the formation of 2-dimensional electron gas (2DEG) at the heterojunction interface, the effects of insertion layers and cap layers on device performance, and the principles of ohmic and Schottky contacts. This chapter provides a comprehensive understanding of the underlying physics and mechanisms governing the behaviour of AlGaN/GaN Schottky diodes.

#### Chapter 3: Fabrication Process

Chapter 3 describes the fabrication process of the AlGaN/GaN Schottky diodes. It includes the steps involved in the device fabrication, such as epitaxial growth, dielectric deposition, lithography, and metallization.

Chapter 4: Measurement and Analysis of AlGaN/GaN Schottky Diodes on Different Si Substrates

This chapter presents the measurement and analysis of AlGaN/GaN Schottky diodes fabricated on Si substrates with varying resistivity. The impact of different substrate resistivities on the diode's RF performance is thoroughly investigated and discussed. The chapter sheds light on how the choice of substrate material can influence the electrical characteristics and RF performance of the devices, providing valuable insights into optimizing the diode's behaviour for specific RF applications.

Chapter 5: Effect of the Number of Anode Fingers on Device RF Performance

This chapter delves into the effect of the number of anode fingers on the diode's RF performance. The fabrication of two-finger and four-finger devices allows for a direct comparison of how the anode geometry influences the device's characteristics. The extracted parameters and measurement results offer critical observations on the significance of anode finger design in optimizing the diode's RF performance, providing design guidelines for enhanced RF behaviour.

## Chapter 6: Effect of AlGaN Layer on Device Performance

Chapter 6 explores the effect of the AlGaN layer on the diode's performance. Two diodes with different AlGaN layer thicknesses are fabricated and characterized to understand the role of this epilayer in shaping the device's RF behaviour. The extracted parameters and comparison of the diodes provide valuable insights into the impact of the AlGaN layer on the diode's electrical properties, helping to optimize the design for improved RF performance.

#### Chapter 7: Conclusion and future work

Chapter 7 discusses the overall findings from the thesis and provides a comprehensive conclusion. It summarizes the key results and insights obtained from the experimental study on AlGaN/GaN Schottky diodes for RF applications. The chapter highlights the implications of the research in the context of current RF device technology and potential future advancements. Additionally, it discusses any limitations of the study and suggests areas for further exploration. Also presents the recommendations and future prospects for further research and development in the field of AlGaN/GaN Schottky diodes for RF applications. It identifies potential areas of improvement, explores novel device designs, and proposes new avenues for enhancing the performance and efficiency of RF devices based on the findings from the thesis. This chapter concludes the thesis by providing a roadmap for future research in the field of AlGaN/GaN Schottky diodes.

# Chapter 2

# AlGaN/GaN Schottky diode theory

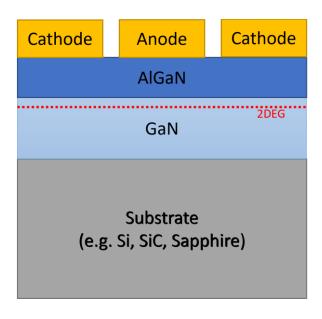

The typical AlGaN/GaN Schottky diode cross-section structure is shown in Figure 2.1. Several substrates can be used for growing GaN, including Sapphire (used in [7] and [8]), AlN and AlGaN (used as the nucleation layer for GaN on SiC substrate in [9] and [10]), GaN-on-Si technology (recently reviewed in [11]), and GaN-on-diamond devices (studied in recent years [12]).

The choice of substrate plays a critical role in determining the performance, cost, and scalability of GaN-based devices. Several substrate materials are commonly used for GaN epitaxy, including sapphire, silicon carbide (SiC), and silicon (Si). Each of these substrates presents trade-offs between thermal, electrical, and economic factors.

- Sapphire offers high resistivity and good lattice compatibility with GaN, but suffers from low thermal conductivity (~0.3 W/cm·K) and limited wafer sizes (typically ≤ 4"). Its brittleness and relatively high cost also limit its scalability.

- Silicon Carbide (SiC) provides excellent thermal conductivity (~4.9 W/cm·K) and close lattice matching to GaN, making it ideal for high-power and high-frequency applications. However, SiC substrates are expensive and limited in wafer size (up to 6"), which increases production cost.

- Silicon (Si) is the most cost-effective substrate due to its abundance, low bulk cost, and compatibility with large-diameter wafers (up to 12").

Moreover, Si processing benefits from decades of CMOS infrastructure, offering low-cost fabrication tooling and high-volume manufacturing

capability. The main challenges of GaN-on-Si include lattice mismatch, thermal mismatch, and higher dielectric losses, especially at RF frequencies. However, these can be partially mitigated through buffer layer engineering and advanced epitaxial techniques.

The GaN channel layer with a thickness of 1-3 $\mu$ m is positioned above the substrate. The barrier layer, with a higher bandgap compared to GaN, is used to form the 2DEG.  $Al_xGa_{1-x}N$  is commonly used as the material for the barrier layer, and its properties depend on the aluminum (Al) mole fraction x (ranging between x =0 and x =1). InAlN has also been studied as a barrier layer for InAlN/GaN heterojunction [13]. The anode and cathode are formed by metallization, and there are two types of metal-semiconductor contacts: Schottky contact for the anode and ohmic contact for the cathode.

Figure 2.1 Cross session of typical AlGaN/GaN Schottky diode

# 2.1 Material lattice mismatch and buffer layer

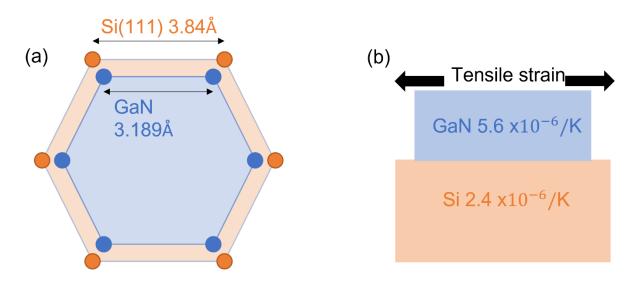

Epilayer growth is a critical process during device fabrication, as lattice mismatch and different thermal expansion coefficients between materials can lead to wafer cracking and bowing due to the high density of dislocations. Table 2.1 displays the lattice and thermal properties of several materials [14]. GaN film exhibits relatively larger mismatch with Si substrate compared to other materials (as shown in Figure 2.2 [15]).

Several approaches have been applied to minimize the mismatch between GaN film and Si substrate to grow the crack-free and high quality GaN film. Another problem of direct growth of GaN on Si is that a Ga–Si eutectic alloy will be formed due to the strong reaction between Ga and Si during the low temperature GaN layer growth [16], also known as melt-back etching.

Table 2.1 Lattice and thermal properties of SiC, sapphire, Si(111), AlN, GaN [2][14][17]

|                                          | SiC  | Sapphire | Si (111) | AIN   | GaN   |

|------------------------------------------|------|----------|----------|-------|-------|

| Lattice constant (Å)                     | 3.08 | 2.747    | 3.84     | 3.112 | 3.189 |

| Lattice mismatch to GaN (%)              | 3.5  | 16.08    | -16.9    | 2.4   | none  |

| Thermal expansion (x10 <sup>-6</sup> /K) | 4.3  | 7.5      | 2.4      | 4.15  | 5.59  |

| Thermal mismatch to GaN(%)               | 30   | -23      | 116      | 34    | none  |

Figure 2.2 GaN on Si (a) lattice mismatch, (b) thermal mismatch

Therefore, a thin film of AIN is widely used as nucleation layer on the top of Si. As can be seen from table 2.1, the lattice and thermal expansion coefficient mismatch between AIN and GaN is significantly smaller than those of Si and GaN. High quality AIN film can be grown on Si (111) due to the lattice matching between Si (111) and wurtzite AIN along certain crystallographic orientation and

through strain relaxation via large number of misfit dislocations at the Si/AIN interface [18], even there is 18.9% lattice mismatch between AIN and Si(111). A buffer layer is required above the nucleation layer to minimize the effect of mismatch on GaN channel layer to preserve the epilayer quality further. This buffer layer needs to be thick, and highly resistive. Commonly used buffer layer structure includes the graded AlGaN buffer [19, 20], AlGaN/GaN superlattice buffer [21, 22], AIN/GaN superlattice buffer [23, 24], and p-type doped GaN buffer. Mg and Fe are used as dopants in GaN buffer in [25] and [26] respectively, and C-doped GaN buffer is reported in [27, 28]. However, the Mg and Fe-doped buffer suffer from the memory effect. Memory effects in GaNbased devices are typically caused by trap states in the buffer layer or at the heterointerface, leading to delayed or hysteretic electrical responses under bias. These effects can degrade both DC stability and RF linearity, particularly in devices operated at high frequencies. In this work, a carbon-doped buffer layer was used instead of conventional Fe- or Mg-doped buffers. Carbon doping is widely reported to reduce the concentration of deep-level traps and associated memory effects, due to its non-metallic nature and better thermal/chemical stability within the GaN matrix [27]. As such, no significant memory effect was observed during characterisation, and no additional pulsed or transient techniques were required.

This design choice reflects a key trade-off in buffer layer engineering: achieving adequate isolation and resistivity while minimising dynamic trapping effects that compromise high-frequency performance.

#### 2.2 2DEG formation

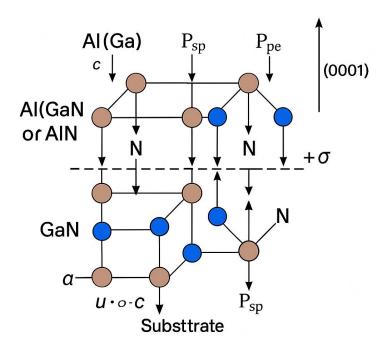

GaN channel layer is grown above the buffer layer, followed by the barrier layer. As mentioned earlier, the commonly used material for barrier layer to form the 2DEG with GaN is AlGaN. The band gap between GaN and AlGaN is similar due to the electrical and mechanism properties of AlGaN is between those of GaN and AlN. Therefore, the heterojunction can be formed without compromising the crystalline structure of these two materials. The polarization

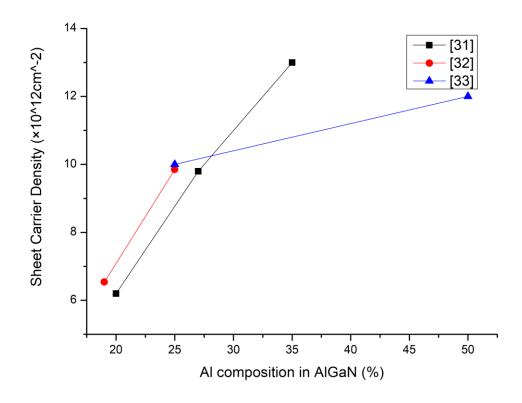

is generated when a wurtzite crystal symmetry is relaxed [29], it is called spontaneous polarization (P<sub>SP</sub>). P<sub>SP</sub> exists in both AlGaN barrier layer and GaN channel layer and contributes to the formation of 2DEG. As a piezoelectric material, when a film of AlGaN is grown on GaN, the piezoelectric polarization (Ppf) occurs due to the strain in AlGaN caused by the lattice mismatch between two layers. Figure 2.3 shows the crystal structure of AlGaN/GaN interface and the polarization in both layers [30]. With more Al composition in AlGaN layer, the electrical and mechanism properties of AlGaN is closer to AlN rather than GaN. This will increase the band gap and lattice mismatch between two layers, and the carrier density in 2DEG consequently. Figure 2.4 shows the sheet carrier density in 2DEG with different Al composition [31-33]. According to [31] an increase of Al composition from 20% to 35% results in a rise in the sheet carrier density from 6.2 x  $10^{12}cm^{-2}$  to 13 x  $10^{12}cm^{-2}$ . A similar trend is observed in another study [32], where an increase in Al composition from 19% to 25% leads to a rise in sheet carrier density from 6.54 x  $10^{12} \, cm^{-2}$  to 9.85 x  $10^{12} cm^{-2}$ . Moreover, even at a high Al composition of 50%, the carrier density remains substantial, reaching 12 x  $10^{12}$  cm<sup>-2</sup> as reported in [33]. However, in [31] the electron mobility decreases from 1440  $cm^2/VS$  to 1330  $cm^2/VS$  when the AI composition increase from 27% to 35%.

The higher 2DEG density at moderate Al composition enhances the screening of impurity and interface roughness scattering, which leads to improved electron mobility. Therefore, an initial increase in Al content can result in mobility enhancement, despite the concurrent presence of alloy disorder scattering.

Figure 2.3 crystal structure of AlGaN/GaN and the polarization in both layers

Figure 2.4 Sheet carrier density with different Al composition in AlGaN barrier

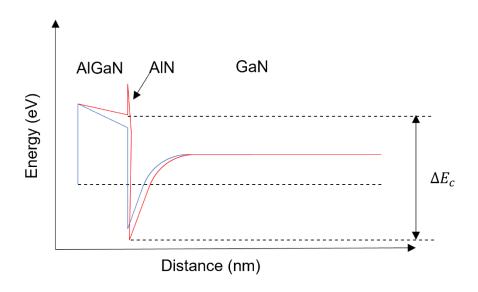

The 2DEG mobility is significantly affected by different scatterings, such as interface roughness scattering and alloy disorder scattering [34]. The AlGaN/GaN heterojunction suffer from the alloy disorder scattering, as AlGaN is a ternary compound, this will lead to a dissipation of electron and therefore the decrease of 2DEG mobility [35]. To improve the 2DEG mobility, a AlN spacer layer is applied between AlGaN barrier and GaN channel layer. It is found that HEMTs with AlGaN/AlN/GaN epilayer structure can supply high mobility 2DEG than that without the thin AlN layer [36]. The experiment in [35] shows that the insertion of AlN spacer layer increases the barrier height and therefore suppresses the electron penetration from GaN channel into the barrier, as shown in figure 2.5, the band diagram of AlGaN/GaN and AlGaN/AlN/GaN.

Figure 2.5 Band diagram of AlGaN/GaN (blue) and AlGaN/AlN/GaN (red)

The thickness of AIN spacer layer is critical, as with thick AIN layer, surface roughness scattering is more important than alloy disorder scattering. The experiment result reported in [37] shows that the carrier mobility increases with AIN thickness increases from 0nm to 1nm, while a sharp decrease can be observed when the thickness increased to 2nm. [38] also indicates that the heterojunction with 1.5nm AIN spacer layer has lower carrier mobility than AIGaN/GaN structure, and AIGaN/AIN/GaN with 2 nm AIN has the lowest mobility comparing to other two structures.

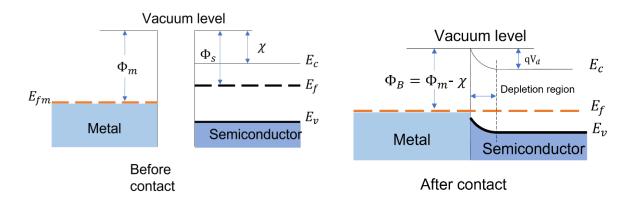

#### 2.3 Metal-semiconductor contact

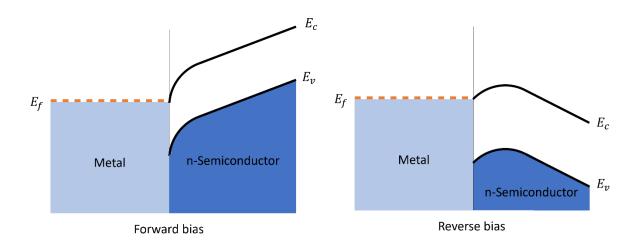

As mentioned above, there are two types of metal-semiconductor contacts, either ohmic contact or Schottky contact. The type of formed contact depends on the work function of the metal  $(\phi_m)$  and the electron affinity of semiconductor  $(\chi)$ . Figure 2.6 shows the energy band diagram for Schottky contact formed by metal and n-type semiconductor.

Figure 2.6 Energy band diagram of metal and n-type semiconductor Schottky contact

When a metal is brought into contact with an n-type semiconductor, the alignment of their Fermi levels leads to band bending at the interface. If the metal has a higher work function than the electron affinity plus conduction band edge of the semiconductor, the conduction band bends upward, resulting in the formation of a Schottky barrier with height  $\phi_B$ . This potential barrier limits electron flow from the semiconductor to the metal under equilibrium, and the resulting structure behaves as a Schottky contact.

Conversely, when a low work function metal is used, the conduction band bends downward, and the barrier for electron injection is greatly reduced. In this case, the contact exhibits ohmic behaviour, allowing bidirectional current flow with negligible barrier height.

Figure 2.7 shows the energy band diagrams of an ohmic contact under different biasing conditions. Under forward bias (positive voltage on the metal), electrons can easily move from the semiconductor into the metal. Under reverse bias

(negative voltage on the metal), electrons still encounter only a small barrier, enabling efficient injection from metal to semiconductor.

Figure 2.7 Ohmic contact energy band bending in bias

Electron transport between metal and semiconductor in Schottky diode can be divided into three main mechanisms, which are thermionic emission, electron tunnelling, and generation-recombination in the depletion region.

# 2.3.1 Schottky contact

In HEMTs and GaN-based Schottky diodes, the gate contact is typically designed as a Schottky contact. This enables the gate to modulate the 2DEG channel without forming a p-n junction, allowing for depletion-mode operation and low gate leakage under reverse bias. To reduce leakage through the gate, high work function metals are preferred, as they result in a larger Schottky barrier height and hence, lower tunnelling probability.

Table 2.2 shows the work function of several commonly used metals and the ideal Schottky barrier height formed with GaN. As shown in Table 2.2, metals with higher work functions such as Pt, Ni, and Pd form larger Schottky barriers with GaN, which helps suppress reverse leakage current. This is particularly important for Schottky diodes operating at high frequencies, where low leakage and high rectification efficiency are desired.

Table 2.2 Metal work function and Schottky barrier height formed with GaN

|                             | Al   | Ti   | Au  | Pd   | Ni   | Pt   |

|-----------------------------|------|------|-----|------|------|------|

| Work function $\phi_m$ (eV) | 4.28 | 4.33 | 5.1 | 5.12 | 5.15 | 5.65 |

| Schottky barrier height     | 0.18 | 0.23 | 1   | 1.02 | 1.05 | 1.55 |

| $\phi_B$ (eV)               |      |      |     |      |      |      |

Au/n-Gan Schottky contact was formed in [39, 40], and the measured barrier height are 1.02 eV and 0.87 eV respectively. However, Au tends to diffuse into GaN under thermal or electrical stress, creating interfacial states and reducing the effective Schottky barrier height, thereby increasing reverse leakage current [41]. Pt/n-GaN and Pd/n-GaN Schottky barrier were reported in [42], the measured barrier height are 1.27 eV and 1.24 eV respectively. Apart from the work function, metal's adhesion to semiconductor is also critical to metal-semiconductor contact. Ni has better adhesion to GaN comparing to Au and Pt [43]. In these cases, the most commonly used for Schottky contact is Ni/Au. The use of Au is to prevent oxidation and improve the conductivity. Table 2.3 shows the Schottky barrier height and ideal factor of different Ni/Au/n-GaN contact [44].

Table 2.3 Schottky barrier height and ideal factor of Ni/Au/n-GaN contact

| Source                       | [41]  | [42]   | [45]  | [46]   | [47]  |

|------------------------------|-------|--------|-------|--------|-------|

| Ni/Au thickness (nm)         | 30/50 | 10/300 | 40/80 | 50/300 | 30/50 |

| Schottky barrier height (eV) | 1.3   | 0.88   | 0.86  | 1.18   | 0.91  |

| Ideal factor n               | ~1.8  | 1.18   | 1.17  | 1.78   | 1.52  |

In addition to diodes, Schottky gates are widely used in GaN-based HEMTs to modulate the 2DEG channel without forming a p-n junction. A high Schottky barrier gate metal such as Ni/Au helps reduce gate leakage under reverse bias, which is essential for achieving high breakdown voltage and stable RF performance.

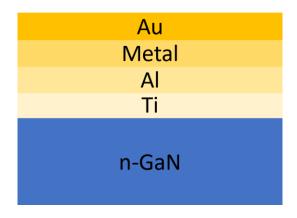

#### 2.3.2 Ohmic contact

A good ohmic contact requires the metal-semiconductor contact resistance to be low. It can be seen from table 2.2 that the two candidates for ohmic contact forming are Al and Ti, due to their low work function. However, Al-only or Ti-only ohmic contact is not preferred due to the high oxidation propensity and their low reliability on high power and high temperature properties, and the low melting point of Al (600 °C) causes the thermal stability problem [48]. Ti/Al/metal/Au metal stack is mostly used for ohmic contact with n-GaN, as shown in figure 2.8.

Figure 2.8 Ti/Al/metal/Au metal stack on n-GaN Ohmic contact

When the Ti is used as the first metal layer, the N atoms from n-GaN will be extracted by the Ti atoms and forms TiN compound. The N vacancies in the surface of GaN becomes the electrically active donors. The formation of TiN compound reduces the effective barrier height due to its lower work function (3.74eV) than Ti. The N vacancies leaved in GaN allow electrons flow via tunnelling and therefore reduce the contact resistivity. Experiment in [49] indicates that the strong reaction between Ti and GaN creates the TiN layer, and also a thicker Ti-Ga alloy above the TiN. This strong reaction leaves a large area of void between Ti and GaN, and increases the contact resistance as a result. However, a Al layer above Ti can decrease the Ti-GaN reaction by alloying with Ti. The reason using Au on the top of ohmic contact is the same with Schottky contact, to prevent the oxidation and increase the conductivity. The metal layer between Au and Al is a diffusion barrier to reduce the diffusion

of Au to Al and Ti. Table 2.4 shows the specific contact resistance ( $\rho_c$ ) of different metal stacks [50-55].

Table 2.4 Specific contact resistance of different metal stacks

|             | Thickness (nm) | $\rho_c \ (\Omega \cdot cm^2)$ | Reference |

|-------------|----------------|--------------------------------|-----------|

| Ti/Al/Ni/Au | 25/80/20/100   | $1.2 \times 10^{-5}$           | [48]      |

|             | 20/20/20/200   | $3.15 \times 10^{-5}$          | [49]      |

| Ti/Al/Ti/Au | 30/100/30/30   | $6 \times 10^{-7}$             | [50]      |

|             | 20/170/5/50    | $2.2 \times 10^{-5}$           | [51]      |

| Ti/Al/Pt/Au | 30/100/40/20   | $8.4 \times 10^{-5}$           | [52]      |

|             | 25/100/50/200  | $8 \times 10^{-6}$             | [53]      |

## 2.3.3 GaN cap layer

The electron affinity ( $\chi$ ) of AlGaN decreases with increasing Al mole fraction[56]. For an n-type Schottky contact, the ideal barrier height follows  $\phi B \approx \Phi M - \chi$ ; hence a lower  $\chi$  (higher Al content) increases the ideal  $\phi B$ . Thicker barriers also reduce tunnelling, typically lowering reverse leakage. (We therefore interpret composition-dependent trends in SBH accordingly in later chapters.). A film of GaN is applied on the AlGaN barrier as the cap layer to improve the effective barrier height, suppress the current leakage [57], due to the lower  $\chi$  of GaN than AlGaN. The growth of GaN cap layer can also suppress the current collapse caused by the surface state [58].

# 2.4 Schottky barrier diode operational principle

In an AlGaN/GaN Schottky diode, the current flow is primarily governed by the presence of a Schottky barrier at the metal-semiconductor interface and the formation of a 2DEG in the AlGaN/GaN heterostructure. These factors determine the diode's behavior in both forward and reverse bias conditions, making it a valuable component in various electronic devices and circuits.

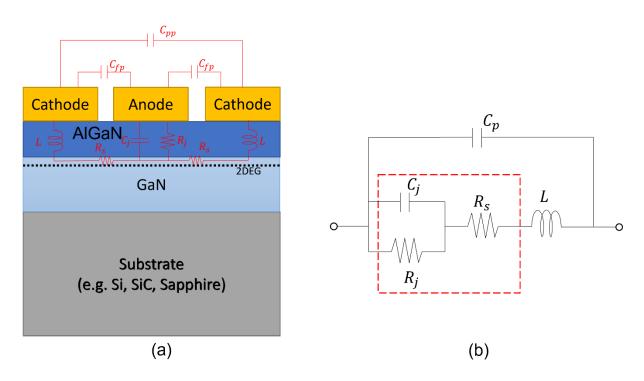

Figure 2.9 illustrates a comprehensive RF equivalent circuit model for Schottky Barrier Diodes (SBDs), essential for analyzing the diode's operational characteristics in RF applications. The equivalent circuit is an abstraction that simplifies the diode's behavior by representing its physical phenomena with idealized circuit elements, each contributing to the overall performance.

- Parasitic Capacitances ( $C_{fp}$ ,  $C_{pp}$ ): These capacitances are due to the physical layout and dielectric properties of the diode's construction. Parasitic capacitances can lead to undesired coupling between different parts of the circuit, causing signal distortion and loss of efficiency, especially at high frequencies where capacitive reactance becomes significant.

- Inductance (L): The inductance symbolized here primarily accounts for the effects of lead and wiring inductances. These inductive components are vital in high-frequency circuits as they can resonate with capacitive elements, affecting the impedance and phase response of the diode.

- Series Resistance ( $R_s$ ):  $R_s$  is critical in RF diode performance as it contributes directly to insertion loss and can degrade signal-to-noise ratio. Minimizing  $R_s$  is vital for maintaining efficiency, particularly in power-sensitive applications. It is influenced by the materials and the geometry of the diode's construction.

- Junction Resistance (R<sub>j</sub>): In a reverse-biased state, R<sub>j</sub> is considered to be very high, effectively isolating the anode from the cathode. This high resistance ensures that the reverse current remains negligible, a desirable property for rectification and switching applications.

- Junction Capacitance (C<sub>j</sub>): C<sub>j</sub> at zero bias (C<sub>j0</sub>) is a function of the depletion region's physical dimensions and the dielectric constant of the semiconductor material. It affects the charging time and, consequently, the speed at which the diode can switch from conducting to nonconducting states.

The cut-off frequency ( $f_T$ ), representing the maximum frequency at which the diode can effectively operate as a rectifier, is given by equation 2.1:

$$f_T = \frac{1}{2\pi C_{j0} R_S} \tag{2.1}$$

Figure 2.9 (a) Schematic cross-section of an AlGaN/GaN Schottky barrier diode and (b) its equivalent circuit model

# 2.5 Schottky diode RF applications

Schottky diodes find widespread applications in radio frequency (RF) circuits due to their unique characteristics and superior performance at high frequencies. Their key attributes make them essential components in various RF applications, providing benefits such as low noise, fast switching speeds, and minimal power dissipation. In this section, we will explore the significant RF applications of Schottky diodes and highlight their advantages in these areas.

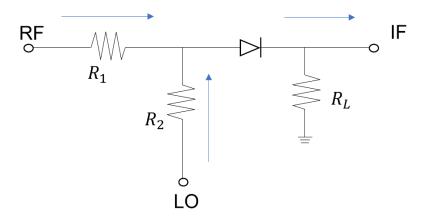

#### 2.5.1 Mixer

In high-frequency communication systems, particularly in the W-band (75–110 GHz), Schottky diodes are widely used as mixers due to their fast switching, low capacitance, and nonlinearity. These mixers serve as key components for

up/down-converting RF signals to intermediate frequencies (IF), which is essential in radar, satellite receivers, and point-to-point communication systems. GaN-based Schottky diodes, with their superior breakdown voltage and power handling capabilities, have become strong candidates for future high-frequency mixer designs.

A simplified single diode mixer schematic is shown in Figure 2.10, illustrating the basic configuration. However, practical diode mixers are more complex and often involve multiple diodes and additional circuitry for improved performance. Various mixer designs, such as single-balanced, double-balanced, and single-sideband, are employed to optimize specific applications.

Figure 2.10 Simplified single diode mixer schematic

The power level of the local oscillator (LO) signal plays a critical role in determining the mixer's conversion gain. A higher LO power level can result in a higher conversion gain (lower conversion loss). However, it is essential to ensure proper LO-RF and LO-IF isolation, as well as impedance matching at the LO, RF, and IF ports to maximize the conversion gain. Mismatched ports can lead to signal reflections and loss of power, impacting the overall performance of the mixer.

Table 2.5 compares the reported performance of mixers across a range of frequencies and LO power levels. The goal here is to illustrate the typical conversion loss achievable in real-world designs, as well as the LO drive requirements.

From this table, it is evident that mixers operating in the mm-wave region (e.g., 75 GHz, 91 GHz, 94 GHz) require relatively high LO power (~10–15 dBm) and still suffer from non-negligible conversion losses (>5 dB). This highlights the importance of optimizing the diode parameters—particularly series resistance and junction capacitance—to minimize losses at these frequencies.

Table 2.5 Reported performance of mixer at different operation frequencies

|                      | [59] | [60] | [61] | [62] | [63] |

|----------------------|------|------|------|------|------|

| Frequency(GHz)       | 2.5  | 94   | 10   | 91   | 75   |

| LO power(dBm)        | 10   | 9.5  | 13   | 12   | 15   |

| Conversion loss (dB) | 12.9 | 5.5  | 8    | 8.5  | 11.4 |

These insights reinforce the motivation behind this thesis: to develop Schottky diodes with low R\_on, reduced C\_j, and high cut-off frequency, making them suitable for future W-band mixer applications.

The series resistance in the diode is a crucial factor influencing mixer performance. A higher series resistance can lead to increased power losses and reduce the conversion gain [64].

Parasitic capacitance refers to unintended capacitances present in the diode structure due to its physical layout and the presence of other conductive elements. These capacitances can introduce additional reactance into the circuit and reduce the conversion gain, especially at high frequencies [65].

Furthermore, the junction capacitance of the diode also plays a significant role in determining the mixer's performance. The junction capacitance affects the diode's impedance, which is essential for matching the input and output signals to achieve optimal conversion gain. Proper tuning and optimization of the junction capacitance are necessary to maximize the mixer's overall efficiency.

#### 2.5.2 Multiplier

In addition to mixers, Schottky barrier diodes (SBDs) are widely employed as nonlinear elements in frequency multipliers. These circuits generate harmonic signals of the input frequency and are essential for producing high-frequency local oscillator (LO) signals in radar, spectroscopy, and wireless communication systems, particularly in the millimetre-wave and terahertz bands.

GaAs-based SBDs have traditionally been used in commercial multiplier designs due to their high cutoff frequency and mature fabrication technology. However, recent studies have shown that GaN-based SBDs offer promising advantages in terms of higher breakdown voltage, thermal stability, and power handling, which are particularly desirable in high-power mm-wave frequency multipliers.

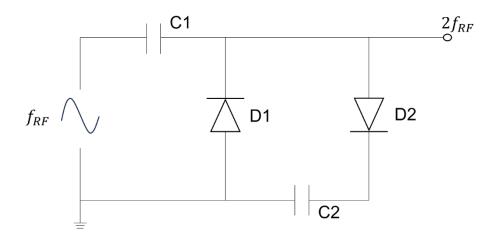

A basic Schottky diode frequency multiplier configuration is shown in Figure 2.11, where the input signal  $(f_{RF})$  is applied to a single diode that generates output components at harmonics such as  $2^*f_{RF}$ ,  $3^*f_{RF}$ , etc. While the simplified schematic illustrates a basic doubler, practical multiplier designs often incorporate multiple diodes in anti-parallel or balanced configurations, along with resonant circuits and impedance-matching networks to optimise the output power and spectral purity.

Recent works demonstrate the potential of GaN-based multipliers in achieving high efficiency and output power at mm-wave frequencies. For example, Kim et al. [66] reported a 94 GHz GaAs tripler achieving 12.5% efficiency, while Choi et al. [67] demonstrated a GaN-based W-band doubler with an output power exceeding 100 mW. These studies highlight the evolution of Schottky multipliers from low-power designs toward high-efficiency solid-state sources suitable for demanding mm-wave applications.

The development of GaN SBDs with low junction capacitance and high thermal stability is crucial to further improving the performance of frequency multipliers

operating beyond 100 GHz. This motivates the exploration in this thesis of GaNon-Si diode structures optimised for such nonlinear RF applications.

Figure 2.11 Diode doubler circuit

#### 2.6 Conclusion

This chapter provides a detailed exploration of the theoretical and operational principles of AlGaN/GaN Schottky diodes, focusing on the following key aspects:

- Lattice Mismatch and Buffer Layers: The chapter discusses the significance of lattice mismatch and buffer layers in the fabrication of AlGaN/GaN Schottky diodes. These factors significantly impact the performance and reliability of the devices.

- Formation of the Two-Dimensional Electron Gas (2DEG): A thorough discussion is presented on the formation of 2DEG in AlGaN/GaN heterostructures. The 2DEG is key to the high performance of these diodes.

- Types of Metal-Semiconductor Contacts: The mechanisms of Schottky and Ohmic contact formation and their impact on device performance are analysed.

- 4. RF Applications of Schottky Diodes: The chapter emphasizes the application of Schottky diodes in RF systems, such as mixers and

frequency multipliers, and highlights the importance of proper circuit design and diode characteristics for performance optimization.

The research in this chapter not only provides deep insights into the fundamental theories behind AlGaN/GaN Schottky diodes but also offers significant guidance for their practical applications in RF systems. Through careful consideration of material selection, device structure, and circuit design, the performance and efficiency of these diodes can be further enhanced, playing a vital role in high-frequency and high-power applications.

# Chapter 3

# AlGaN/GaN Schottky diode fabrication and measurement

#### 3.1 Introduction

This chapter presents a detailed fabrication process of AlGaN/GaN Schottky diodes, which are essential components for achieving efficient and reliable electronic devices in various applications, including high-frequency and high-power circuits. The unique material properties of the AlGaN/GaN heterostructure make it a promising platform for Schottky diodes in RF circuits.

The fabrication process involves a series of carefully optimized steps, including material growth, device structure design, lithography, etching, metallization, and device characterization. Each step plays a crucial role in determining the final device characteristics and performance. This chapter highlights the key aspects of each fabrication step and discusses the influence of process parameters on the resulting device properties.

# 3.2 Epilayer growth

The first step in the fabrication process is the growth of the AlGaN/GaN heterostructure on a suitable substrate. Epilayer growth is to transport the atoms of material from high purity sources to the substrate wafer surface. The commonly used GaN growth methods are Molecular Beam Epitaxy (MBE) and is metal-organic chemical vapour deposition (MOCVD).

#### 3.2.1 MBE

MBE is a sophisticated and highly controlled method used for the synthesis of thin films and crystal structures layer by layer on a substrate. Conducted in an ultra-high vacuum environment, MBE introduces elemental or compound sources, which are heated to produce a directed molecular or atomic beam towards a substrate. As the particles arrive at the substrate surface, they can migrate, interact, and integrate into the growing film, ensuring precise control over layer thickness, composition, and doping. One of the key advantages of MBE is the precise control it offers, making it possible to grow high-quality epitaxial layers with atomically sharp interfaces [66]. However, the growth rate of GaN using MBE is typically below  $1\mu m/h$ . The low growth rate has limited MBE's application in the demand for thick GaN and increased production costs [67].

#### **3.2.2 MOCVD**

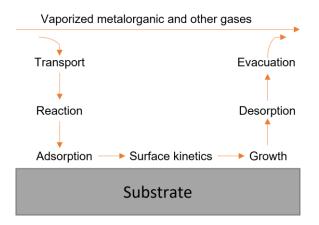

The technique used in this thesis to grow epitaxial structures is MOCVD. The growth parameters should be optimized during this process, such as the growth temperature, and reactant gases flow pattern [68]. MOCVD is a widely used epitaxial growth technique that enables precise control over the material composition and thickness. The growth process involves the decomposition of metal-organic precursors in a heated reactor, resulting in the deposition of crystalline AlGaN and GaN layers on the substrate. In MOCVD, chemicals are vaporized and react with other gases in the reaction chamber to turn the chemicals into desired crystal. Comparing to MBE, the growth rate of GaN epilayers using MOCVD commonly exceeds 1-3 $\mu$ m/h. Figure 3.1 shows the deposition process on substrates surface.

Figure 3.1 Deposition Process on substrate surface

The quality, uniformity, and crystalline nature of the GaN films heavily depend on the choice of precursors. Trimethyl gallium (TMGa) and triethyl gallium (TEGa) are the most commonly utilized gallium precursors, and the nitride precursor is ammonia ( $NH_3$ ). The typical chemical reaction is shown by equation 3.1, where  $CH_4$  is methane, and  $C_2H_6$  is ethane.

$$TMGa + NH3 \rightarrow GaN + CH4$$

$$TEGa + NH3 \rightarrow GaN + C2H6$$

(3.1)

TMGa, being more reactive, typically decomposes at lower temperatures compared to TEGa.  $NH_3$  is the preferred nitrogen source due to its high reactivity and ability to provide the necessary nitrogen atoms for GaN growth [69].

## 3.3 Lithography

Lithography is a process used in microfabrication to transfer a pattern onto a substrate. The pattern is defined on a mask, which is positioned in close proximity to the substrate, and light is shone through the mask to transfer the pattern onto the substrate. The substrate is then chemically treated to produce the desired pattern. Lithography is a critical step in the device manufacturing process, as it enables the creation of the microscopic features that define the performance and functionality of the resulting device. Two mainly used

lithography are optical lithography, also known as photolithography, and electron beam lithography (e-beam lithography).

## 3.3.1 Photolithography

Photolithography is a light-based lithography technique that involves projecting light through a mask (photomask) onto a light-sensitive photoresist-coated wafer. The light changes the properties of the photoresist, which is then developed to reveal the desired pattern. Photolithography is a widely used and highly scalable technology, but it has limitations in terms of the minimum feature size that can be achieved.

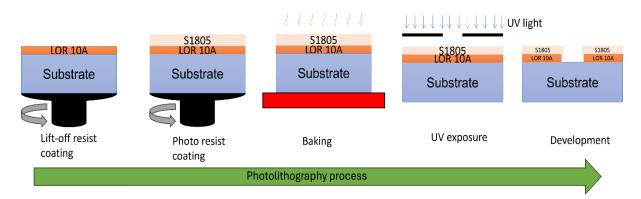

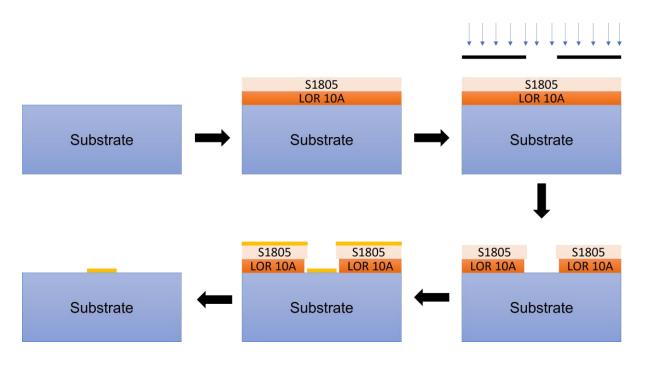

As illustrated in figure 3.2, the intricate steps of the photolithography process are showcased. In the context of this work, a bilayer photoresist system was employed to enhance the lithography results. This bilayer approach uses two distinct layers: a bottom layer known as a lift-off resist (in this case, LOR 10) and a top imaging layer (S1805). The LOR 10 serves to create an undercut profile, essential for subsequent lift-off processes, while the S1805, being sensitive to light, captures the intricate patterns from the photomask. This combination ensures improved pattern fidelity and simplifies subsequent processing steps, such as metal deposition and lift-off.

Figure 3.2 Photolithography process used in this study

## 3.3.2 Electron beam lithography

Electron beam lithography (EBL) is a highly advanced nanofabrication technique that enables patterning at the nanoscale with exceptional resolution

and alignment accuracy. Unlike optical lithography, which relies on light exposure through a mask, EBL employs a focused electron beam, typically within a scanning electron microscope (SEM), to directly write patterns onto an electron-sensitive resist. This technique offers alignment accuracy down to 0.5 nm, making it suitable for sub-micron device fabrication.

In this work, the Raith EBPG 5 system was used for all EBL processes. A bilayer resist scheme comprising PMMA 2010 (bottom) and PMMA 2041 (top) was adopted. PMMA 2010, having a lower molecular weight and higher concentration, serves as the bottom layer to provide structural support. PMMA 2041, with its higher molecular weight and lower concentration, forms the top layer and develops more readily in solvent, enabling an undercut profile favourable for lift-off processes.

In addition, a thin aluminum discharge layer (~30 nm) was deposited on top of the resist. This is crucial when performing EBL on insulating substrates or using non-conductive resists like PMMA. The aluminum layer prevents charge accumulation, which can distort the electron beam trajectory and degrade pattern fidelity. It acts as a conductive path, allowing excess charge to dissipate during exposure.

While Figure 3.2 illustrates the optical photolithography process using S1805/LOR 10A, the overall EBL process follows similar steps in terms of coating, baking, exposure, and development, with the main difference being the resist system and the inclusion of the discharge layer.

## 3.4 Etching

Etching is a critical step in the fabrication process, used to remove unwanted material and define the diode's active area. Etching techniques in semiconductor fabrication are broadly classified into wet etching, which uses chemical solutions, and dry etching, which relies on plasma-based methods. In this work, only dry etching techniques were used, specifically Reactive Ion Etching (RIE) and inductively coupled plasma (ICP). Wet etching is discussed

here for completeness and comparison. RIE and ICP are commonly used for etching the AlGaN/GaN layers with high precision. The etch depth is carefully controlled to achieve the desired mesa depth, typically around 150nm, which defines the diode's active region.

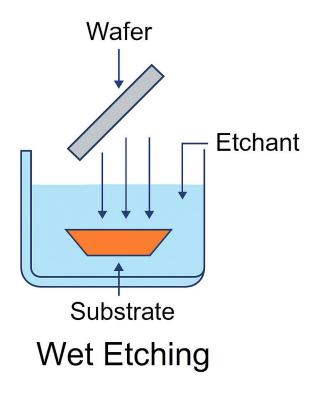

#### 3.4.1 Wet etching

Wet etching is a fundamental and widely used technique in the field of semiconductor processing and microfabrication. It plays a crucial role in defining precise patterns and structures on semiconductor substrates, allowing for the creation of intricate and complex devices. Wet etching involves the selective removal of material from a substrate using chemical solutions, known as etchants, to achieve the desired pattern or structure. A schematic illustration of the wet etching process is shown in Figure 3.3.

Figure 3.3 Wet Etching

One of the significant advantages of wet etching is its ability to produce smooth and isotropic etch profiles, particularly in comparison to dry etching techniques such as RIE. This capability is crucial in applications where a uniform and defect-free surface is required, such as in the fabrication of microelectronic devices or microfluidic systems.

Despite its advantages, wet etching does have limitations. It is less suitable for creating sub-micron features and structures with high aspect ratios, as it tends to cause under-etching or lateral material removal. Additionally, wet etching may introduce some surface contamination and produce relatively lower resolution patterns compared to more advanced lithographic techniques.

GaN is a material characterized by its high hardness and chemical stability, which results in a relatively low etching rate and limited etching selectivity during the wet etching process. Various aqueous acid and base solutions were tested for etching of GaN in [70], while no wet etch solutions appreciably etched GaN films. [71] reported that GaN can be etched in sodium hydroxide (NaOH) solution. However, the etching ceased due to the formation of gallium hydroxide  $(Ga(OH)_3)$ .

#### 3.4.2 Dry etching

Dry etching, also known as plasma etching or dry plasma etching, is a vital and widely used semiconductor processing technique for microfabrication and nanofabrication. Unlike wet etching, which uses chemical solutions to selectively remove material from a substrate, dry etching employs plasma, a high-energy ionized gas, to etch materials with exceptional precision and control.

One of the primary advantages of dry etching is its anisotropic etch characteristics. Unlike wet etching, which tends to cause isotropic material removal, dry etching produces well-defined and vertical etch profiles, allowing for the creation of high-aspect-ratio structures and precise patterning. This anisotropic etching capability is crucial for producing sub-micron features and nanoscale structures.

Furthermore, dry etching enables better control over the etching process, offering higher selectivity, uniformity, and repeatability compared to wet etching. The use of reactive gases allows for the customization of etching rates and etch

profiles, making it possible to etch multiple materials selectively and with high accuracy. This level of control is essential in the fabrication of complex integrated circuits and advanced microelectronic devices.

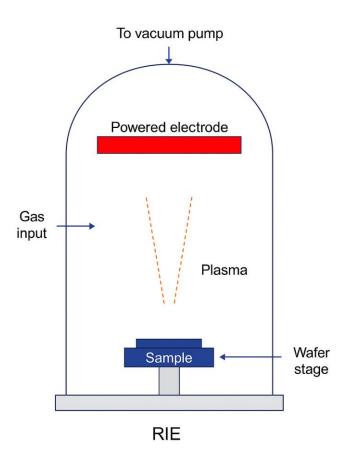

RIE is a dry etching process that employs chemically reactive plasma to remove material deposited on substrates. The plasma is generated by introducing a mixture of gases into a low-pressure chamber and applying a RF power to create a glow discharge. This discharge dissociates the gas molecules into ions, radicals, and other excited species.

Figure 3.4 RIE dry etching

The fundamental mechanism of RIE involves both physical and chemical etching. Physically, the ions are accelerated by the electric field towards the substrate, where they physically bombard the surface, causing a sputtering

effect. Chemically, the reactive species in the plasma can react with the surface material.

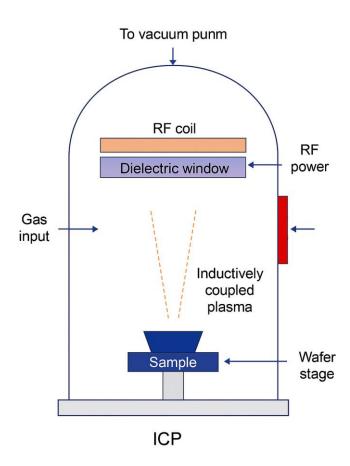

Another commonly used dry etching method is ICP, which is a technology that generates plasma by using an inductively coupled electromagnetic field.

Figure 3.5 ICP dry etching

ICP is known for its high etch rates and the ability to control the directionality of the etch, which is critical for anisotropic profile transfer. The low ion energy also minimizes the physical damage to the substrate, which is particularly advantageous when processing delicate structures.

## 3.5 Ohmic and schottky metal deposition

Metallization is a crucial step in the fabrication process as it forms the contact to the AlGaN/GaN heterostructure. Metal deposition onto semiconductor wafers or samples can be carried out in several different ways including thermal evaporation, electron beam evaporation and sputtering.

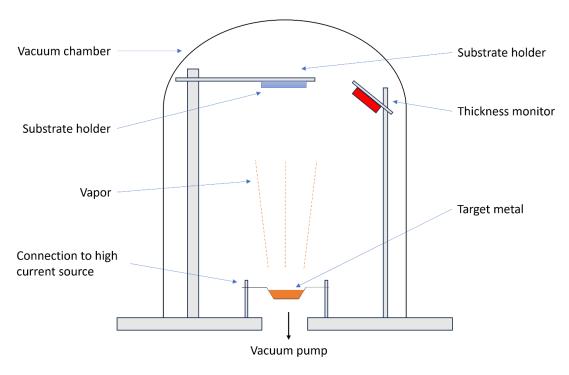

## 3.5.1 Thermal evaporation

Thermal evaporation is one of the fundamental techniques employed in the deposition of metallic thin films. The core principle of this method revolves around heating the metal in a high-vacuum environment. Upon reaching its evaporation point, the material transforms into a vapor, which subsequently condenses onto a cooler substrate, resulting in a thin film. One of the primary advantages of this technique is its straightforwardness, coupled with the ability to achieve high-purity films. However, thermal vaporization faces challenges when dealing with materials that possess exceedingly high melting points, as the required temperatures might be difficult to attain. Additionally, achieving a uniform thickness, especially over expansive areas, can be problematic. Figure 3.6 shows the thermal evaporation system.

Figure 3.6 Thermal evaporation system

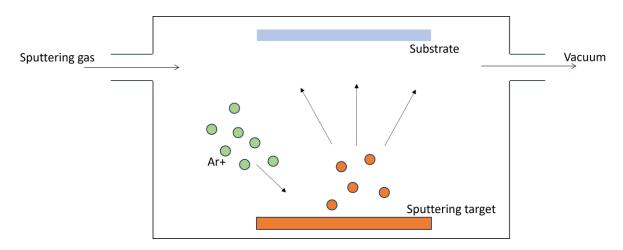

#### 3.5.2 Sputtering

Sputtering stands out as a distinct metal deposition method due to its reliance on ionized gas, primarily argon, to instigate the deposition process. The gas ions, when directed at a target material, result in atomic ejections from the target. These atoms subsequently form a thin film upon encountering a substrate. Sputtering's versatility is evident in its ability to cater to a diverse range of materials, offering excellent step coverage, which makes it exceptionally suitable for substrates with intricate topographies. Moreover, the films generated through sputtering often exhibit commendable adhesion properties to the substrate. However, the deposition rates in sputtering are characteristically slower in comparison to the evaporation techniques. The sputtering process is shown in figure 3.7.

Figure 3.7 Sputtering

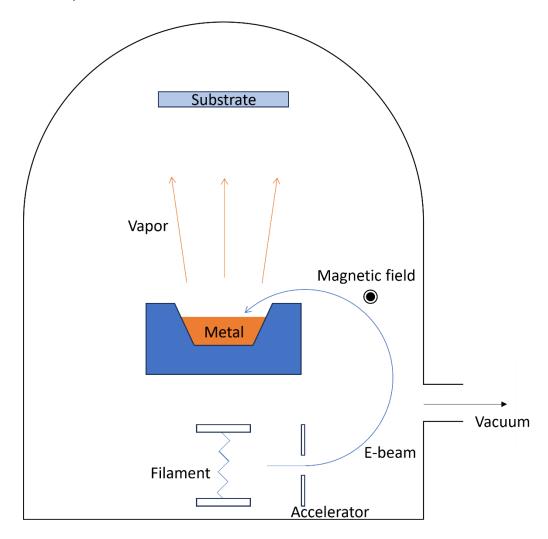

## 3.5.3 E-beam evaporation

A more sophisticated technique, e-beam vaporization, employs an electron beam (e-beam) directed onto the material intended for deposition. The kinetic energy from the electrons results in the heating and eventual evaporation of the target material. This vapor then follows a trajectory similar to thermal vaporization, condensing onto a substrate to form a film. Electron beam evaporation offers a distinct advantage in its ability to evaporate materials that are otherwise resistant to thermal evaporation due to their high melting points. This method also provides enhanced control over deposition rates and is

capable of producing films of superior quality and density. Figure 3.8 shows the e-beam evaporation.

Figure 3.8 E-beam evaporation

For ohmic contacts, a metal stack of Ti(30nm)/Al(180nm)/Ni(40nm)/Au(100nm) is deposited onto the etched surface. The choice of this metal stack is based on its work function and compatibility with the AlGaN/GaN material, enabling low-resistance ohmic contacts.

For Schottky contacts, a metal stack of Ni(20nm)/Au(200nm) is deposited onto the mesa surface. The Schottky metal stack is carefully chosen to achieve the desired Schottky barrier height, a critical parameter in diode performance.

#### 3.5.1 Lift-off technique

The lift-off process is a crucial step in the fabrication of AlGaN/GaN Schottky diodes, enabling precise metal definition without damaging the underlying epilayers. A bilayer resist structure composed of LOR 10A and S1805 was used to facilitate an undercut profile for successful liftoff. During development, the exposed S1805 layer is removed, along with the underlying LOR 10A. Due to the differential solubility and bake conditions, a natural undercut is formed at the interface, which is essential to prevent metal fence formation during liftoff. The metal stack (Ti/Al/Ni/Au for ohmic contacts and Ni/Au for Schottky contacts) is then deposited over the entire wafer, covering both the patterned S1805 and surrounding LOR10. The crucial step is the lift-off process, where the wafer is immersed in a solvent that dissolves the LOR10 layer, causing the overlying metal to lift off and detach from the substrate. This results in the desired metal pattern, precisely defined on top of the S1805 resist, facilitating the fabrication of well-defined metal contacts and interconnections for high-performance electronic devices. This process is illustrated in figure 3.9.

Figure 3.9 Lift-off process

#### 3.6 Annealing

Following metallization, a rapid thermal annealing process is performed to improve the metal-semiconductor interface and reduce contact resistance. The annealing in this work is conducted at a temperature of 830°C for 30 seconds, ensuring the formation of stable and low-resistance contacts.

## 3.7 Marker metal deposition

In this work, Ti/Pt metal stacks were deposited on the wafer surface as alignment markers to assist in precise alignment during subsequent lithography steps. These markers are essential for multi-step processes such as mesa etching, ohmic metal, and Schottky gate patterning.

Titanium was chosen due to its strong adhesion to GaN, high thermal stability, and low diffusivity, making it ideal for use in high-temperature processes. Platinum, layered above Ti, enhances visibility under optical and SEM inspection. In contrast, alternative metals such as Au are prone to diffusion and contamination during annealing, while Al has a low melting point and poor resistance to standard etchants.

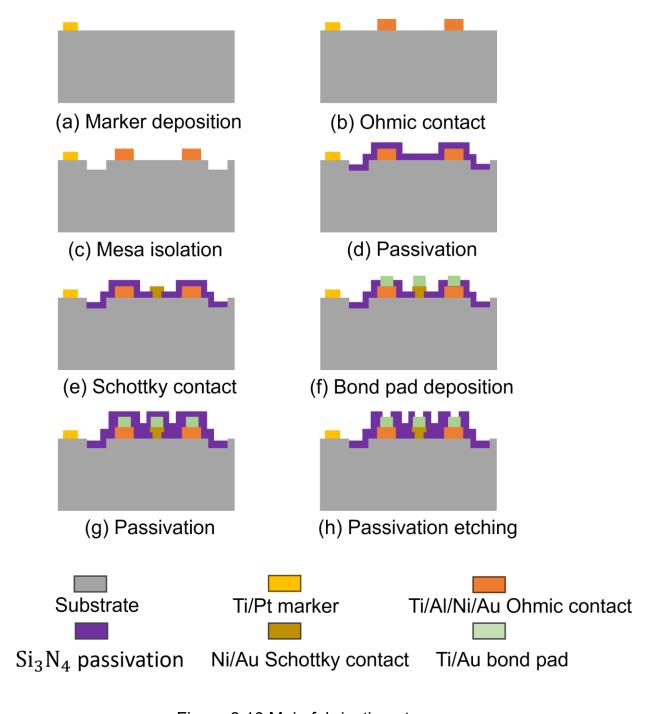

#### 3.8 Diode fabrication flow

The complete device fabrication process is illustrated in Figure 3.5, showing the step-by-step integration of alignment marks, ohmic contacts, mesa isolation, and Schottky gate metallisation.

The process began with the deposition of alignment markers (Ti/Pt) using photolithography and liftoff. Next, the ohmic contact metal stack Ti (30 nm) / Al (180 nm) / Ni (40 nm) / Au (100 nm) was deposited and patterned to form the cathode contacts, followed by rapid thermal annealing.

After ohmic contact formation, a mesa isolation etch was performed using RIE, defining the device active area. A passivation layer of SiN was then

deposited to reduce surface states and leakage current. Via holes were opened in the SiN using photolithography and dry etching.

Finally, a Schottky contact (Ni/Au) was deposited over the AlGaN surface, completing the diode structure. The schematic steps of this process are shown in Figure 3.10.

Figure 3.10 Main fabrication steps

#### 3.9 Device characterization

After the completion of the fabrication process, the AlGaN/GaN Schottky diodes undergo thorough device characterization to evaluate their electrical and RF performance. Device characterization is a critical step in the development of electronic devices as it provides valuable insights into the device's behaviour and functionality under different operating conditions.

## 3.9.1 DC Current-Voltage (I-V) Measurements

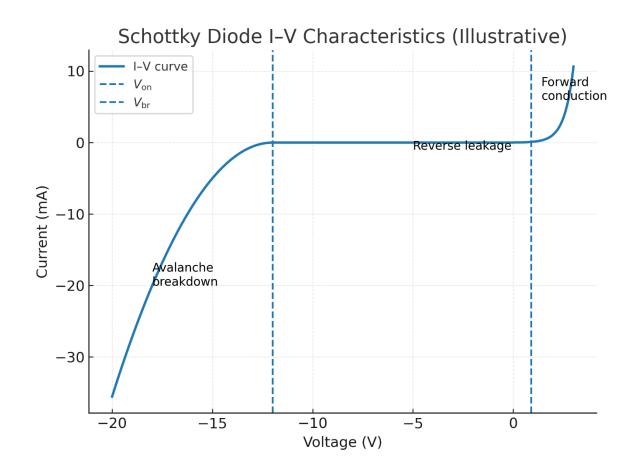

One of the primary electrical characterizations performed on the fabricated Schottky diodes is the current-voltage (I-V) measurement. I-V measurements are conducted to understand the diode's electrical behaviour and to determine key parameters such as the ideality factor, Schottky barrier height, series resistance, and reverse breakdown voltage.

I-V measurements are typically carried out using a semiconductor parameter analyzer. During the measurement, a bias voltage is applied across the Schottky diode, and the resulting current is recorded. The process is repeated for different bias voltages to establish the current-voltage characteristic curve.

From the I–V curve, the ideality factor (n) can be extracted, which provides insight into the nature of carrier transport mechanisms across the Schottky diode interface. The ideality factor is also related to the effective barrier height of the device.

Figure 3.11 depicts the I-V curve of the diode. A diode primarily conducts when a forward bias is applied. This conduction starts appreciably at a voltage termed the 'forward voltage' ( $V_{on}$ ). When reverse biased, an ideal diode would exhibit no current flow. However, in practical diodes, a small reverse saturation current does exist due to minority carriers. As the magnitude of the reverse bias increases, this current remains nearly constant until reaching a point called the 'breakdown voltage' ( $V_{br}$ ), Beyond this voltage, the diode enters a breakdown region where the reverse current rises sharply. Depending on the nature and

design of the diode, this breakdown might be destructive or a utilized characteristic.

Figure 3.11 Diode I-V curve

#### 3.9.2 RF characterization

RF characterization of the AlGaN/GaN Schottky diodes is essential to assess their performance in high-frequency applications. RF measurements are conducted to determine key parameters such as the S-parameters, cut-off frequency.

S-parameters are crucial for characterizing the diode's RF behaviour, as they describe the relationship between incident and reflected RF waves at the diode's terminals. S-parameters provide information about the diode's transmission, reflection, and scattering characteristics, enabling the design and optimization of RF circuits and systems.

In this work, RF measurements were performed using a Keysight Performance Network Analyzer (PNA) N5227A, covering a frequency range from 100 MHz to 50 GHz. A Short-Open-Load-Thru (SOLT) calibration was carried out at the probe tips. The main purpose of this calibration is to remove the effects of the measurement infrastructure—including cables, probe arms, and connectors—by shifting the reference planes directly to the device terminals. This ensures that the extracted S-parameters accurately represent the intrinsic response of the device under test (DUT).

Figure 3.12 shows the actual calibration standards (Short, Open, Load, and Thru) used in this work, captured under an optical microscope. These standards are patterned on a commercial GSG calibration substrate with a 150 µm pitch, matching the RF probe pitch for minimal mismatch. This ensures high confidence in the accuracy and repeatability of S-parameter extraction across the 100 MHz–50 GHz frequency range.

Figure 3.12 Optical microscope images of the SOLT (Short, Open, Load, Thru) calibration standards used for RF on-wafer calibration

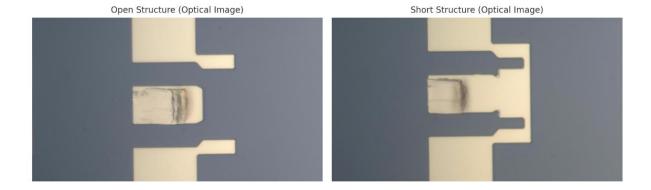

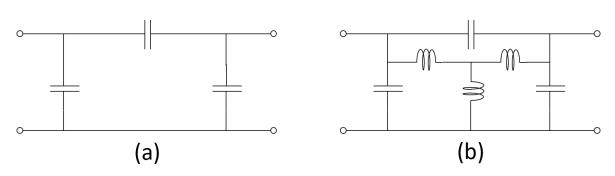

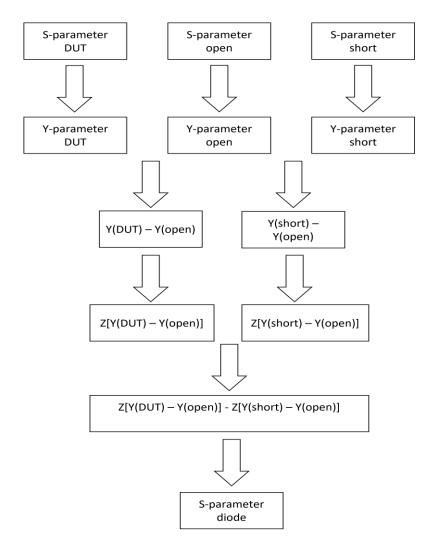

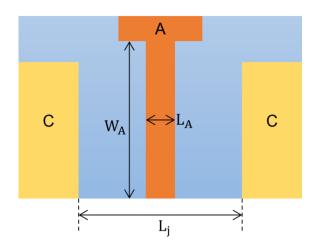

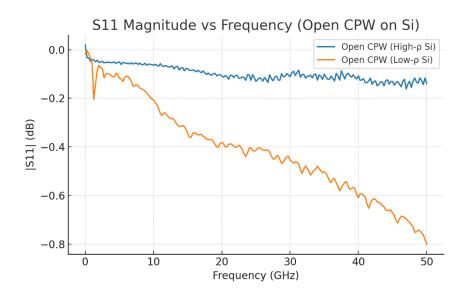

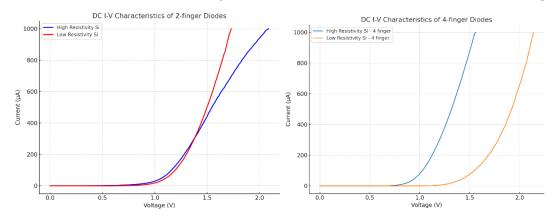

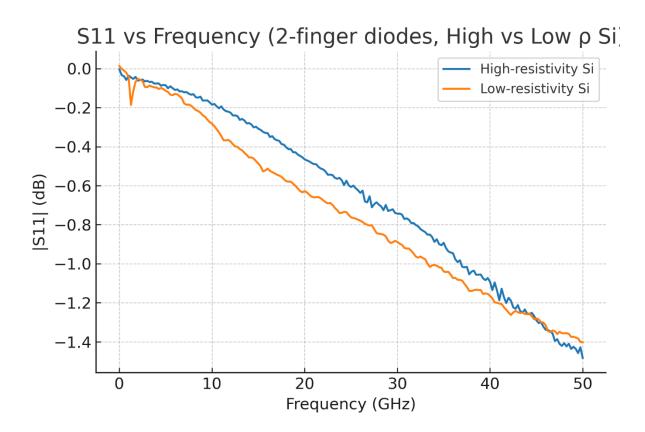

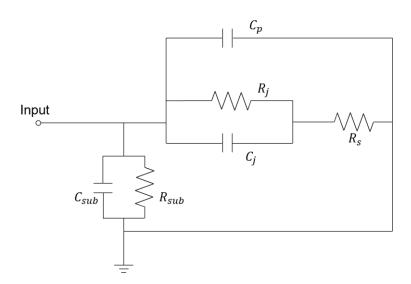

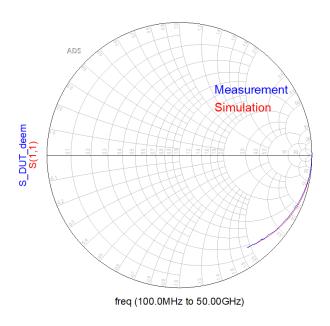

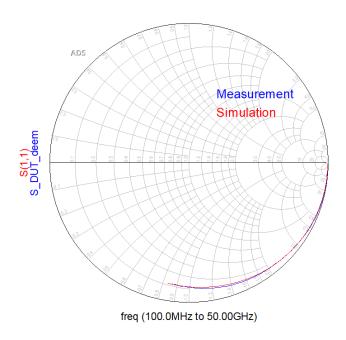

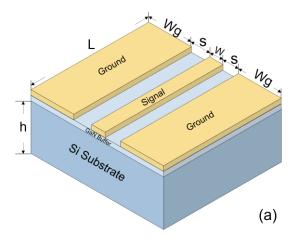

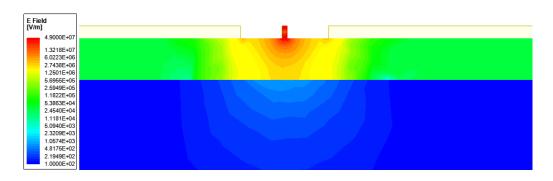

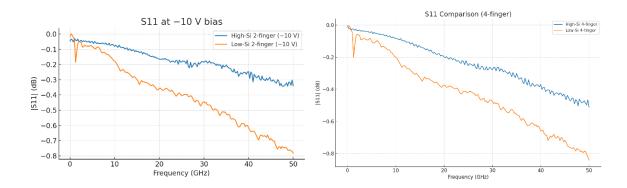

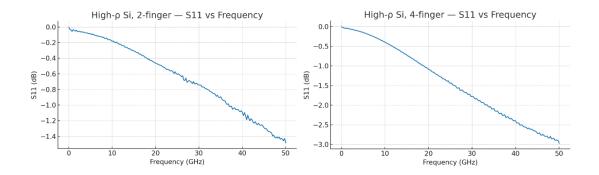

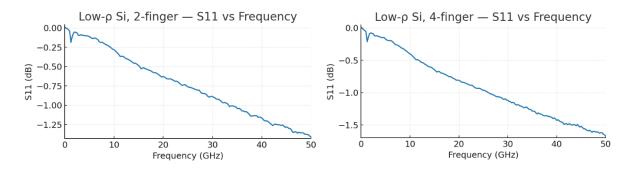

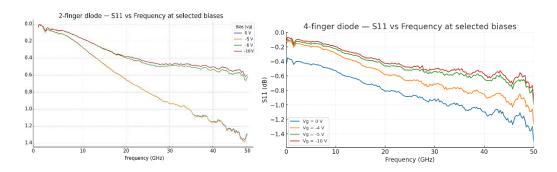

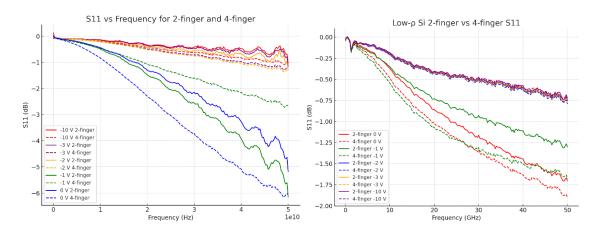

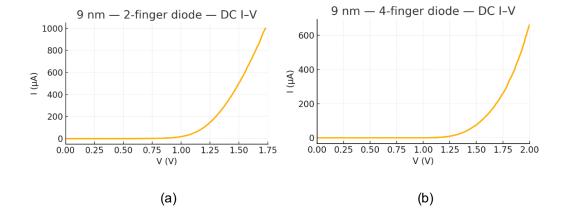

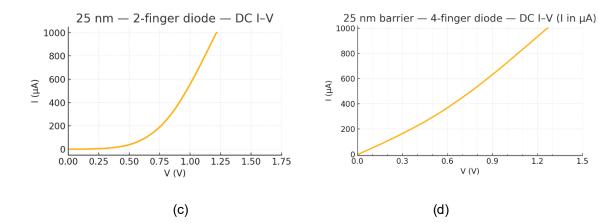

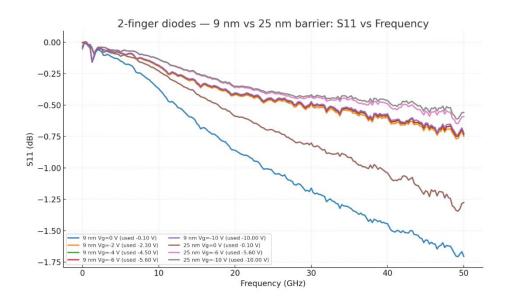

Representative optical micrographs of the fabricated **2-finger** and **4-finger** SBDs are shown in figure 3.13, highlighting the Schottky anode finger array, ohmic cathode pad and CPW pad geometry used for on-wafer S-parameter measurements (100 MHz–50 GHz).