This is an Open Access document downloaded from ORCA, Cardiff University's institutional repository:<https://orca.cardiff.ac.uk/id/eprint/183300/>

This is the author's version of a work that was submitted to / accepted for publication.

Citation for final published version:

Shi, Charley, Lo, Suzanne, Thrimawithana, Duleepa J., Adams, Francesca, Wadsworth, Aaron, Pearce, Matthew G.S., Oliver, Rachel A., Wallis, David J. and Badcock, Rodney A. 2024. A circuit for evaluating GaN HEMT dynamic Rds(on) at cryogenic temperatures. Presented at: 9th Southern Power Electronics Conference (SPEC), Brisbane, Australia, 2-5 December 2024. Proceedings of 9th Southern Power Electronics Conference. IEEE, pp. 1-6. 10.1109/spec62217.2024.10893110

Publishers page: <https://doi.org/10.1109/spec62217.2024.10893110>

Please note:

Changes made as a result of publishing processes such as copy-editing, formatting and page numbers may not be reflected in this version. For the definitive version of this publication, please refer to the published source. You are advised to consult the publisher's version if you wish to cite this paper.

This version is being made available in accordance with publisher policies. See <http://orca.cf.ac.uk/policies.html> for usage policies. Copyright and moral rights for publications made available in ORCA are retained by the copyright holders.

# A Circuit for Evaluating GaN HEMT Dynamic $R_{ds(on)}$ at Cryogenic Temperatures

Charley Shi\*, Suzanne Lo\*, Duleepa J. Thrimawithana\*, Francesca Adams†,

Aaron Wadsworth\*, Matthew G.S. Pearce\*, Rachel A. Oliver†, David J. Wallis†‡, Rodney A. Badcock§

\*Department of Electrical, Computer, and Software Engineering, The University of Auckland, New Zealand

†Department of Materials Science and Metallurgy, University of Cambridge, United Kingdom

‡Department of Engineering, Cardiff University, United Kingdom

§Robinson Research Institute, Victoria University of Wellington, New Zealand

**Abstract**—GaN HEMTs are promising power switching devices for cryogenic power converters in superconducting motor drives and space applications. However, GaN HEMTs experience dynamic on-resistance  $R_{ds(on)}$  which is not well understood at cryogenic temperatures (CT). This paper presents a circuit for evaluating the dynamic  $R_{ds(on)}$  of GaN HEMTs at CT by using on-the-fly measurements to capture off-state trapping transients. The evaluation circuit utilises a measurement circuit with a blocking switch to accurately measure the  $V_{ds}$ . Due to the much lower  $R_{ds(on)}$  at CT than room temperature (RT), an amplifier was implemented to amplify the output of the measurement circuit, for which the performance is validated using a coaxial shunt resistor. Results demonstrate that the circuit can successfully measure the dynamic  $R_{ds(on)}$  2  $\mu$ s after the device turns on at both RT and 77 K.

## I. INTRODUCTION

Cryogenic power conversion has applications requiring high power density and efficiency such as superconducting motor drives [1–4] and deep space exploration [5]. In particular, superconducting motor drives are crucial for enabling electric aircraft [1, 6] which are a key part of reducing greenhouse gas emissions [7]. When designing any power converter, the selection of the power switch is of paramount importance in which switching speed and on-resistance  $R_{ds(on)}$  are the primary performance metrics. Fast switching enables higher switching frequencies which reduce capacitor and inductor size, while low  $R_{ds(on)}$  reduces conduction losses which in turn reduce heat sinking requirements. Thus, both fast switching and low  $R_{ds(on)}$  serve to boost power density and reduce volume and mass [8–10]. In this respect, GaN HEMTs perform excellently in cryogenic conditions [11–16] and thus have been used in cryogenic power converter designs to date [17, 18].

However, due to material defects, GaN HEMTs suffer from charges trapping effects which degrade  $R_{ds(on)}$  [19, 20]. This causes dynamic (time-varying)  $R_{ds(on)}$  due to charge trapping phenomena, where the actual  $R_{ds(on)}$  is generally greater than the static  $R_{ds(on)}$ . As dynamic  $R_{ds(on)}$  effects dominate the conduction losses in most applications, the static  $R_{ds(on)}$  may severely underestimate the conduction losses and device heating [21, 22]. Thus, characterisation of dynamic  $R_{ds(on)}$  is vital so that conduction losses can be accurately calculated and device temperature can be appropriately managed. Note that though some commercial GaN devices exhibit negligible dy-

namic  $R_{ds(on)}$  effects at room temperature (RT) [23], concerns have been raised regarding the feasibility of driving them at cryogenic temperatures [11].

To this date, static  $R_{ds(on)}$  has been extensively characterised at cryogenic temperature (CT) [24]. However, the dynamic  $R_{ds(on)}$  has not. An attempt was made by Wei *et al.* [15], but the authors only managed to obtain results down to 143 K. Additionally, dynamic  $R_{ds(on)}$  was characterised down to 77 K in [25], but the authors tested a depletion-mode device which is suboptimal for power electronics applications [26]. No other work on dynamic  $R_{ds(on)}$  at CT, to the best of the authors' knowledge, has been done to this date. Thus, this paper presents a dynamic  $R_{ds(on)}$  characterisation method suitable for CT measurements, as a first step to acquiring dynamic  $R_{ds(on)}$  data at CT.

In Section II, a measurement scheme is developed to characterise the trapping kinetics, a key step to modelling and simulating dynamic  $R_{ds(on)}$  in power converters. Based on the measurement scheme, a dynamic  $R_{ds(on)}$  evaluation circuit suitable for CT measurements is proposed in Section III, entailing a comparison of measurement circuits used in literature. The hardware implementation of the evaluation circuit is presented and validated in Section IV. To conclude, key achievements and future work are highlighted.

## II. MEASUREMENT SCHEME

Off-state charge trapping occurs due to voltage stress (mainly from high  $V_{ds}$ ) when the GaN HEMT is off [27, 28], and is one of the primary causes of dynamic  $R_{ds(on)}$  effects in power converters. When the GaN HEMT is on, trapped charges are released (detrapped). Dynamic  $R_{ds(on)}$  due to off-state trapping is commonly evaluated by measuring the drain current transient (DCT) [19, 29], or equivalently the  $R_{ds(on)}$  transients [30, 31]. Subsequently, a mathematical model of the dynamic  $R_{ds(on)}$  can be formulated by curve fitting to a sum of decaying exponentials of different amplitudes and time constants [29]. Using the models, they can be simulated for a power converter in circuit simulation software such as LTSpice, after which the models can be validated in practice using power converters [32, 33]. The method of measuring the transients is detailed as follows.

First consider the detrapping transient. Some authors have characterised the detrapping transient by having the device under test (DUT) biased in the OFF state with  $V_{gs} = V_{ds} = 0$  [30, 31]. However, in a practical application, the detrapping occurs when the device is on so only the on-state detrapping transient is meaningful in power converters. Thus, detrapping transients should be characterised with the DUT on. Moreover, the DUT being on simplifies the measurement of the detrapping transient as the DUT is always on so the  $R_{ds(on)}$  can be readily measured.

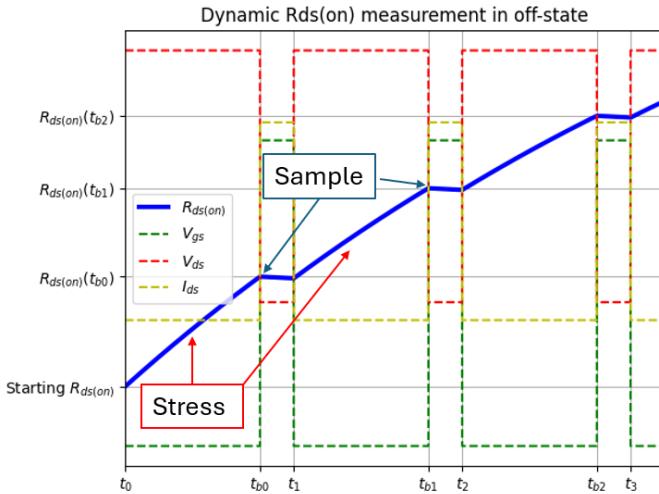

However, capturing the off-state trapping transient is trickier because the DUT is not in the on state so the  $R_{ds(on)}$  cannot be readily measured. A solution is to execute on-the-fly measurements [19, 27, 30, 31] [Fig. 1], whereby the DUT is periodically pulsed to sample the  $R_{ds(on)}$ . It is vital to sample the  $R_{ds(on)}$  as soon after the DUT is turned on as possible because detrapping commences immediately after the turn-on so sampling delays will cause error. Furthermore, sampling as soon as possible allows the pulse to be shortened so that significant detrapping does not occur during the pulse and interfere with the trapping transient. Examples of pulse widths used in literature are 5  $\mu$ s [31], 10  $\mu$ s [30] and 50 ms [27].

Fig. 1: Theoretical  $R_{ds(on)}$  waveform when using on-the-fly measurements to capture the off-state trapping transient.  $V_{gs}$ ,  $V_{ds}$  and  $I_{ds}$  are plotted in dashed lines to indicate the shape of those waveforms and the switching scheme of the GaN HEMT.

Hot electron trapping is another trapping phenomena which occurs when there is simultaneously high  $V_{ds}$  and high  $I_{ds}$  across the device. The practical scenario in which this occurs is the high power switching transitions when hard switching [20, 21, 28, 34]. Thus, the off-state trapping analyses above are insufficient for modelling and simulating dynamic  $R_{ds(on)}$  in a hard switching power converter, and are limited to soft switching. Due to the complexity of hot electron trapping characterisation and modelling [35, 36], it is out of the scope of this paper. Moreover, the DUT must be soft switched in the off-state trapping measurements to prevent unintended

introduction of hot electron traps that would alter the  $R_{ds(on)}$  and cause measurement error [31].

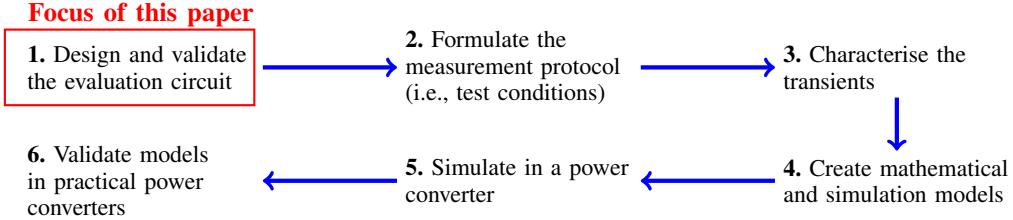

The process of characterising and modelling the dynamic  $R_{ds(on)}$  pertaining to power converters is outlined in Fig. 2. Steps 3 to 6 summarize the procedure described at the beginning of this section, those steps being preceded by the determination of all test conditions to evaluate dynamic  $R_{ds(on)}$  under. These test conditions encompass a wide range of stress voltages and temperatures which allow a comprehensive voltage and temperature dependent model to be formulated in Step 4. Considering the entire process in Fig. 2, designing and validating the experimental setup is the first step, on which the remainder of this paper will focus.

### III. EVALUATION CIRCUIT

A dynamic  $R_{ds(on)}$  evaluation circuit has been designed based on the requirements of the measurement scheme in Section II. These requirements are that the circuit must

- be able to stress the device under test (DUT) with high voltage  $V_{stress}$  in the off state, where  $V_{stress}$  should be able to vary over a large range (e.g., 50-400 V) to characterise the potentially significant variation in dynamic  $R_{ds(on)}$  with stress voltage [31, 37].

- in the on-state, pump a known drain current  $I_{ds(on)}$  through the DUT and sense the on-state drain-source voltage  $V_{ds(on)}$  so that  $R_{ds(on)} = \frac{V_{ds(on)}}{I_{ds(on)}}$  can be calculated.

- be able to keep the DUT on for long time to characterize long-term detrapping transients, and off for a long time during long stress intervals for off-state trapping characterisation. This 'long time' is on the order of seconds because the duration of the transients is typically tens to hundreds of seconds [27, 30, 31].

The dynamic  $R_{ds(on)}$  evaluation circuit has two parts:

- 1) **Test circuit:** Stresses the DUT with high  $V_{ds}$  when the DUT is off and supplies constant current  $I_{ds(on)}$  when the DUT is on.

- 2) **Measurement circuit:** Outputs a voltage from which  $V_{ds(on)}$  and thereby  $R_{ds(on)}$  can be recovered.

#### A. Test circuit

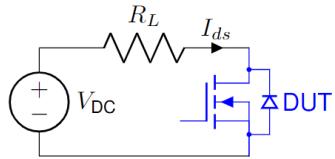

The proposed measurement scheme is essentially a pulsed I-V measurement method [19] for which resistive loads are typically used [22, 38]. A basic version of the test circuit with a resistive load is shown in Fig. 3. Though double pulse testing (DPT) circuits are also commonly used for dynamic  $R_{ds(on)}$  pulsed characterisations [38-41], they cannot measure the long on-state detrapping transient due to the inductor. This is because  $I_{ds(on)}$  will change over time and become a confounding variable that influences the dynamic  $R_{ds(on)}$  by hot electron trapping [28]. Furthermore, if the DUT is on for a long time, the current in the DPT inductor will increase until the inductor saturates, resulting in very large  $I_{ds(on)}$  that will cause significant self-heating of the DUT. Other circuit topologies used in literature also contain inductors [38] and are thus not suitable for characterising detrapping transients; however, they are useful for measuring dynamic  $R_{ds(on)}$  in high

Fig. 2: Procedure of characterising and modelling the dynamic  $R_{ds(on)}$  of GaN HEMTs in power converters.

frequency switching to validate the models obtained from the measurement scheme. Moreover, the presence of an inductor inherently adds complexity to the design and assembly of the test circuit. Thus, the resistive load is the chosen solution for implementing the proposed measurement scheme because it enables detrapping for long periods of time with constant  $I_{ds(on)}$  and is also the simplest.

However, Fig. 3 has two key disadvantages. Firstly, the power dissipation in  $R_L$  will be unmanageable at high voltage (e.g. 500V) when the DUT is on for a long time unless a very large  $R_L$  is used, but a very large  $R_L$  will cause  $I_{ds(on)}$  to be very low and thereby make the  $R_{ds(on)}$  difficult to accurately measure. Secondly,  $I_{ds(on)} \approx \frac{V_{DC}}{R_L}$  so as  $V_{DC}$  is varied to change the stress voltage,  $I_{ds(on)}$  will change; this is undesired because  $I_{ds(on)}$  may influence the  $R_{ds(on)}$  and hence become a confounding variable [21]. Therefore, the circuit in Fig. 3 is not suitable.

Fig. 3: Basic test circuit with resistive load  $R_L$  for pulsed I-V characterisations [38]

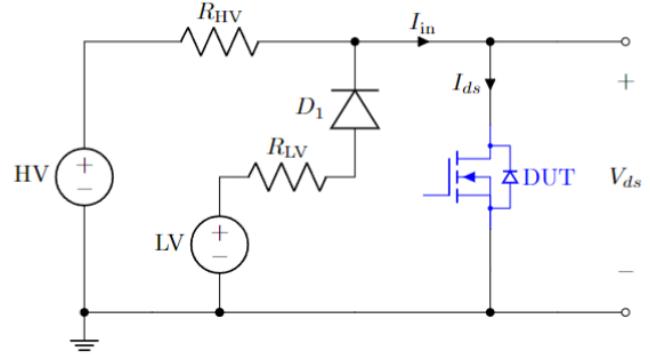

To address the disadvantages of Fig. 3, the test circuit in Fig. 4 is proposed, where the stress voltage and  $I_{ds(on)}$  are independent. Here, the high voltage source (HV) controls the stress voltage.  $R_{HV}$  is a large resistance (100s of k $\Omega$ ) which couples HV to the drain during the off state to stress the DUT.  $R_{LV}$  is a resistive load (few  $\Omega$ ) which, in conjunction with the low voltage source (LV), sets  $I_{ds(on)}$ .  $D_1$  is a high voltage diode which prevents the drain from being pulled down near LV during the off state.

#### B. Measurement circuit

Measuring  $I_{ds(on)}$  is straightforward because with the proposed test circuit,  $I_{ds(on)}$  is DC and can be measured with a multimeter while the DUT is held on. However, measuring  $V_{ds(on)}$  is difficult because the high off-state  $V_{ds}$  must be blocked to protect downstream circuitry and prevent the oscilloscope from saturating and being damaged [46, 56]. Moreover, the measurement circuit must not only accurately measure the low on-state  $V_{ds}$  but also respond as quickly as

Fig. 4: Dynamic  $R_{ds(on)}$  test circuit with independent control of stress voltage and  $I_{ds(on)}$

possible to the DUT turn-on so that the  $R_{ds(on)}$  can be sampled as soon after the turn-on as possible.

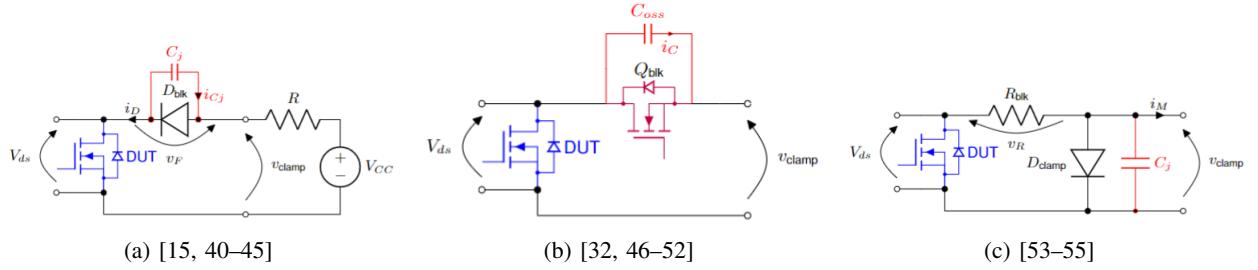

In literature, three types of dynamic  $R_{ds(on)}$  measurement circuits have been used [Fig. 5].  $v_{clamp}$  is the output of the measurement circuit which corresponds to  $V_{ds(on)}$ . Though the literature surveyed usually includes additional components (e.g. Zener diodes [15, 40]) which vary between authors, those additional components do not change the essence of how the measurement circuit functions. Measurement circuits using a blocking diode [Fig. 5a] are simple, but require calibration for the I-V characteristics of the diode at the specific operating temperature due to the forward voltage drop [15, 40, 42, 44, 45]. This may introduce error due to temperature variation [24] and fast transients during measurement [51], and the errors are exacerbated when measuring the much lower  $R_{ds(on)}$  at CT.

The clamping diode measurement circuit [Fig. 5c] is a solution to the forward voltage drop issue. However, it is still not suitable because when the DUT is off ( $V_{ds} = V_{stress}$ ), the instantaneous power in  $R_{blk}$  is approximately  $P = \frac{V_{stress}^2}{R_{blk}}$  which results in very high power dissipation at high stress voltages. For example, if  $V_{stress} = 500$  V and  $R_{blk} = 100$  k $\Omega$ ,  $P = 2.5$  W, a power dissipation that becomes significant when the DUT is off for a large portion of the time as in off-state transient measurements. This demonstrates the necessity of using a large  $R_{blk}$  in this circuit, but such a large resistance forms a long  $RC$  time constant with the diode capacitance  $C_j$  which slows the measurement circuit down [43, 52] and increases the error due to current  $i_M$  flowing into the measurement device (e.g. oscilloscope) which

Fig. 5: Measurement circuits used in literature: (a) Blocking diode, (b) blocking switch and (c) clamping diode. Parasitic capacitances are drawn in red.

has finite input impedance. Though a resistor can be placed in parallel with  $D_{\text{clamp}}$  to reduce the  $RC$  time constant and impact of  $i_M$ , it divides down the measured voltage and reduces the measurement accuracy. Therefore, the blocking switch measurement circuit [Fig. 5b] is preferred because there is negligible voltage drop between the DUT and  $v_{\text{clamp}}$ , there are no large  $RC$  time constants slowing it down, and there is low power dissipation [51, 52].

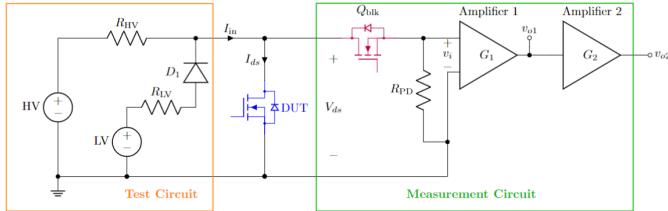

### C. Complete circuit

Fig. 6: Schematic of the complete dynamic  $R_{\text{ds}(\text{on})}$  evaluation circuit

The complete evaluation circuit is shown in Fig. 6.  $Q_{\text{blk}}$  is switched synchronously with the DUT so that the high off-state  $V_{\text{ds}}$  is blocked while the on-state  $V_{\text{ds}}$  is passed to  $v_i$  (i.e.,  $v_{\text{clamp}}$  in Fig. 5b). Due to the significantly lower  $R_{\text{ds}(\text{on})}$  of GaN HEMTs at CT [11, 15, 24], an amplifier is used to amplify  $v_i$  to a level which the oscilloscope can accurately measure. Though a high  $I_{\text{ds}(\text{on})}$  could theoretically be chosen to achieve a larger  $v_i$  which is accurately measurable without an amplifier, such high currents will cause significant self-heating of the DUT,  $R_{\text{LV}}$ , and  $D_1$  during detrapping transients which causes inaccurate DUT temperature and drifts in  $I_{\text{ds}(\text{on})}$ . When testing low  $R_{\text{ds}(\text{on})}$  devices with low  $I_{\text{ds}(\text{on})}$  (e.g., 1A),  $V_{\text{ds}(\text{on})}$  is quite small even at RT, so  $v_{o1} = G_1 v_i$  is used to measure  $R_{\text{ds}(\text{on})}$  at RT and  $v_{o2} = G_1 G_2 v_i$  is used to measure the much lower  $R_{\text{ds}(\text{on})}$  at CT.  $R_{\text{PD}}$  ensures that the amplifier input is not floating when  $Q_{\text{blk}}$  is off and enables the DUT's soft switching. For this purpose,  $R_{\text{ds}(\text{on}), \text{Qblk}} \ll R_{\text{PD}} \ll R_{\text{HV}}$  where  $R_{\text{ds}(\text{on}), \text{Qblk}}$  is the on-resistance of  $Q_{\text{blk}}$ , so that approximate ZVS can be achieved while not significantly dividing down the measured  $V_{\text{ds}}$ ; a value in the 10s or 100s of  $\Omega$  is thus suitable. An extra function of  $R_{\text{PD}}$  is to act as a low impedance path to

ground for the  $C_{\text{oss}}$  current of  $Q_{\text{blk}}$  during switching instants, suppressing voltage spikes on  $v_i$ .

In our implementation,  $Q_{\text{blk}}$  is driven by an isolated gate drive and not with automatic switching as done by several authors [32, 46, 47, 50, 57]. This is because in the evaluation circuit, HV is coupled to the drain via large resistance  $R_{\text{HV}}$  so  $Q_{\text{blk}}$  would clamp the drain to a low voltage, preventing the DUT from being stressed, if it was automatically switched. Moreover, this permits soft switching which is required for the measurement scheme, whereby  $Q_{\text{blk}}$  is turned on slightly prior to the DUT to pull  $V_{\text{ds}}$  low and approximately achieve zero-voltage switching (ZVS); only hard switching is possible with automatic switching. With the isolated gate drive, hard switching can still be achieved by turning  $Q_{\text{blk}}$  on slightly after the DUT.

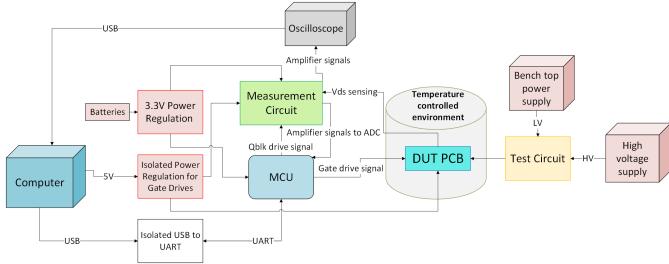

## IV. CIRCUIT VALIDATION

A diagram of the complete system for evaluating dynamic  $R_{\text{ds}(\text{on})}$  is shown in Fig. 7. The PCB with the DUT resides in an environment at the testing temperature (e.g. RT, liquid nitrogen, or vacuum chamber) while the other circuitry may remain outside that environment. Note that the DUT PCB is identical to the GaN half-bridge PCB validated to work at 77K in [17], except with top-side instead of bottom-side cooled GaN HEMTs, so the DUT PCB will work at CT. A C2000 microcontroller (MCU) is used to control the switches and measure the amplifier outputs. To cross-check the MCU's measurements, an oscilloscope is used to monitor the amplifier outputs in parallel. A computer controls and logs data from both the MCU and oscilloscope via USB and supplies power for the gate drives. To minimize noise on the amplifier signals, batteries are used to supply a clean DC voltage to the amplifier.

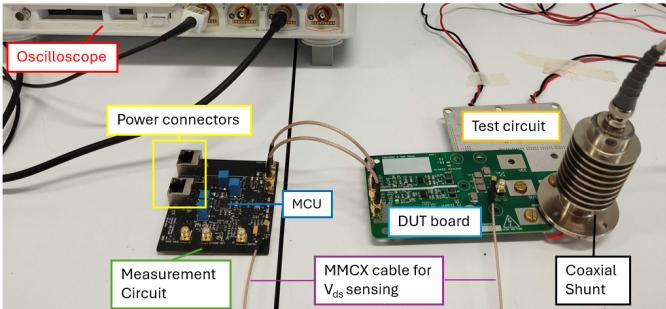

Fig. 8 shows the physical implementation of the evaluation circuit. Power for the gate drives, microcontroller and amplifier are supplied through two RJ45 connectors. Key component values and parameters are specified in Table I. The amplifiers utilize the AD8656 OpAmp and have a bandwidth of approximately 3 MHz. Soft switching of the DUT is enacted by turning  $Q_{\text{blk}}$  on 200 ns before the DUT.

Fig. 7: Diagram of the dynamic  $R_{ds(on)}$  evaluation system

Fig. 8: The assembled evaluation circuit with a coaxial shunt for validation tests

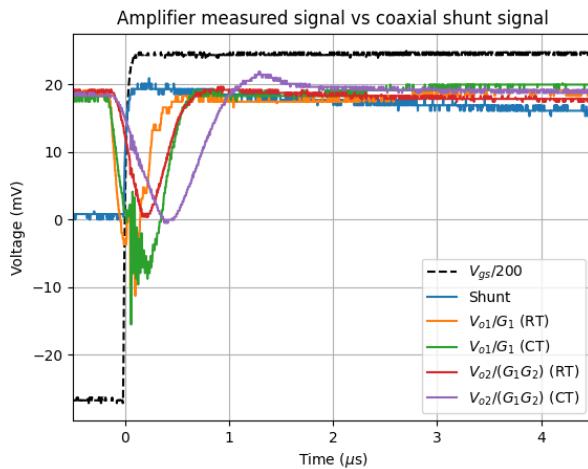

Fig. 9: Waveforms for amplifier validation using the coaxial shunt at  $I_{ds(on)} = 1$  A at both RT and CT (77 K). The amplifier signals have the corresponding gains removed for comparison with the shunt signal.

To validate the operation of the evaluation circuit, a  $20\text{ m}\Omega$  coaxial shunt resistor (1M-1 from T&M [58]) was placed in series with the DUT. The output signal of the shunt, proportional to  $I_{ds}$ , is measured by the oscilloscope and fed into the measurement circuit (i.e. instead of measuring  $V_{ds}$ , the measurement circuit measures the shunt signal) to verify the accuracy of the measurement circuit. Measurements were performed on the measurement circuit and MCU at both RT and CT (77 K), because in actual cryogenic experiments, those

TABLE I: Parameters of the evaluation circuit

| Component | Value                |

|-----------|----------------------|

| DUT       | GS66508T             |

| $Q_{blk}$ | GS66508T             |

| $R_{LV}$  | $5\ \Omega$          |

| $R_{HV}$  | $390\text{ k}\Omega$ |

| $D_1$     | IDL04G65C5           |

| $R_{PD}$  | $11\ \Omega$         |

| $G_1$     | 9.52                 |

| $G_2$     | 9.45                 |

components may be exposed to cryogenic temperatures due to their close proximity to the DUT. Results in Fig. 9 demonstrate that at RT  $v_{o1}$  and  $v_{o2}$  converge to the shunt signal within approximately 500 ns and 900 ns after the turn-on respectively. At CT, the measurement circuit functions correctly but is slower, whereby  $v_{o1}$  and  $v_{o2}$  converging to the shunt signal within approximately 900 ns and 2  $\mu$ s respectively. Therefore, for CT measurements, the  $R_{ds(on)}$  will need to be sampled a longer time after the DUT turn-on than for RT measurements.

The coaxial shunt signal confirms that  $I_{ds(on)}$  is DC as theorized in Section III-B. There is, however, a small ripple on  $I_{ds(on)}$  which can be eliminated by additional bulk decoupling capacitors on LV. Furthermore, the DC steady state errors are due to tolerances in the amplifier gain and the OpAmp input offset voltages which can be calibrated out prior to executing dynamic  $R_{ds(on)}$  measurements. Note that the test circuit may also be exposed to cryogenic temperatures and works at CT because it is composed of only passive components and diodes which work at CT [24].

## V. CONCLUSION

A measurement scheme utilizing on-the-fly measurements has been proposed to characterise the off-state trapping transients in GaN HEMTs. Based on requirements derived from the measurement scheme, a dynamic  $R_{ds(on)}$  evaluation circuit suitable for measurements at CT has been designed and validated. The evaluation circuit consists of (a) a novel test circuit using a resistive load with independent control of stress voltage and device current and (b) a clamping circuit utilizing a blocking switch, which was selected after a comprehensive analysis of clamping circuits in the literature. A high speed amplifier was designed to amplify the output of the measurement circuit so that the low  $R_{ds(on)}$  at CT can be accurately measured. The evaluation circuit was demonstrated to successfully measure the dynamic  $R_{ds(on)}$  500 ns after the DUT turn-on for RT measurements and 2  $\mu$ s after the DUT turn-on for CT measurements. Dynamic  $R_{ds(on)}$  characterisations are thus ready to be performed in future work.

## ACKNOWLEDGEMENT

This work was supported by the New Zealand Ministry of Business, Innovation, and Employment through the Strategic Science Investment Fund Advanced Energy Platform under the program *High Power Electric Motors for Large-Scale Transport* contract RTVU2004.

## REFERENCES

[1] L. Ybanez *et al.*, "ASCEND: The first step towards cryogenic electric propulsion," *IOP Conference Series: Materials Science and Engineering*, vol. 1241, no. 1, p. 012034, May 2022.

[2] H. Schefer, W.-R. Canders, J. Hoffmann, R. Mallwitz, and M. Henke, "Cryogenically-Cooled Power Electronics for Long-Distance Aircraft," *IEEE Access*, vol. 10, pp. 132,279-133,308, 2022.

[3] K. Rajashekara and B. Akin, "Cryogenic Power Conversion Systems: The next step in the evolution of power electronics technology," *IEEE Electrification Magazine*, vol. 1, no. 2, pp. 64-73, Dec. 2013.

[4] F. F. Wang, R. Chen, and Z. Dong, "Power Electronics: A critical enabler of future hydrogen-electric systems for aviation," *IEEE Electrification Magazine*, vol. 10, no. 2, pp. 57-68, Jun. 2022.

[5] R. L. Patterson *et al.*, "Electrical Devices and Circuits for Low Temperature Space Applications," 2003.

[6] C. A. Luongo *et al.*, "Next Generation More-Electric Aircraft: A Potential Application for HTS Superconductors," *IEEE Transactions on Applied Superconductivity*, vol. 19, no. 3, pp. 1055-1068, Jun. 2009.

[7] "The aviation sector wants to reach net zero by 2050. How will it do it?" World Economic Forum, (Dec. 9, 2022), [Online]. Available: <https://www.weforum.org/agenda/2022/12/aviation-net-zero-emissions/> (visited on 01/21/2024).

[8] T. Van Do, J. P. F. Trovão, K. Li, and L. Boulin, "Wide-Bandgap Power Semiconductors for Electric Vehicle Systems: Challenges and Trends," *IEEE Vehicular Technology Magazine*, vol. 16, no. 4, pp. 89-98, Dec. 2021.

[9] A. Doronzo, "Advantages of wide band gap materials in power electronics – part 1," 2023.

[10] M. Di Paolo Emilio, *Ed.*, *GaN Technology: Materials, Manufacturing, Devices and Design for Power Conversion*. Cham: Springer Nature Switzerland, 2024.

[11] A. Wadsworth, D. J. Thrimawithana, L. Zhao, M. Neuburger, R. A. Oliver, and D. J. Wallis, "GaN-based cryogenic temperature power electronics for superconducting motors in cryo-electric aircraft," *Superconductor Science and Technology*, vol. 36, no. 9, p. 094002, Jul. 2023.

[12] Y. Wei, M. M. Hossain, and H. A. Mantooth, "Static and Dynamic Cryogenic Characterizations of Commercial High Performance GaN HEMTs for More Electric Aircraft," in *2022 International Power Electronics Conference (IPEC-Himeji 2022- ECCE Asia)*, May 2022, pp. 2300-2306.

[13] R. Chen and F. F. Wang, "SiC and GaN Devices With Cryogenic Cooling," *IEEE Open Journal of Power Electronics*, vol. 2, no. 1, Apr. 22, 2021.

[14] R. Ren *et al.*, "Characterization and Failure Analysis of 650-V Enhancement-Mode GaN HEMT for Cryogenically Cooled Power Electronics," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 66-76, Mar. 2020.

[15] Y. Wei, M. M. Hossain, and H. A. Mantooth, "Comparisons and Evaluations of Silicon and Wide Band Gap Devices at Cryogenic Temperature," *IEEE Transactions on Industry Applications*, pp. 1-13, 2022.

[16] M. Mehrabankhahmardash *et al.*, "Static and Dynamic Characterization of 650 V GaN E-HEMT's in Room and Cryogenic Environments," in *2021 IEEE Energy Conversion Congress and Exposition (ECCE)*, Oct. 2021, pp. 5289-5296.

[17] A. Wadsworth, M. G. Pearce, and D. J. Thrimawithana, "A Cryogenic 3-kW GaN E-HEMT Synchronous Buck Converter," *IEEE Transactions on Industrial Electronics*, pp. 1-10, 2023.

[18] M. ul Hassan, A. I. Emon, F. Luo, and V. Solov'yov, "Design and Validation of a 20-kVA, Fully Cryogenic, Two-Level GaN-Based Current Source Inverter for Full Electric Aircrafts," *IEEE Transactions on Transportation Electrification*, vol. 8, no. 4, pp. 4743-4759, Dec. 2022.

[19] M. Meneghini *et al.*, "GaN-based power devices: Physics, reliability, and perspectives," *Journal of Applied Physics*, vol. 130, no. 18, p. 181101, Nov. 8, 2021.

[20] M. Meneghini *et al.*, "Reliability and failure analysis in power GaN-HEMTs: An overview," in *2017 IEEE International Reliability Physics Symposium (IRPS)*, Apr. 2017, 3B-2.1-3B-2.8.

[21] G. Zulaulf, M. Guacci, and J. W. Kolar, "Dynamic On-Resistance in GaN-on-Si HEMTs: Origins, Dependencies, and Future Characterization Frameworks," *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 5581-5588, Jun. 2020.

[22] J. P. Kozak *et al.*, "Stability, Reliability, and Robustness of GaN Power Devices: A Review," *IEEE Transactions on Power Electronics*, vol. 38, no. 7, pp. 8442-8471, Jul. 2023.

[23] "White Paper - Reliability and qualification of CoolGaN™."

[24] H. Gui *et al.*, "Review of Power Electronics Components at Cryogenic Temperatures," *IEEE transactions on power electronics*, vol. 35, no. 5, pp. 5144-5156, May 2020, pmid: 32499667.

[25] T.-T. Kuo *et al.*, "An Extensive Negative Gate Bias Stress Degradation Mechanism in GaN MIS-HEMTs for Aerospace Applications," *IEEE Transactions on Electron Devices*, pp. 1-8, 2024.

[26] J. Hudgins, G. Simin, E. Santi, and M. Khan, "An assessment of wide bandgap semiconductors for power devices," *IEEE Transactions on Power Electronics*, vol. 18, no. 3, pp. 907-914, May 2003.

[27] M. Meneghini *et al.*, "Temperature-Dependent Dynamic  $R_{ON}$  in GaN-Based MIS-HEMTs: Role of Surface Traps and Buffer Leakage," *IEEE Transactions on Electron Devices*, vol. 62, no. 3, pp. 782-787, Mar. 2015.

[28] M. Meneghini *et al.*, "Trapping in GaN-based metal-insulator-semiconductor transistors: Role of high drain bias and hot electrons," *Applied Physics Letters*, vol. 104, no. 14, p. 143505, Apr. 8, 2014.

[29] J. Joh and J. A. del Alamo, "A Current-Transient Methodology for Trap Analysis for GaN High Electron Mobility Transistors," *IEEE Transactions on Electron Devices*, vol. 58, no. 1, pp. 132-140, Jan. 2011.

[30] N. Modolo *et al.*, "Understanding the effects of off-state and hard-switching stress in gallium nitride-based power transistors," *Semiconductor Science and Technology*, vol. 36, no. 1, p. 014001, Jan. 1, 2021.

[31] M. Goller, J. Franke, J. Lutz, S. Mouhoubi, G. Curatola, and T. Basler, "Investigation of the Trapping and Detrapping Behavior by the On-State Resistance at Low Off-State Drain Bias in Schottky p-GaN Gate HEMTs," *Solid State Phenomena*, vol. 360, pp. 9-15, Aug. 23, 2024.

[32] K. Li, P. L. Evans, and C. M. Johnson, "Characterisation and Modeling of Gallium Nitride Power Semiconductor Devices Dynamic On-State Resistance," *IEEE Transactions on Power Electronics*, vol. 33, no. 6, pp. 5262-5273, Jun. 2018.

[33] K. Li, A. Videt, N. Idir, P. Evans, and M. Johnson, "Modelling GaN-HEMT Dynamic ON-state Resistance in High Frequency Power Converter," in *2020 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2020, pp. 1949-1955.

[34] I. Rossetti *et al.*, "Evidence of Hot-Electron Effects During Hard Switching of AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 64, no. 9, pp. 3734-3739, Sep. 2017.

[35] N. Modolo *et al.*, "A Physics-Based Approach to Model Hot-Electron Trapping Kinetics in p-GaN HEMTs," *IEEE Electron Device Letters*, vol. 42, no. 5, pp. 673-676, May 2021.

[36] "GaN Reliability and Lifetime Projections: Phase 14," (), [Online]. Available: <https://epc-co.com/epc/Portals/0/epc/documents/product-training/Reliability%20Report%20Phase%2014.pdf> (visited on 09/18/2024).

[37] H. Zhu and E. Matioli, "Accurate Measurement of Dynamic On-Resistance in GaN Transistors at Steady-State," *IEEE Transactions on Power Electronics*, vol. 38, no. 7, pp. 8045-8050, Jul. 2023.

[38] L. Gill, S. DasGupta, J. C. Neely, R. J. Kaplar, and A. J. Michaels, "A Review of GaN HEMT Dynamic ON-Resistance and Dynamic Stress Effects on Field Distribution," *IEEE Transactions on Power Electronics*, vol. 39, no. 1, pp. 517-537, Jan. 2024.

[39] A. Santarelli *et al.*, "A Double-Pulse Technique for the Dynamic I/V Characterization of GaN FETs," *IEEE Microwave and Wireless Components Letters*, vol. 24, no. 2, pp. 132-134, Feb. 2014.

[40] R. Hou, Y. Shen, H. Zhao, H. Hu, J. Lu, and T. Long, "Power Loss Characterization and Modeling for GaN-Based Hard-Switching Half-Bridges Considering Dynamic on-State Resistance," *IEEE Transactions on Transportation Electrification*, vol. 6, no. 2, pp. 540-553, Jun. 2020.

[41] W. Wang, Y. Liang, M. Zhang, F. Lin, F. Wen, and H. Wang, "Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test," *Electronics*, vol. 10, no. 10, p. 202, 10 Jan. 2021.

[42] T. Foulkes, T. Modeer, and R. C. N. Pilawa-Podgurski, "Quantifying Dynamic On-State Resistance of GaN HEMTs for Power Converter Design via a Survey of Low and High Voltage Devices," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4036-4049, Aug. 2021.

[43] N. Badawi and S. Dieckerhoff, "A new Method for Dynamic Ron Extraction of GaN Power HEMTs," 2015.

[44] R. Li, X. Wu, S. Yang, and K. Sheng, "Dynamic On-State Resistance Test and Evaluation of GaN Power Devices Under Hard- and Soft-Switching Conditions by Double and Multiple Pulses," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1044-1053, Feb. 2019.

[45] N. Badawi, O. Hilt, E. Bahat-Treidel, J. Böcker, J. Wuerfl, and S. Dieckerhoff, "Investigation of the Dynamic On-State Resistance of 600V Normally-off and Normally-on GaN HEMTs," Sep. 20, 2015.

[46] B. Lu, T. Palacios, D. Ristad, S. Bahl, and D. I. Anderson, "Extraction of Dynamic On-Resistance in GaN Transistors: Under Soft- and Hard-Switching Conditions," in *2011 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS)*, Waikoloa, HI, USA: IEEE, Oct. 2011, pp. 1-4.

[47] C. Bernal, M. Jimenez, and F. Andrade, "Evaluating the JEDEC Standard JEP173, Dynamic RDS(on) Test Method for GaN HEMTs," in *2020 IEEE International Symposium on Circuits and Systems (ISCAS)*, Oct. 2020, pp. 1-4.

[48] T. Arai, "Dynamic On-Resistance Measurement Technique for GaN Power Transistors," 2021.

[49] A. Chini and F. Iucolano, "Evolution of on-resistance (RON) and threshold voltage (VTH) in GaN HEMTs during switch-mode operation," *Materials Science in Semiconductor Processing: Wide Band Gap Semiconductors Technology for next Generation of Energy Efficient Power Electronics*, vol. 78, pp. 127-131, May 1, 2018.

[50] Y. Lao *et al.*, "Versatile Dynamic On-Resistance Test Bench for GaN Power Transistors with Considerations for Soft and Hard Switching, Time-Resolved Test, Packaged and On-Wafer Devices," in *2024 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, Jun. 2024, pp. 534-537.

[51] M. Sir and I. Feno, "Measurement Method for the Dynamic On-State Resistance of GaN Semiconductors," in *2018 2nd European Conference on Electrical Engineering and Computer Science (EECS)*, Bern, Switzerland: IEEE, Dec. 2018, pp. 543-546.

[52] A. N. Rahman, M.-Y. Li, M. Tampubolon, and H.-J. Chu, "High Resolution Dynamic RDS(on) Measurement of GaN using Active VDS(on) Measurement Clamp Circuit," in *2019 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia)*, May 2019, pp. 1-4.

[53] A. Alemanno, A. Santarelli, E. Sangiorgi, and C. Florian, "Characterization of the Dynamic RON of 600 V GaN Switches under Operating Conditions," *Electronics*, vol. 12, no. 4, p. 943, 4 Jan. 2023.

[54] T. Cappello, A. Santarelli, and C. Florian, "Dynamic RON Characterization Technique for the Evaluation of Thermal and Off-State Voltage Stress of GaN Switches," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 3386-3398, Apr. 2018.

[55] M. Elhazizi, Z. Khatir, R. Lallement, and J.-P. Ousten, "Investigations on the Evolution of Dynamic Ron of GaN Power Transistors during Switching Cycles," in *CIPS 2018: 10th International Conference on Integrated Power Electronics Systems*, Mar. 2018, pp. 1-6.

[56] "Dynamic ON-Resistance Measurement Techniques for GaN Power Transistors - Technical Articles," (), [Online]. Available: <https://leepower.com/technical-articles/dynamic-on-resistance-measurement-techniques-for-gan-power-transistors/> (visited on 07/23/2023).

[57] Yoshiaki Nozaki, Hiroshi Kawamura, John Kevin Twynam, and Masatomo Hasegawa, "US 2008/0309355A1," pat.

[58] "Series M Current Viewing Resistors," (), [Online]. Available: [https://www.tandmresearch.com/index.php?mact=ListIt2Products\\_cntnt01\\_detail\\_0&cntnt01item=series-m&cntnt01template\\_summary=Side&cntnt01returnid=19](https://www.tandmresearch.com/index.php?mact=ListIt2Products_cntnt01_detail_0&cntnt01item=series-m&cntnt01template_summary=Side&cntnt01returnid=19) (visited on 10/30/2024).