# Performance Engineering of Hybrid Message Passing + Shared Memory Programming on Multi-Core Clusters

**Martin James Chorley**

2012

Cardiff University

School of Computer Science & Informatics

A thesis submitted in partial fulfilment of the requirement for the degree of Doctor of Philosophy

| <b>T</b> |      | 4 •  |

|----------|------|------|

| Decl     | lara | tion |

This work has not previously been accepted in substance for any other degree or award at this

### **Statement 3**

Date

| I hereby give consent for my thesis, if accepted, to be available for photocopying and for inte | r |

|-------------------------------------------------------------------------------------------------|---|

| library loan, and for the title and summary to be made available to outside organisations.      |   |

| Signed | <br>(candidate) |

|--------|-----------------|

| Date   |                 |

Signed ..... (candidate)

For Lisa

## **Abstract**

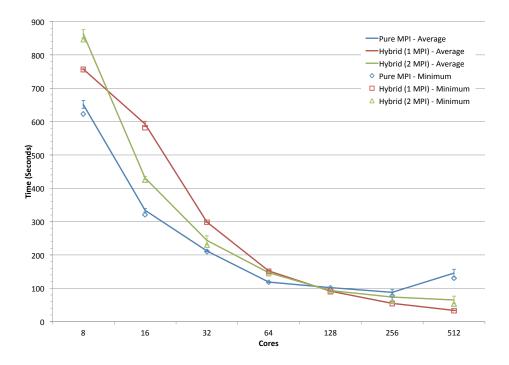

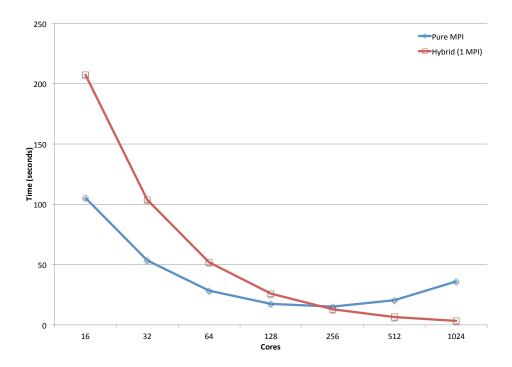

The hybrid message passing + shared memory programming model combines two parallel programming styles within the same application in an effort to improve the performance and efficiency of parallel codes on modern multi-core clusters. This thesis presents a performance study of this model as it applies to two Molecular Dynamics (MD) applications. Both a large scale production MD code and a smaller scale example MD code have been adapted from existing message passing versions by adding shared memory parallelism to create hybrid message passing + shared memory applications. The performance of these hybrid applications has been investigated on different multi-core clusters and compared with the original pure message passing codes. This performance analysis reveals that the hybrid message passing + shared memory model provides performance improvements under some conditions, while the pure message passing model provides better performance in others. Typically, when running on small numbers of cores the pure message passing model provides better performance than the hybrid message passing + shared memory model, as hybrid performance suffers due to increased overheads from the use of shared memory constructs. However, when running on large numbers of cores the hybrid model performs better as these shared memory overheads are minimised while the pure message passing code suffers from increased communication overhead. These results depend on the interconnect used. Hybrid message passing + shared memory molecular dynamics codes are shown to exhibit different communication profiles from their pure message passing versions and this is revealed to be a large factor in the performance difference between pure message passing and hybrid message passing + shared memory codes. An extension of this result shows that the choice of interconnection fabric used in a multi-core cluster has a large impact on the performance difference between the pure message passing and the hybrid code. The factors affecting the performance of the applications have been analytically examined in an effort to describe, generalise and predict the performance of both the pure message passing and hybrid message passing + shared memory codes.

viii Abstract

# Acknowledgements

Throughout this research I have been supported by many different people who deserve acknowledgement here. Firstly I must thank my supervisor David Walker for his invaluable assistance and support over the last five years. I must also thank Martyn Guest for technical advice and support; without his aid in gaining access to multi-core systems the performance analysis in this thesis would be much slimmer. The advice of the external examiners was also gratefully received and helped to improve the thesis immensely, as did the tireless work of Professor Alex Gray, who deserves many thanks for his help and assistance. Thanks are due to all the system admins and developers who have put up with a barrage of emails and questions from me over the years, and their frequent and timely responses were a huge help. The community of research students in COMSC is a great support network and thanks are due to all of them. Special thanks are due to Ian Cooper and Gualtiero Colombo who have been great office mates and work colleagues over the last few years, and Mark Hall who provided much support during his time here. I must also thank Matt, Chris, Will, Mark, Rich and Jon for keeping me entertained and distracted for the last year. I definitely need to acknowledge my colleagues and bosses, Roger Whitaker and Stuart Allen, who have led me onto new and exciting research projects and then put up with me when I needed to stop and come back to this thesis. I would like to thank everyone at EPCC in Edinburgh where I spent my time on the MSc in HPC during my PhD, being there taught me an enormous amount about HPC and computational science, and I am forever grateful for the opportunity to spend time in a truly great city. My friends have also provided much support while I have been working on this thesis. Robert and Carin, Chris J and Chris F have all made frequent visits to Cardiff and provided most welcome distractions from my work over the last few years. Finally of course I must thank my family. Mum and Ed, who have provided both emotional and financial support during my PhD deserve big thanks, as do my sister Hannah and nephews Ryan and Alex. I must also thank my father for the invaluable life lessons I have learnt from him in the last few years. Most of all, I thank Lisa. Her support and encouragement has been unwavering, and it is down to her that I have finally reached this point.

Thank you all.

# **Contents**

| Abstract |                  |         |                                               | vii |  |

|----------|------------------|---------|-----------------------------------------------|-----|--|

| A        | Acknowledgements |         |                                               |     |  |

| Co       | ontent           | ts      |                                               | xi  |  |

| 1        | Intr             | oductio | n                                             | 1   |  |

|          | 1.1              | Introdu | uction                                        | 2   |  |

|          | 1.2              | Thesis  | Aims                                          | 4   |  |

|          | 1.3              | Contri  | butions                                       | 4   |  |

|          | 1.4              | Thesis  | Structure                                     | 5   |  |

|          |                  | 1.4.1   | Small Scale MD Code                           | 7   |  |

|          |                  | 1.4.2   | Real World MD Application                     | 8   |  |

|          |                  | 1.4.3   | Performance Analysis                          | 9   |  |

| 2        | Bacl             | kground | d                                             | 11  |  |

|          | 2.1              | Paralle | el Programming                                | 13  |  |

|          |                  | 2.1.1   | Data Parallelism                              | 13  |  |

|          |                  | 2.1.2   | Message Passing and Shared Memory Programming | 15  |  |

|          |                  | 2.1.3   | MPI                                           | 17  |  |

|          |                  | 2.1.4   | OpenMP                                        | 27  |  |

|          |                  | 2.1.5   | MPI vs. OpenMP                                | 30  |  |

|          | 2.2              | Multi-  | core Clusters                                 | 30  |  |

|          |                  | 2.2.1   | Multi-core Processors                         | 32  |  |

|          |                  | 2.2.2   | Multi-core Nodes vs. SMP Systems              | 34  |  |

xii Contents

|   |      | 2.2.3    | HPC Interconnects                        | 36 |

|---|------|----------|------------------------------------------|----|

|   | 2.3  | Hybrid   | l Programming                            | 38 |

|   |      | 2.3.1    | Hybrid Model Performance                 | 39 |

|   |      | 2.3.2    | Hybrid Code Profiling                    | 41 |

|   |      | 2.3.3    | Performance Issues with the Hybrid Model | 42 |

|   |      | 2.3.4    | Classifying Hybrid Codes                 | 44 |

|   |      | 2.3.5    | Other MP + SM Combinations               | 45 |

|   |      | 2.3.6    | Previous Work Comparison                 | 46 |

|   | 2.4  | Perform  | mance Modelling                          | 46 |

|   |      | 2.4.1    | Modelling MPI Routines                   | 48 |

|   |      | 2.4.2    | Modelling Hybrid Code                    | 49 |

|   | 2.5  | Molec    | ular Dynamics                            | 50 |

| 3 | Perf | ormanc   | re Testing                               | 53 |

|   | 3.1  | Hardw    | are                                      | 54 |

|   |      | 3.1.1    | Merlin                                   | 54 |

|   |      | 3.1.2    | CSEEM64T                                 | 54 |

|   |      | 3.1.3    | Stella                                   | 55 |

|   |      | 3.1.4    | Hardware Performance                     | 55 |

|   | 3.2  | Testing  | g Methodology                            | 59 |

|   |      | 3.2.1    | Performance Timing                       | 60 |

|   |      | 3.2.2    | Job Schedulers                           | 62 |

|   |      | 3.2.3    | MPI Processes and OpenMP Threads         | 65 |

|   | 3.3  | Nodes    | /Cores/Processes/Threads                 | 65 |

| 4 | Sma  | ll Scale | MD Code                                  | 69 |

|   | 4.1  | MD In    | troduction                               | 70 |

|   |      | 4.1.1    | Hybrid Version                           | 71 |

|   | 4.2  | Perform  | mance Testing                            | 73 |

|   |      | 4.2.1    | Methodology                              | 73 |

|   | 4.3  | Hybrid   | l Code Performance                       | 74 |

Contents xiii

|   |      | 4.3.1   | Memory Bandwidth and Cache Sharing         | 75  |

|---|------|---------|--------------------------------------------|-----|

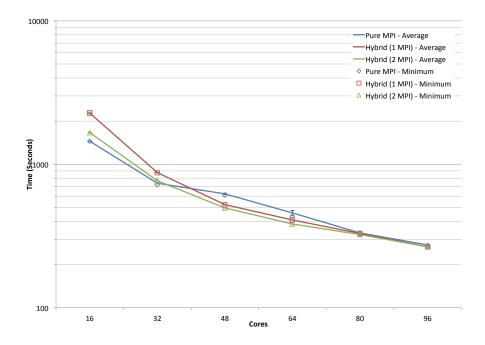

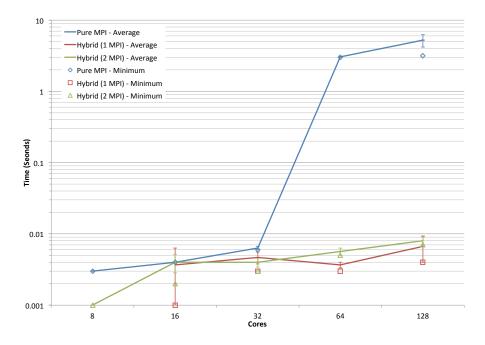

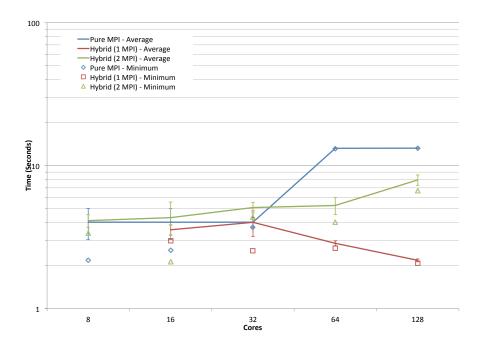

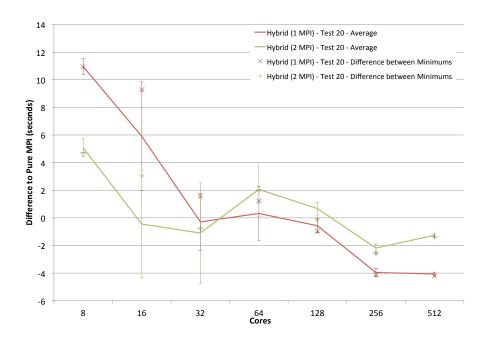

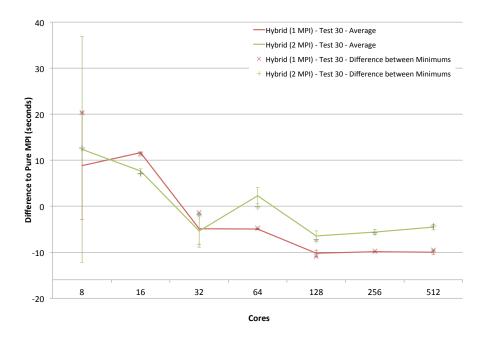

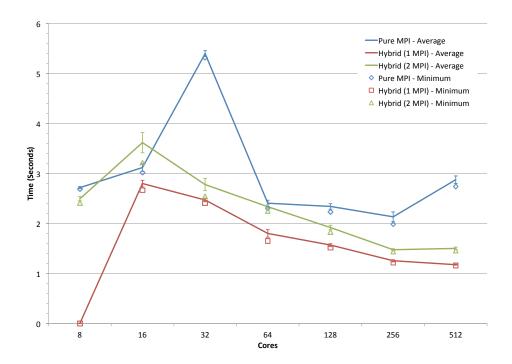

|   |      | 4.3.2   | Overall Timing                             | 78  |

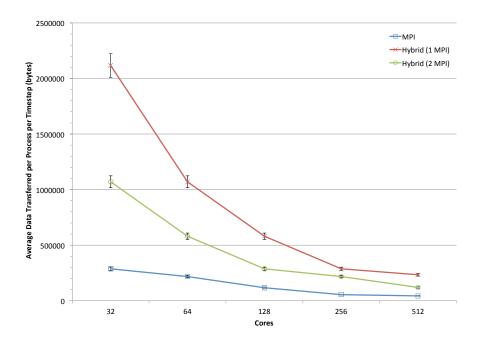

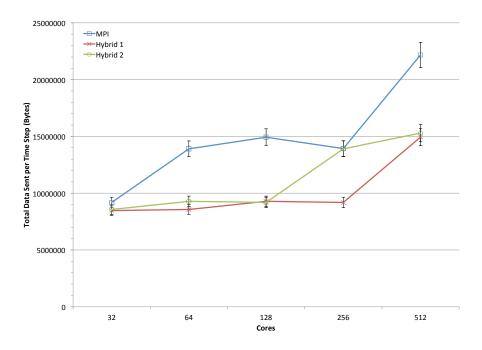

|   |      | 4.3.3   | Communication Profile                      | 88  |

|   |      | 4.3.4   | Shared Memory Overheads                    | 98  |

|   |      | 4.3.5   | Routine Breakdowns                         | 101 |

| 5 | Real | l-World | MD Application                             | 107 |

|   | 5.1  | DL_Po   | oly Introduction                           | 108 |

|   |      | 5.1.1   | Hybrid Version                             | 109 |

|   | 5.2  | Perform | mance Testing                              | 112 |

|   |      | 5.2.1   | Methodology                                | 112 |

|   | 5.3  | Hybrid  | l Code Performance                         | 113 |

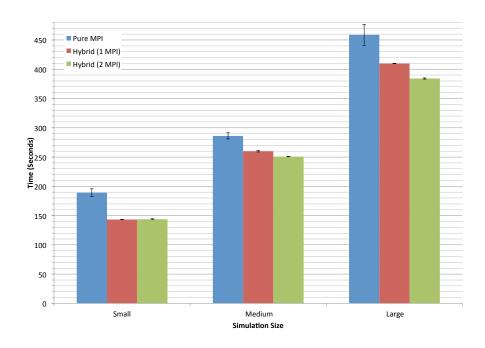

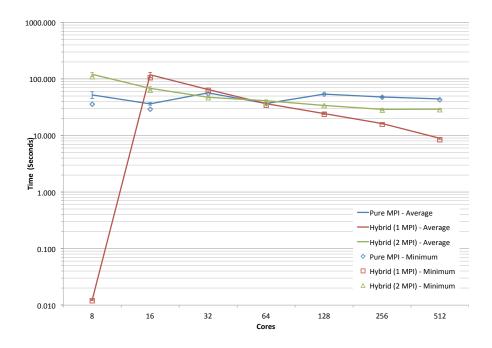

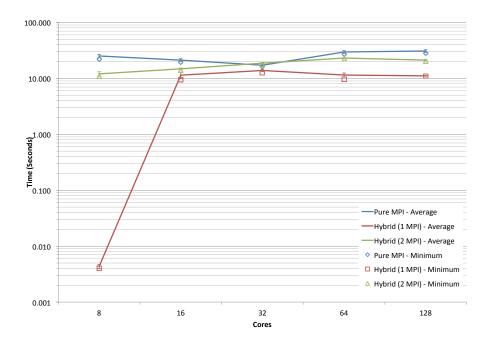

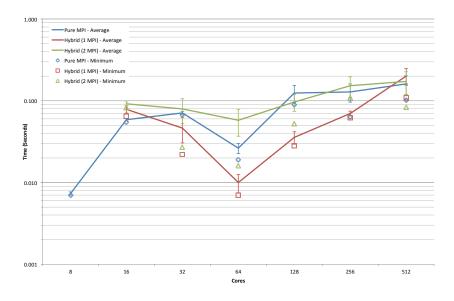

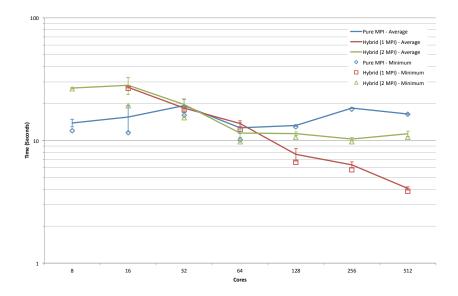

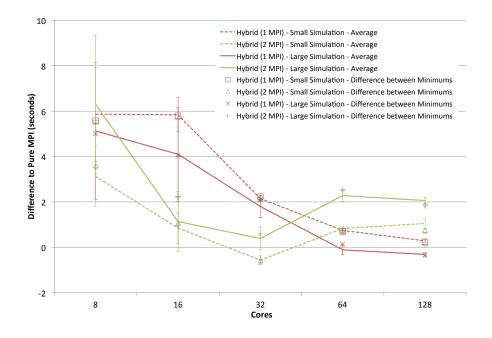

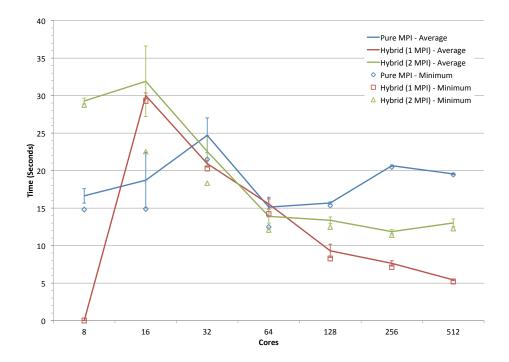

|   |      | 5.3.1   | Overall Timing                             | 113 |

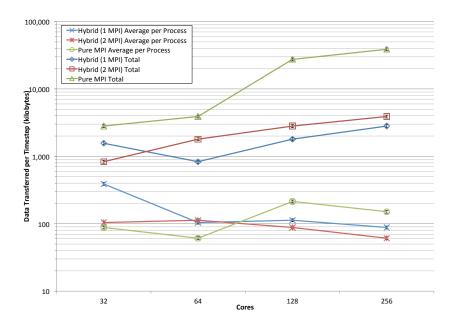

|   |      | 5.3.2   | Communication Profile                      | 121 |

|   |      | 5.3.3   | Threading Overheads                        | 132 |

| 6 | Hyb  | rid Mo  | del Performance                            | 141 |

|   | 6.1  | Introdu | action                                     | 142 |

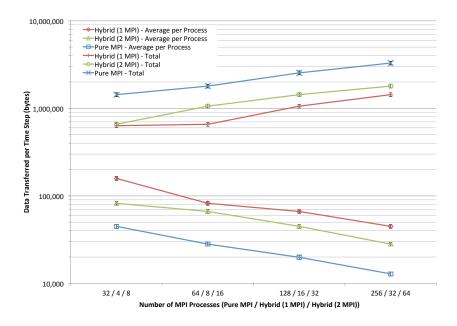

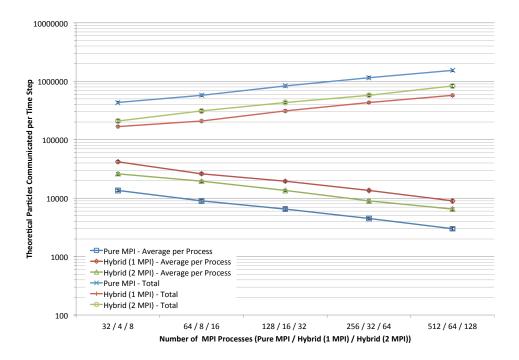

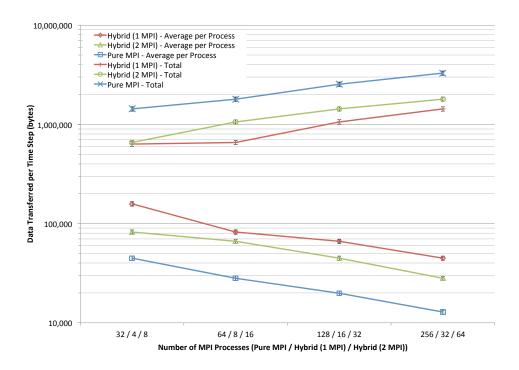

|   | 6.2  | Comm    | unication Profile                          | 144 |

|   |      | 6.2.1   | Point-to-Point Communication               | 145 |

|   |      | 6.2.2   | Collective Communication                   | 156 |

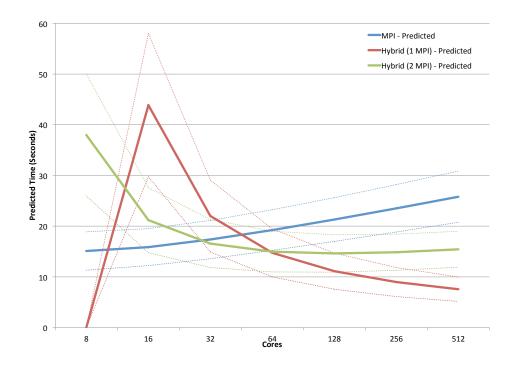

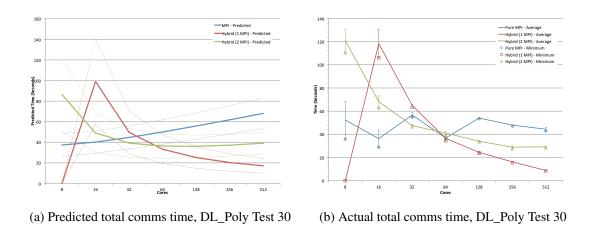

|   |      | 6.2.3   | Total Communication                        | 161 |

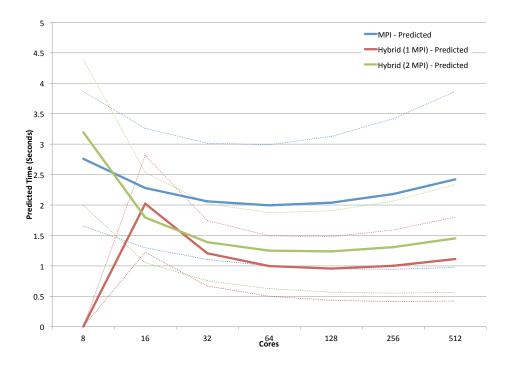

|   |      | 6.2.4   | Communication Timing Performance Models    | 166 |

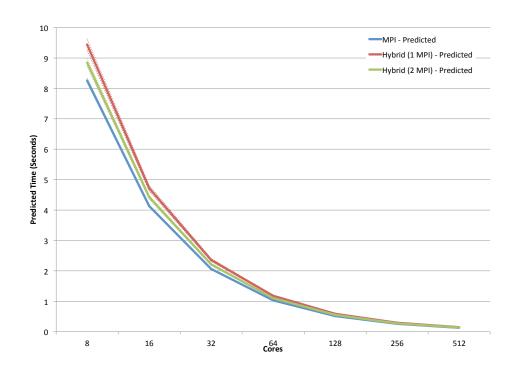

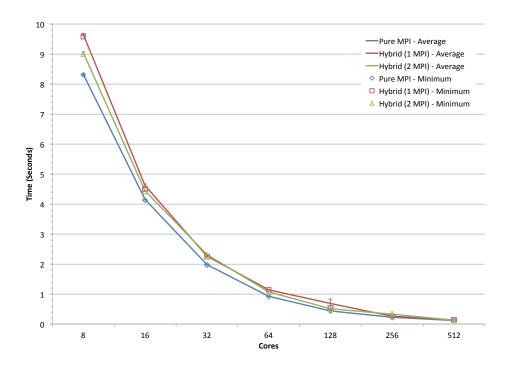

|   | 6.3  | Comp    | ıtation                                    | 167 |

|   |      | 6.3.1   | Direct Overheads                           | 167 |

|   |      | 6.3.2   | Indirect Overheads                         | 173 |

|   | 6.4  | Overal  | l Performance                              | 174 |

|   | 6.5  | Applic  | ability to General Hybrid Code Performance | 179 |

|   | 6.6  | Future  | Hybrid Code Performance                    | 182 |

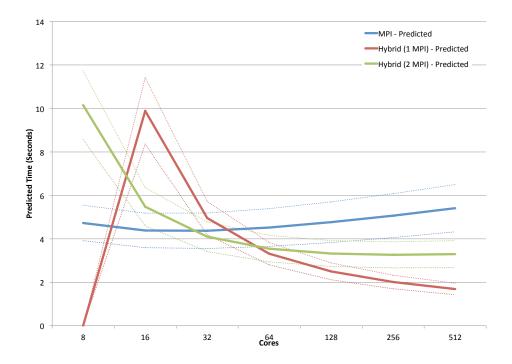

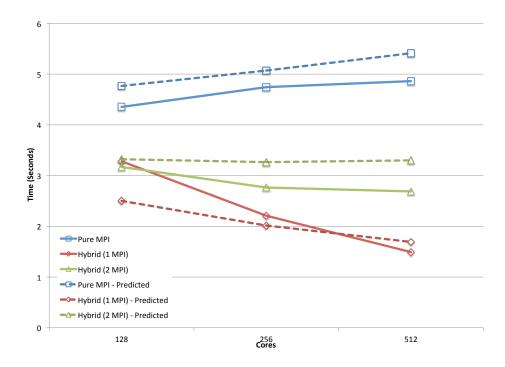

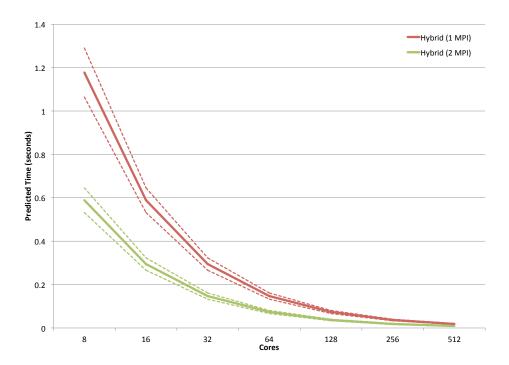

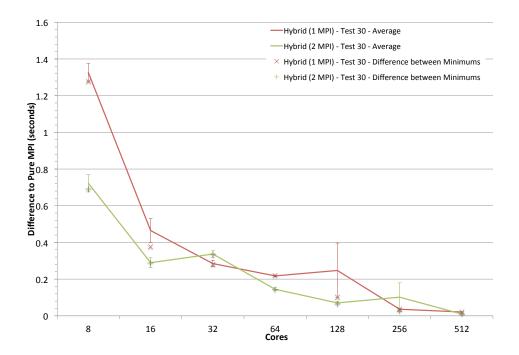

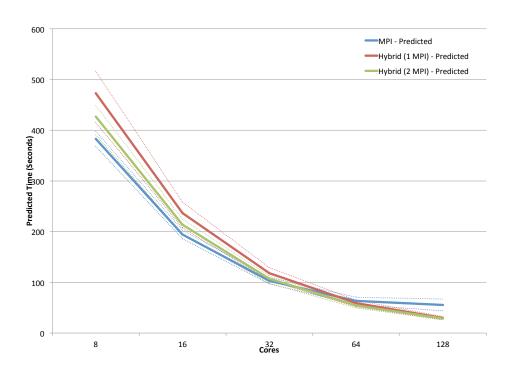

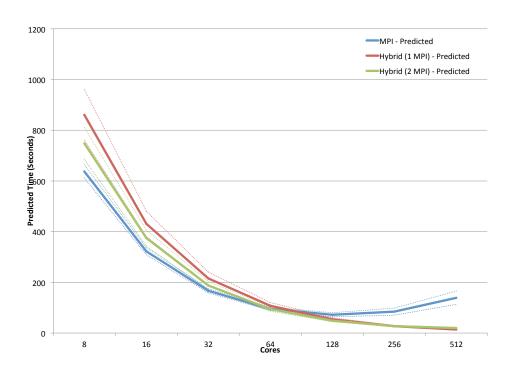

|   | 6.7  | Perform | mance Model Evaluation                     | 186 |

xiv Contents

| 7 Conclusion |                 |                                    |     |  |  |  |  |

|--------------|-----------------|------------------------------------|-----|--|--|--|--|

|              | 7.1             | Introduction                       | 190 |  |  |  |  |

|              | 7.2             | Shared Memory Threading            | 191 |  |  |  |  |

|              | 7.3             | Communication Profile              | 192 |  |  |  |  |

|              | 7.4             | Performance Models                 | 193 |  |  |  |  |

|              | 7.5             | Hybrid Code Performance            | 194 |  |  |  |  |

|              | 7.6             | Future Work                        | 195 |  |  |  |  |

|              |                 | 7.6.1 Hybrid Implementations       | 195 |  |  |  |  |

| A            | Prac            | tical Notes on Running Hybrid Code | 197 |  |  |  |  |

| Lis          | List of Figures |                                    |     |  |  |  |  |

| Lis          | List of Tables  |                                    |     |  |  |  |  |

| Lis          | Listings        |                                    |     |  |  |  |  |

| Bil          | Bibliography 2  |                                    |     |  |  |  |  |

# **Chapter 1**

## Introduction

#### **Overview**

This thesis is concerned with examining and analysing the hybrid message passing + shared memory parallel programming model as it applies to a particular class of parallel applications and their performance on multi-core clusters. The performance of the hybrid model has been examined with reference to the performance of the pure message passing programming model, allowing comparisons to be made between the two. Analysis of the performance of the two models reveals the main differences between the paradigms and allows understanding of the model performance.

This chapter presents an overview of the thesis topic and a motivation for the work included. It presents the main aims of the thesis, describes the work carried out and the contributions arising from that work. It also presents the structure of the thesis.

2 1.1 Introduction

#### 1.1 Introduction

This thesis is focused in the field of High Performance Computing (HPC). HPC is a fast changing area, where technologies and architectures are constantly advancing; a field "characterized by a rapid change of vendors, architectures, technologies and the usage of systems" [109, 108]. Much programming effort is focused on improving and maximising parallel efficiency of codes on current hardware architectures. The result of this effort may be that parallel code and applications that are written for one generation of hardware may not perform efficiently on the next generation of parallel architectures. "[S]oftware that encapsulates all this time, energy and thought, routinely outlasts ... the hardware it was originally designed to run on" [42], and a "rapid growth in computational capability ... is driving computational scientists to develop new, more complex algorithms to make better use of the systems" [6]. Understanding the best programming models and parallelisation strategies to use in order to achieve maximum efficiency of new hardware is an important task [116, 9]. As hardware changes, application codes and programming models must necessarily change also; with reference to modern multi-core architectures: "We are on the verge of a transformation in software design at least as potent as the change engendered a decade ago by message passing architectures, when the community had to rethink and rewrite many of its algorithms, libraries and applications" [25].

This thesis specifically examines the behaviour and performance of the hybrid message passing (MP) + shared memory (SM) programming model, (sometimes also more distinctively known as mixed-mode programming [23]) which combines both message passing and shared memory programming styles within a single parallel application in order to take advantage of the hierarchical and hybrid nature of the underlying parallel hardware. Two hybrid Molecular Dynamics (MD) applications are analysed within this work. Both are adapted from pre-existing 'pure' message passing codes that have been parallelised using the Message Passing Interface (MPI) library. OpenMP parallelisation is added to these applications to provide shared memory parallelism on top of the existing message passing parallelisation in order to create a hybrid

1.1 Introduction 3

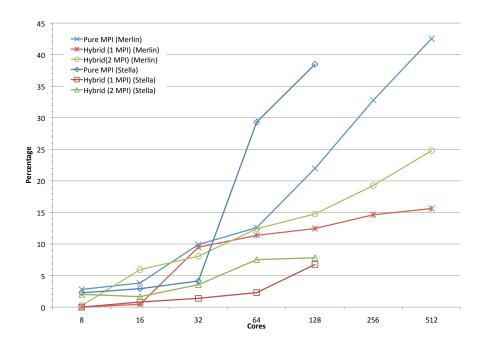

code. This hybrid message passing + shared memory code is performance tested and compared to the original pure MPI code, to draw conclusions about the performance of the hybrid model. Performance tests are carried out on a number of different multi-core HPC clusters, each of which utilises a different HPC interconnect between nodes.

Much of the previous work on the hybrid message passing + shared memory model focuses on Symmetric Multi-Processing (SMP) systems (shared memory systems) or clusters of SMPs. While multi-core systems share many characteristics with SMP systems, there are significant differences as discussed in Section 2.2 that may affect code performance. As such the study of the hybrid model on multi-core systems is a novel direction of research. The work presented in this thesis contributes further knowledge to the discussion of the hybrid programming model and its suitability for use on multi-core clusters.

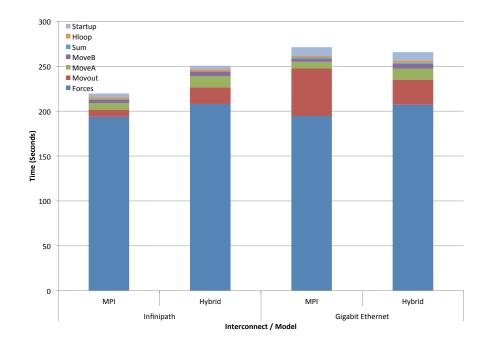

As a significant portion of the performance differences between hybrid and pure MPI codes are due to the difference in communication patterns between the two types of code, (see, for example, [26, 62, 98]) this thesis also examines the effect that the choice of interconnect fabric has on the performance of a pure MPI code compared with a hybrid MPI + OpenMP code, examining both high-end HPC Infiniband and Infinipath interconnects, a more standard 1 Gigabit Ethernet connection and a newer 10 Gigabit Ethernet connection. The properties of the interconnect used are found to have a significant bearing on the performance of the hybrid applications, and this is discussed in detail in the performance results.

The thesis provides a quantitative analysis of the differences in performance between a pure message passing and a hybrid message passing + shared memory code. This analysis gives insights into the performance of the hybrid model not only as it applies to the application codes examined in this thesis, but also into how general hybrid codes may perform on current and future generations of HPC architectures.

In the future the number of cores per processor is likely to increase, and these many-core nodes may be combined to form ever-larger clusters. Performance engineering of parallel codes and understanding the performance of the hybrid model is likely to become increasingly important

4 1.3 Contributions

in order to understand the performance characteristics of future petascale/exascale clusters and will help with understanding how to achieve good performance and scalability when using such systems.

#### 1.2 Thesis Aims

The main aim of this thesis is to offer an understanding of the hybrid message passing + shared memory model, particularly as it applies to Molecular Dynamics codes. It aims to provide a detailed investigation of the performance of such codes on modern multi-core clusters, examining not just the runtime of the applications, but also the factors affecting performance, and to provide an analytic description of these factors. In doing so it aims to increase the general knowledge of the hybrid message passing + shared memory model.

#### 1.3 Contributions

The main contributions offered by this thesis are:

- 1. A hybrid Molecular Dynamics code has been created, tested and analysed. The analysis of the performance results of this code allow us to draw conclusions on the applicability of the hybrid model to simple parallel applications of this type. Details are revealed as to which parts of the code are significantly affected by the hybridisation, and where the performance differences occur as a result of this.

- 2. A larger MD application (DL\_Poly 3.0) has been adapted to use hybrid parallelisation. This has again been performance tested and analysed, allowing further conclusions to be made on the hybrid model and allowing its applicability to large scale Molecular Dynamics codes to be assessed. This shows how the results from the small scale MD code apply to a real-world application, with larger scope and more complicated communication

1.4 Thesis Structure 5

and memory access patterns. Again, the results reveal significant differences between the performance of the hybrid message passing + shared memory and the pure message passing codes.

3. The differences between pure message passing and hybrid message passing + shared memory codes have been analytically examined. Models have been created attempting to describe the performance differences that may be seen between the two types of code, breaking these differences into their constituent factors, allowing the behaviour of particular parts of the application to be examined as well as the general performance. These models may aid with the creation of future hybrid codes and with the understanding of current code performance on future generations of parallel architecture.

#### 1.4 Thesis Structure

The thesis is structured as follows:

• Chapter 2 presents the background knowledge behind the work in this thesis and discusses related and relevant work. It begins in Section 2.1 by working from first principles of parallel programming, introducing the ideas of shared memory programming and message passing programming, then introducing the two standards for using both these models. In Section 2.2 multi-core clusters are introduced, describing multi-core processors, the differences between multi-core clusters and previous generations of hardware, and giving information on the HPC interconnects used within these systems. Section 2.3 presents the idea of combining message passing and shared memory programming, analysing previous work on the hybrid model and how the previous work compares and relates to the work contained in this thesis. This is followed with a discussion on performance modelling in Section 2.4. Finally, molecular dynamics codes are introduced in Section 2.5

6 1.4 Thesis Structure

• Chapter 3 describes the multi-core cluster hardware used for performance testing of applications within the thesis, as well as the software used on these clusters, and then presents the testing methodology used for performance analysis.

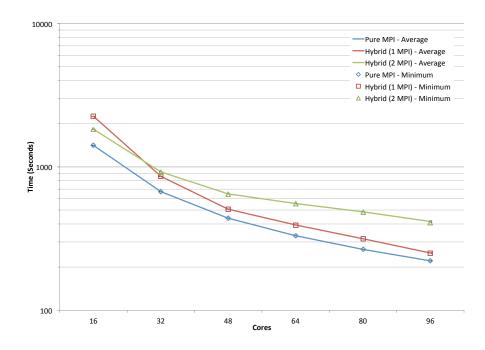

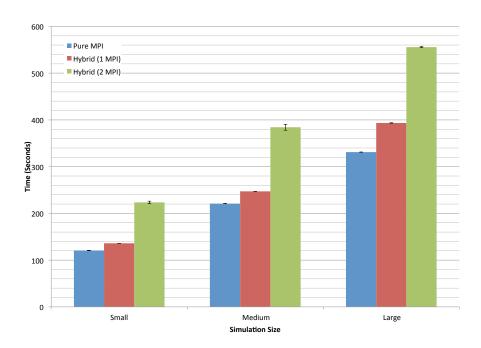

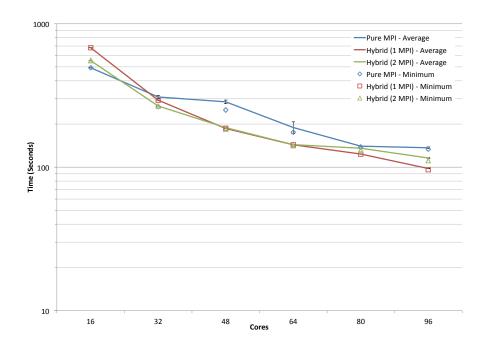

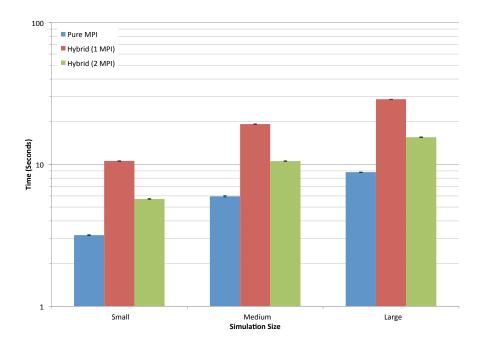

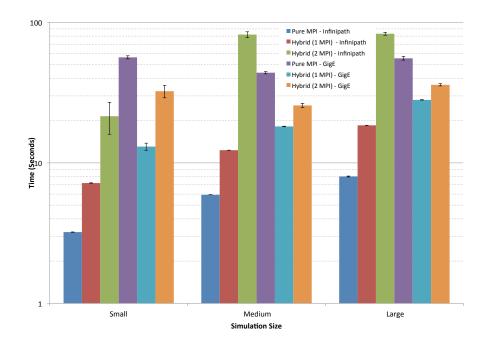

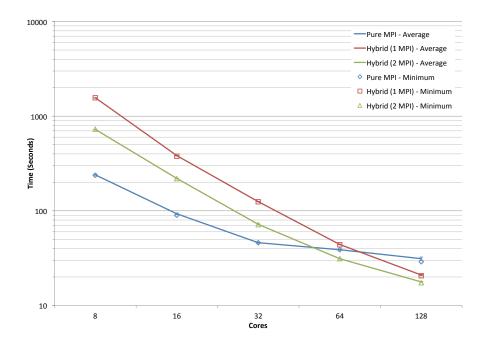

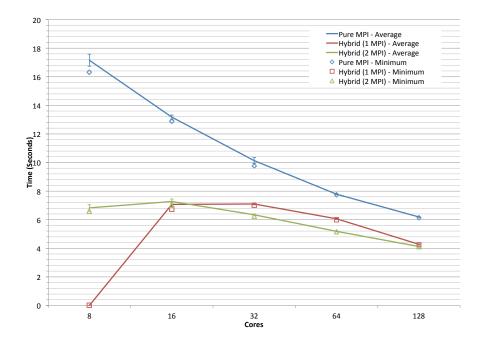

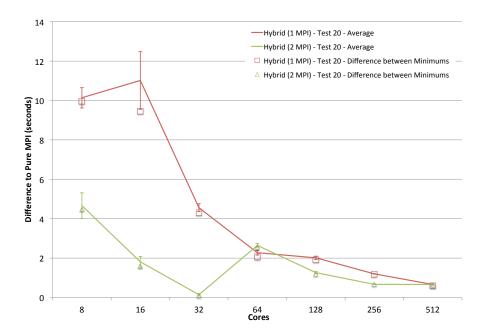

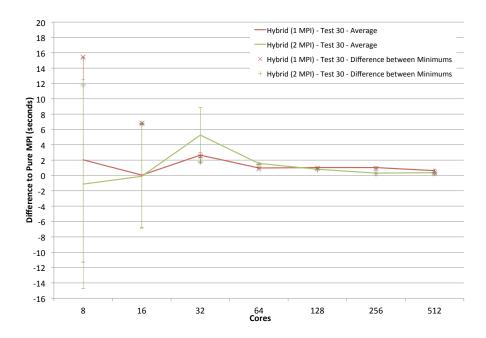

- Chapter 4 discusses the first contribution of the thesis: the creation, testing and performance analysis of the first hybrid MD code. It presents the results and draws conclusions based on these. The first MD code used in the thesis is a very simple application written in the C programming language that simulates a three-dimensional fluid using a shifted Lennard-Jones potential to model the short-range interactions The chapter starts by discussing the code in further detail in between particles. Section 4.1, before describing the creation of the hybrid version of the code from the existing message passing version. The overall performance of the code is then described and analysed in Section 4.3, followed by an in-depth look at the differences in both the communication and computation of the two styles of code. The creation of a hybrid version of the code in this chapter acts as a proof of concept, illustrating that while performance gains can be made with the hybrid model, they are highly dependent on both the interconnect used and the number of nodes of a system that are used. Pure message passing performance is much better than hybrid message passing + shared memory code performance on low numbers of nodes, and with fast low-latency interconnects.

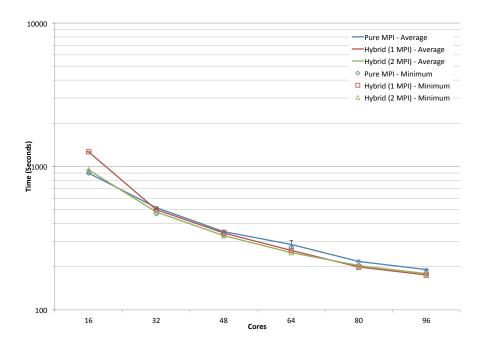

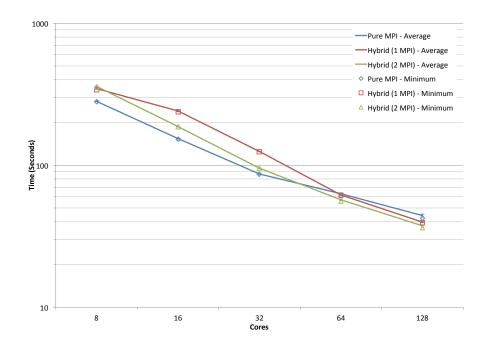

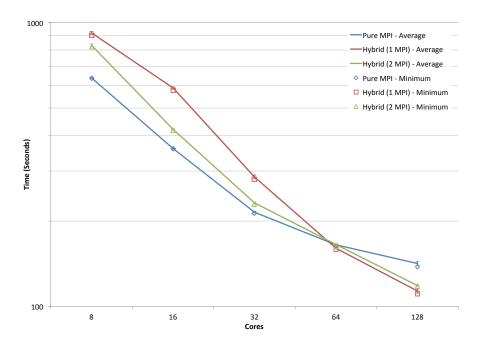

- Chapter 5 describes the contribution arising from creating and testing a hybrid version of the real world application DL\_Poly, extending the conclusions from the previous chapter to see how they apply to a larger scale code with a more complicated communication pattern. It follows a similar pattern to the previous chapter, beginning by introducing the code in Section 5.1, describing the general structure and the creation of the hybrid version. It then presents overall results of a performance comparison of the pure message passing and the hybrid message passing + shared memory versions of the code in Section 5.3. This overall discussion is again extended to look in detail at the performance differences between the two types of code. This second application is written in Fortran and is much larger in scale, containing more complicated communication patterns and increased

1.4 Thesis Structure 7

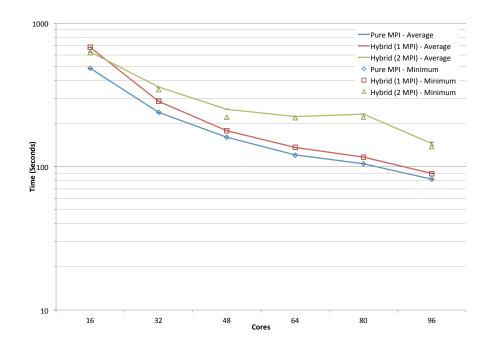

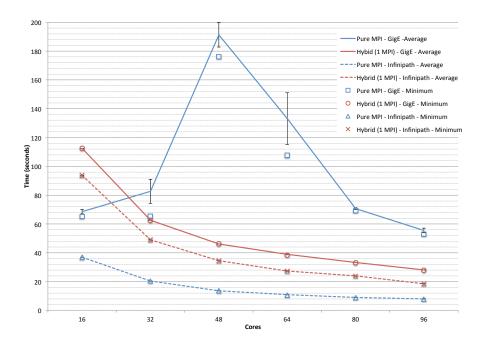

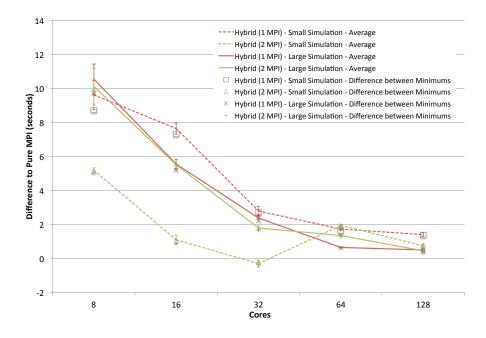

amounts of collective communication. The hybrid version of this code shows that hybridisation of existing large scale applications can also deliver performance gains, this time obtaining better performance than the pure message passing code at large processor numbers over a fast Infiniband interconnect. However, the performance of the pure message passing code is still better than the hybrid message passing + shared memory code on low numbers of processors.

- Chapter 6 gathers the main performance results from the analysis of the two hybrid codes and examines the factors affecting performance of the hybrid message passing + shared memory and pure message passing codes. It introduces and examines performance models which describe the behaviour of these codes, enabling an analytical understanding of the code performance. These results are generalised to the differences between the pure message passing model and hybrid message passing + shared memory models allowing prediction of performance of other similar parallel applications on current and future hardware.

- Chapter 7 presents the conclusions of the work, drawing together the findings from the

previous chapters, and in Section 7.6 it highlights future directions for this avenue of

research.

#### 1.4.1 Small Scale MD Code

The work presented in Chapter 4 investigates the performance of a hybrid molecular dynamics application and compares the performance of the application to the same code parallelised using pure MPI. Much of the work in this chapter has been published as [32]:

• M.J. Chorley, D.W. Walker, M.F. Guest (2009), Hybrid Message-Passing and Shared-Memory Programming in a Molecular Dynamics Application On Multicore Clusters, 196-211. In International Journal of High Performance Computing Applications 23 (3).

doi:10.1177/1094342009106188

8 1.4 Thesis Structure

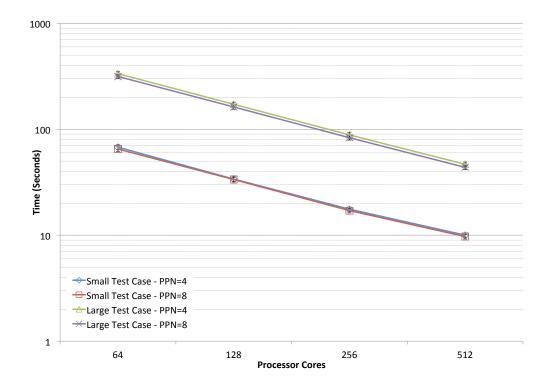

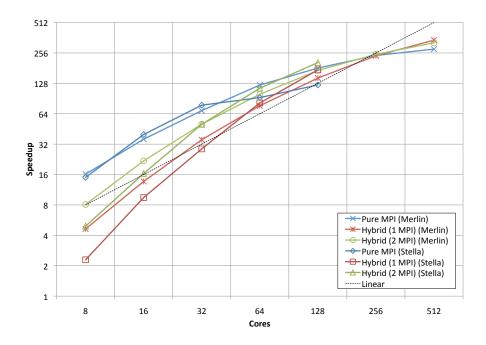

In this chapter the performance of both versions of the code is considered on two high-end multicore systems, and the effect that the choice of interconnection fabric has on the performance of a pure MPI code compared with a hybrid MPI and OpenMP code is discussed, examining both high-end HPC Infiniband and Infinipath interconnects and a lower performance 1 Gigabit Ethernet connection.

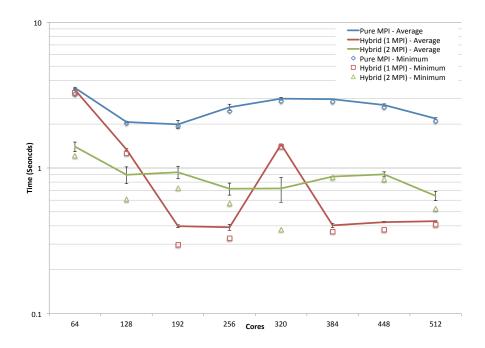

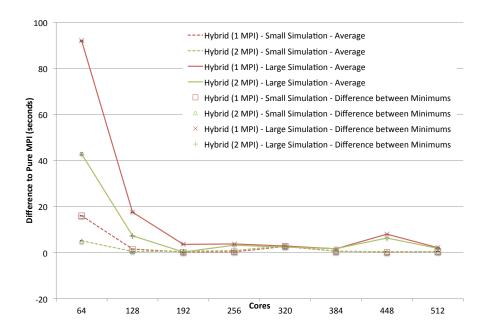

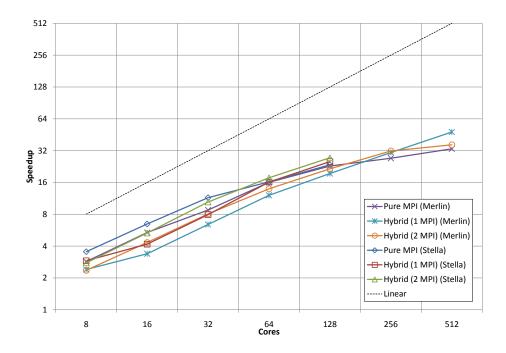

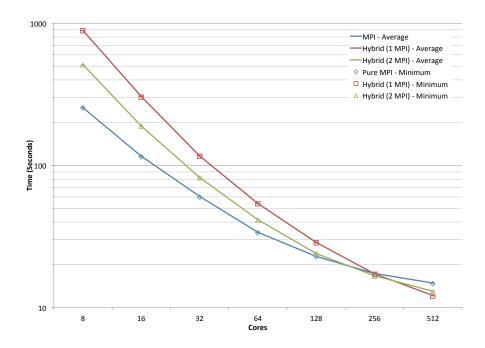

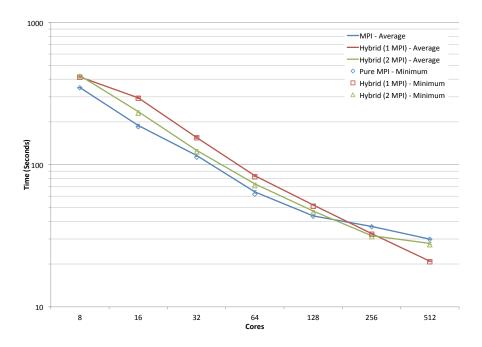

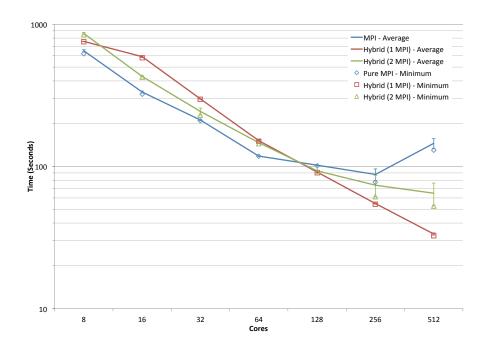

The pure MPI code is found to perform better than the hybrid code on higher end Infiniband and Infinipath connections and at lower processor numbers on the Gigabit Ethernet connection. However, at higher processor numbers on the standard 1 Gigabit Ethernet connection the hybrid model has the better performance.

#### 1.4.2 Real World MD Application

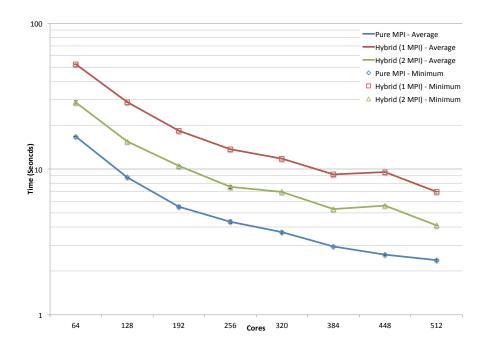

The work presented in Chapter 5 examines the performance of a large scale hybrid molecular dynamics application, again comparing the performance with a pure MPI version of the code.

This chapter has been published in an edited form as [31]:

M.J.Chorley and D.W.Walker (2010), Performance Analysis of a Hybrid MPI/OpenMP Application on Multi-core Clusters. In Journal of Computational Science, 1 (3). doi: 10.1016/j.jocs.2010.05.001.

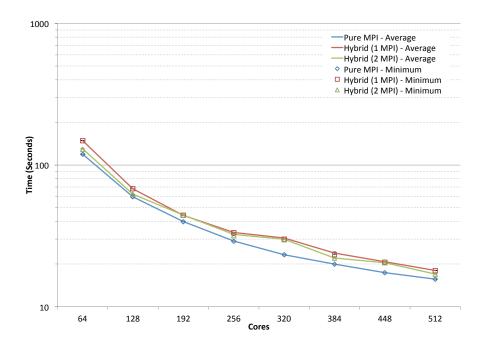

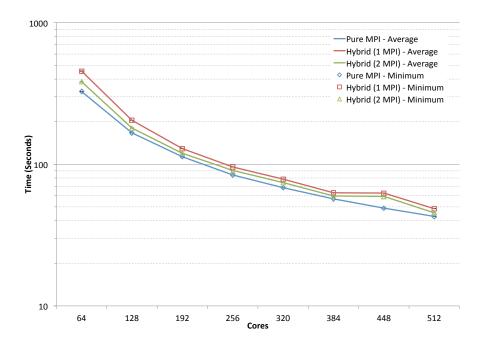

The performance of the hybrid DL\_Poly application is considered on two multi-core systems: one utilising an Infiniband connection, the other utilising a 10 Gigabit Ethernet connection.

With this large scale MD code the pure MPI version is again found to provide the better performance at low processor numbers. However, at higher processor numbers the hybrid message passing + shared memory code performs better on both the 10 Gigabit Ethernet and the lower latency higher bandwidth Infiniband connection.

1.4 Thesis Structure

#### 1.4.3 Performance Analysis

The work presented in Chapter 6 aims to analytically describe the performance differences observed between the hybrid and pure MPI codes, generalising results so that suggestions may be made about the performance of the model on future generations of hardware.

## **Summary**

This chapter has introduced the thesis topic, and the motivation for the work carried out in the dissertation. It has described the aims and contributions of the thesis, as well as the thesis structure. The following chapter will examine the background to the work contained in the thesis.

1.4 Thesis Structure

# **Chapter 2**

# **Background**

#### **Overview**

This chapter discusses the background topics and previous work in HPC relevant to the research presented in this thesis.

It begins in Section 2.1 by discussing some basic theory of programming an application in parallel, before then introducing the two dominant styles of parallel programming in HPC: Message Passing (MP) programming and Shared Memory (SM) programming. The *de facto* standards for these programming styles, MPI [84] and OpenMP [92], are then introduced and compared, with the advantages and disadvantages of both explored.

Section 2.2 then discusses issues surrounding multi-core clusters and HPC hardware. Reference is made to typical HPC interconnection networks used in clusters, with particular focus on the interconnects found in the multi-core clusters used in this work: 1 and 10 Gigabit Ethernet, Infiniband and Infinipath. Multi-core processor technology is examined, and the differences between multi-core and Symmetric Multi Processing (SMP) hardware are shown.

Combining message passing and shared memory programming models to create hybrid message passing + shared memory code is then examined along with previous work on the subject in Section 2.3. Previous work on the use of the model on clusters of both SMP hardware and multi-core nodes is examined with reference to the relevance of the work to this thesis.

Issues pertaining to the performance modelling of parallel code are discussed in Section 2.4,

1.4 Thesis Structure

with particular reference to the modelling of message passing communication.

Finally Molecular Dynamics codes are introduced in Section 2.5, with the typical structure of such codes presented.

## 2.1 Parallel Programming

In order to understand the operation of the applications used in this thesis it is necessary to introduce some basic concepts of parallel programming. Parallel programming is the term used to describe the process of writing an application that may be run on more than one processor. The aim is that by increasing the number of processors working on completing a specific task the time taken to complete this task will be reduced, as portions of the application can be executed in parallel with one another.

When implementing an application in parallel, the application must be broken down so that separate portions may be executed at the same time. This may be done via task parallelism in which the separate tasks undertaken by the application are executed concurrently, or it may be done via data parallelism in which the data to be operated on is broken into separate sections and each section of data is operated on at the same time. The data parallelism style of programming is "the most common strategy for scientific programs on parallel machines" [41]. Scientific applications frequently operate on large domains of data, and the separation of this data into distinct parts is an efficient way of allowing the application to run in parallel. The applications examined in this thesis all use the data parallelism strategy, so this is introduced next.

#### 2.1.1 Data Parallelism

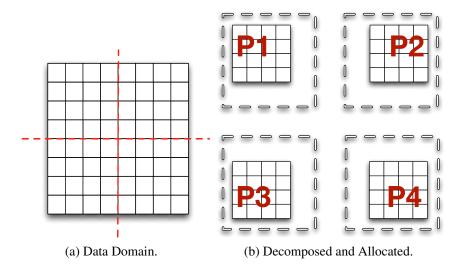

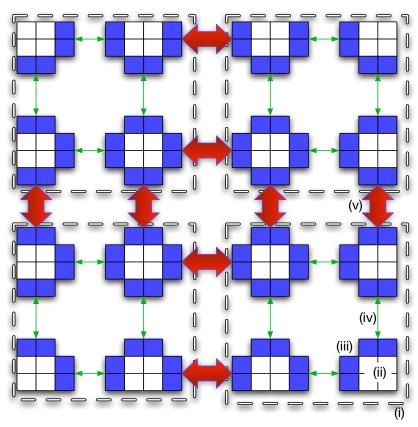

The data parallelism style of parallel programming is concerned with dividing the data domain of an application into smaller sub-domains, each of which may be operated on at the same time by a separate processor, as illustrated in Figure 2.1, in which a data domain, (here a set of cells to be processed, 2.1a) is divided into sections and allocated to four separate processors, P1, P2, P3 and P4 (2.1b).

Often a processor will need to read data from the neighbouring sub-domains in order to correctly calculate results within its own sub-domain. A data-parallel decomposition strategy will therefore often involve some form of communication between individual processors so that

Figure 2.1: Domain Decomposition - a domain of cells is divided into sub-domains, each of which is assigned to an individual processor.

they may have access to all the data required to perform their task. The data from neighbouring processors will need to be kept up-to-date, so multiple communications between processors may be needed as the application runs. In addition to this swapping of data between individual processors during a run of an application, there may also be times when all processors need to communicate as a group in order to calculate some global statistic, or synchronise some value. In this case there are many strategies to communicate data globally. For example, a value may be reduced to one process which then broadcasts the new value to all other processes, or all processes may simultaneously communicate with each other. Both 'point-to-point' and 'collective communication' are discussed further in Section 2.1.3.

The communication between processors in the parallel application may be either explicit via message passing, or implicit via shared memory, as described in the next section. This results in differences in implementation details but the overall parallel strategy remains the same. In a message passing implementation each processor will maintain its own copy of the data that surrounds its own subdomain but which resides on neighbouring processes. This data is usually termed 'halo data'. This halo data will need to be updated through explicit message passing as the simulation progresses. In a shared memory implementation, each processor will access the halo data it requires through direct access to the memory required, so there is no explicit

communication.

A parallel application using the data parallelism strategy will usually exhibit a regular sequence of behaviour, where each processor performs calculations on some data, communicates updated data to its neighbours and receives updated data itself, then performs more calculations on its data. This pattern of a calculation phase followed by a communication phase is commonly seen in parallel applications, including those used in this research.

#### 2.1.2 Message Passing and Shared Memory Programming

"For the past decade, those developers who have focused on workstation and SMP solutions have threaded their programs, while those interested in supercomputing solutions have switched from vector to message passed programming" [74].

HPC has in recent years been dominated by two styles of implementing a parallel application: Message Passing (MP) and Shared Memory (SM) programming, each of which is closely related to a different class of parallel hardware.

- Message Passing programming is associated with Distributed Memory (DM) machines,

where independent nodes are linked together via a communication network (a cluster

architecture). In this scenario separate processes are run in parallel on each node or

processor and use explicit communication through messages in order to coordinate their

work.

- 2. Shared Memory programming is closely associated with Shared Memory (SM) machines, where several processors within the same logical system share access to a memory space. This scenario typically involves using threading within an application, and communication between threads is implicit. Threads primarily access those portions of the shared memory relevant to themselves, but also have access to the shared memory 'belonging' to the other threads, allowing synchronisation and coordination of the parallel task.

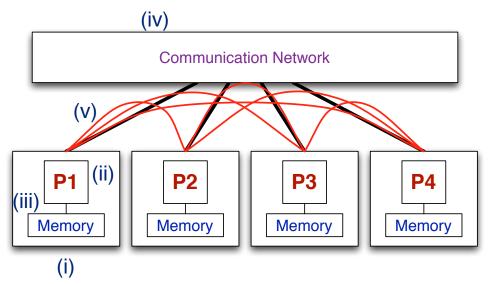

(a) Distributed Memory - individual processors within nodes communicate through explicit messages over a communication network.

(b) Shared Memory - individual processors access the same shared memory space, allowing implicit communication.

Figure 2.2: Distributed Memory and Shared Memory.

The two styles of programming and the hardware with which they are closely associated are illustrated in Figure 2.2. Firstly, Figure 2.2a shows an example of distributed memory hardware, in which individual nodes (i), each containing a processor (ii) and local memory (iii) are connected together via a communication network (iv). In order to communicate, the processes running on each node send explicit messages (v) to each other through the communication network. Figure 2.2b shows an example of shared memory hardware (i), in which individual processors (ii) are connected to a large shared memory (iii) via a shared bus connection (iv).

Communication is carried out implicitly, as a thread running on one processor will have access to the data it requires in the shared memory space (v).

The *de facto* standards for programming in Message Passing and Shared Memory styles in HPC are MPI [84] and OpenMP [92], as introduced in the following sections. Both have become dominant in their areas, although other alternatives are available. Global Arrays [89, 88] can be used to provide shared memory constructs across distributed memory clusters, providing for concepts such as single sided communication (where only one process is explicitly involved in communication) and for large arrays of data to be shared between remote processes. Unified Parallel C (UPC) [114] offers a similar ability to carry out shared memory threading over distributed memory hardware. Shared memory programming may also be accomplished using threading libraries such as Posix threads (pThreads)[85], or Intel Threaded Building Blocks (TBB)[94]. Some take issue with the use of libraries for threading however: [16] suggests that the approach taken by pThreads in implementing threads in a library is not ideal, as issues concerning under-specification of behaviour lead to correctness depending on the implementation specifics. A further option for running shared memory code on distributed memory clusters may be automatic translation from OpenMP code to MPI [13].

#### 2.1.3 MPI

"Message Passing Interface (MPI) is a widely accepted standard for writing message passing programs." [68]

The Message Passing Interface (MPI) standard [84] defines a set of library routines and data types that can be used to implement the Message Passing style of parallel programming within an application. Use of the standard is widespread throughout HPC and many parallel codes use it to enable their parallel operation. The standard specifies the routines that should be available within an MPI implementation, their behaviour as part of a parallel application, and the data types that may be used between MPI processes, but does not go into detail about the

implementation. Thus it does not matter how an MPI library implements the communication, merely that it behaves as the standard requires.

MPI usage is fairly straightforward and follows a similar outline pattern in most parallel applications. Basic initialisation of a set of MPI processes and the associated MPI environment is done through a call to the MPI\_Init routine within the application code; this routine must be called before any other MPI routines are used. This initialisation method sets up the default MPI communicator MPI\_COMM\_WORLD, which contains the context for the set of processes running in the parallel application. Each process within the communicator is assigned a unique identifying 'rank' number that can be used to identify processes within MPI routines. The initial call to MPI\_Init is matched by an MPI\_Finalize call at the end of the application code, which closes down the MPI environment, and after which no MPI routines may be used. Between these two calls, application code may call other methods from the MPI library to carry out message passing communication between processes.

There are two main classes of communication defined by the MPI standard which are relevant to this work: Point-to-Point and Collective communication.

Point-to-Point communication involves one process sending data to one other receiving process. This may be achieved in the simplest case through the use of MPI\_Send and MPI\_Recv calls. The sending process will initiate an MPI\_Send call, specifying parameters such as the data to be sent and the rank of the destination process. The receiving process will call the MPI\_Recv method to receive this data, specifying the maximum amount of data it can receive, and the rank of the sending process it is expecting to receive data from. This is the simplest type of point-to-point communication, although other routines are available to provide for synchronous/asynchronous and blocking/non-blocking communication.

Collective communication typically involves all processes within a parallel application communicating simultaneously. This may be done to broadcast a value to all processes (using MPI\_Bcast for example) or to reduce a value (using MPI\_Allreduce for instance) across all running processes. Global communication may also be used to synchronise processes using

a call to MPI\_Barrier. It is worth noting that most collective communication is expensive in terms of communication time, as all processes will need to be synchronised in order to carry out the communication, and imbalance between the running time of the processes will cause a hold up to all other processes. For example, as [76] says: "The complete data exchange collective, MPI\_Alltoall is one of the most intensive communication patterns used" [76]. The expense (in terms of performance) of collective communication leads to a desire to reduce its usage within parallel message passing applications.

It is worth noting the differences between point-to-point and collective communication as they apply to the requirements of HPC interconnects: "collective communication requirements are strongly differentiated from point-to-point requirements. Collective communication ... tended to involve very small messages that are primarily latency bound. As the numbers of cores increases, the importance of these fine-grained, smaller-than-cache-line sized collective synchronisation constructs will likely increase." [9]. So, although collective communication in general involves small messages that do not require much bandwidth to transmit, they are bound by the latency of the connection - that is the ability for the interconnect to setup a connection from one process to another. As the number of MPI processes involved in a collective communication increases, this can have a significant effect on performance. This is an important factor even as interconnects improve, as "latency is likely to improve much more slowly than bandwidth" [9]. This indicates that as the number of processing cores per node increases, the performance of collective communication is likely to worsen, if connection latency does not also improve. For point-to-point communication however, latency is less of an issue: "The sizes of most point-to-point messages are typically large enough that they remain strongly bandwidth bound, even for on-chip interconnects" [9]. This means that for most pointto-point messages the latency of the interconnect is not as important, rather it is the bandwidth of the connection between processes which has the larger effect on performance.

While MPI specifies many other types of communication such as Single Sided Communication and Parallel Input/Output, these are not discussed here as they are not relevant to the work presented within this thesis.

An important issue when using MPI in a hybrid code is that of thread safety, and the behaviour of MPI library calls when called from within a multi-threaded environment. The MPI standard defines an initialisation method (MPI\_Init\_thread) for specifying the level of thread support required, allowing application programmers to explicitly request that an implementation behave in a thread safe manner. There is no guarantee however that an implementation will actually provide this level of support. Much work has already been done examining the issues of multi-threading and MPI. In [113] a test suite is described for evaluating the performance of multi-threaded MPI communication, looking at the specific case of MPI communication in hybrid message passing + shared memory codes, where MPI calls may be made from different threads. It notes that while there are overheads associated with maintaining thread safety, a slow interconnect "such as GigabitEthernet masks some of these overheads" [113], highlighting that slower data transfer may hide the increased overheads of ensuring thread safety. Although this indicates that a slower interconnect may actually be a benefit in some cases when using a hybrid message passing + shared memory model, it does suggest that when using a faster interconnect the overheads of ensuring thread safety will be exposed in the code performance, which could be a significant disadvantage of the model. Both [50] and [11] examine how the MPI standard relates to thread safety issues, again finding that requiring thread safety adds extra overheads to MPI operations. However, both papers ([50] and [11]) present discussions on limiting these overheads and reducing their impact within message passing code, suggesting that it is possible to do this. It is worth noting that the application codes examined in this thesis do not require MPI calls to be made from within different threads, so theoretically they do not explicitly require a thread safe MPI implementation to operate correctly. However in practice they do actually need the MPI implementation to support multithreaded environments to enable correct operation, as some implementations will restrict the spawning of shared memory threads if explicit multithreading support is not requested by the programmer.

MPI is designed primarily for distributed memory systems where each node contains a single processor. On multi-core systems, "many scientific applications today are written in MPI using a one-process-per-core model that partitions memory among the cores" [39]. This is the most

natural progression when taking a pure MPI application onto a multi-core system, requiring no changes to the application, and treating the multi-core node exactly the same as a collection of single core nodes.

Although MPI is designed for implementing a Message Passing style of programming with processes communicating through some type of networking interconnect, on systems where shared memory nodes are available many MPI implementations will actually use communication through the shared memory for intra-node communication. When MPI is able to use direct shared memory access within a compute node to carry out communications, performance can be dramatically improved [18] as the communication will not need to be transferred over the network interconnect, removing the overheads of both establishing a connection and transmitting the data.

There are many MPI implementations available: among the most popular are MPICH [49] and OpenMPI [47]. The MPICH implementation of the MPI standard is the basis for many vendor specific MPI implementations [17, 64], which may include further fine tuning and performance enhancements specific to vendor hardware. As implementation details vary from implementation to implementation, performance differences may be observed when using the same application with different MPI libraries [38]. Communication time is in fact dependent on many software and hardware parameters [78], which can make the tuning and understanding of performance issues a difficult task.

#### **Advantages**

"explicit parallelism often provides a better performance and a number of optimised collective communication routines are available for optimal efficiency. Data placement problems are rarely observed and synchronisation occurs implicitly with subroutine calls and hence is minimised naturally" [104].

MPI has many advantages that have made it the *de facto* standard for message passing programming on HPC clusters. The specification defines interfaces for both C and Fortran,

two of the most widely used languages in HPC. The specification itself provides a large number of message calls to suit particular needs, covering synchronous and asynchronous communication, blocking and non-blocking sends and receives, single-sided communication, parallel IO, separate or joined send and receive calls and synchronisation constructs such as broadcast, reduce and all\_to\_all. A large number of parameters for each message routine allow fine grained control over communication between processes.

As stated above from [104], MPI implementations are optimised for typical operations, and the style of message passing programming naturally leads to a more efficient style of programming with regard to synchronisation.

The advantages of the MPI specification itself have led to further advantages that stem from the dominance of MPI within the HPC ecosystem. Because of its wide use in the scientific computing community it is supported well on HPC clusters by hardware vendors, compilers and systems support staff. As a widely used specification there is a large knowledge base in the community to rely on when coding, testing and running MPI codes. The performance problems are mainly well understood, and for many tasks there is already a best practice to utilise MPI to solve a problem. MPI is now well supported by code profiling tools and debuggers, aiding in the coding process. The separation of communication routines from computation allows both to be optimised independently of one another [98].

#### **Disadvantages**

One of the immediate drawbacks of MPI is that it presents the novice programmer with a steep learning curve in order to parallelise a code. Much of the parallelisation work must be done by the programmer, who is responsible for the whole process of work sharing, from the division and sharing of data across the processes to the synchronisation and gathering of results. "MPI has evolved as the dominant library, but enormous, assembly-language style effort is required to develop MPI programs" [74]. The amount of control given to the application programmer by its low-level approach is also a disadvantage, as it makes the library more complicated and

prone to errors.

When moving from an existing sequential application to a parallel application it may be hard to relate the resultant parallel application to the sequential version: "[a]n arbitrary MPI program may not have much resemblance to a sequential program from which it was derived" [74]. Significant effort may be required in order to re-purpose a parallel application to use MPI, as the library "typically requires a thorough (re-) design of a parallel application" [21].

Explicit communication adds overheads to the running of the application, and as already discussed, collective communication can be very time consuming indeed. There is also an issue that "[d]ecomposition, development and debugging of applications can be time consuming and significant code changes are often required." [104].

#### **Data Decomposition and Message Passing**

In order to understand how the applications used in this thesis communicate data, and how that relates to the performance of both the pure message passing and hybrid shared memory + message passing models, it is necessary to explain the typical methods of decomposition and communication of data within a message passing application using a data parallel model.

Given a 2 dimensional domain of data, with width w and height h, and a 2 dimensional mesh of processors with width x and height y it is clear that when this is decomposed over the processors being used to run the application, each processor will end up with a subdomain of approximately  $\frac{w}{x} \times \frac{h}{y}$ , provided that the domain may be decomposed so that  $\frac{w}{x}$  and  $\frac{h}{y}$  make sense within the logic of the application. If the domain sizes are multiples of the processor mesh sizes, this is usually not an issue.

Similarly for a 3 dimensional decomposition, if the data domain has width w, height h and depth d, and it is decomposed onto a 3 dimensional mesh of processors of width x, height y and depth z, then each processor will have a subdomain of data of dimension approximately  $\frac{w}{x} \times \frac{h}{y} \times \frac{d}{z}$ .

When carrying out a data decomposition within a parallel application written in a message

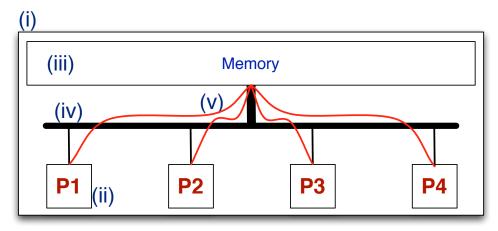

Figure 2.3: Data Required from Neighbour Processes - P5 requires knowledge of the data belonging to the subdomains on the neighbouring processes in order to complete the work for its own subdomain.

passing style, it is important to ensure that each process has access to the data it needs during the application run. This accessing of data belonging to other processors is shown in Figure 2.3, simplified to the two dimensional case. Here, in order to carry out its work, processor P5 needs the neighbouring data in the cells (highlighted in blue) belonging to the other 8 processors P1, P2, P3, P4, P6, P7, P8 and P9. This data will also need to be kept loosely coherent as the application progresses, so that it is current at the points in the algorithm where it is needed. Each processor will keep a local copy of the data from its neighbours (halo data), and this will be updated periodically throughout the application run.

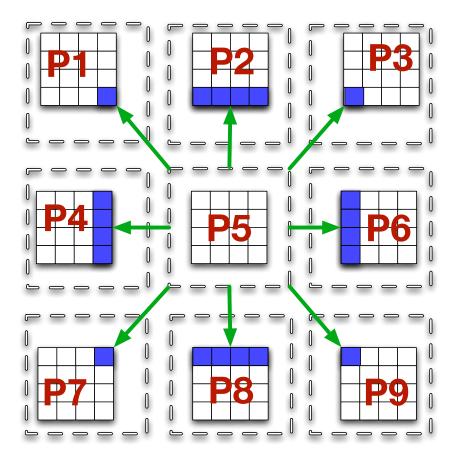

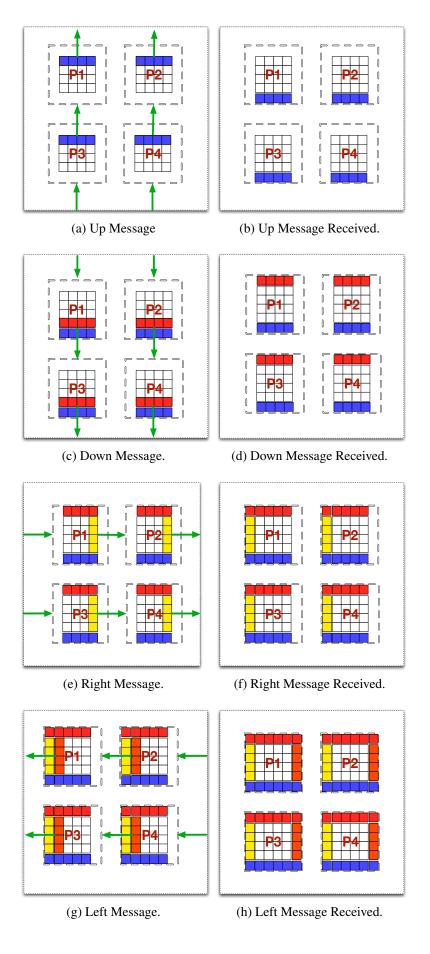

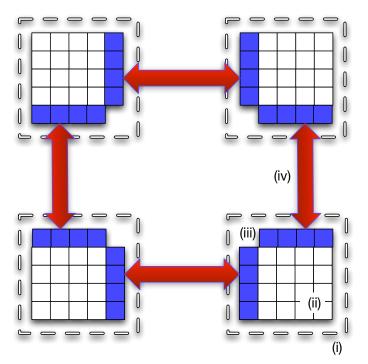

The updating of required data follows a simple pattern. Sets of messages are exchanged, with all processes communicating in the same direction at the same time, enabling all data to be updated with a minimum of communication. This process is illustrated in Figure 2.4. Here, processes communicate data in four separate phases in order to ensure that each process has an

up to date copy of the halo data it requires. Firstly, each process sends data from its top most boundary up to the receiving process above (Figure 2.4a) resulting in each process having a copy of the boundary data from the process below (Figure 2.4b). The second phase involves similar communication, this time in the down direction (Figure 2.4c), resulting in each process having a halo copy of the data from both the process above and the process below (Figure 2.4d). Data is then sent from each process to the process to its right. This time however, as well as the boundary data from the process' right most edge, data from the rightmost edge of the upper and lower halo data is also sent (Figure 2.4e). This enables each process to have not just the data for the left halo copy, but also for the upper and lower left corners (Figure 2.4f). This process is then carried out again, in the left direction (Figure 2.4g), finally ending with all processes having a copy of all the halo data they require, from the processes above and below, to the left and the right, and from the upper and lower left and right corners (Figure 2.4h).

This describes the simplified two dimensional case, but the same process occurs for a three dimensional decomposition. A three dimensional decomposition will have an extra set of messages for communicating data in the extra dimension.

Communication between processes when carrying out updates of halo data in three dimensions can be described in terms of the size of their subdomains. If a process has a subdomain of width  $sd_w$ , height of  $sd_h$  and depth of  $sd_d$ , and a halo depth of  $h_d$ , and it follows the procedure above for communicating and updating halo data, then the following holds:

- 1. A process can first send data to the processors to the left and right of itself, sending a halo of size  $(sd_h \times sd_d) \times h_d$ , while also receiving the same size of halo from the neighbouring processors.

- 2. It can then send data to the up/down neighbours, comprising its own halo of size  $sd_w \times sd_h$ , plus a portion of the left/right halo data it received from the left/right neighbours, giving a total size of  $(sd_w \times sd_h + (2 \times h_d \times sd_h)) \times h_d$ . As before, it also receives this amount of data from its up/down neighbours.

Figure 2.4: Data Parallelism - Halo Data Communication.

3. Finally it may send data to the north/south neighbour processors. This message comprises a halo of its own data of size  $sd_w \times sd_d$  plus additional data from the two sets of halos it has already received, giving a total message size of  $(sd_w + 2 \times h_d) \times (sd_d + 2 \times h_d) \times h_d$ .

These three steps, comprising six distinct messages, will ensure that each processor has a copy of the correct halo data it needs to carry out calculations on its own subdomain.

# 2.1.4 OpenMP

"OpenMP is probably the most commonly used communication standard for shared-memory based parallel computing" [21]. "OpenMP is becoming the standard programming model for shared memory parallel architectures" [45].

The OpenMP Application Programming Interface (API) [92] defines a set of library routines and compiler directives that facilitate parallelisation on shared memory systems using threading. A newer standard than MPI, it specifies some library routines for general tasks (such as discovering the number of threads in a parallel application) but relies primarily on compiler directives to parallelise a code. These directives are translated at compile time into parallel code by a compatible compiler, which will produce the threaded application code. It is now a widely accepted standard for "annotating programs for parallel executions" [66]. The bulk of directives (in OpenMP 2.0) are related to work sharing constructs and synchronisation.

In order to use OpenMP the programmer specifies which sections of the code should be carried out in parallel through the declaration of parallel regions, using the omp parallel and omp end parallel directives. Within these regions, the programmer can then specify the distribution of work via constructs such as the sharing of iterations in a loop (using an omp for directive), or (if using OpenMP 3.0) the specification of tasks that may be carried out concurrently. Data access may be controlled also, allowing variables to be declared as private to a thread or shared between all threads. Other constructs allow for the synchronisation of threads at barriers (omp barrier), and for other useful operations such as the copying in of data

values to a parallel region, or the reduction of values across a group of threads. OpenMP also allows nested parallelism (i.e. threads spawned from within other threads, which may match underlying hierarchical architecture features in multi-core systems), but the performance may be reduced using this style [37].

As with MPI, the use of OpenMP introduces overheads to a parallel code. In contrast to MPI, these overheads are not generally explicitly incurred through calls to external libraries, rather they are inherent within the operation of the shared memory threading. Many operations will be carried out as part of the parallel operation of the code which will consume run time. Threads must be forked and joined at the start and end of each parallel region. Synchronisation may also need to be carried out while an application is running, as may reduction of global variables. Some shared memory related constructs such as locking of variables for atomic updates can be very expensive in terms of runtime. Various systems and toolkits exist to characterise these overheads caused by OpenMP, such as CLOMP [19] or the EPCC micro-benchmarks [22].

While OpenMP is designed primarily for shared memory hardware, distributed shared memory versions do exist, but these do not provide the same level of performance as pure MPI on distributed memory hardware [19].

#### **Advantages**

A clear advantage of OpenMP is its high level nature which makes it much easier to perform simple parallelisation of a code [75]. The low level implementation is done by the compiler; this allows the programmer to specify *what* to parallelise, without having to specify exactly *how* it is parallelised. The API defines a large range of directives and routines to use in a parallel code, allowing a vast range of codes to use OpenMP for parallelisation. The API defines the exact behaviour of routines and directives in both C and Fortran, appealing to the wide C and Fortran code base already in use in HPC. The ease of use is pointed out in [21]: "OpenMP ... can be easily adapted to existing sequential software".

Simple parallelisation of code using OpenMP is much more straightforward than using MPI,

with far less programming effort required. OpenMP is also overall much easier to use than 'hand-threading' using pThreads [75]. Code parallelised using OpenMP can be easily made sequential by simply turning off the OpenMP compilation option.

Many tools exist for debugging OpenMP, and the nature of the shared memory threading makes it easier to debug and tune than a distributed application [75] such as one using MPI, or a shared memory application using pThreads or similar mechanisms. [74] has found that: "OpenMP performance profiling can be done more easily than for performance profiling of a program making manual calls to a threads library", and that for OpenMP: "current tools can very accurately locate threading correctness problems" [74]. These examples point to the advantage OpenMP applications have over distributed MPI based applications when debugging and maintaining application code.

OpenMP also has some speed advantages; on some architectures, OpenMP barriers are faster than the equivalent MPI barriers, and broadcasting data can also be much faster [60].

#### **Disadvantages**

Although simple parallelisation is very straightforward with OpenMP, it can be much harder to get very good performance when a more complicated strategy is required. It may also be hard to debug problems such as false sharing caused by an incorrect parallelisation strategy. The shared memory model is only scalable as far as the shared memory hardware, and this disadvantage is carried into OpenMP. The knowledge base for OpenMP among the HPC community, while growing, is still smaller than that of MPI. Additionally there may be performance problems caused by OpenMP itself. Synchronisation of OpenMP threads may cause issues relating to cache that may slow down an application [98], and furthermore OpenMP may have performance problems on cache-coherent Non Uniform Memory Access (ccNUMA) hardware [20]. The use of OpenMP during compilation may stop the compiler carrying out certain loop optimisations which may affect code performance [52].

30 2.2 Multi-core Clusters

# 2.1.5 MPI vs. OpenMP

Understanding how MPI and OpenMP compare in terms of performance is an issue frequently discussed in the literature. Much comparison of MPI and OpenMP has been done (e.g [27, 15, 8]), with no real consensus reachable as to the better model to use. In any given situation, best performance is dependent on many factors, most importantly the hardware and algorithms under consideration.

# 2.2 Multi-core Clusters

"Commodity off the shelf (COTS) clusters, driven in the mid-1990s by Beowulf clusters, have grown in popularity and performance as microprocessor-based clusters have been enhanced by architectural ideas that were pioneered by earlier custom systems" [74].

Clusters are "perhaps more widely used than any other type of parallel computer because of their low cost, flexibility, and accessibility" [43].

As [43] and [74] highlight, a significant trend within the HPC community over recent years has been away a move away from large Massively Parallel Processing (MPP) machines based on proprietary chip technology and software, and a move towards clusters of standard PCs or workstations using off-the-shelf components and open source software. This cluster architecture has come to dominate the field: the June 2010 Top500 ranking<sup>1</sup> of the world's supercomputers shows that 424 are classed as having a cluster architecture, whereas the November 2002 list shows just 81 clusters in the Top500. The increased availability and decreased cost of commodity-off-the-shelf (COTS) hardware and software means that clusters are also gaining in popularity in smaller computing centres and research departments as well as the larger centres that tend to feature in the Top500 list. The introduction of multi-core processors has enabled

<sup>&</sup>lt;sup>1</sup>http://www.top500.org

2.2 Multi-core Clusters 31

a significant trend towards clusters with many thousands of processing cores. The machines in the upper reaches of the Top500 list now contain not just tens of thousands but hundreds of thousands of processor cores per system. As multicore chips become more widespread there is a growing need to understand how to efficiently harness the power available within these systems.

These clusters are normally built from 'standard' hardware. 'Nodes' containing one or more processors, along with local memory and (optionally) some local storage are linked through one or more networks. These nodes are typically built from commodity components, usually many-socket motherboards primarily designed for the rack-mounted server market, coupled with commodity processors, memory and hard drives. Many clusters include dedicated high-speed networks such as Infiniband for communication between nodes and network file storage access, while also containing slower networks such as Gigabit Ethernet for tasks such as cluster management.

Not only is the cluster now the dominant HPC architecture, but "almost all current high performance computing systems now contain nodes which consist of shared memory multiprocessors" [23]. The vast majority of these shared memory multi-processor nodes will be multi-core processors. These multi-core clusters can have significant effects on the performance of codes: "application runtimes on large High-Performance Computing (HPC) systems with dual- or quad-core chips are slower when compared, core for core, with single-core chip performance" [103]. To compensate for the effects of multi-core processors on code performance may require making architectural changes to application code: "users should examine their codes and consider restructuring them to increase locality, increase intra-node communications, assign MPI ranks to promote spatial locality, use compiler optimizations and make other multicore aware changes" [103].

Recent advances, such as 64-bit architectures, multi-core and multi-threading processors [2] and software multi-threading [87], can all be used to benefit the scientific computing community. These technological advances are leading to the dividing lines between HPC architectures becoming blurred. As discussed, previous HPC architectures were generally divisible into

32 2.2 Multi-core Clusters

two classes: systems of distributed memory nodes in which each node is a processor with its own distinct memory, and systems in which nodes access a single shared memory (SMP's). Systems in which the nodes themselves are identical SMP systems introduce another level of complication, while the introduction of multi-core processors has yet further increased this complexity. As the number of processing cores within processors increases, individual nodes within a distributed memory cluster have become more like SMP machines, with large amounts of memory shared between multiple processing cores, while the overall cluster still retains the global characteristics of a distributed memory machine.

This results in HPC cluster architectures being more complicated, containing several levels of memory hierarchy across and within the cluster. In a multi-core cluster parallelism exists at the global level between the nodes of the cluster, and across the multiple processors and cores within a single node. At the global level, the memory of the cluster is seen as being distributed across many nodes. At the node level, the memory is shared between the processors and processor cores that are part of the same node. At the chip level, cache memory may be shared between some processing cores within a chip, but not others. This complex hierarchy of processing elements and memory sharing presents challenges to application developers that need to be overcome if the full processing power of the cluster is to be harnessed to achieve high efficiency.

## 2.2.1 Multi-core Processors

"Multicore architectures integrate multiple processing units into one chip to overcome the physical constraints of unicore architectures, and their exponentially growing power consumption" [110].

As it has become increasingly hard to pack more transistors into a single processor and increase the raw power of the chip, manufacturers have turned to putting multiple processor cores on one chip to increase performance. This has had a large effect on HPC: "Multi-core processors 2.2 Multi-core Clusters 33

are beginning to revolutionize the landscape of high-performance computing" [3]. The design of multi-core processors is hoped to "sustain performance growth while depending less on raw circuit speed" [3].

Much work has been done examining the effects of multi-core processors on the performance of scientific applications within HPC. Multi-core processors have many performance effects on codes, increasing performance of some, and decreasing the performance of others [102]. Much as with the discussion over which is best, OpenMP or MPI, the effect of multi-core processors on code performance is highly dependent on the class of application and algorithms being used.

There are significant architectural differences between single core and multi-core processors that can affect code performance. Memory access can be a problem due to the multiple levels of cache and memory access latency [110], as found in many studies: "cache and memory contention may prevent the multi-core system from achieving best performance, because two cores on the same chip share the same L2 cache and memory controller" [29]. In [103] it is agreed that "memory bandwidth contention is the single most important cause of multicore performance degradation" [103].

Attempts can be made to overcome the performance problems caused by multi-core processors, focusing on areas such as the intra and inter-node communication in an application, and the placement of processes or data within a node or across a cluster. Solutions such as "reducing network overhead by more logical process placement, updating or optimizing multi-node I/O, and working with more distributed and shared-memory programming models" [102] may help performance. Similarly, "overlapping working sets in threads running on cores sharing a cache can improve runtime" [93]. The importance of the communication on overall performance is highlighted: "intra-node communication is as important as optimizing internode communication in a multi-core cluster" [29]. These all serve to show that to get increased performance using multi-core processors is not as simple a task as simply deploying an existing parallel application on to a multi-core machine, but that significant engineering effort may be required to change the application structure and operation to gain best performance on a multi-

34 2.2 Multi-core Clusters

core cluster.

Despite the performance drawbacks and increased effort in engineering applications for multi-core systems, multi-processor systems may still exhibit larger performance improvements than single processor systems [70]. Awareness of cache affinity can have a significant effect on performance when using multi-processor multi-core systems, and multi-processor multi-core systems can increase application performance above the increase from multi-processor systems alone [70].

Some aspects of poor performance of applications on multi-core clusters are due to the processor designs themselves; multi-core processors "do not take advantage of the proximity between cores to improve synchronisation and communication between concurrent threads. Thread synchronization and communication instead use memory/cache interactions" [46]. This suggests that performance could be further improved if individual cores within a chip were able to directly communicate with one another, rather than requiring communication through the cache or memory.

Overall system design also has a part to play when multi-core processors are used. A cc-NUMA architecture may reveal performance problems: "it is hard to obtain high performance on the latter [cc-NUMA] architecture, particularly when large numbers of threads are involved" [30].

# 2.2.2 Multi-core Nodes vs. SMP Systems

"[P]rogrammers will not be able to consider these cores independently (i.e. multi-core is *not* "the new SMP") because they share on-chip resources in ways that separate processors do not" [42].

The distinction between SMP and multi-core systems is an important one. In an SMP system, a number of distinct physical processors access shared memory through a shared bus, with each processor having its own caches and connection to the bus. Multi-core processors however have several processing cores on the same physical chip. These processors will often share

2.2 Multi-core Clusters 35

cache at some level (L2 or L3) while having their own separate L1 caches. The cores often also share a connection to the bus. This cache sharing can have performance implications for parallel codes [4]. Cache sharing may introduce performance problems, as "access by a core to a memory block limits concurrent access to the same block by other cores" [3]. The increase in the numbers of cores causes issues with "data-locality, shared cache, bus contention and memory bandwidth limits ... due to increases in resource sharing" [4]. These problems with multi-core processors (as discussed in the previous section) can also occur with SMP systems, so while cache contention is not an issue in an SMP machine (as the processor cores do not share cache), there may still be issues related to shared bus access and memory bandwidth limits.

SMP systems typically suffer from a lack of scalability. There is an upper limit to the number of cores you can attach to a shared bus before the bandwidth constraints become a limiting factor. "In SMP's, contention due to the shared bus located between the processor's L2 cache and the shared main memory subsystem adds additional delay to the memory latency" [77]. There are solutions to this problem such as Non-Uniform Memory Access (NUMA) systems or cache-coherent Non-Uniform Memory Access (cc-NUMA) systems, where a global memory is partitioned between sets of processors, but these systems are still limited in scalability. SMP systems will normally contain a number of cores measured in the tens. One term used to describe such SMP nodes (with somewhere in the region of 16-128 cores) when used in a cluster system is a 'fat node'. These SMP nodes will typically have very large memories too, measured in the tens of gigabytes.

Nodes of a multi-core cluster will normally contain many fewer cores than SMP nodes. Current typical nodes may contain one or two dual or quad core processors (although hex-core is now a distinct possibility), so a node may have anywhere from 2 to 8 cores, and will usually have less memory than a large SMP node. These nodes are considered 'thin nodes', compared to the 'fat node' SMPs.

This distinction between multi-core nodes and traditional SMP systems obviously becomes harder to define as SMP systems start to contain multi-core processors, and multi-core

36 2.2 Multi-core Clusters

processors become many-core, with physical chips containing many tens of processing cores.

### 2.2.3 HPC Interconnects

"An important part of modern supercomputing platforms is the network interconnect" [72].

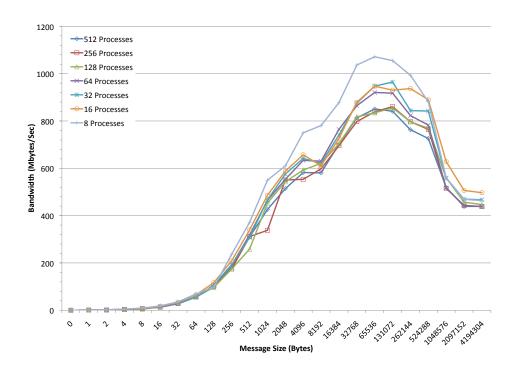

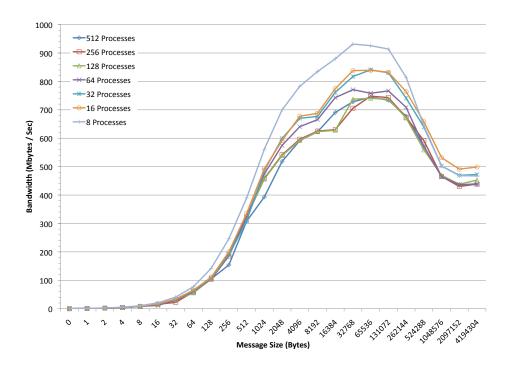

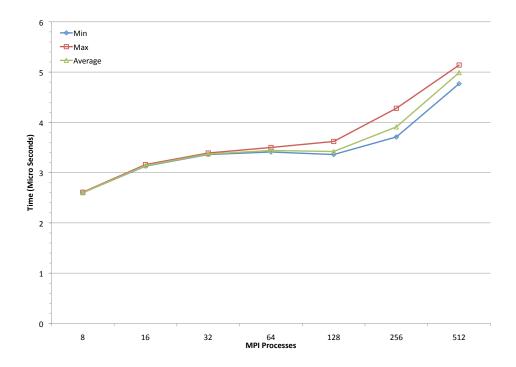

A major contributory factor to the performance of an HPC cluster is the performance of the interconnect used to connect nodes together. There are many types of interconnect in use today, ranging from low end 1 Gigabit Ethernet (GigE) through 10 Gigabit Ethernet (10GigE) and Infinipath connections to high end Infiniband interconnects, and performance of the different network interconnects is key to their adoption in modern HPC systems: "Modern interconnects such as Infiniband, Quadrics and Myrinet have become popular due to their low latency and increased performance over traditional Ethernet" [72]. Work has already been done comparing the performance of message passing communication such as MPI over these interconnects [79].

#### **Gigabit Ethernet**