# Novel MMIC Design Process Using Waveform Engineering

A thesis submitted to the University of Wales, Cardiff

In candidature for the degree of

**Doctor of Philosophy**

Ву

Dominic Michael FitzPatrick B.Sc., M.Sc.

Division of Electrical and Electronic Engineering

School of Engineering

Cardiff University

Wales

United Kingdom

October 2012

# **Summary**

It has always been the case that talented individuals with an innate understanding of their subject have been able to produce works of outstanding performance. The purpose of engineering science is to define ways in which such achievements can be made on a regular, predictable basis with a high degree of confidence in success.

Some tools, such as computers, have enabled an increase in speed and accuracy, whilst others have given a dramatic increase in the insight into the operation or behavior of materials; the electron microscope for instance. Still others have enabled the creation of devices on a scale unimaginable to our predecessors, Molecular Beam Epitaxy for example.

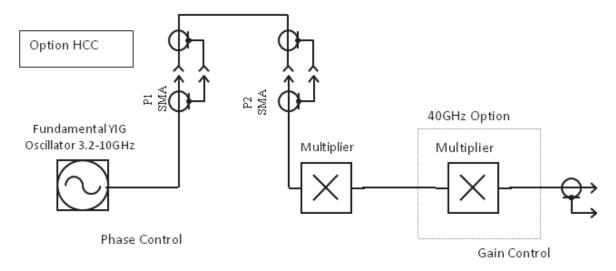

This work is the product of the availability of an understanding of complex theory on microwave transistor operation, significant increases in mathematical processing and data handling, and the assembly of a 'tool' that not only allows the measurement of high frequency waveforms, but their manipulation to simultaneously create the environments envisioned by the design engineer. It extends the operation of previous narrow band active load pull measurement systems to 40GHz and importantly facilitates the design of high efficiency modes at X band.

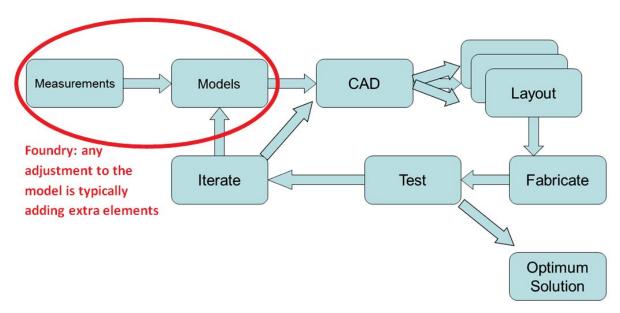

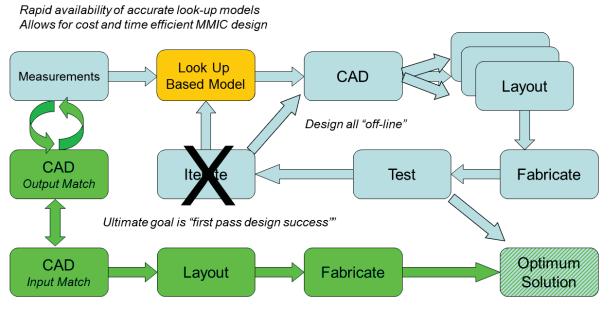

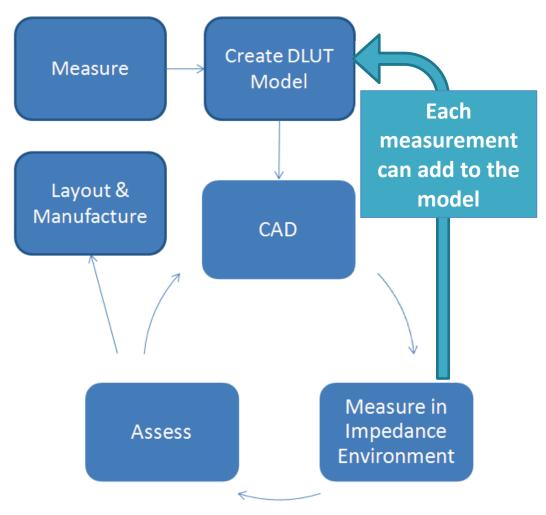

The main tenant of this work is to propose that rather than the linear approach of characterisation, design, test, re-iterate, that has been the standard approach to MMIC design to date, the first three stages should be integrated into a single approach which should obviate the need for design reiteration. The result of this approach should be better performance from amplifier designs, greater probability of success first time, and lower costs through less wafer real estate being consumed and fewer design 'spins'.

# **Acknowledgements**

This work would not have been possible without the help and support of a great many people, not only during my time at Cardiff University, but during my engineering career which led me to this point; my early mentors Mike Nunn and John Lillington being key amongst those engineers who set me along the particular path I have travelled. I would like to thank Professor Johannes Benedikt for suggesting and organizing my joining the research effort at the Centre for High Frequency Engineering and Professor Paul Tasker for his inspiration and insight that has driven the work forward at Cardiff. I have been privileged to work alongside and be greatly assisted by Dr. Jonathan Lees who has probably given me the most vital assistance over the years; whilst without the patience of Dr. Tudor Williams I wouldn't have cleared those first hurdles.

The work was sponsored and supported by the Defense Technology Centre and Selex Galileo and I am particularly grateful to Mervyn Haynes and Paul Robertson for their assistance throughout the course of the project. Key assistance has been provided by Malcolm Edwards and Taisto Tinttunen of AWR Corp particularly with incorporating the Cardiff Model DLUT into the MicroWave Office™ nonlinear simulation engine.

Returning to academia was a significant step and the experience was made all the more pleasant by colleagues at Cardiff; the cooperation and assistance offered by Professor Steve Cripps, Amir Sheik, Simon Woodington, and Randeep Saini amongst many others, is very much appreciated.

This work could not have been completed without the support of my family and so I leave my last and greatest thanks to my sons Nathan, Ben, Joel and Samuel and most especially my wife, Verena, without whom this work would never have been started, let alone finished. Her encouragement and faith leave me in awe.

### Introduction

It was as a young graduate engineer that I learnt my most important lesson in microwave engineering. Whilst not understanding the behaviour of a solid state power amplifier (in those days 5W at S band was considered high power!), my first mentor, in extreme frustration with me exclaimed, "It's all \$\*\*\*\*\* \$ Ohm's Law!"; perhaps I should have paid more attention at school and university? I am still surprised by how often this very simple observed relationship has come back to me as fundamental in solving or understanding complicated behaviour in microwave circuits. All too often we have sought explanations by complicated phenomena such as moding or earth loops, or have got carried away with the microwave engineers version of the perpetual motion machine; the 100% efficient amplifier, when a return to basics would have more quickly resolved the questions. It is this appreciation of the fundamental underpinning nature of Ohm's Law and its application in sinusoidal signals and reactive impedances that has produced seminal works from Cripps [1] with loadline theory and his text books [2]. It has also been the keystone of waveform engineering, a methodology that I have had the privilege to observe develop at Cardiff University, first as a sponsor of PhD students and latterly as one myself, under the guidance and inspiration of Professor Paul Tasker.

There is a danger in the modern world of fabulous nonlinear and electro-magnetic simulators, GHz processors, and Terabyte memory that we skim over the fundamentals and get carried away with digital outputs (microwave power measurements to 4 or 5 decimal places!). Without the sanity check of Ohm's Law we can delude ourselves or find solutions, the root of which we don't really understand. Hence the intrinsic beauty of the measurement system developed at Cardiff University; the ability to look in detail at the actual voltage and current waveforms and their dependency on the impedance environment. I remembered from my first degree nearly 30 years ago now that square waves were made from odd harmonics, but when I could actually construct and observe these at microwave frequencies by altering the harmonic impedances it brought a real smile of satisfaction to my face. Similarly when I first de-embedded the drain capacitance from the observed RF loadline and I recognised the shapes described by Cripps in [2], the satisfaction was immense. Having been designing, or perhaps more accurately crafting, microwave amplifiers since the early 1980s, I finally began to feel a real connection between

the theory and what I could observe in the real world. Yes there are times when Ohm's Law can be stretched somewhat, particularly at breakdown in semiconductors, but experience has taught me that you ignore it at your peril.

I feel very fortunate to be working in this industry at this time, but also to have been around long enough to appreciate what we have. I did match circuits using a compass and protractor on a Smith chart,... and I wouldn't go back there. I did run CAD simulations overnight and printout a line of results for each iteration; so that we could scan through the next morning and see if there were any good combinations of variables, - and now I wish the simulations would take long enough to go and get a coffee. I did spend hours calibrating analysers and actually that hasn't changed much (but at least I get a really good screen copy of the results instead of making sketches in my log book and I can store the data in an easily readable electronic file instead of copying them out by hand). We have so much capability accessible to us, but if we don't really understand what we are doing, and take the time to make sure that our measurements are accurate, test our assumptions, model in detail, we might as well be right back in the 1980's taking wild stabs in the dark, hoping to hit the target.

{See the end of chapter 1 for reference details}

#### **List of Publications**

1. D. FitzPatrick, T. Williams, J. Benedikt, P.J. Tasker "High frequency sampling technique for microwave active and passive device characterization", ARMMS (RF & Microwave Measurement Society) Conference, November 2007.

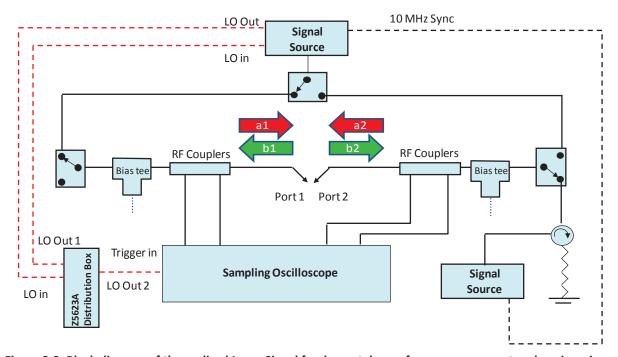

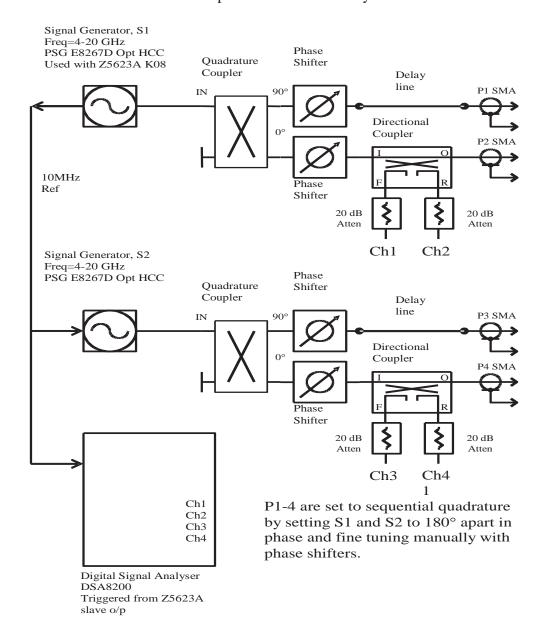

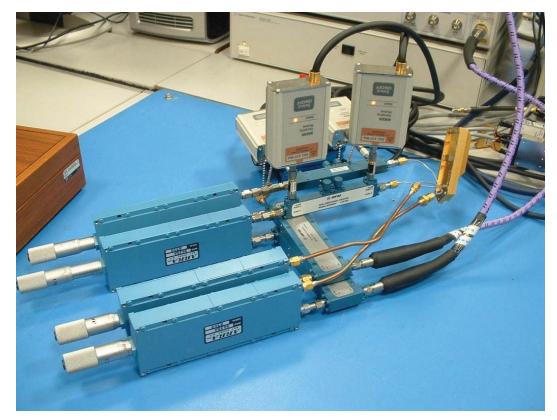

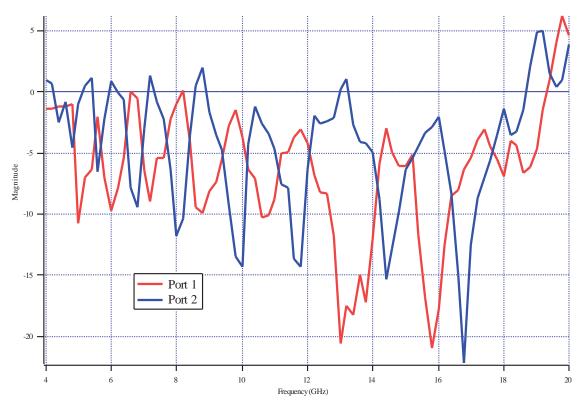

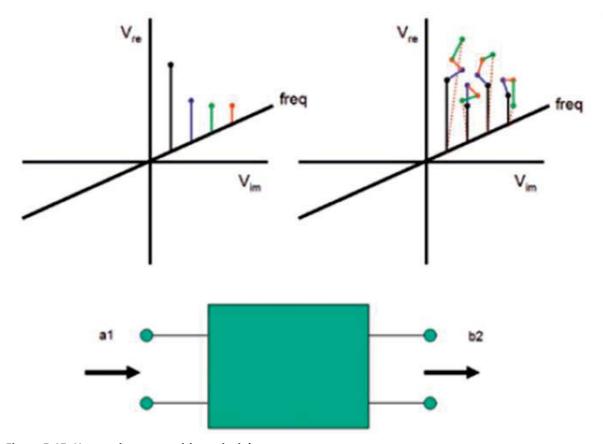

The most commonly used method for characterising microwave components is to measure the s-parameters of the device using a Vector Network Analyser. A problem with this method is that the VNAs are essentially narrow band down converters and cannot handle harmonic and distortion products. By directly measuring the incident and reflected waveforms on the device ports with wide bandwidth samplers and then processing these waveforms, not only can large signal s-parameters be extracted but also harmonic and compression characteristics. The flexibility offered by the direct access to the sampling heads allows for the construction of measurement systems which can, for example, directly measure the multi-port devices with all ports simultaneously excited (such as phased array elements). This paper describes the basic waveform measurement system developed at Cardiff University, and then some of the applications to which this system has been applied including, small and large s-parameter measurement, DC-IV device characterisation, active load-pull including harmonic, and four port antenna match. The potential for 'waveform engineering' and accurate large signal device modeling is described.

2. D. FitzPatrick, T. Williams, J. Lees, J. Benedikt, P.J. Tasker "Large signal device characterization using active load-pull for improved MMIC design", IET seminar on RF and Microwave IC design, 28<sup>th</sup> February 2008.

**Abstract:** The design of high frequency large-signal active devices depends heavily upon the accuracy of the models used by CAD programs. Traditionally, these models have either been physics or equivalent-circuit based, and this paper presents an alternative approach where measured large-signal data is directly incorporated into the design environment. This approach ensures an accurate representation of the device under large-signal operating conditions and also offers the ability to validate any matching solutions developed before the physical MMIC is realised.

3. D. FitzPatrick, J. Lees, A. Sheikh, J. Benedikt, P.J. Tasker, T. Williams "Fundamental and harmonic termination impedance considerations in the design of optimally efficient wideband MMIC PAs", EMRS-DTC Conference, Edinburgh, July 2009.

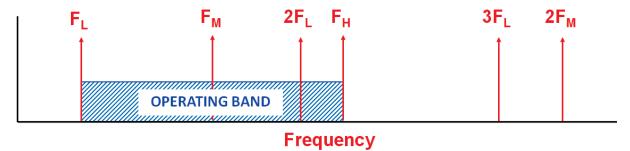

**Abstract:** The importance of harmonic terminations in achieving high-efficiency operation in narrow band amplifiers has been widely published. In wide bandwidth applications however, the emphasis has been on maintaining a broadband match at the fundamental frequencies with little regard to the harmonic impedances. The problem is further complicated by the fact that for the lower frequencies their harmonics often fall in band. This paper demonstrates a technique to measure and quantify the impact of harmonic impedance on a devices performance through the active load-pulling of a class A biased 0.3μm GaAs DpHEMT ½W device over 4 to 18 GHz.

4. D. FitzPatrick, J. Lees, A. Sheikh, J. Benedikt, P.J. Tasker "Systematic investigation of the impact of harmonic termination in the efficiency performance of above octave bandwidth microwave amplifiers", European Microwave Conference 2009, pp. 1445-1448.

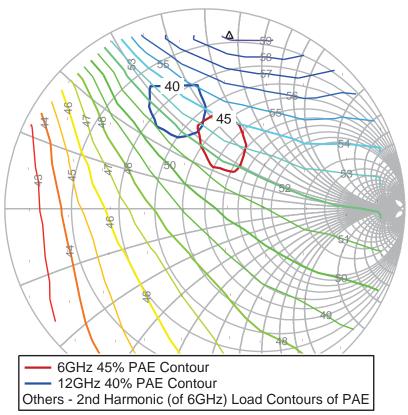

**Abstract:** The importance of harmonic terminations in achieving high-efficiency operation in Narrow Band (NB) amplifiers has been widely published. In Wide Bandwidth (WB) applications however, the emphasis has been on maintaining a broadband match at the fundamental frequencies with little regard to the harmonic impedances. The problem is further complicated by the fact that the harmonics of the lower frequencies often fall within the operational bandwidth of the amplifier. This paper presents an active load-pull technique for measuring and quantifying the impact of harmonic impedance on device performance, and is achieved through the characterisation of a class A biased 0.3  $\mu$ m GaAs pHEMT ½W device at 6, 12 and 18 GHz.

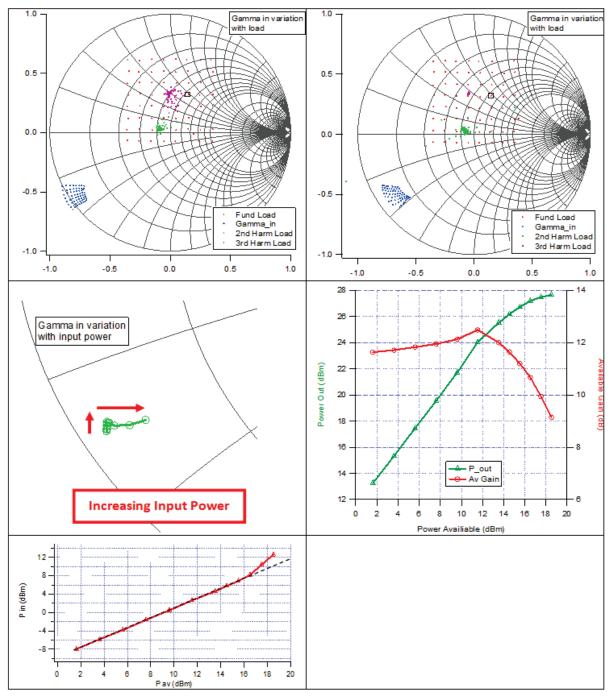

5. D. FitzPatrick, T. Williams, J. Lees, J. Benedikt, S.C. Cripps, P.J. Tasker, "Exploitation of active load-pull and DLUT models in MMIC design", 2010 IEEE Radio Frequency Integrated Circuits Symposium, pp. 487-490.

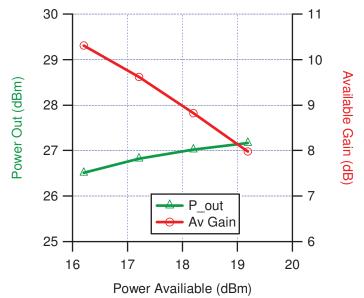

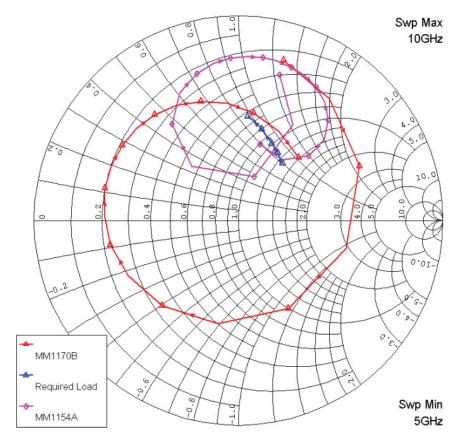

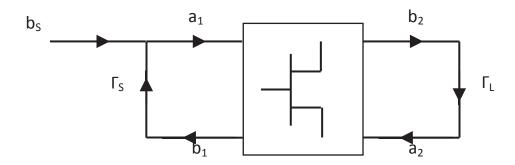

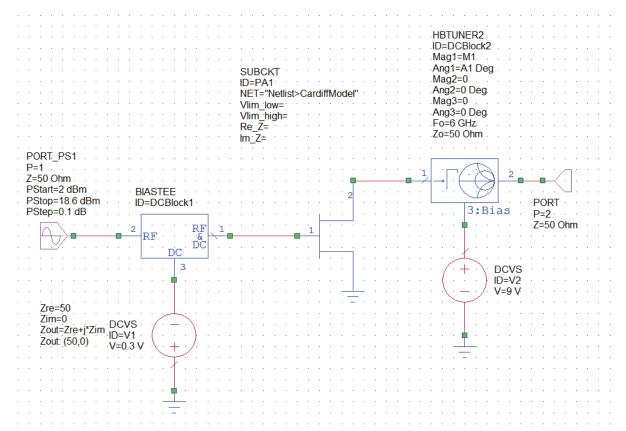

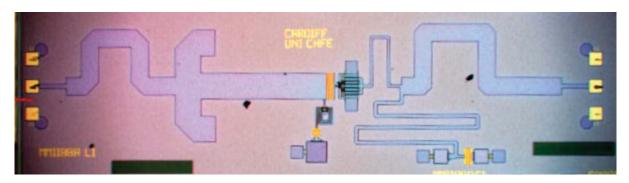

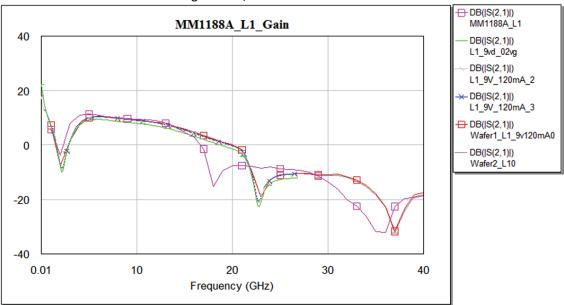

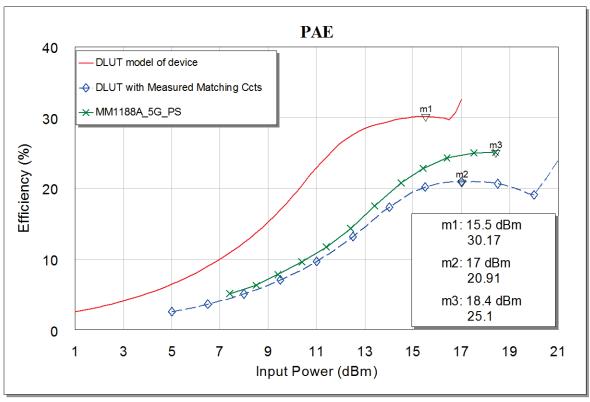

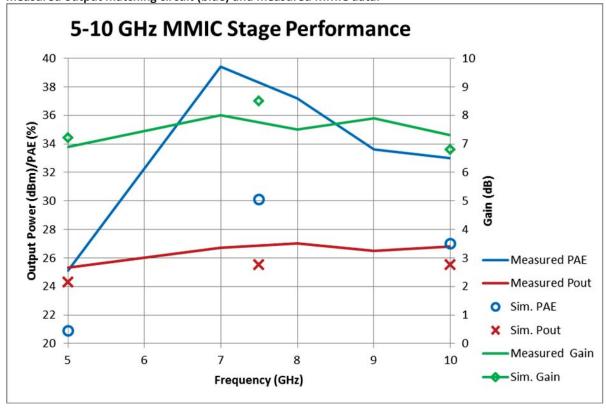

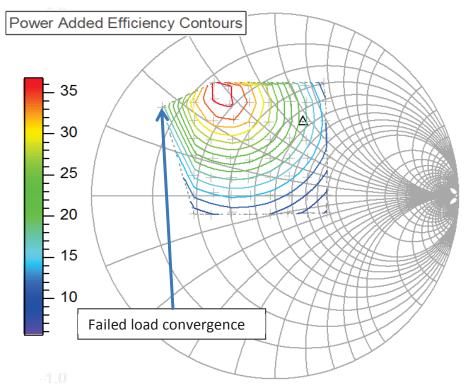

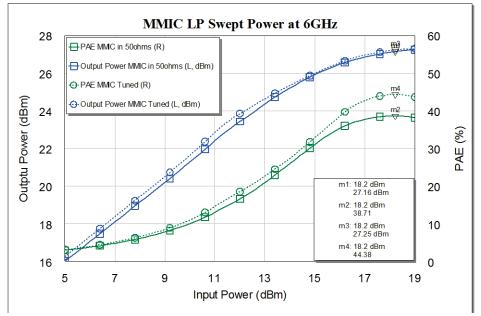

Abstract: The use of active load-pull techniques in the design of high efficiency microwave amplifiers has been well documented. This paper describes how it has been applied to the design of a wideband RFIC gain stage. The technique is particularly relevant in new and developing processes where accurate device models are not available and designers otherwise are often forced to use multiple iterations of a design to attempt to encompass the variability in the process. Often in RFIC design, components operate outside of the ideal operating impedance. A look-up table model technique based on measured data which can be used by conventional CAD programs is used to analyze behaviour. This paper shows how the design process and capabilities of the system can be combined to improve the cost effectiveness and performance of RFIC development and with a stable manufacturing process a "first pass" design methodology. The use of the measurement system as an analysis tool is described.

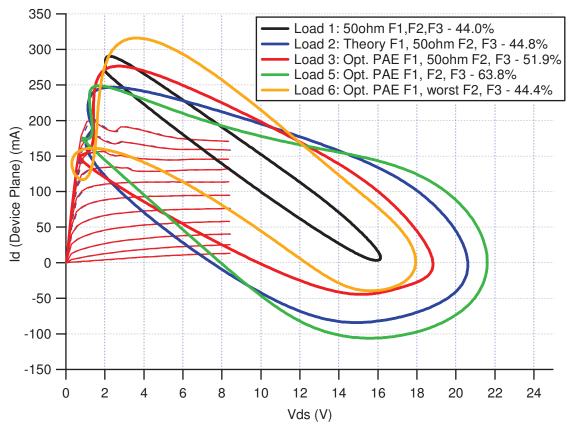

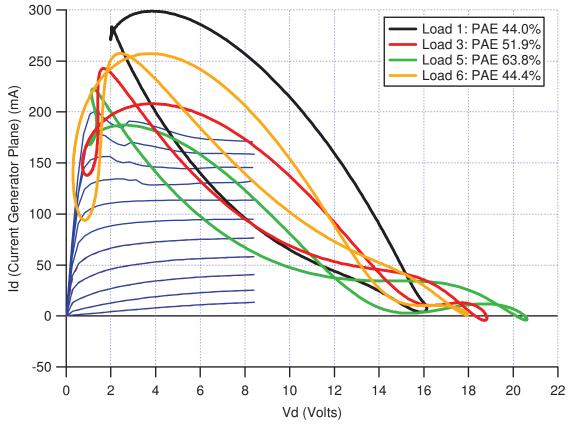

6. D. FitzPatrick, S. Woodington, J. Lees, J. Benedikt, S.C. Cripps, P.J. Tasker, T. Williams "Utilization of DLUT model in the design of an harmonically enhanced high efficiency MMIC amplifier", EMRS-DTC Conference, Edinburgh, July 2010.

**Abstract:** The benefits of higher efficiencies in the power amplifier stages have a multiplied effect on system performance. Traditional approaches to the design of these elements suffer from inaccurate nonlinear modeling which results in multiple iterations until satisfactory performance is achieved, with associated increased costs and delays in project completion. The approach presented in this paper not only increases confidence in delivered circuit behavior, but also allows the determination of the absolute optimum performance without relying on predetermined model constraints.

- 7. D. FitzPatrick, S. Woodington, J. Lees, J. Benedikt, S.C. Cripps, P.J. Tasker "The application of the Cardiff Look-Up Table model to the design of MMIC power amplifiers", ARMMS (RF & Microwave Measurement Society) Conference, November 2010.

- **Abstract:** The design of microwave power amplifiers has been greatly enhanced by the use of CAD; however despite the improvements in the area of E-M simulation and non-linear analysis, de-signs still often require to be 'tweaked'. While this may be a practical option for discrete amplifiers it is extremely difficult in the MMIC domain. The requirement for increased efficiency operation and hence the use of modes such as class F and J have highlighted inadequacies in current models. This paper describes the use of waveform engineering not only in the area of device measurement, but also as an integral part of the MMIC design process. The practical limits on current nonlinear models are discussed and an example design using harmonic enhancement, is shown.

- 8. D. FitzPatrick, R. Saini, J. Lees, J. Benedikt, S.C. Cripps, P.J. Tasker "A waveform engineering approach to the design of improved efficiency wideband MMIC amplifiers", WAMICON (IEEE Wireless And Microwave Conference) April 2011.

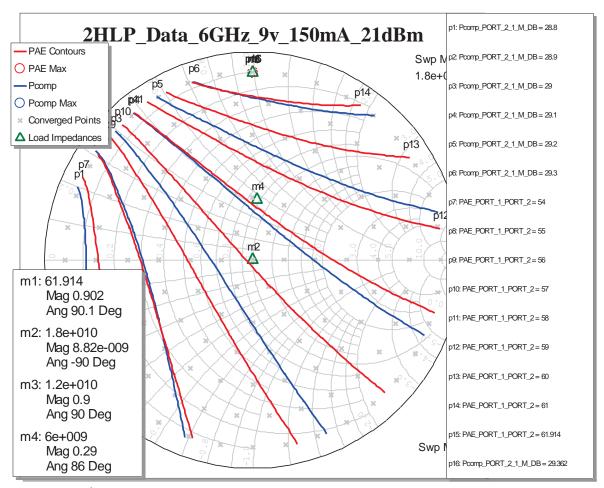

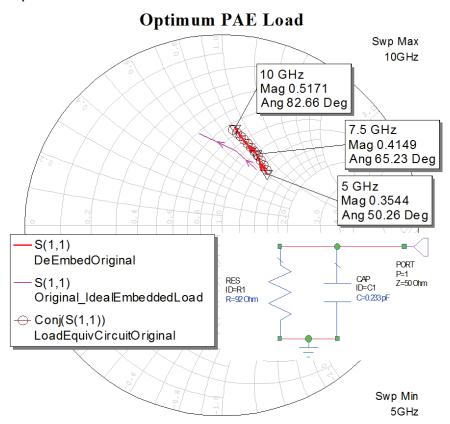

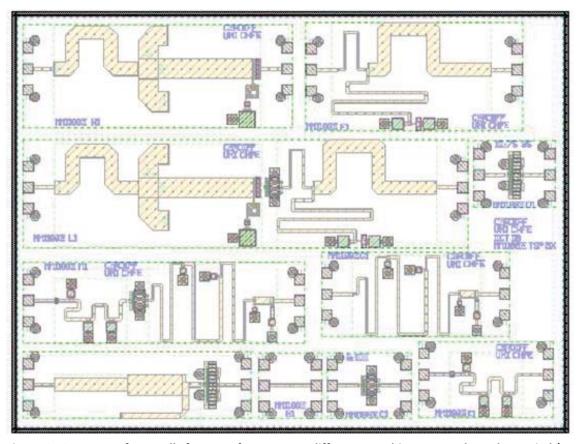

Abstract: This paper describes a design methodology based on waveform

- engineering within a harmonic active load-pull system and utilizing the Cardiff Direct Look-Up Table (DLUT) model. The process seeks to address some of the key issues facing designers when using nonlinear simulation of high power microwave amplifiers: model validity, boundary conditions and yield. The application of this process to the design of a 0.5 W, 5-10 GHz GaAs pHEMT with good PAE is detailed.

- 9. D. FitzPatrick, J. Lees, T. Williams, R. Saini, S. Woodington, A. Sheikh, J. Benedikt, S.C. Cripps, P.J. Tasker "The use of harmonic active load pull and direct device modelling in the MMIC design process", Workshop on Advanced III-V MMIC design techniques, European Microwave Conference 2011.

- **Abstract:** This presentation will outline the importance of including harmonic load pull in the characterisation of transistors and the benefits of creating Direct Look-Up Table models in an integrated measurement simulation-design environment. A design methodology will be presented which is applicable to both narrow and wide band applications and which delivers faster development cycles.

## List of Abbreviations

AC - Alternating Current

ALP - Active Load Pull

BGA - Ball Grid Array

CAD - Computer Aided Design

CW - Continuous Wave

DC - Direct Current

DE - Drain Efficiency

DFT - Discrete Fourier Transform

DSA - Digital Serial Analyser

DUT - Device Under Test

FET - Field Effect Transistor

FFT - Finite (Fast) Fourier Transform

GaAs - Gallium Arsenide GaN - Gallium Nitride

GSG - Ground - Signal - Ground

HBT - Heterojunction Bipolar TransistorHEMT - High Electron Mobility Transistor

LPF - Low Pass Filter

MAG - Maximum Available Gain MSG - Maximum Stable Gain

MDF - (MDiF) Measurement Data interchange Format

MMIC - Microwave Monolithic Integrated Circuit

MSUB - Microstrip Substrate

MTA - Microwave Transition Analyser

PAE - Power Added Efficiency

PCB - Printed Circuit Board

PDK - Process Design Kit

PRM - Phase Reference Module

Si - Silicon

SiC - Silicon Carbide

SOLT - Short, Open, Load, Thru (calibration technique) tand - Loss Tangent (tan  $\delta$  – referring to dielectric loss)

VNA - Vector Network Analyser

YIG - Yttrium Indium Garnet

# **Table of Contents**

| Decla  | aratio                                                    | n                                                                                     | ii              |  |

|--------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|--|

| Sumi   | mary                                                      |                                                                                       | iii             |  |

| Ackn   | owled                                                     | Igements                                                                              | iv              |  |

| Intro  | ductio                                                    | on                                                                                    | V               |  |

| List c | of Pub                                                    | lications                                                                             | vii             |  |

| List c | of Abb                                                    | reviations                                                                            | х               |  |

| 1      | 1.1                                                       | duction to Novel MMIC Design Process Using Waveform Engineering Introduction          | 1               |  |

|        | 1.2<br>1.3                                                | Applications of Broadband Amplifiers – Requirements & Performance Broad Band Matching | Drivers 8<br>10 |  |

|        | 1.4                                                       | Input Impedance Matching                                                              | 36              |  |

|        | 1.5                                                       | Output Matching Impedance                                                             | 43              |  |

|        | 1.6                                                       | Class J Operation                                                                     | 78              |  |

|        | 1.7                                                       | Summary                                                                               | 87              |  |

|        | 1.8                                                       | Bibliography                                                                          | 89              |  |

| 2      | Current Approaches to the Design of MMIC Power Amplifiers |                                                                                       |                 |  |

|        | 2.1                                                       | Introduction                                                                          | 92              |  |

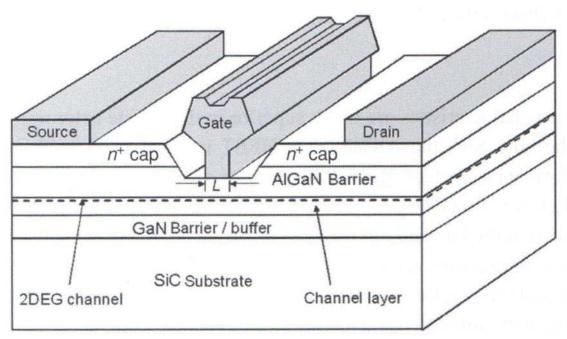

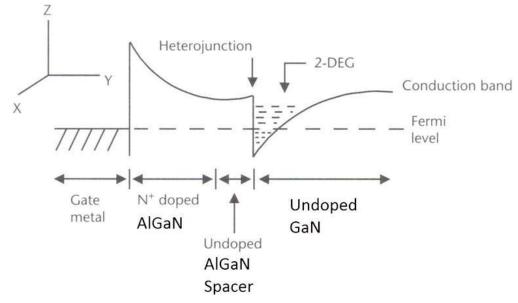

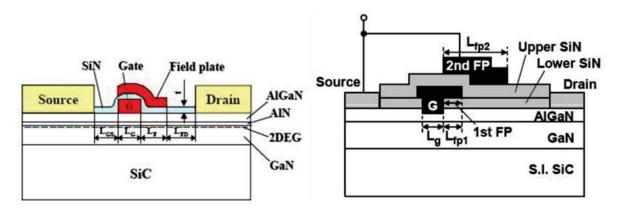

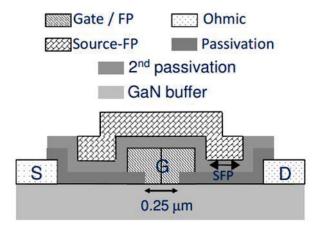

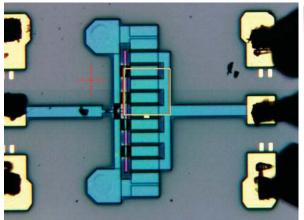

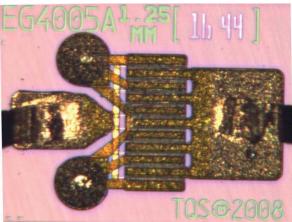

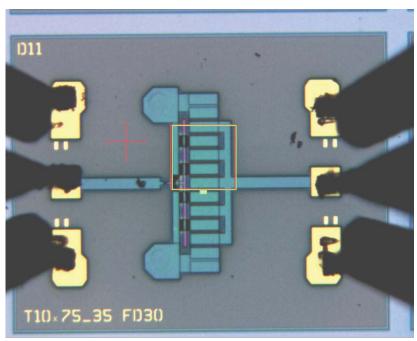

|        | 2.2                                                       | Device Construction                                                                   | 98              |  |

|        | 2.3                                                       | Technology Selection                                                                  | 101             |  |

|        | 2.4                                                       | Amplifier Topologies                                                                  | 109             |  |

|        | 2.5                                                       | Practical MMIC PA design considerations                                               | 117             |  |

|        |                                                           | 2.5.1 Architecture Design                                                             | 118             |  |

|        |                                                           | 2.5.2 Nonlinear Analysis and Design                                                   | 130             |  |

|        |                                                           | 2.5.3 Integration                                                                     | 131             |  |

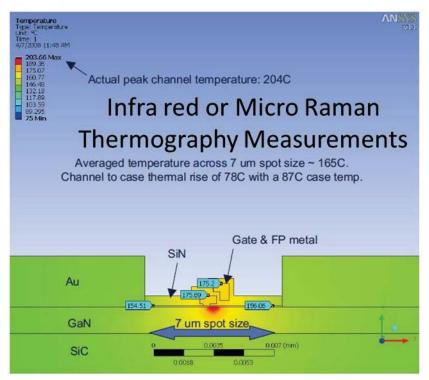

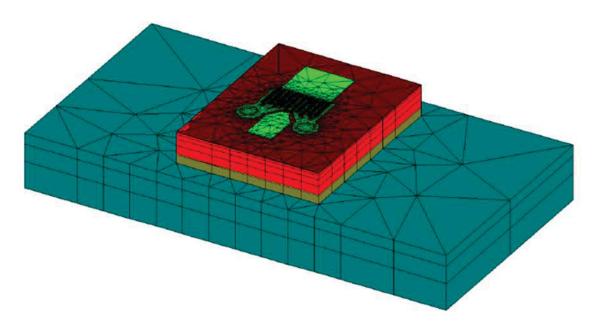

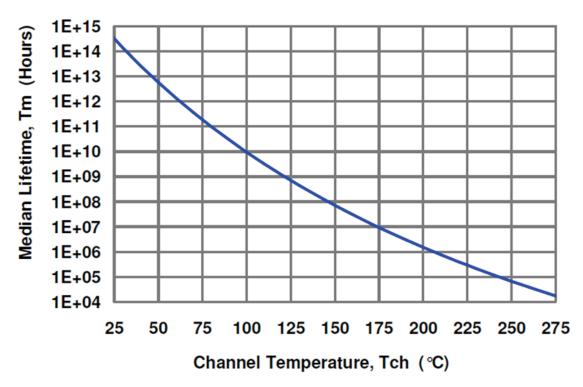

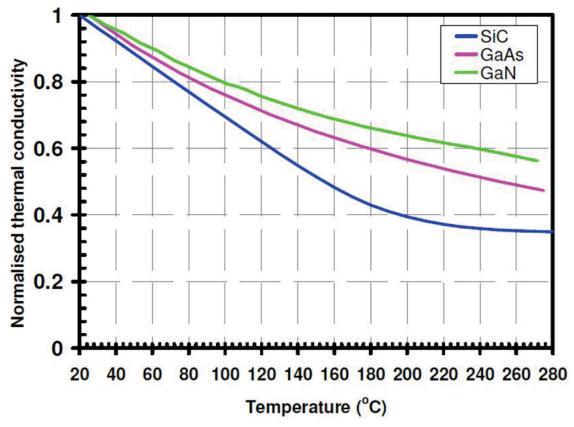

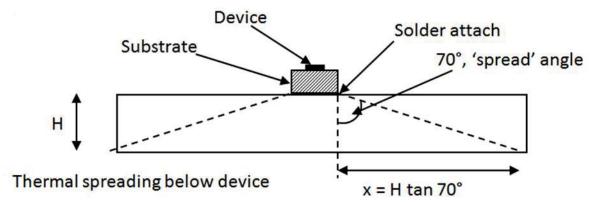

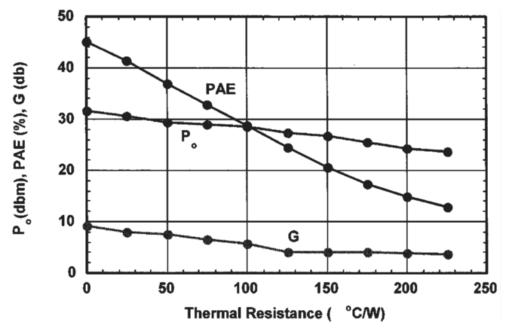

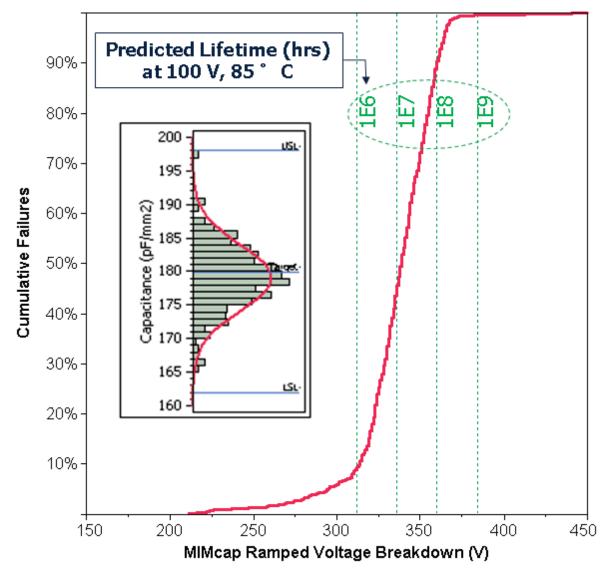

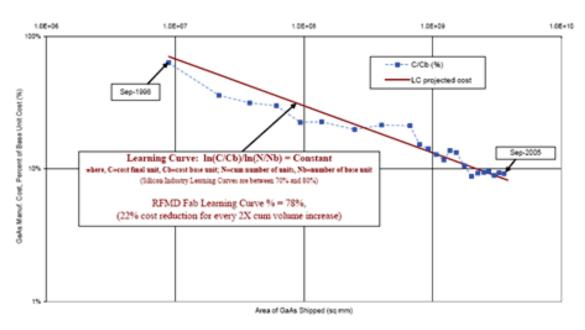

|        | 2.6                                                       | Thermal Design                                                                        | 133             |  |

|        | 2.7                                                       | Specific Considerations for Broadband GaN MMIC design                                 | 144             |  |

|        | 2.8                                                       | Performance of wideband MMIC designs                                                  | 148             |  |

|        | 2.9                                                       | Bibliography                                                                          | 153             |  |

| 3 | Measurement System Construction and Verification |                                                |     |  |  |  |  |

|---|--------------------------------------------------|------------------------------------------------|-----|--|--|--|--|

|   | 3.1                                              | Introduction                                   | 158 |  |  |  |  |

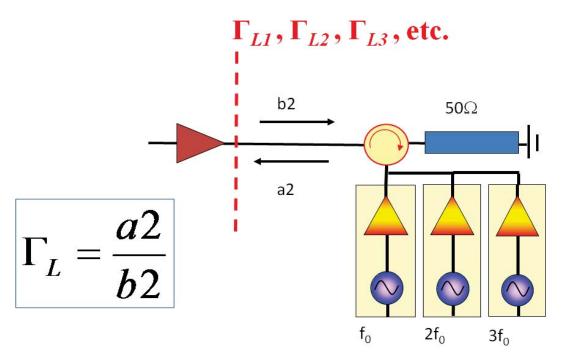

|   | 3.2                                              | Harmonic Active Load Pull                      | 159 |  |  |  |  |

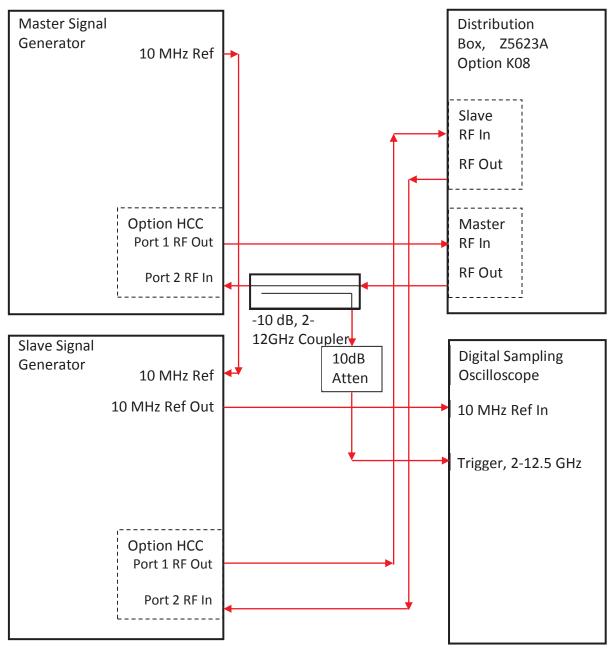

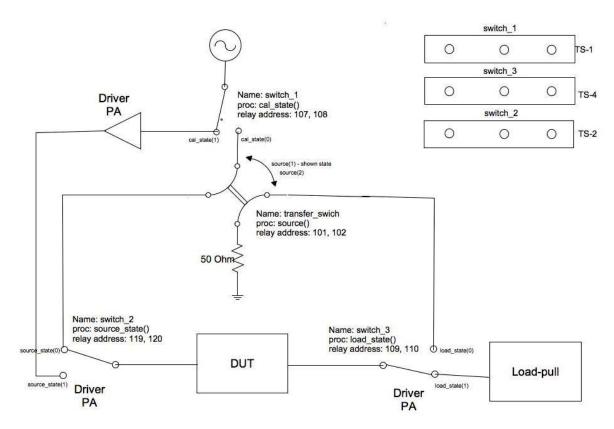

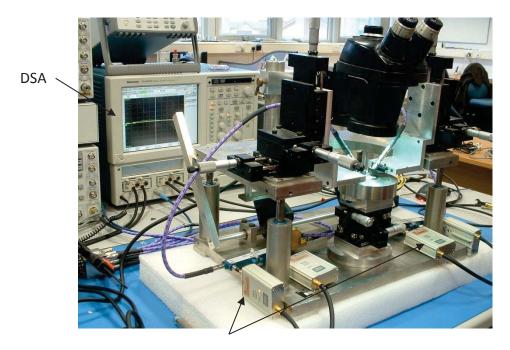

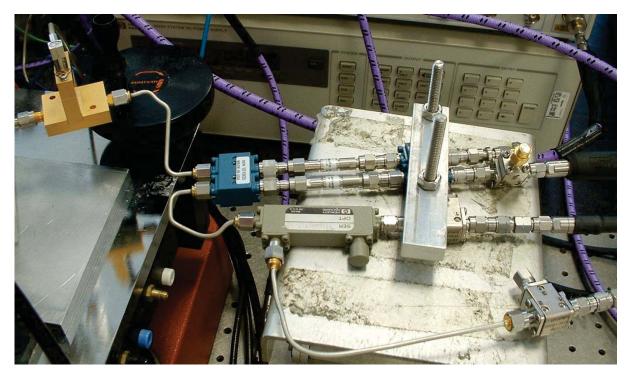

|   | 3.3                                              | System Description                             | 161 |  |  |  |  |

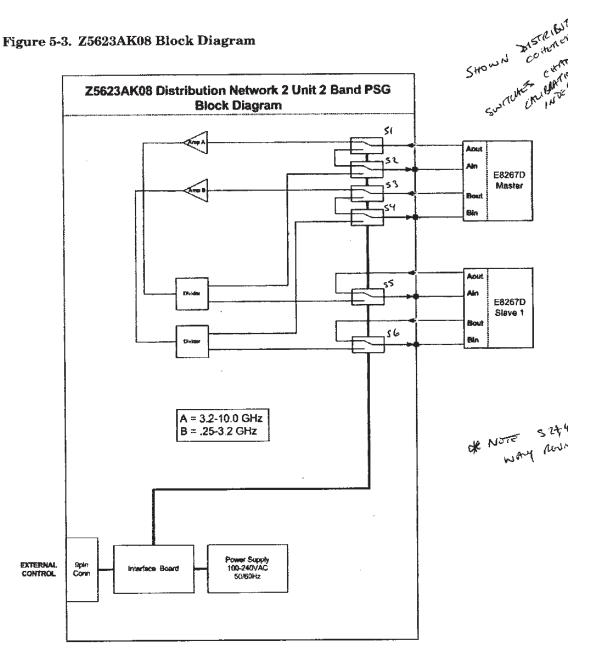

|   | 3.4                                              | Measurement System Switching                   | 174 |  |  |  |  |

|   | 3.5                                              | System Verification [11]                       | 175 |  |  |  |  |

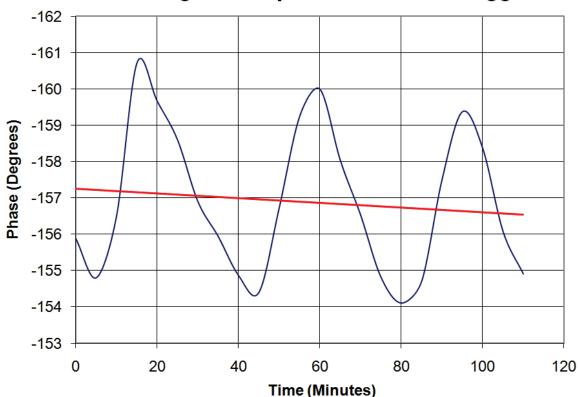

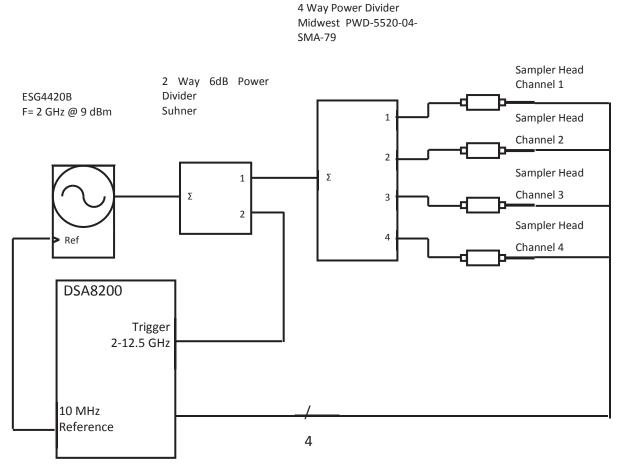

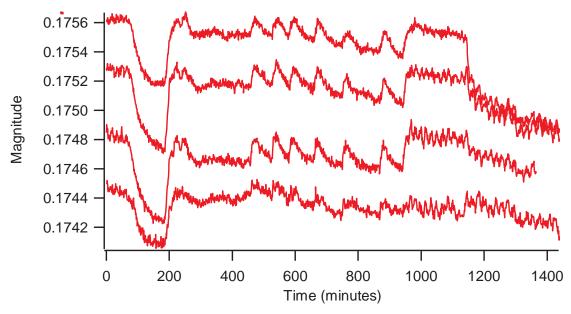

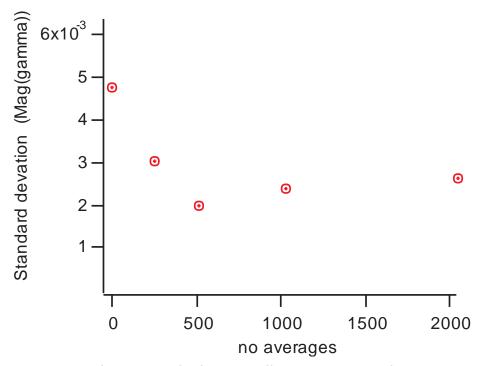

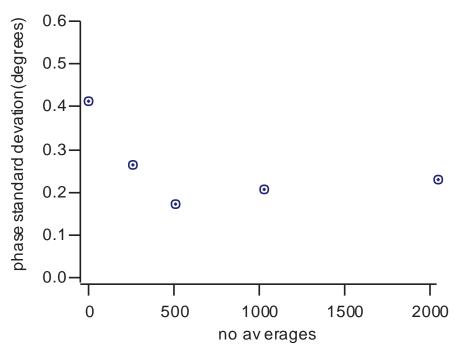

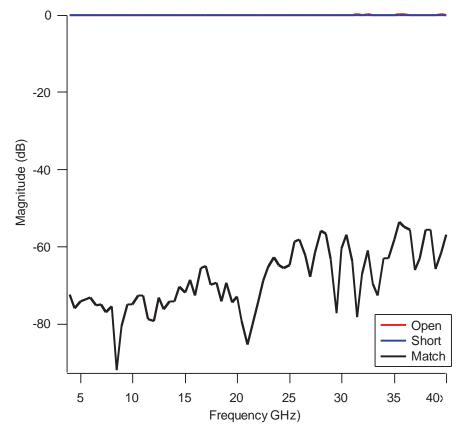

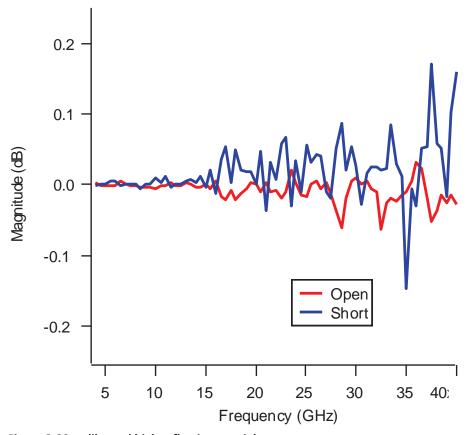

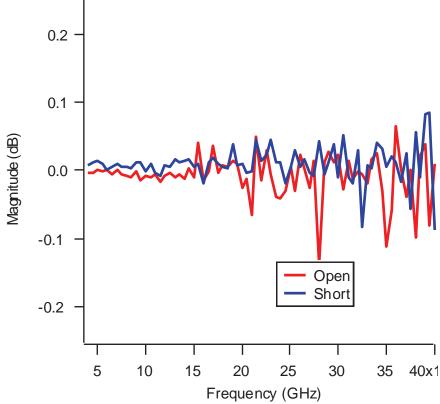

|   |                                                  | 3.5.1 Repeatability of Reflection measurements | 176 |  |  |  |  |

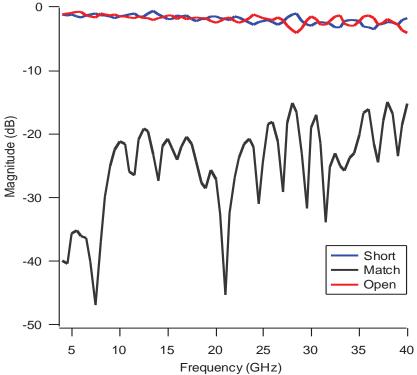

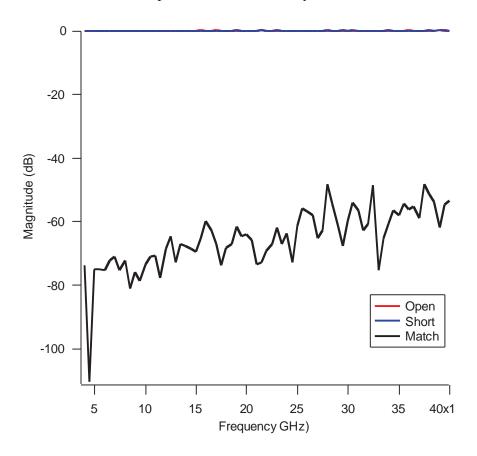

|   |                                                  | 3.5.2 Dynamic Range of measurements            | 178 |  |  |  |  |

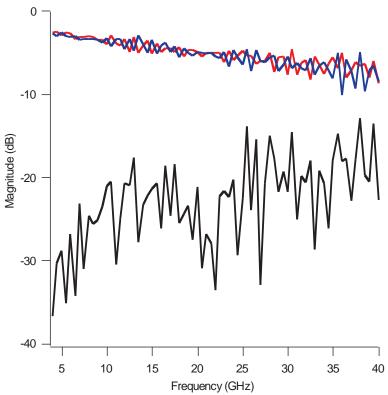

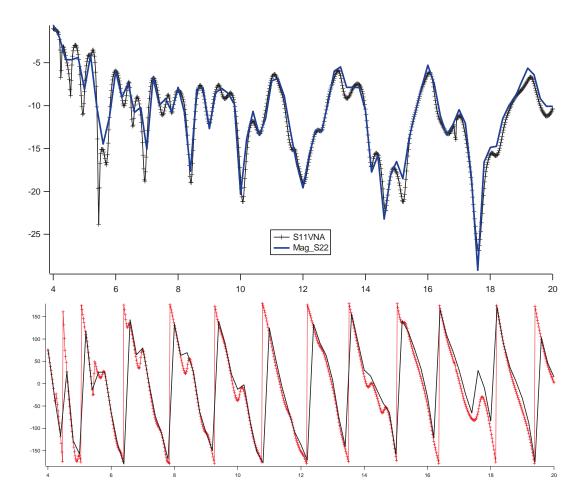

|   |                                                  | 3.5.3 Comparative Measurement with VNA         | 183 |  |  |  |  |

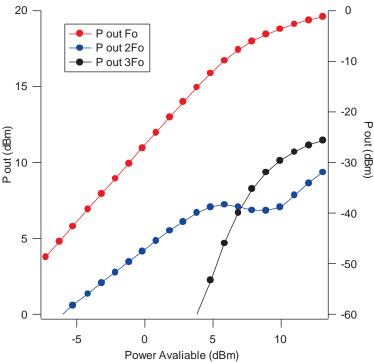

|   | 3.6                                              | System Measurements                            | 183 |  |  |  |  |

|   | 3.7                                              | System Improvements                            | 190 |  |  |  |  |

|   |                                                  | 3.7.1 System Losses                            | 190 |  |  |  |  |

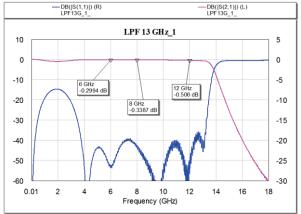

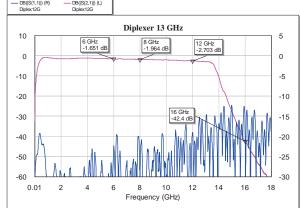

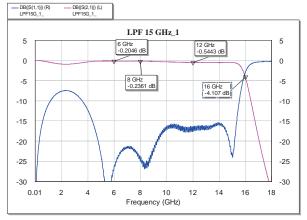

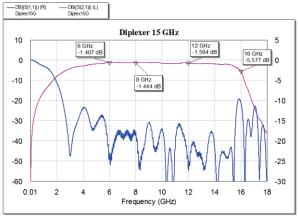

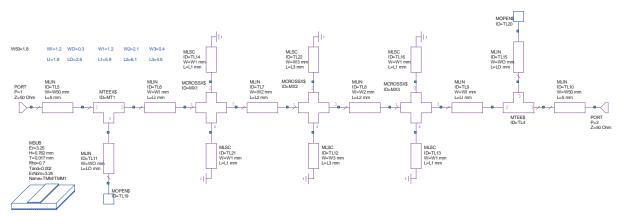

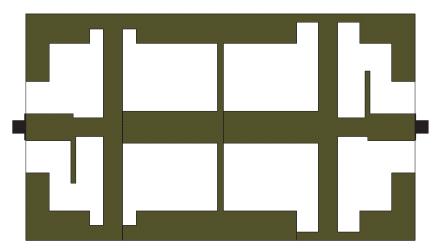

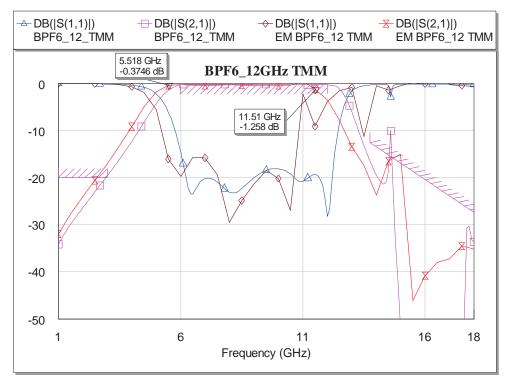

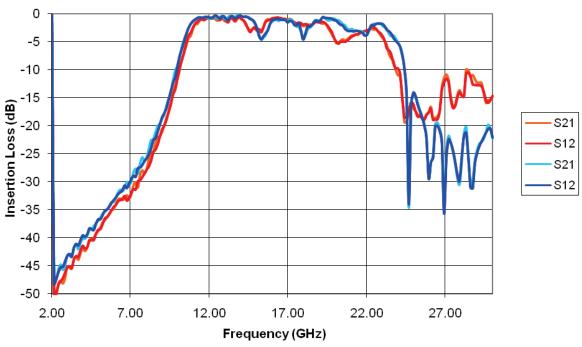

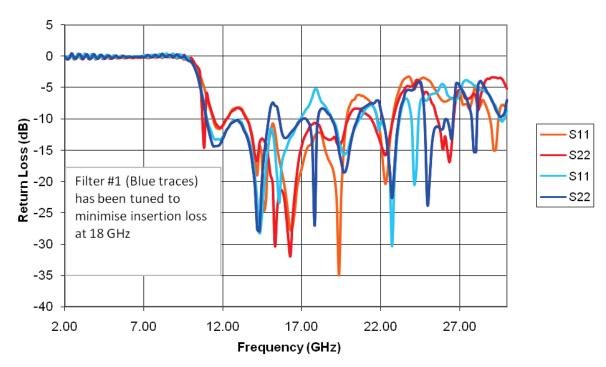

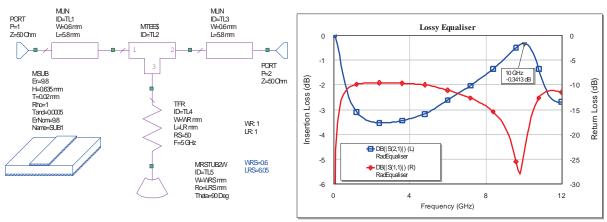

|   |                                                  | 3.7.2 Broadband Triplexer                      | 195 |  |  |  |  |

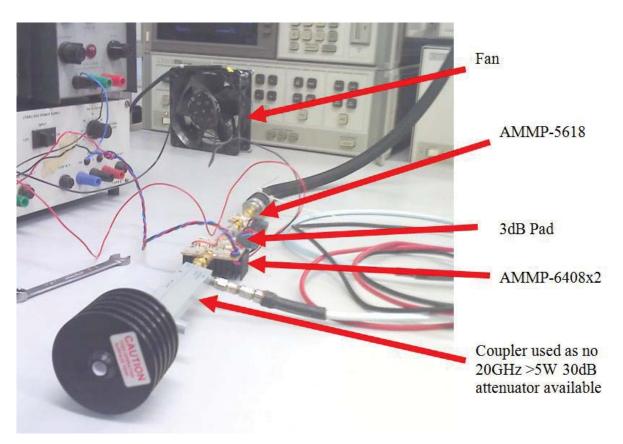

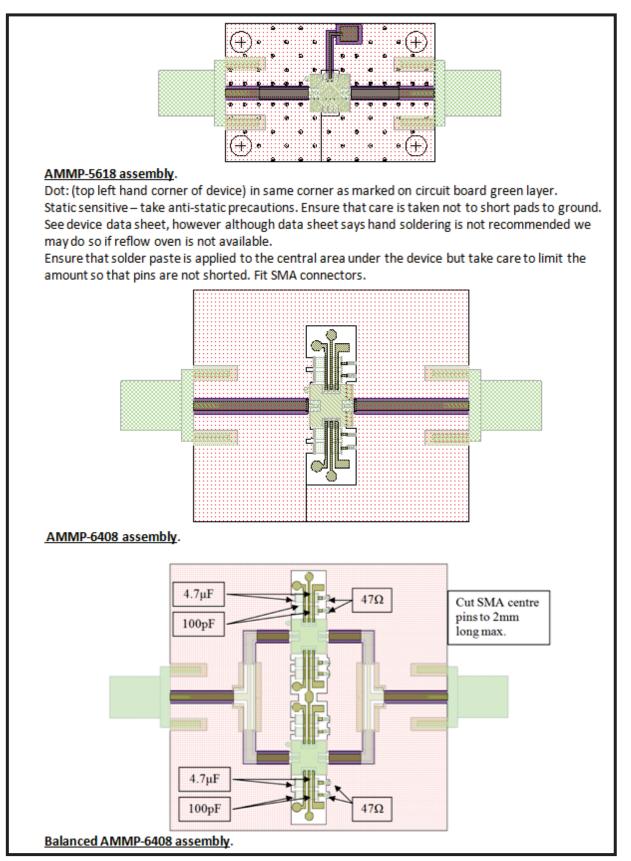

|   |                                                  | 3.7.3 Driver Amplifiers                        | 205 |  |  |  |  |

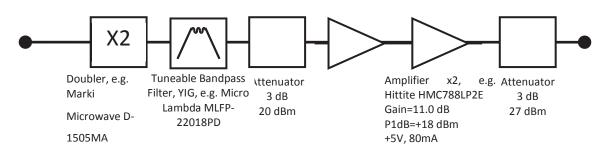

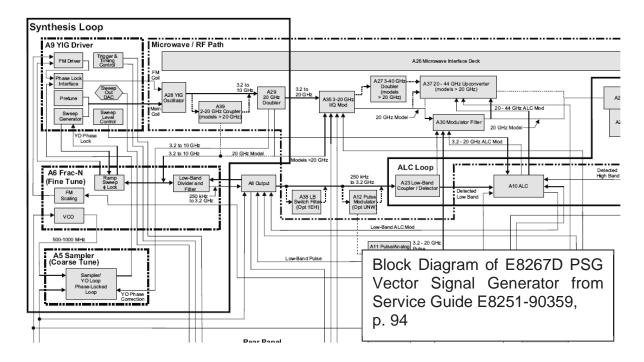

|   |                                                  | 3.7.4 Signal Generation                        | 211 |  |  |  |  |

|   | 3.8                                              | Summary                                        | 215 |  |  |  |  |

|   | 3.9                                              | Recommendations                                | 216 |  |  |  |  |

|   | 3.10                                             | Bibliography                                   | 217 |  |  |  |  |

|   | 3.11                                             | Appendices                                     | 219 |  |  |  |  |

| 4 | Activ                                            | Active Harmonic Load Pull Device Measurements  |     |  |  |  |  |

|   | 4.1                                              | Introduction                                   | 221 |  |  |  |  |

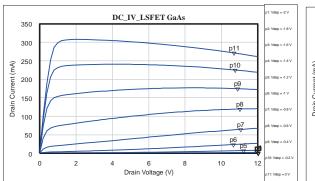

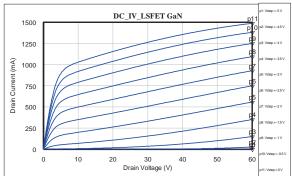

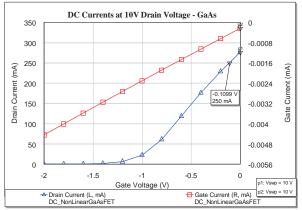

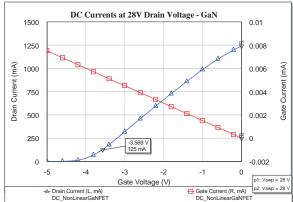

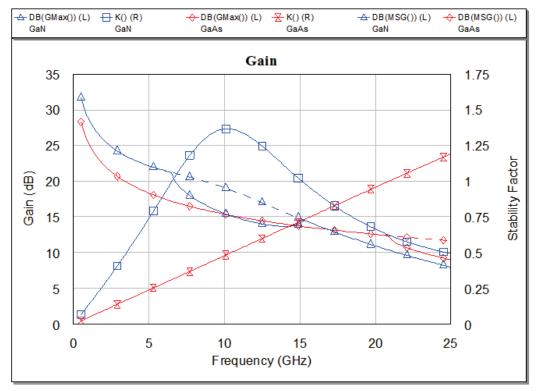

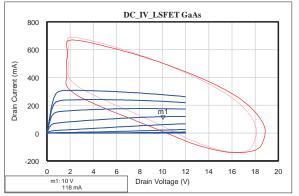

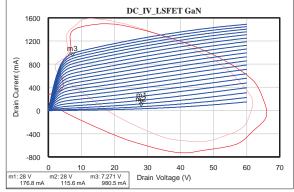

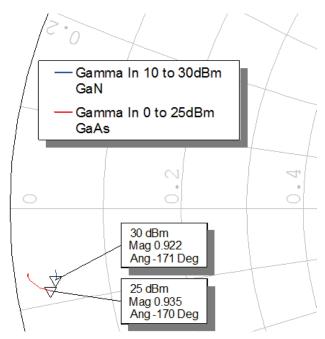

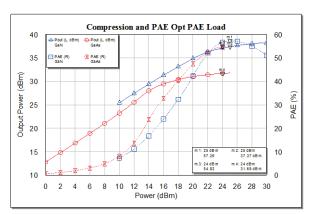

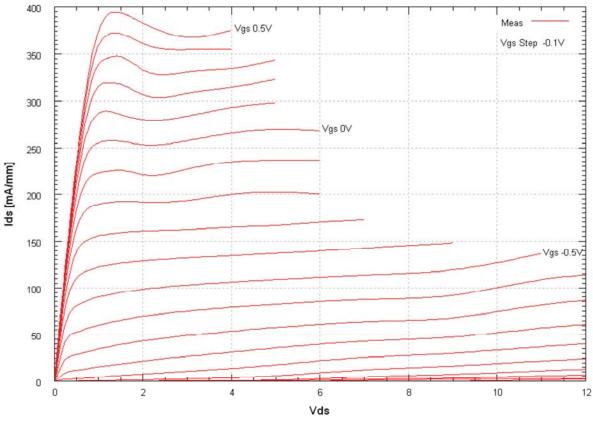

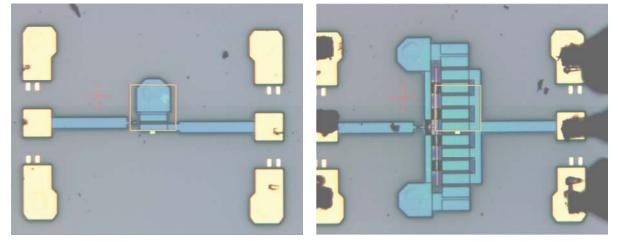

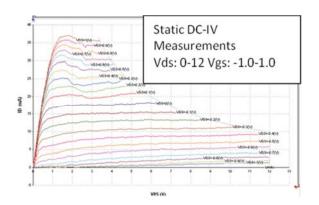

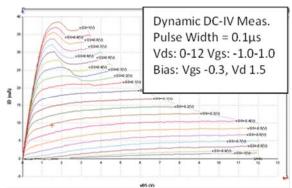

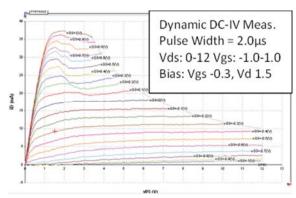

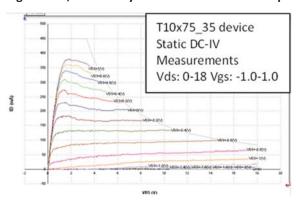

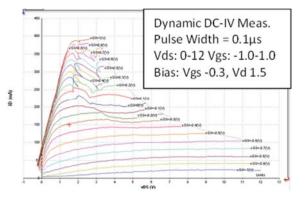

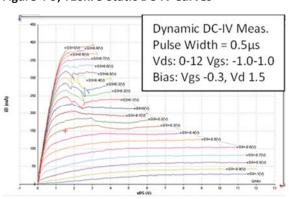

|   | 4.2                                              | DC-IV Measurements                             | 227 |  |  |  |  |

|   | 4.3                                              | Device De-Embedding                            | 231 |  |  |  |  |

|   | 4.4                                              | Device Measurements                            | 236 |  |  |  |  |

|   | 4.5                                              | Harmonic Impedance Effects                     | 255 |  |  |  |  |

|   | 4.6                                              | Reduced Conduction Angle Measurements          | 292 |  |  |  |  |

|   | 4.7                                              | Input Pre-matching                             | 311 |  |  |  |  |

|   | 4.8                                              | Summary                                        | 315 |  |  |  |  |

|   | 4.9                                              | Bibliography                                   | 317 |  |  |  |  |

| 5 | Novel Device Modelling Techniques                |                                                |     |  |  |  |  |

|   | 5.1                                              | Introduction                                   | 318 |  |  |  |  |

|   | 5.2                                              | Measurements                                   | 320 |  |  |  |  |

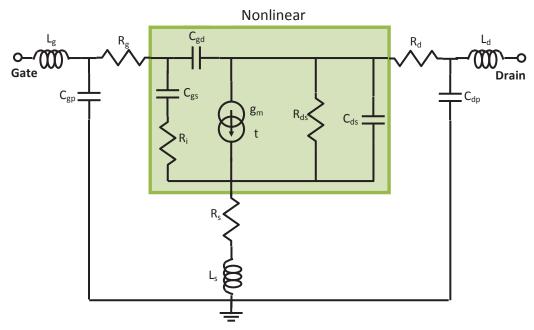

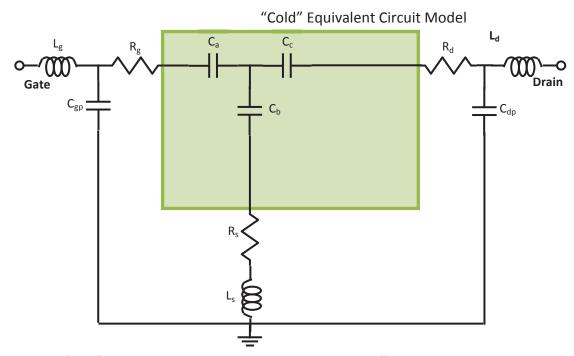

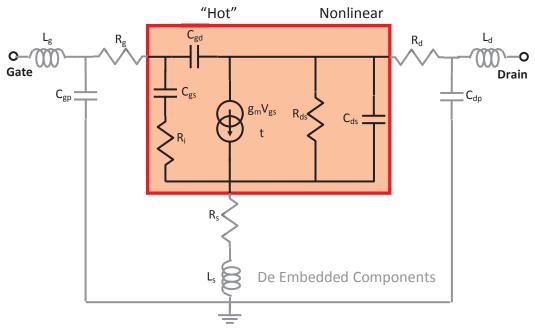

|   | 5.3                                              | Equivalent Circuit Models                      | 324 |  |  |  |  |

|   | 5.4                                              | Large Signal Modelling                         | 330 |  |  |  |  |

|   |                                                  | 5.4.1 Nonlinear Analysis Techniques            | 331 |  |  |  |  |

|   | 5.5                                              | 'Black Box' Modelling                          | 343 |  |  |  |  |

|   | 5.6                                              | Direct Measurement Model Implementation        | 353 |  |  |  |  |

|   | 5.7                                              | Summary                                        | 365 |  |  |  |  |

|   | 5.8                                              | Bibliography                                   | 367 |  |  |  |  |

|   |                                                  |                                                |     |  |  |  |  |

| 6 | MMIC Design Using Active Harmonic Load Pull                               |                                                 |     |  |  |

|---|---------------------------------------------------------------------------|-------------------------------------------------|-----|--|--|

|   | 6.1                                                                       | Introduction                                    | 371 |  |  |

|   | 6.2                                                                       | Design Approach                                 | 374 |  |  |

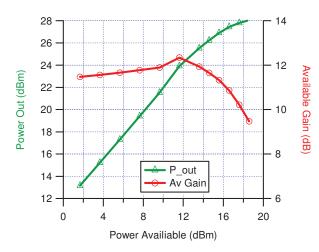

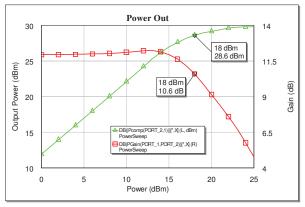

|   | 6.3                                                                       | 5 – 10 GHz 26dBm Driver Stage Design            | 381 |  |  |

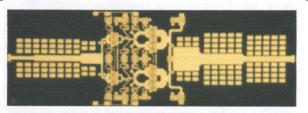

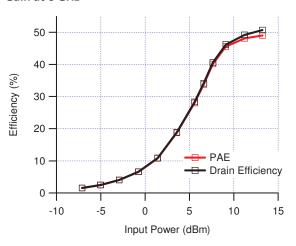

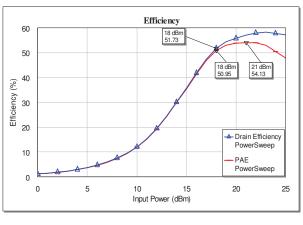

|   | 6.4                                                                       | Design of 0.5W Harmonically Enhanced MMIC stage | 404 |  |  |

|   | 6.5                                                                       | Summary of MMIC Design Process Implementation   | 436 |  |  |

|   | 6.6                                                                       | Bibliography                                    | 440 |  |  |

| 7 | Summary and Conclusion of Research into a Novel MMIC Design Process Using |                                                 |     |  |  |

|   | Waveform Engineering                                                      |                                                 |     |  |  |

|   | 7.1                                                                       | Summary                                         | 442 |  |  |

|   | 7.2                                                                       | Conclusion                                      | 451 |  |  |

|   | 7.3                                                                       | Further Work                                    | 451 |  |  |

|   | 7.4                                                                       | Bibliography                                    | 454 |  |  |

# 1 Introduction to Novel MMIC Design Process Using Waveform Engineering

"The current through a conductor between two points is directly proportional to the potential difference across the two points."

Modern form of Ohm's Law, 1827. Georg Simon Ohm, 1789-1854.

Figure 1-1, Pictorial description of Ohm's Law, the relationship between voltage, current and resistance.

#### 1.1 Introduction

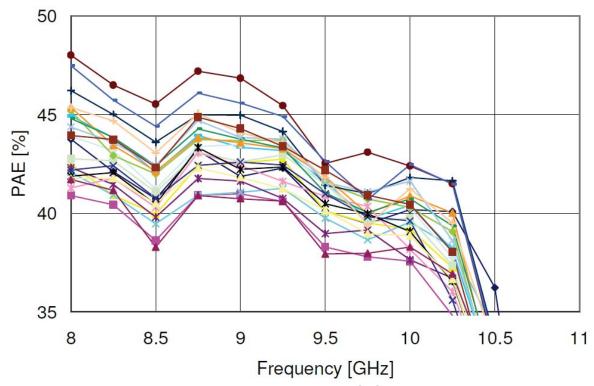

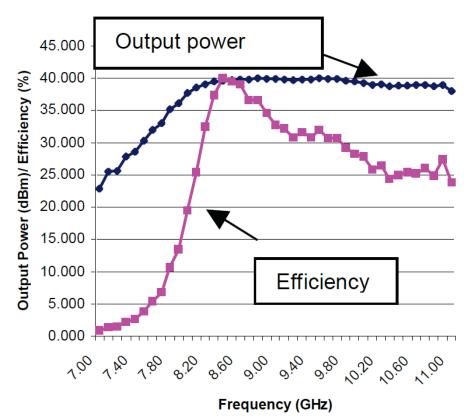

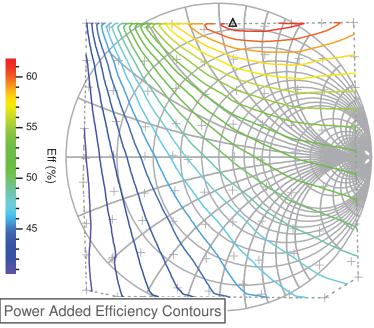

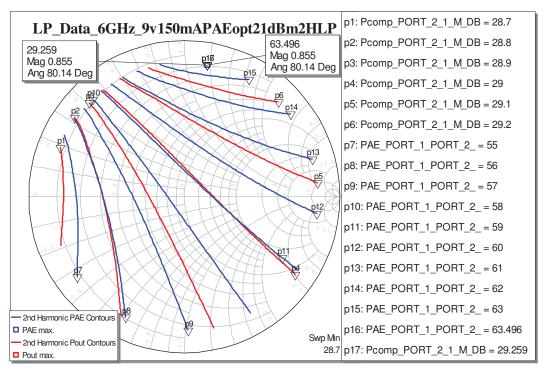

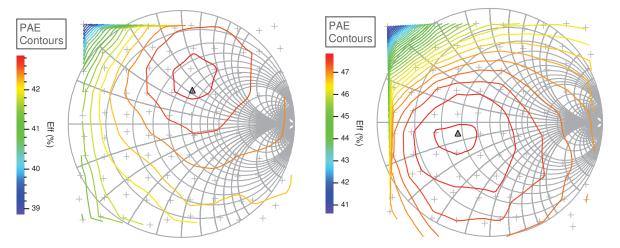

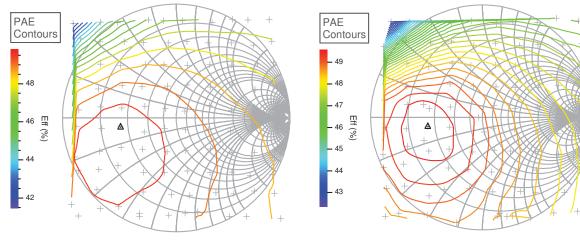

The project addresses fundamental challenges relating to further developments of RF Systems and Transduction Devices & Materials for remote sensing applications. The main objective is to improve the output power and Power Added Efficiency (PAE) of anticipated RF systems for emerging ultra-wideband radar equipment (6-18GHz) of the future. This will effectively minimise the power consumption, thermal dissipation, and the size of RF systems for a given performance, resulting in benefits to a wide range of applications with a particular relevance to mobile or field-deployable units, which are affected by significant size and power consumption constraints.

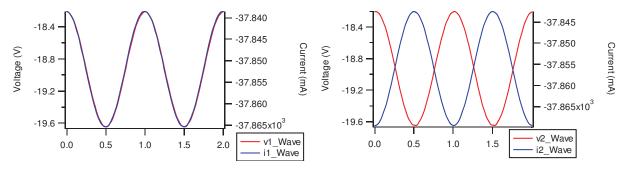

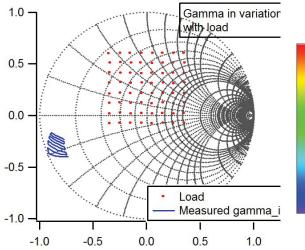

To overcome the incremental improvements in the design methodology of military RF systems the project aimed to extend techniques, developed for the optimisation of mobile communications technologies, to the higher frequencies of interest. These techniques, based on a novel measurement concept, allow complete access to and manipulation of the information contained at the interfaces between the RF system components. The approach involves the measurement and engineering (including dynamic load line control) of current and voltage waveforms and represents a major departure from currently established non-linear design and analysis methods. It is important to note that despite its novelty, the information provided still allows direct reference and comparison with past and present design techniques and thus allows the inclusion of the significant know-how which has been developed in the last few decades.

To fully utilise the additional information, which is directly obtained from this technique [3] [4] a new development methodology for broadband RF systems will be created. This will be achieved through a coherent and systematic linkage of all development stages: measurement, analysis, CAD based design and RF system testing. The resulting methodology would, for the first time, utilise the complete nonlinear information within the emergent military RF system. At present, nonlinear information is only available at few of the development stages with very limited capabilities to transfer it across development stages. This is due to theoretical limitations as nonlinear information is automatically lost when exported into present design packages; examples of which include S parameter or power spectrum measurements.

The approach described in this work allows all subcomponents and their complex nonlinear interactions to be fully accounted for. Therefore, the impact of a single design parameter on a complete RF system can be determined. This allows the investigation of design parameter sets to give the optimum performance of the complete RF system and not just its subcomponents. An example is the development of high power transmitters where power amplifiers and antennas are developed separately with little or no consideration of their complex impedance changes over the operational bandwidth leading to sub-optimal designs and performance parameters. This issue takes on additional significance in broadband RF systems, where complex interfaces between sub-components are numerous.

The methods used in the design of Microwave Power Amplifiers (MPAs) depend upon the tools available. When all that were available were S parameters, small signal

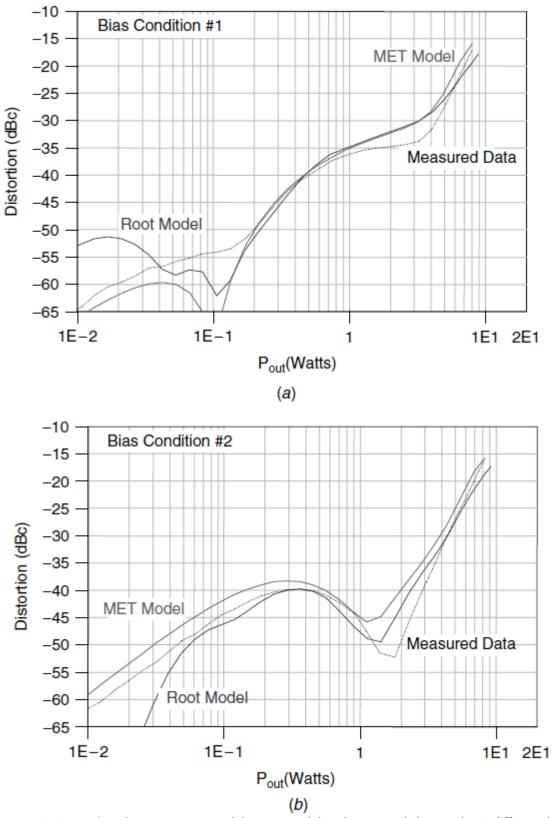

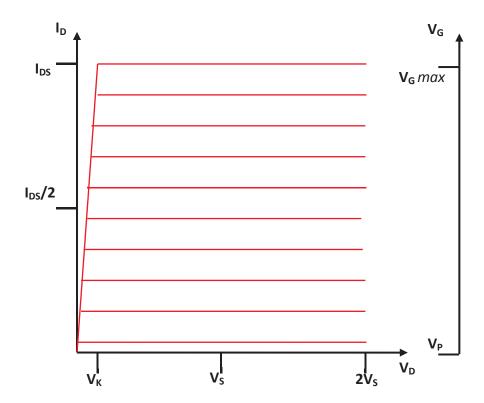

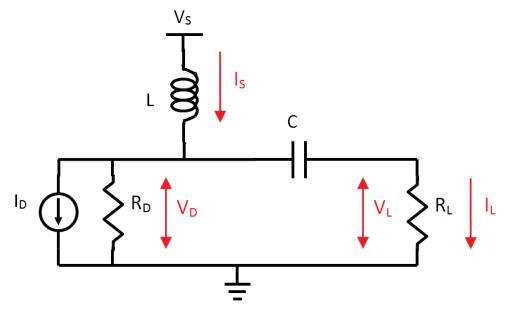

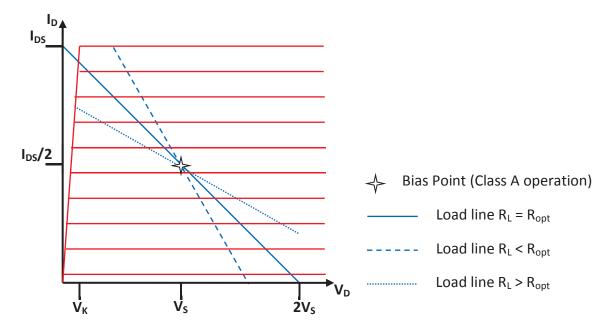

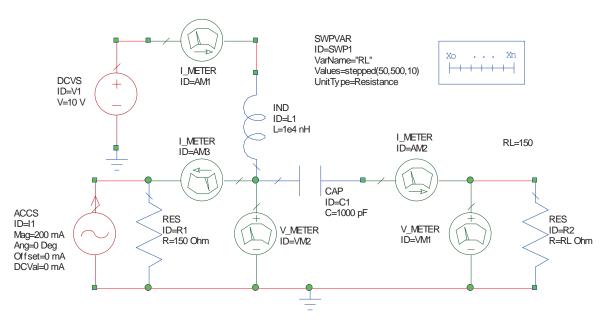

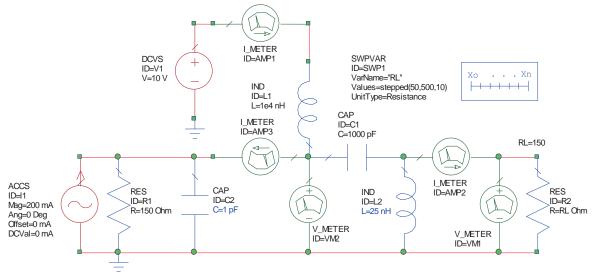

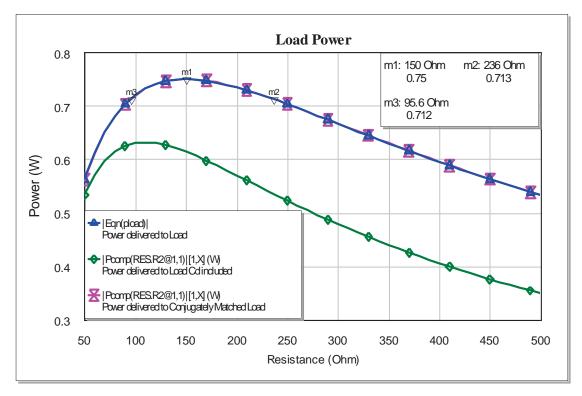

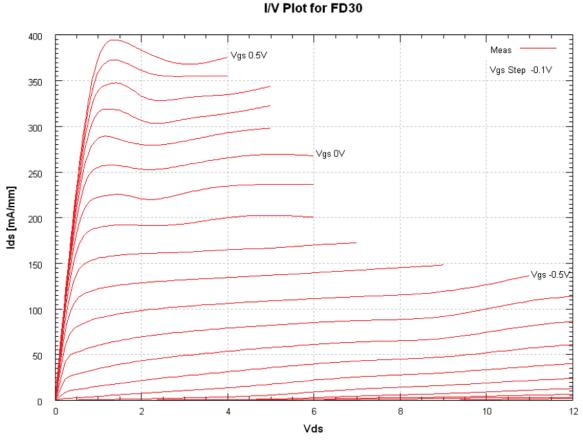

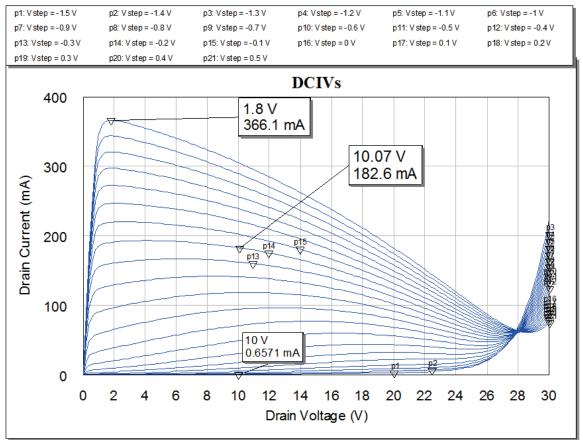

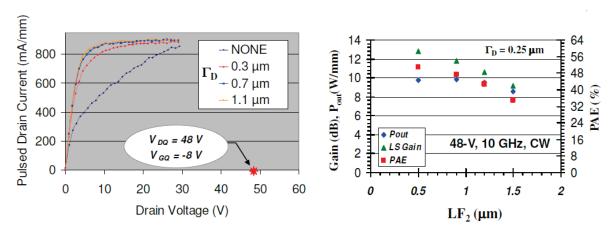

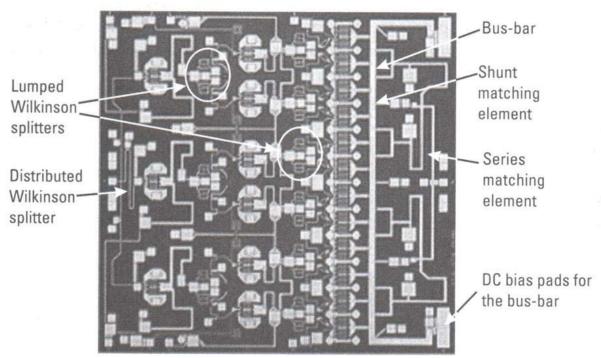

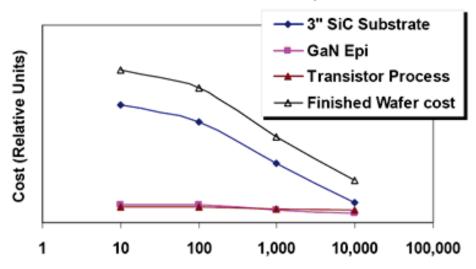

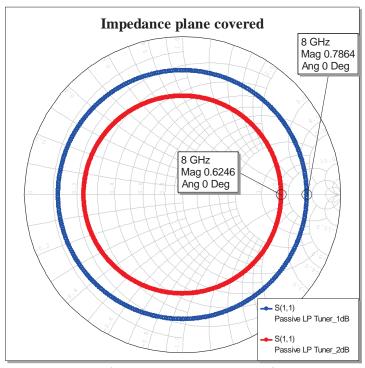

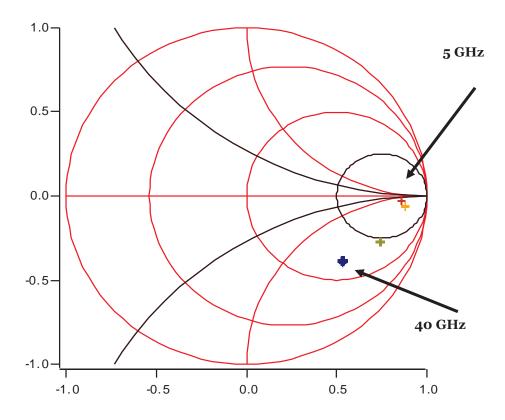

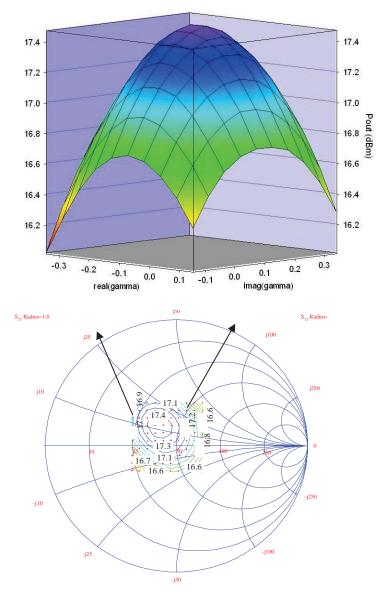

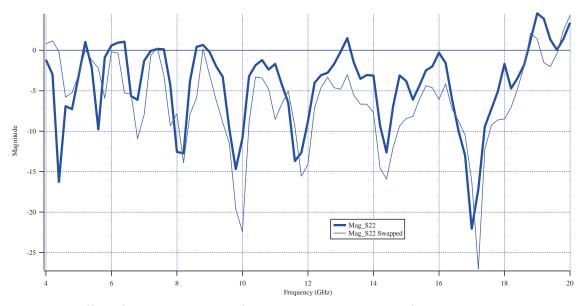

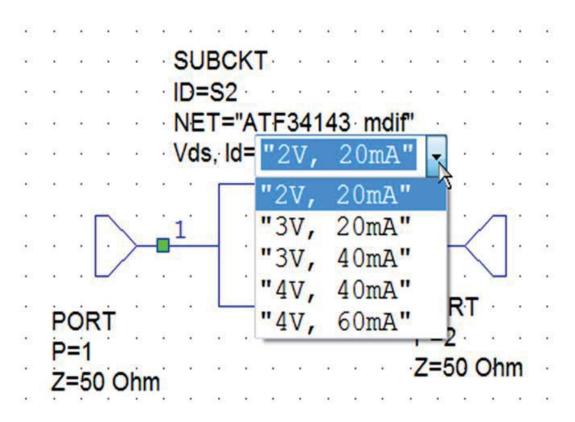

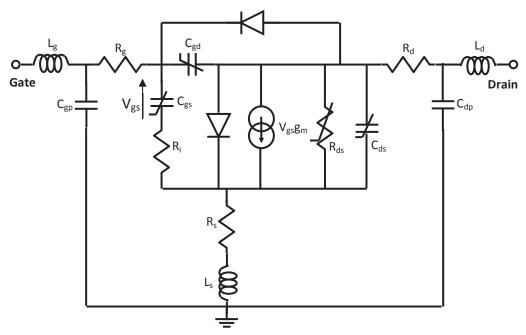

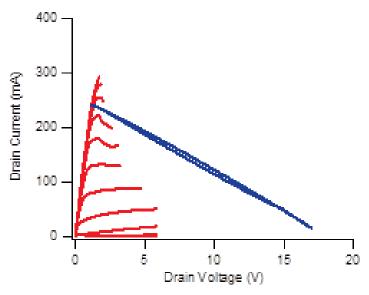

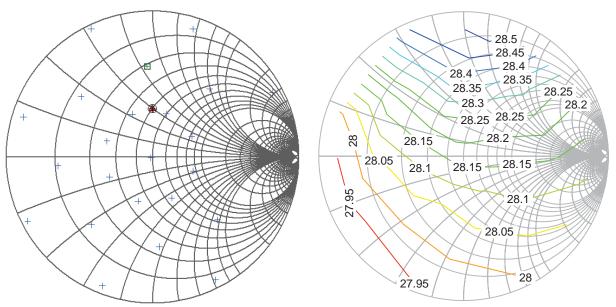

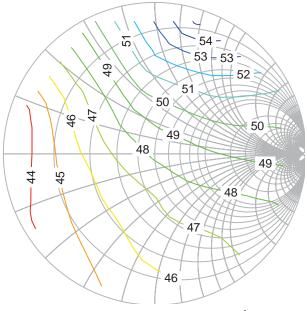

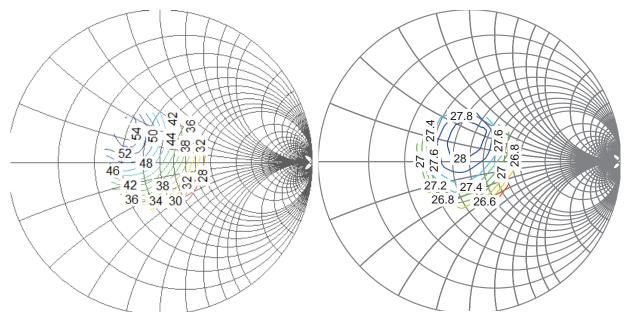

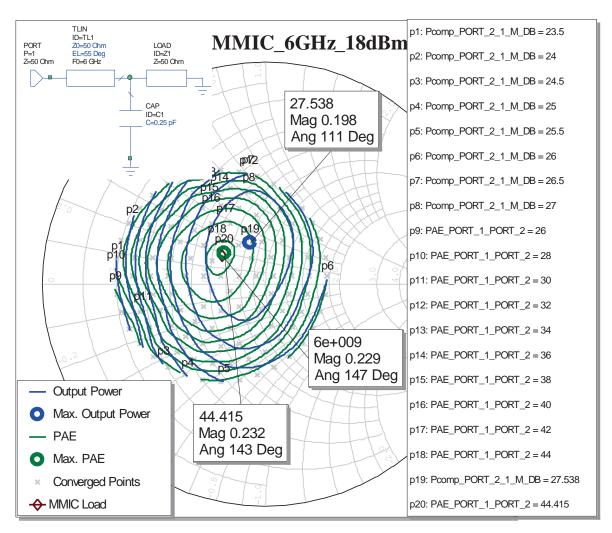

(because high output power, S parameters were difficult to measure - S22) data was used to design the best matching circuits and then the design would be tuned on the bench. One of the most difficult parts of which was knowing when to stop working on the unit, i.e. when the optimum performance been reached. In fact this approach is often still used for new processes/devices before models are available, [5]. To some extent the improvement in design tools has been a 'leap-frogging' of that of simulation, models and measurement capability. At first it didn't matter very much that the models were very crude, because the capability of the simulators was very limited. As these have improved (see Chapter 5, Nonlinear modelling) it has highlighted the deficiency of the models. These in turn put an emphasis on the measurement methods. Load pull techniques which had depended on short circuit tuners being adjusted for maximum performance, (Pout, PAE etc.), and then the tuner impedance being measured, were hugely labour intensive and required deembedding which with the basic capabilities of hardware and software was no easy matter, began to give way to automated systems. These allowed large areas of the impedance plane to be 'mapped' thus providing the designer with evidence, not only of the location of the optimum load point but also the sensitivity of the performance characteristic to load impedance. However, as frequencies increased, the losses between the tuner and the device meant that the high reflection coefficients required, firstly with high power device fundamental loads and then with high efficiency harmonic tuning, could not be realised. Also load pull measurements on their own did not provide a complete solution as there was no way to directly incorporate this data with a nonlinear simulation package. The design engineer could construct output matching circuits to produce an impedance close to the measured optimum but the measured data could not be directly accessed by a simulator. At this point the increased computing power now available on the desktop allowed the model designers to increase the number of elements in the model and alongside new optimisation algorithms allowed them to take advantage of the increased amount of device data that was now being generated by the measurement systems. No single model has been able to capture all the nuances of device behaviour across the full range of operating conditions, as can be seen from the vast range of models developed. Some very good models were developed which were optimised to a particular narrow frequency range and specific bias conditions (such as the Motorola METModel and the Root Model), Figure 1-2, however behaviour away from these conditions and frequencies (even by a few percentage points) could produce very inaccurate simulations.

Hence the approach successfully employed [6] was to fit trusted large signal models to measured DC and small signal behaviour and to compare the large signal performance with load-pull data measurements. For narrow band applications (<30% bandwidth) such an approach produces accurate simulations, however required DC and small signal measurements as well as the large signal to ensure that the model was accurate, and the optimisation of the model is not a trivial process in itself.

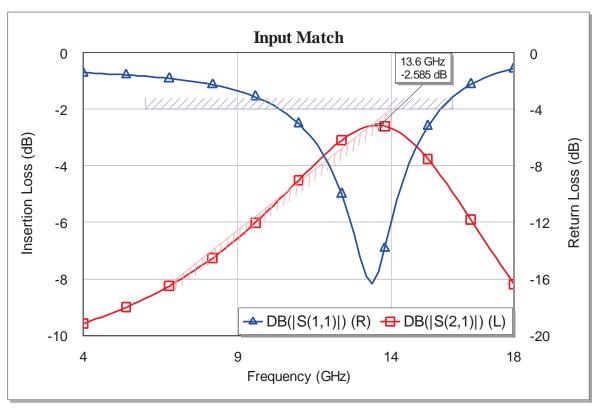

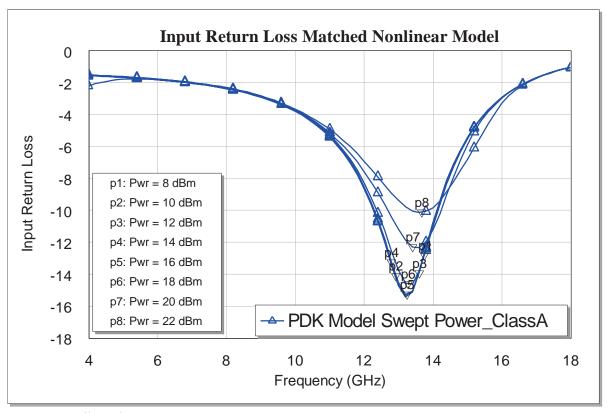

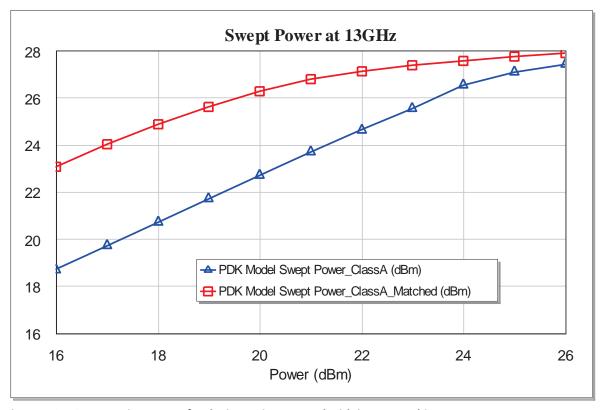

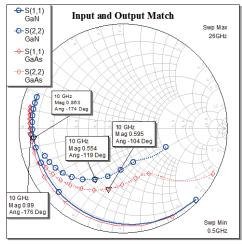

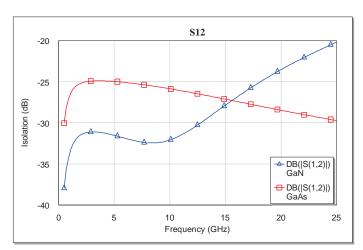

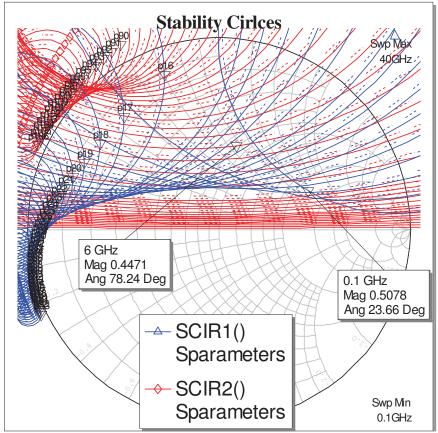

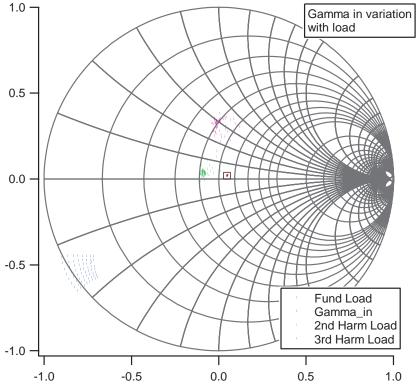

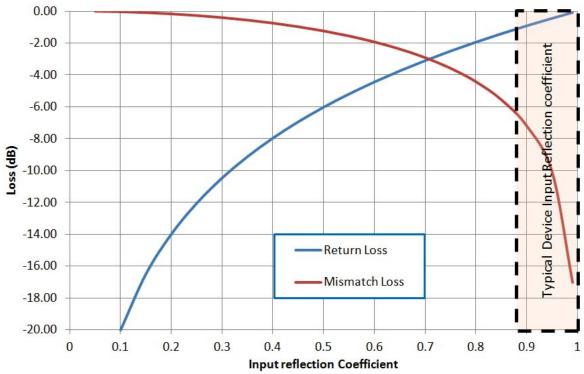

Improvements in modelling continue to be made, for example Cree included the effects of self-heating within the model [7], which assisted with one of the key differences between class A and class B biasing. When a model was received it was rare for it to include a description of the acceptable operating environment, thus it was still necessary for engineers to test devices to be used, to prove the veracity of the device models. A difficult parameter to accurately model is the transistor input reflection coefficient, partly due to its value, (high reflection coefficients) and partly due to its sensitivity (at high frequencies) to the device load impedance (due to finite S12). Although in power amplifiers the input impedance is less critical than the output impedance, it is still important in the design of the input matching network, both to avoid excessive input currents at saturation and to maximise PAE, {1-1}.

Figure 1-2, Comparison between MET Model, Root Model and measured data under 2 different bias conditions, from [39].

$$PAE = \frac{(P_{out} - P_{in})}{P_{DC}}$$

{1-1}

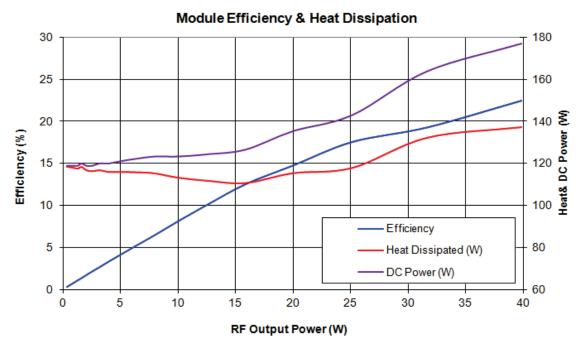

Amplifier efficiency can be easily improved by operation in classes 'above' class A whereby the device(s) are operated at a lower current; the RF signal itself turning the device on. The advantage of class A is increased linearity, and typically higher gain and output power. However these generalities will be shown to be only rough approximations, heating in particular greatly complicates the actual operation. A less efficient transistor will generate more heat, gain and output power are inversely proportional to temperature, thus a more efficient device may run cooler and therefore under certain operating conditions produce more power and gain than its equivalent class A configuration. Hence an important development in modelling has been the incorporation of self-heating [7], which is essential in accurate power amplifier simulation. In saturation the 'normal' biasing conditions change; the RF drive signal itself changes the quiescent bias point. As will be shown, with the correct configuration of load impedances the nominal 50% rule for maximum class A PAE operation can be 'broken'. It should be remembered that broadband class A amplifiers do not typically get close to this 50% figure for efficiency (PAE should be used as the Figure of Merit, FoM, particularly in broad band amplifiers where stage gain is often low), with results in the 20-30% range being typical, [8].

Returning to device impedances, for inter-stage matching in particular it is important to have accurate knowledge of the input and output device impedances, which has previously meant large signal S parameter measurements, [9]. It has long been recognised, [8], that to maximise the PAE over wide bandwidths there is a need for models that are not only accurate over the operating bandwidth, but at the harmonics as well. However in the classic work [2] Cripps wrote, "More and more, one is driven to the conclusion that the best way of deriving accurate models for RF power transistors is to build amplifiers, even non-optimized ones, and fit the combined circuit and device models to the measured results". Whilst possible for narrow bandwidth applications, this is obviously not suitable for wide bandwidths; however the idea of measuring actual device performance within the desired impedance environment does have considerable merit and has been reported earlier, [10]. What has been missing is the ability to fully and flexibly measure the device behaviour and capture this information in a manner applicable to modern microwave design software.

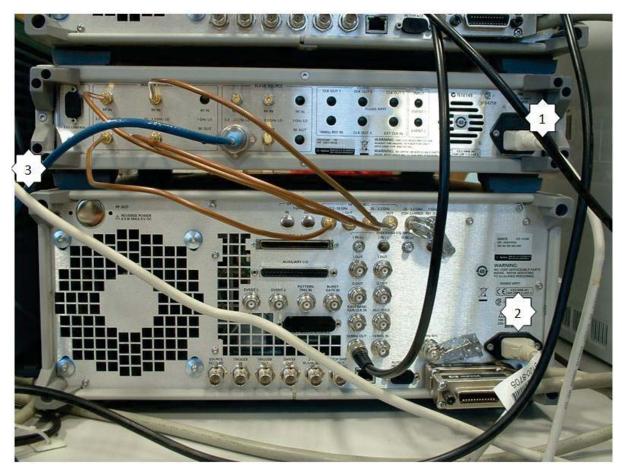

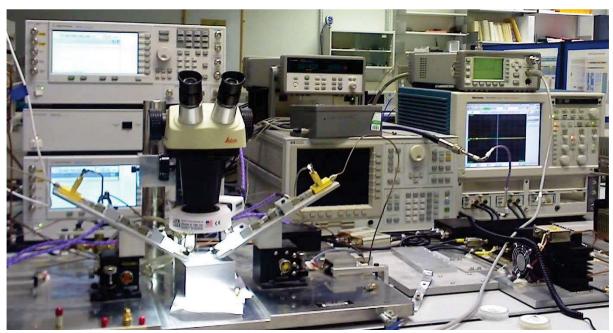

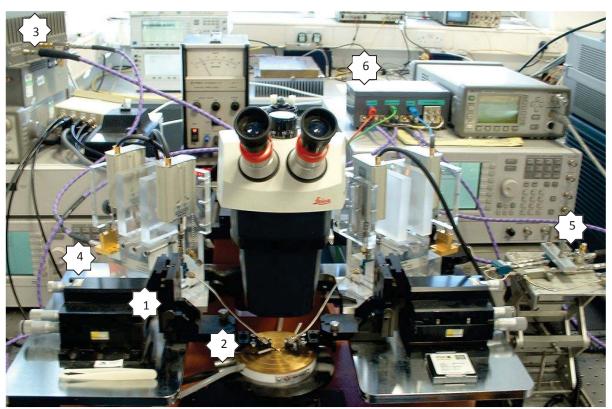

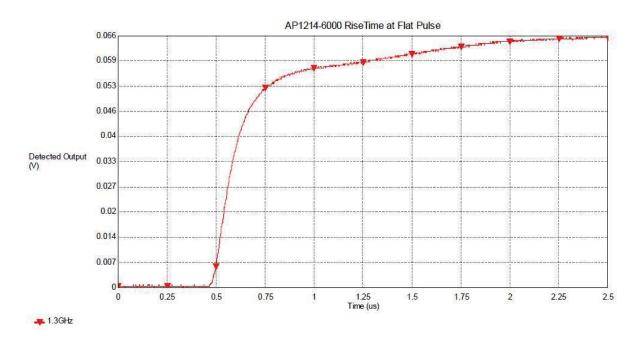

The research at Cardiff University sought to bring these various elements together, the improvement in measurement speed and capability, accurate modelling and their integration into the CAD environment. The early work, [3], [4] was centred on the narrow band frequencies for the communications industry. The research described in this work started with the creation of a wide bandwidth (1-40 GHz) Active Load Pull (ALP) measurement system, and the implementation of a Direct Look-Up Table (DLUT) Model within the MicroWave Office (MWO) design software, mirroring the developments in the narrow band application space, but in a much reduced time period thanks to the frame work defined by those who had started the investigations. During the course of the research the measurement control software was completely redeveloped and the approach to the DLUT was changed to looking up PHD model coefficients. Such progress is at the same time a great boon and a great frustration. A part of you would like to wait until "all the i's are dotted and the t's crossed" before pursuing the new approaches; however the advantages offered by the improvements are such that they cannot be ignored. Hence some of the early work in this research has used methods that, whilst still valid as an approach, have already been overtaken by the improved models that we can use now. The proposed design methodology arising from this work will require the commercialisation of the measurement system and the integration of the measurement and simulation environments, two areas which in the industrial world have tended to be kept separate. When models can be produced quickly and viewed in the CAD tool, immediately designers will have the freedom to make changes based upon arriving at the optimum solution rather than compromising by living within the boundaries of established proven models. There will also be speed and economic benefits as any short comings in the measurements, for example impedance or power levels that have not been covered, will be quickly identified and acquired. It is much easier to acquire data whilst a measurement is in operation than to have to return to it later.

The work done by colleagues at Cardiff University will continue to develop these capabilities, whilst it can be seen that the industry is awakening to the insight and potential of the tools by the number of companies now offering large signal nonlinear measurement capability. The beauty of the Cardiff approach is that the investment in the model creation and thereby the understanding of the device truly becomes an asset of the company undertaking the work; it is knowledge that should deliver a competitive advantage, both in

the performance of the product, development cost and time to market (these latter points primarily due to reduced development time).

# 1.2 Applications of Broadband Amplifiers - Requirements and Performance Drivers

The term "broadband" has become somewhat over used in recent years. For example ultra-wideband (UWB) systems were defined by the United States Federal Communications Commission (FCC) as signals occupying a bandwidth greater than 500 MHz or at least 20% of the carrier frequency [11]. Associated with this decision the FCC allocated bandwidth between 3.1 and 10.6 GHz for UWB applications, thus in practice an UWB system may have a percentage bandwidth of <10% at 10.6 GHz. In the case of the research described in this thesis broad bandwidth is considered as amplifiers where the percentage bandwidth exceeds 50%. In these cases a straight forward optimal matching approach will not yield an adequate result, as will be described in section 1.3. Systems requiring such large bandwidths are found in many fields including:

- Electronic Warfare (EW) (including jamming).

- Radar.

- Television Broadcast

- Frequency hopping (covert) communications systems.

- Electro Magnetic Compatibility (EMC) Testing.

- High data rate fibre optic communication systems.

- Multi-channel communication systems.

- Test Instrumentation.

Some of these applications require multi-octave designs, others are satisfied by having switched amplifiers still with broad bandwidths, but not covering the complete range. In EMC testing applications these amplifiers will frequently have different output power capabilities related to both the field strength required and the gain of the transmitting antenna. As with all designs there is a compromise between competing requirements, for example in a multi-band mobile phones there are a number of narrow bandwidth Power Amplifiers (PAs) which are selected as required. Thus there are switch losses associated with this approach, however it has currently been a more practical solution than using a single

broadband amplifier to cover all of the bands in one, as the individual amplifiers including the switch loss can still achieve the required output powers with better efficiency.

Efficiency is an obvious key driver in a mobile phone in order to maximise battery life. In EW systems its importance depends upon the vehicle; it may be of little importance on a naval vessel, but critical on an airborne craft. As the PA is at the end of the power train, efficiency savings at this stage have a multiplier effect. If we were to consider a very simple case of a 1 W transmit PA which had a Power Added Efficiency of 35%. If the output efficiency were increased by just 5% the impact on the overall system would be to decrease the heat generated in the PA and power supply (assuming this ran at an efficiency of 85%) by ~18% and the prime power required by ~12%. This reduction in heat generated would reduce the weight, size and power requirements of any cooling systems and thus have an additional benefit to the operation of the system, possibly allowing greater range and flight time.

Although such drivers would not carry as much weight with instrumentation systems there are still significant benefits in terms of reliability (running devices at a lower temperature), cost (smaller power supply required), noise (fewer/slower fans), besides the environmental benefit of consuming less power. It can thus be seen that in most systems the ability to improve the efficiency is an attractive proposition. The difficulty has largely been in achieving this in line with other aspects of the design.

Considerable effort has been made in making PAs more efficient but often at the expense of other parameters such as linearity. Non linearity leads to distortion of the fundamental signal, interference between communication channels and added complexity in control systems (the linear relationship between input and output power is broken). To combat this ever increasingly complex solutions have been sought, from purely analogue feed forward systems [12], to digital pre-distortion and most recently envelope tracking and dynamic biasing [13]. These however come at a price, be it of additional components (and hence weight, size and cost), detailed system characterization (time and test equipment) or sacrificing peak performance (to benefit average). Thus efforts that increase the primary efficiency of an amplifier stage without negatively impacting upon the other parameters will, if not remove the need for additional measures, at least make their requirements less stringent.

# 1.3 Broad Band Matching

Intrinsically, matching is the arrangement of a circuit such that a certain optimum performance is achieved. In low noise amplifier designs [14] there exists an optimum input reflection coefficient,  $\Gamma_{OPT}$ , which is required to be presented to the input of the device to achieve the minimum noise figure; this is not however the same impedance required to conjugately match the device for maximum gain. Maximum power transfer occurs when the source and load impedances are equal and has been understood since the early days of electric motors run from batteries [15]; in RF circuit design there is the added complexity that impedances (devices and loads such as antennas) are rarely purely resistive and for maximum power transfer the reactive element must also be taken in to account. A conjugate is the equal but opposite, for example the reactance of an inductor (jωL) that cancels out (resonates) a capacitor (-j/ωC). This makes clear the fundamental problem of broadband matching, this cancellation occurs at one frequency,  $f_{res}$ , {1-2}, and away from this frequency either the inductive or capacitive reactance dominates.

$$f_{res} = \frac{\omega_{res}}{2\pi} = \frac{1}{2\pi\sqrt{LC}}$$

{1-2}

Broad band matching circuitry seeks to resolve two key problems, (i) how to achieve a wider bandwidth with a minimum reflection coefficient and (ii) how to minimise the number of matching element sections for a given bandwidth. The issue has been around a while, having been addressed by two of the fathers of circuit theory, Bode and Fano, [16] [17]. The Bode-Fano Criterion states that for a specific load impedance there exists a theoretical minimum refection coefficient that can be achieved with arbitrary lossless matching network. The lossless element is important, in practice all matching elements will have some resistive loss, but in output circuits for power amplifier applications for maximum power transfer very low loss elements will be employed approximating to the lossless condition. In other applications where loss can be tolerated wider bandwidth matches can be achieved, indeed resistive matching can achieve very wide bandwidths (at the cost of insertion loss). For the most common RF and microwave device output equivalent circuit approximation, a shunt resistor capacitor combination, the Bode-Fano Criteria states that:

$$\int_{0}^{\infty} \ln \frac{1}{|\Gamma(\omega)|} \, \partial\omega \, \leq \frac{\pi}{RC} \tag{1-3}$$

The minimum reflection coefficient within a bandwidth  $(\omega_2 - \omega_1)$  is:

$$|\Gamma|_{min} = exp\left(\frac{-\pi}{RC(\omega_2 - \omega_1)}\right)$$

{1-4}

Again these equations {1-3} and {1-4}, are idealised and rely on an infinite number of pure matching elements, and thus determines the best that can be achieved *in extremis*. Also note that the definition of bandwidth is up to the user, but needs to be consistent throughout. In filter applications it is sometimes considered as the 3dB bandwidth, i.e. a measure to the points where the insertion loss has fallen to 3dB. Alternatively it may be defined in terms of the pass band ripple. Similarly with amplifiers, although in this case the bandwidth is often defined and an allowable minimum gain or gain variation within the pass band stated.

A practical solution to what can be achieved is to consider the matching network as a Chebychev matching transformer with the ripple made equal to  $|\Gamma|_{min}$ ; the number of elements required are available from standard filter tables, [18]. An alternative approach was suggested by Carlin, [19], rather than using idealised equivalent circuits for the output of the device the technique uses measured impedance load data,  $Z_L(j\omega) = R_L(\omega) + jX_L(\omega)$  over the frequency range of interest. Matching networks can be designed by considering only the resistive elements of the source and load initially, the topography of the matching is then selected such that the parasitic element (e.g. capacitance) is absorbed into the first element of the matching network.

It is necessary at this point to introduce the concept of Quality factors, Q, as they are integral to bandwidth. There are a number of subtly, but critically different forms of Q and it is important to define clearly which form is being used. Unloaded Q, or  $Q_U$  is defined by the centre frequency  $\omega_0$  of the network and its bandwidth and independent of any other parameters:

$$Q_U = \frac{\omega_0}{(\omega_2 - \omega_1)} \tag{1-5}$$

$$\omega_0 = \sqrt{(\omega_1 \omega_2)} \tag{1-6}$$

The loaded Q,  $Q_L$ , {1-8} is by contrast dependent on the source resistance,  $R_S$ , the load resistance  $R_L$  and the Q of the matching elements themselves,  $Q_E$ . The Q of the matching elements is defined by their ability to store charge and is the ratio of the stored energy to

dissipated energy. For capacitors this is the ratio of the capacitive reactance to the Equivalent Series Resistance (ESR) {1-9}, and for inductors the inductive reactance to the series resistance of the coils, {1-10}. For distributed elements the Q is more complex, but if we consider stored charge gives a good indication as to value. An important caution is that Q is frequency dependent and thus in components usually at a specific frequency(s).

$$R_P = \frac{R_S R_L}{R_S + R_L} \tag{1-7}$$

$$Q_L = \frac{X_P}{R_P} \tag{1-8}$$

$$Q_C = \frac{X_C}{ESR}$$

{1-9}

$$Q_{IND} = \frac{X_L}{R_S} \tag{1-10}$$

Thus if we redefine  $\{1\text{-}4\}$  in terms of  $Q_U$  and  $Q_L$ , we can see the minimum reflection coefficient we can achieve:

$$|\Gamma|_{min} = exp\left(\frac{-\pi Q_U}{Q_L}\right)$$

(1-11)

Turning the expression round we can also see what bandwidth can be achieved for a particular reflection coefficient and 'quality' of matching components:

$$\frac{(\omega_2 - \omega_1)}{\omega_0} = \frac{1}{Q_U} = \frac{-\pi}{Q_L \ln \Gamma_{min}}$$

{1-12}

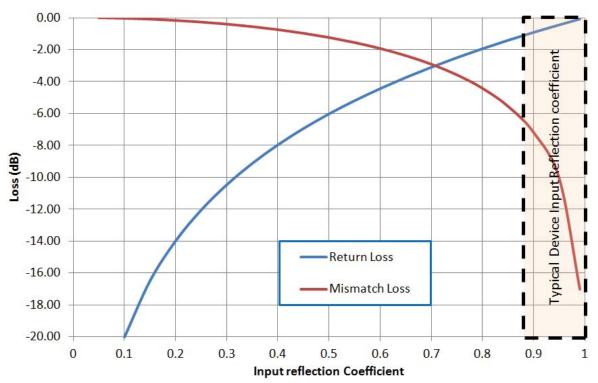

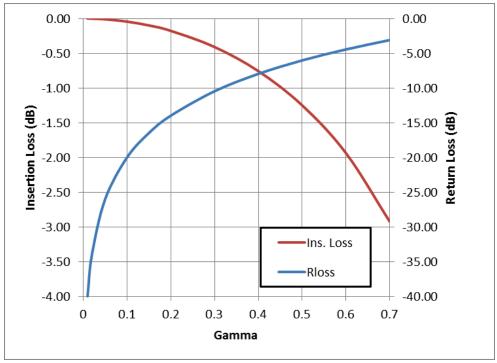

More commonly we define amplifiers in terms of Return Loss (RL) and this is related to reflection coefficient by  $\{1-13\}$  and the insertion loss,  $L_T$ , as a result of the mismatch between impedances is defined by  $\{1-14\}$ .

$$RL(dB) = -20\log|\Gamma|$$

{1-13}

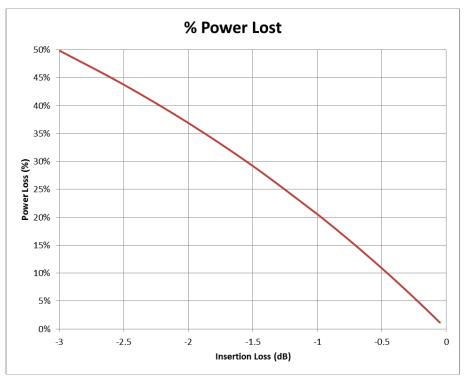

$$L_T = -10\log(1 - |\Gamma|^2)$$

{1-14}

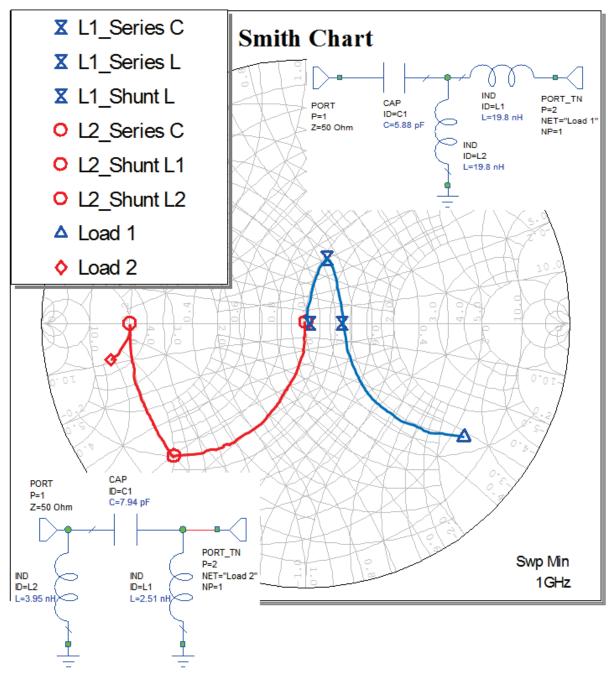

A common approach to matching is to use either "T" or "Pi" circuits, the name coming from the configuration of the matching elements. The Smith Chart, [20] provides a useful tool in visualising the effects of the different combinations of elements. Series elements follow the impedance contours, whilst shunt elements the admittance circles. Figure 1-3 shows how the combination of series and shunt elements can be used to 'move'

Figure 1-3, "T" (blue) and "Pi" (red) matching approaches. Load 1:  $300\Omega//1pF$ , Load 2:  $10\Omega//10pF$  from the load impedances (Load 1 is  $300\Omega$  with 1pF parallel capacitor and Load 2 is  $10\Omega$  with 10pF parallel capacitor) to  $50\Omega$ . Of course there are many other combinations that would produce the same results.

Matching elements are not pure elements. For discrete components besides the parasitics intrinsic in the construction, inductance in leads, resistance in metallisation, unwanted capacitance between plates, etc. there are also those associated with connecting tracks (pads) and the circuit board itself. In MMIC implementations the physical proximity of the components causes cross coupling and as frequency increases the phase length of

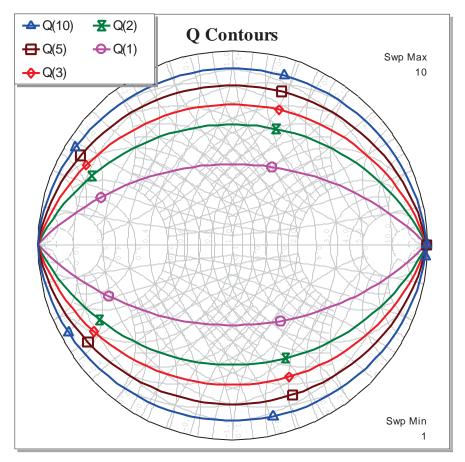

Figure 1-4, Contours of constant Q (Q=1, 2, 3, 5 and 10)

matching elements prevents them from behaving in the ideal manner. Although these factors will complicate the matching circuit design, understanding their implications is more important than the fact that they exist. In input matching and decoupling circuits losses can be beneficial in improving stability and parasitic elements can be included in matching circuit design thereby reducing the number of elements required. In the main output circuits (i.e. not bias lines) it is essential that losses are kept to a minimum, hence the use of high quality materials and components in these areas.

Plotting constant Q factors on the Smith chart produces contours where the impedance points lying on the contour all have a constant ratio of X/R from the impedance of the point R  $\pm$  jX. Figure 1-4 shows contours for Q ranging from 1 to 10. For a single transformation, bounded by the resistive centre line along the diameter of the Smith Chart and a constant Q contour, the transformation ration,  $R_{ratio}$ , is given by {1-15} [21] and for multi-section (n) matching the relationship becomes {1-16}. In practice in amplifier matching circuits the number of sections will rarely go above 4 due to the increasing insertion loss

\_

<sup>&</sup>lt;sup>1</sup> In filter design, particularly in low loss constructions such as waveguide, high number of sections (>10) are often used to achieve the required performance.

and reducing incremental benefit. It should be made clear that this solution does not necessarily realise the optimum matching solution, however it is probably the simplest approach and yields smaller component values.

$$R_{ratio} = 1 + Q^2$$

{1-15}

$$1 + Q^2 = \sqrt[n]{R_{ratio}}$$

{1-16}

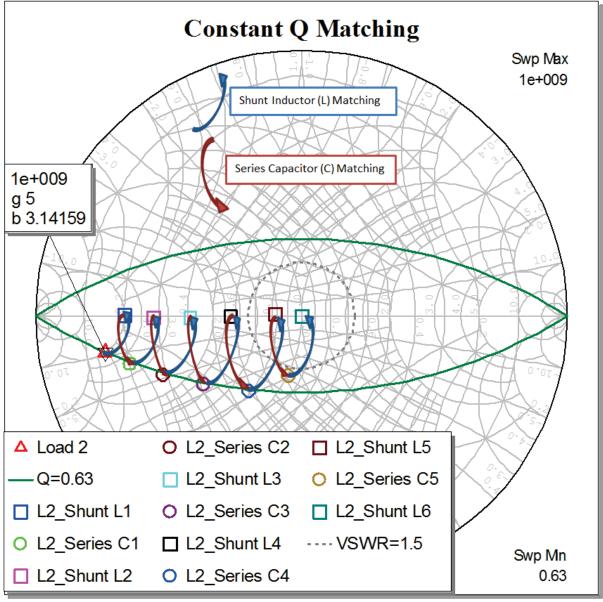

The Q curves can be employed to assist designing a broad band match. Starting from Load 2 of Figure 1-3, the normalised admittance of the load, G + jB, is 5 + j3.14, hence a  $Q \approx 0.63$ . If a successive Pi matching approach is taken until the centre of the chart is reached, staying within the Q contour of the load (Q = 0.63), then after 6 shunt elements and 5 series capacitors the  $50\Omega$ , optimum match is reached, Figure 1-5. Note that the final elements, C5 and L6 do not need to move between a point on the 0.63~Q curve to reach the centre of the chart. It is also worth noting that an 'acceptable' match may be obtained with fewer elements; also drawn on the chart is a circle of constant Voltage Standing Wave Ratio (VSWR – a common term to refer to the match of a load derived from the days when standing waves reflected from a load were measured with voltage probes). If a VSWR of 1.5:1 meets the match specification then a solution can be reached with two fewer elements.

Figure 1-5, Broadband matching staying within Q of load.

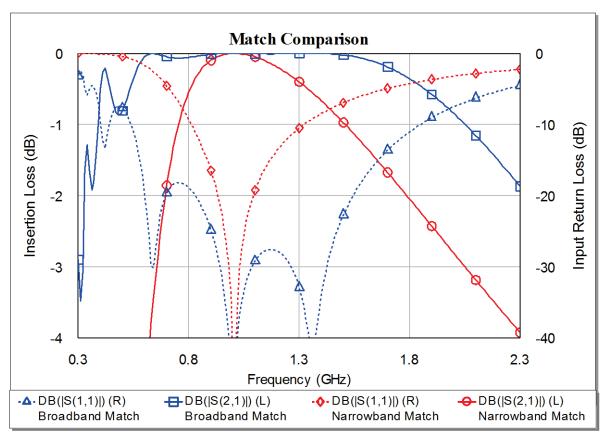

Comparing the bandwidth of the 3 element match of Figure 1-3 and the 11 element of Figure 1-5, it is shown in that there is a significant increase (as would be expected) using the broadband match, Figure 1-6. It should be remembered that these results are obtained using ideal elements with no resistive loss or parasitics, in practice these low insertion losses would not be obtained.

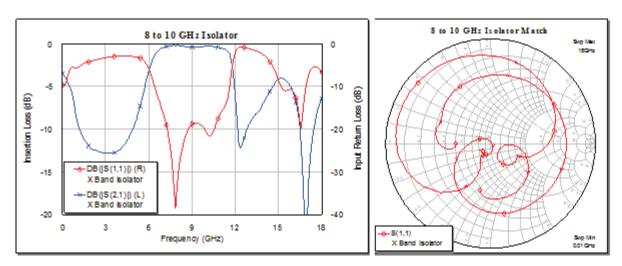

Figure 1-6, Comparison between 3 element narrowband and 11 element broadband match.

Calculating the corresponding values of return loss, mismatch loss and VSWR, it can be seen from Table 1-1 that although in order to maximise the power output we must minimise the loss due to mismatch, going beyond a return loss of 15dB ( $\Gamma$ =0.18) there is a diminishing return. Although this may seem trivial it is important to realise the implications of specifying a particular match for an amplifier. The better matched a transistor; the less power is required to meet a specification. Often an isolator will be added to the output of an amplifier in order to meet an output return loss requirement, but this may have 0.5 dB of insertion loss and will do nothing in terms of translating the output impedance of the device to  $50\Omega$ . Whilst there may be good system considerations for adopting an isolator (such as gain ripple on long cables) in PAs it loses hard won power. A solution based upon the best power match that can be achieved would be more efficient.

| Γ                                                                 | 0.1  | 0.18 | 0.2  | 0.25 | 0.35 | 0.4  | 0.5  | 0.71 | 0.8  |

|-------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|

| RL (dB)                                                           | 20   | 15   | 14   | 12   | 9    | 8    | 6    | 3    | 1.9  |

| L <sub>T</sub> (dB)                                               | 0.04 | 0.14 | 0.18 | 0.28 | 0.58 | 0.76 | 1.25 | 3.0  | 4.44 |

| VSWR                                                              | 1.22 | 1.43 | 1.50 | 1.67 | 2.1  | 2.33 | 3.00 | 5.85 | 9.00 |

| Table 1-1, Γ, Return Loss, Mismatch (Transmission) Loss and VSWR. |      |      |      |      |      |      |      |      |      |

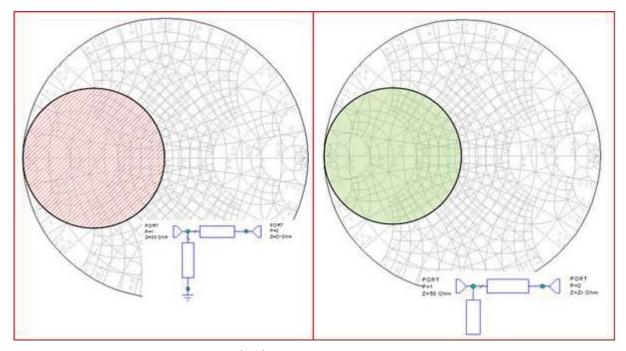

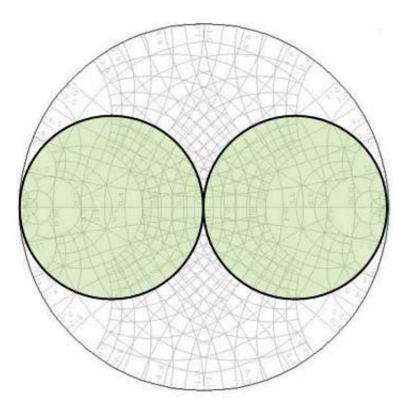

Any real impedance can be matched to the system impedance at a single frequency, the difficulty is doing it over a bandwidth and all amplifier circuits need to have at least a limited bandwidth to account for changes in behaviour with temperature. There are an infinite number of combinations of matching elements able to move from an impedance on one part of the Smith Chart to another [22]. However, because they are largely treated as pure lumped elements (capacitors and inductors) their use in MMIC PAs is restricted to an understanding of the theory, in practice the matching elements used are complex due to their distributed nature. The most common distributed matching elements are impedance transforming transmission lines and open and short circuit stubs. Combined with a series transmission line these can match an impedance over a defined area, this is best explained graphically as in Figure 1-7. High power transistor output impedances will typically lie within the green shaded area, (large periphery hence low resistance and high capacitance) and so often the first matching element will be an open circuit stub. In contrast lower power devices have a higher resistance and lower capacitance and can be matched with the shorted stub.

Figure 1-7, Stub matching approaches: (left) short circuit stub can match any impedance <u>outside</u> the red shaded area; (right) open circuit stub can match any impedance <u>within</u> the green shaded area. Impedance to be matched is to the right of the network.

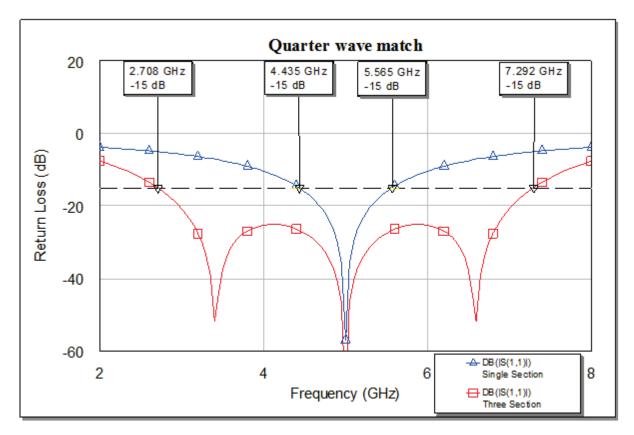

So far, these discussions refer to matching at a single frequency and to  $50\Omega$ . As a rough guide a single quarter-wave matching structure between impedances of a ratio of 6:1 can achieve a bandwidth of ~22%, (15dB return loss). Using multiple sections this can be

Figure 1-8, Comparison of the bandwidth achieved from 1 and 3 section quarter wave transformers between the same resistive loads.

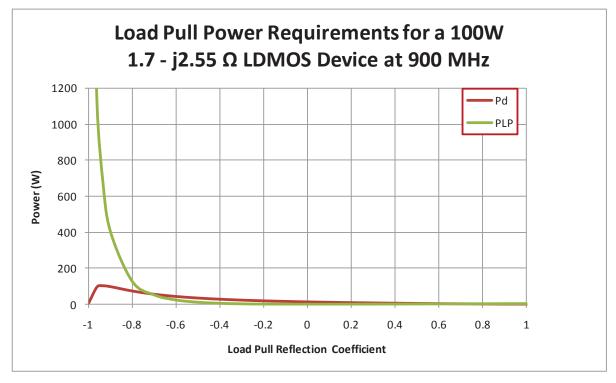

increased, e.g. matching the same load with 3 quarter-wave transformers, the bandwidth that can be achieved increases to ~90%. Clearly, wider bandwidths can be achieved by reducing the impedance ratio; hence the benefit of using higher voltage and wide bandgap materials such as GaN with higher output impedance and, conversely, why with technologies such as LDMOS<sup>2</sup> with its high output capacitance, only narrower bandwidths can be achieved in the microwave region. Figure 1-8 shows the improvement from 1 to 3 sections, using ideal transmission lines and purely resistive loads. The impedance of the quarter wave matching line,  $Z_T$ , is determined from {1-17}. For multiple sections one first needs to calculate the intermediate impedance between the sections,  $Z_{i(n)}$ , [23], {1-18}, where N is the number of steps, and  $R_L$  the load resistance. In the case of the first step  $Z_{i(1)}$  then the impedance can be found from {1-20}.

$$Z_{T} = \sqrt{(Z_0 \times R_L)}$$

{1-17}

\_

<sup>&</sup>lt;sup>2</sup> LDMOS devices are made with high operating voltages (~50V) for high power operation, however to handle the power the periphery is very large which leads to very high output capacitance.

$$Z_{i(n)} = \Delta \times Z_{i(n-1)} \lim_{2} N$$

{1-18}

where,

$$\Delta = \left(\frac{R_L}{Z_0}\right)^{\frac{1}{N}}$$

{1-19}

$$Z_{i(1)} = \Delta \times Z_0 \tag{1-20}$$

Using impedance transformers any impedance within the areas defined in Figure 1-9 can be matched. This assumes an infinite range of transformer impedances is available which, in microstrip, is typically limited to between 25 and  $90\Omega$ . If coplanar waveguide (CPW) is used [24] a wider range of impedances (~15 to  $120\Omega$ ). There is much debate amongst MMIC designers over whether it is better to use microstrip or CPW circuits. The differences are not only in the transmission characteristics of the two approaches but also in the available models and the range of their application, ground connections, processing costs and density and implementation of components on the surface. In power amplifiers a key consideration is the thermal; heat sinking requires good metal connections to the backside of the substrate. In both microstrip and CPW, although the impedances can be determined mathematically, [2], it is often simpler to put approximate values in a simulator and allow the optimiser to produce the best possible result within practical constraints.

Figure 1-9, Single transformer matching space.

Figure 1-10, Double short transformer matching.

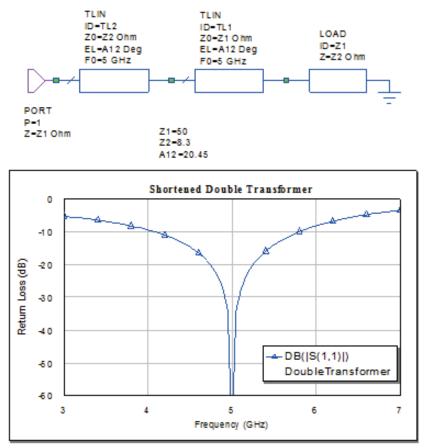

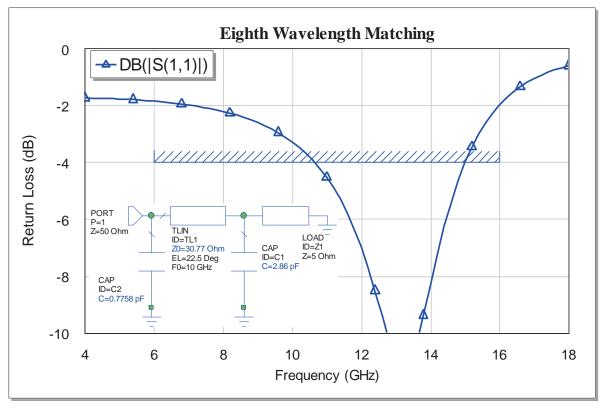

A number of other topologies offer impedance matching, without the size penalty of  $\lambda/4$  structures. Similar performance to the  $\lambda/4$  transformer can be achieved using two lines of impedances the same as those of the terminations, [23], as shown in Figure 1-10. In this case the combined length of the two lines is less than that of a single  $\lambda/4$  transformer with little sacrifice to the bandwidth. A similar version to this involves using a capacitively loaded  $\lambda/8$  line. This is particularly useful if the load impedance that is being matched to has a capacitive reactance as this can be absorbed into the matching capacitance. Figure 1-11 shows the circuit for a  $\lambda/8$  capacitively loaded transformer used to match 12.5 to 50 $\Omega$ , where the capacitors and the line impedance were allowed to vary in the CAD circuit optimiser, Figure 1-11 (a). If this approach were to be used to match to a load of 12.5 - j80.0 (a 0.4pF shunt capacitor at 5 GHz) it would be possible to replace the 0.2pF with the 0.4pF capacitance of the load and re-optimise with the result shown in Figure 1-11 (b), varying only the line impedance and the port 1 capacitor. A further advance on this is to replace the output shunt capacitor with an o/c stub, Figure 1-11 (c). This has a slightly narrower bandwidth due to the lower limit on the impedance of  $25\Omega$ , but is a printed component. In MMIC solutions the lumped element may be a better solution as it could be smaller, but

would depend upon the impact of the inductance of the via and the actual electrical performance of the MIM (Metal-Insulator-Metal) capacitor.

The discussion so far has used ideal components; capacitors, inductors and transmission lines of a fixed impedance and electrical length. In practice all components used in RF and microwave circuits have characteristics determined by their physical construction and assembly; capacitors have loss, additional capacitance including that between the terminals and ground and inductance, and these elements are distributed throughout the component. The importance of this distribution increases with operating frequency, as the size gets closer to a wavelength. Even ground connections have a physical length associated with their implementation which has an increasing impact with frequency.

Figure 1-11, Capacitor loaded  $\lambda/8$  transformer matching.

Distributed elements are those structures whose physical dimensions fundamentally determine their electrical characteristics. Hence the tolerances and repeatability of the manufacturing processes has a direct effect on the performance. On alumina circuits and

MMICs, capacitors and resistors can be incorporated directly during the circuit fabrication process. For resistors, as with their lumped element equivalents, resistive pastes can be used in thick film circuits or a NiCr layer in thin film. These resistive materials are specified in terms of ohms/square and the resistance, R, is proportional to the ratio of the length, I, to the width, W,  $\{1-21\}$ .

$$R = resistivity \times \frac{l}{w}$$

{1-21}

The width can be adjusted to match that of connecting transmission lines. Common resistivities are 50 and 100  $\Omega/\text{sq}$ .

Capacitors can be incorporated by putting down a dielectric on top of conductors and then overlapping with a conductive paste/plating. Although these have been proposed for use in soft substrates, particularly using conductive inks, there has not been a large scale take up as yet. Inductors on microstrip can be difficult to distinguish from high impedance lines. The exception is where the line is wound in a spiral (round or square sided) and is popular in MMIC applications. This is used less frequently in hybrid circuits due to the relatively large size and lower Q compared to wound components. Similarly, interdigital capacitors are used less often in hybrid circuits. An exception is when edge coupled lines used in some bandpass filter applications fulfil two functions, that of filtering and DC blocking. For narrow band applications where the volumes are extremely high, edge coupled lines may be justified on their own due to cost considerations.

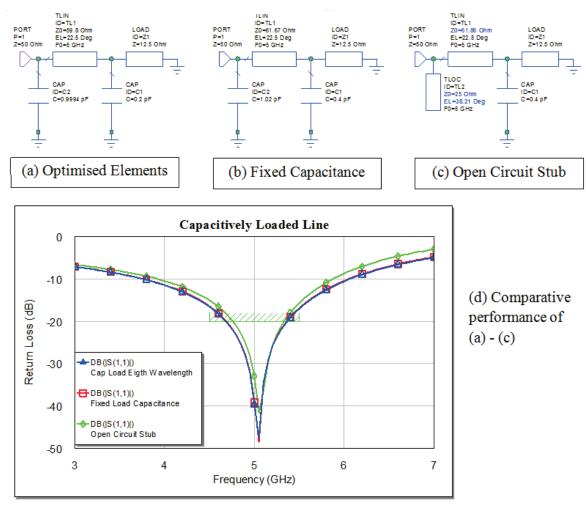

The most common distributed components are transmission lines. As mentioned earlier, the impedance ranges that can be created are limited due to moding and etch tolerances. In practice, circuit structures are also limited by the ability to simulate them within design tools. Distributed circuits have re-entrant properties, that is, the impedances repeat (approximately) at multiples of 90 and 180°. The behaviour of distributed components with frequency differs to that of pure elements. For example, at a specific frequency a shunt inductor of impedance  $X_L$  can be replaced by a shorted transmission line of impedance,  $Z_0 \tan\theta$  where  $Z_0$  is the characteristic impedance and  $\theta$  is the electrical length. However, whereas  $X_L$  increases linearly with frequency, the line impedance increases with  $\tan\theta$ , which is periodic. There are a variety of equivalents between lumped and distributed components, some of which are given in Figure 1-12. The realisation of distributed series

In the special cases where  $\theta$ =90° (quarter wavelength) at the resonant frequency:

And when  $\theta$ =180° (half wavelength) at the resonant frequency:

Figure 1-12, Equivalent Lumped and Distributed Circuits.

capacitors, as mentioned above, is very difficult in hybrid applications. An exception is where very small values are required which can be achieved by using narrow gaps.

A short circuited (S/C) transmission line or S/C stub is basically a transmission line with one end terminated in zero impedance, but this becomes more difficult to achieve as

Chapter 1: Introduction to Novel MMIC Design Process Using Waveform Engineering

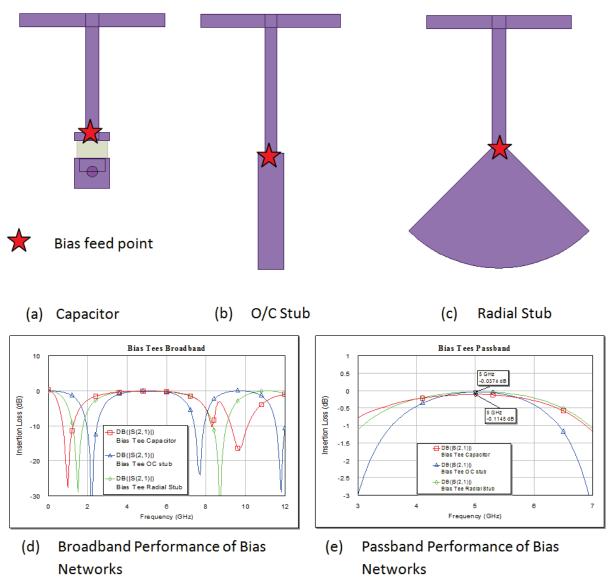

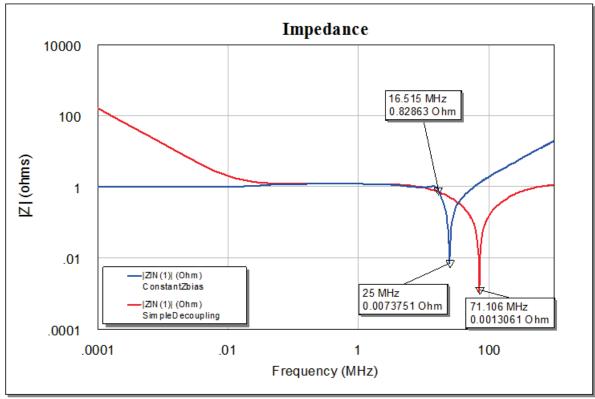

frequency increases due to parasitics. Common methods of producing a short circuit include using a via hole, edge wrapping and a solid ground plane (with or without via holes). One of the benefits of a distributed circuit is that a short circuit at the end of a  $\lambda/4$  line looks like an Open Circuit (O/C) at the other end of the line at the design frequency. Thus another way of creating a short circuit is to attach a  $\lambda/4$  o/c stub at the point where a short circuit is desired. This is inherently a narrow band structure; to broaden the bandwidth a radial stub can be used. Even more effective is a double radial or butterfly stub, [25]. These solutions are often adopted as frequency increases and the inductance/phase length of via holes has more impact, or when an RF short is required but not one at DC. In bias feeds it is required that DC current be injected into the circuit but that the feed arrangement not load the RF matching network. Although microstrip impedances are typically limited to between 25 and  $90\Omega$ , it is possible to create effectively lower impedances by adding two o/c stubs in parallel. A comparison of the performance of various distributed stubs is shown in Figure 1-13. The best performance is from the via, the dispersion in this being due to the inductance/phase length of the connection to the ground plane (backside of the substrate in MMICs).

Figure 1-13, Relative performance of different short circuit elements, the lower the dispersion the closer to the ideal.

A double open circuit stub (on either side of the main transmission line) creates a wider band short circuit than a single radial or open circuit stub, however carries with it the danger of non TEM modes being generated as well as a lack of clarity as the correct modelling method — a wide double stub looks physically like a low impedance short transmission line. This presents a discontinuity and is best analysed in an E-M simulation. When designing with microstrip elements it is important to remember that the models used were developed and optimised for specific substrate thickness to line width ratios. There are often a variety of models for the same structures and it is important to choose the most appropriate one for the materials and frequency range used. Where appropriate models do not exist, the use of E-M simulation is necessary. This can be used for a specific section of the design, as simulating a whole circuit in this way can be time consuming and hence difficult to optimise.

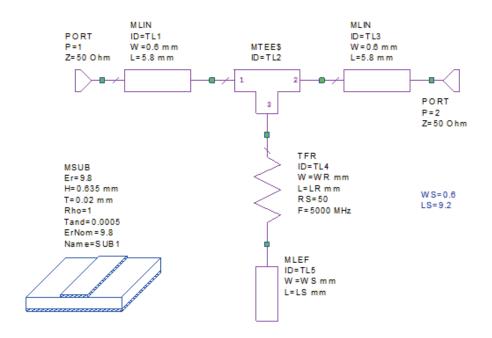

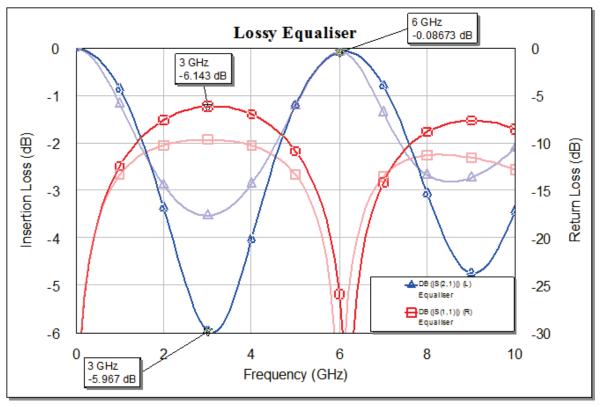

Transistors have a natural gain slope in |S21| of 6dB/octave, which can be a particular problem in broadband amplifier design. A method for compensating for this is to use lossy stubs or equalisers, (input and interstage – not on the output). These do not

## (a) Schematic of Lossy Stub

(b) Performance, Blue S21 and Red S11, as resistance is varied between  $50\Omega$  (faint traces) and  $25\Omega$  (bold traces).

Figure 1-14, Lossy stub equaliser approach.

provide a DC path to ground and hence do not upset device biasing. The basic version of this approach consists of a resistor connected to an o/c stub, as is shown in Figure 1-14 (a). By altering the resistance different slopes can be achieved as shown in Figure 1-14(b) and summarised in Table 1-2. In narrow band applications the equaliser can be used for stopping high frequency oscillation by introducing loss at the problem frequency.

| Nominal Resistor                                                  | Approximate Slope | Worst case Return |  |

|-------------------------------------------------------------------|-------------------|-------------------|--|

| Value (Ω)                                                         | (dB/octave)       | Loss (dB)         |  |

| 25                                                                | 5.9               | 6.1               |  |

| 50                                                                | 3.4               | 9.6               |  |

| 75                                                                | 2.4               | 12.2              |  |

| 100                                                               | 1.8               | 14.1              |  |

| Table 1-2, Equaliser performance as a function of resistor value. |                   |                   |  |

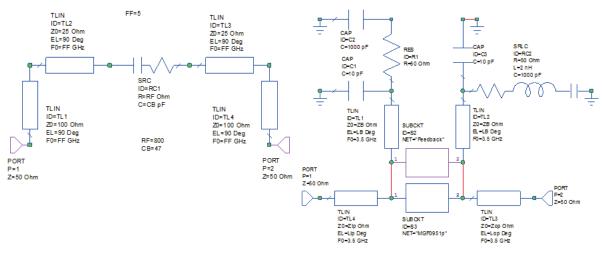

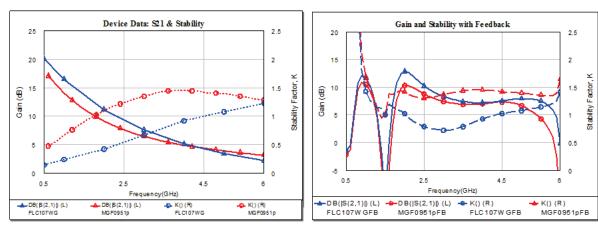

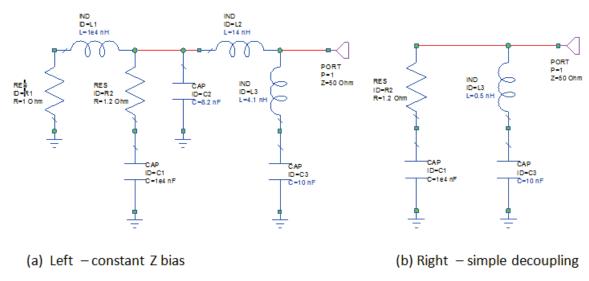

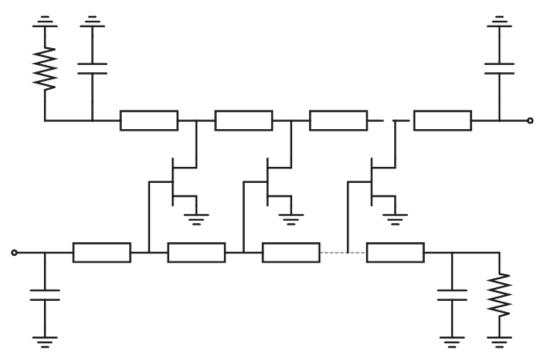

In order to simultaneously achieve improved match, stability and flat gain over wide bandwidths feedback can be employed [26]. The theory has been well documented [27], for power amplifier applications series feedback is rarely used due to the difficulty in simultaneously capacitively decoupling the source and providing a good thermal path to ground. With FETs shunt feedback must, by necessity, incorporate series capacitance as well as resistance to separate the gate and drain DC voltages. Both the capacitor and resistor will have parasitic inductance. This is can actually be of benefit as by incorporating inductance in the feedback model, it can help to increase the RF impedance and increase the gain at the upper end. In discrete designs leaded resistors, not normally used at microwave frequencies, can be specifically chosen to introduce the required inductance. Using shunt feedback, bandwidths of multiple octaves can be achieved. The feedback elements must be capable of handling the power levels of the signals travelling through them, but as they get larger to handle higher powers their parasitic components increase which makes their use more difficult.

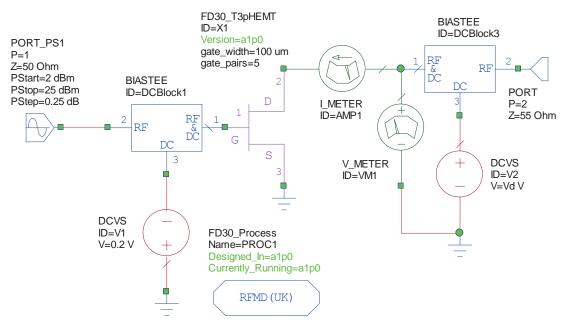

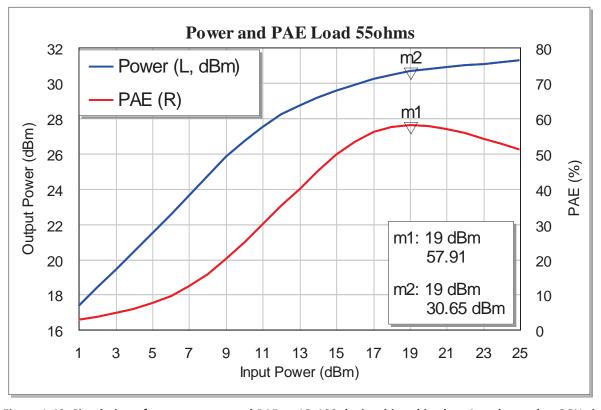

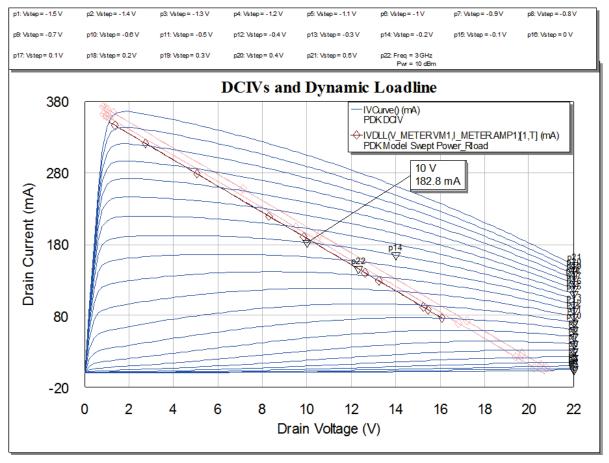

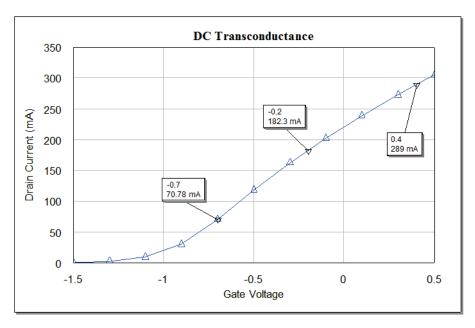

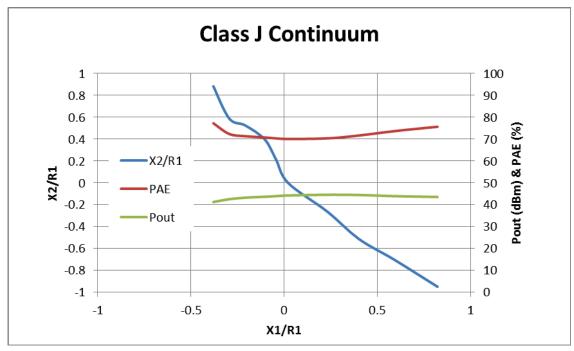

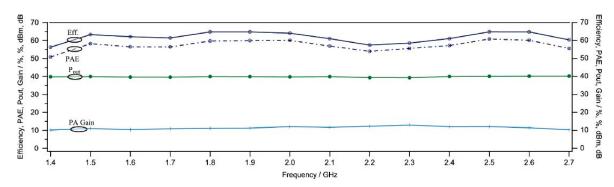

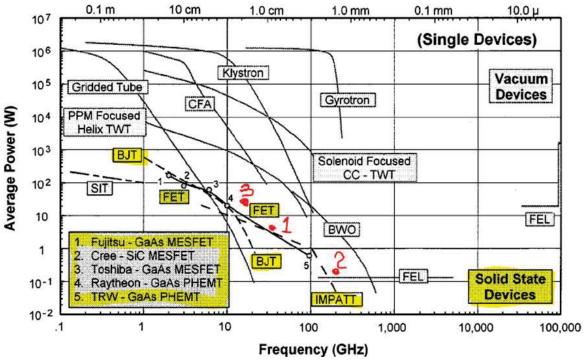

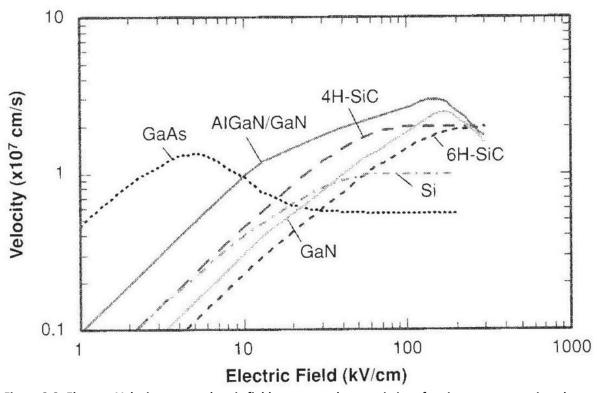

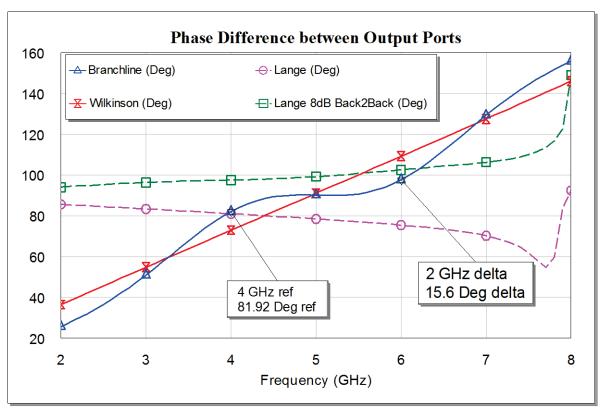

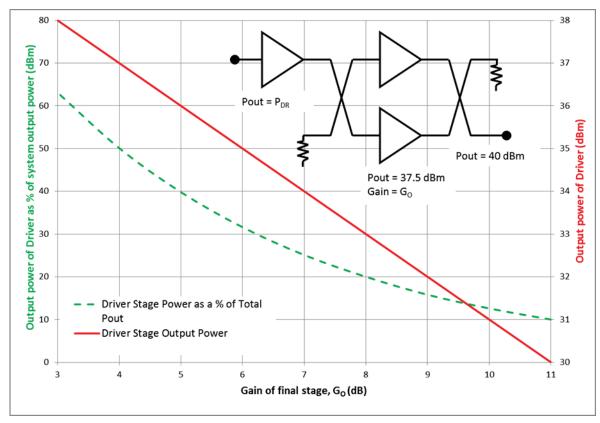

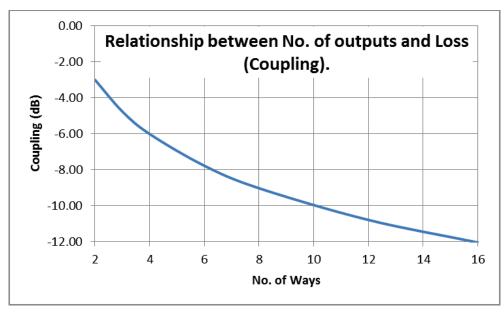

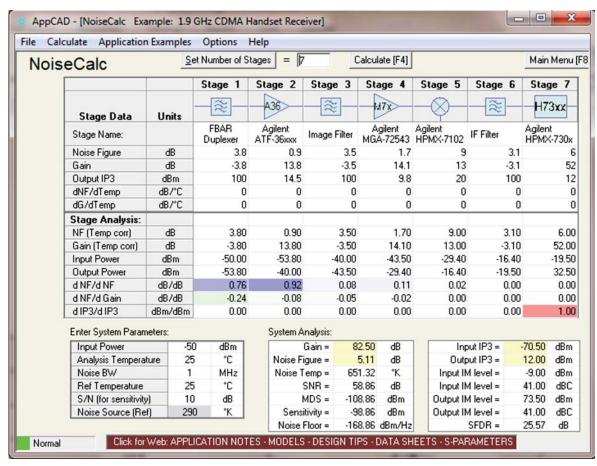

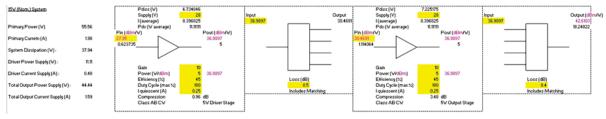

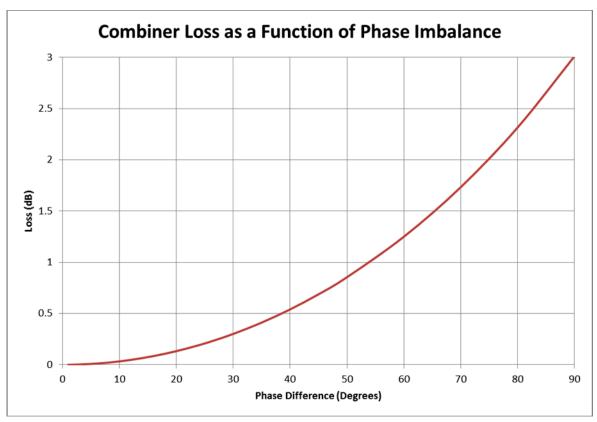

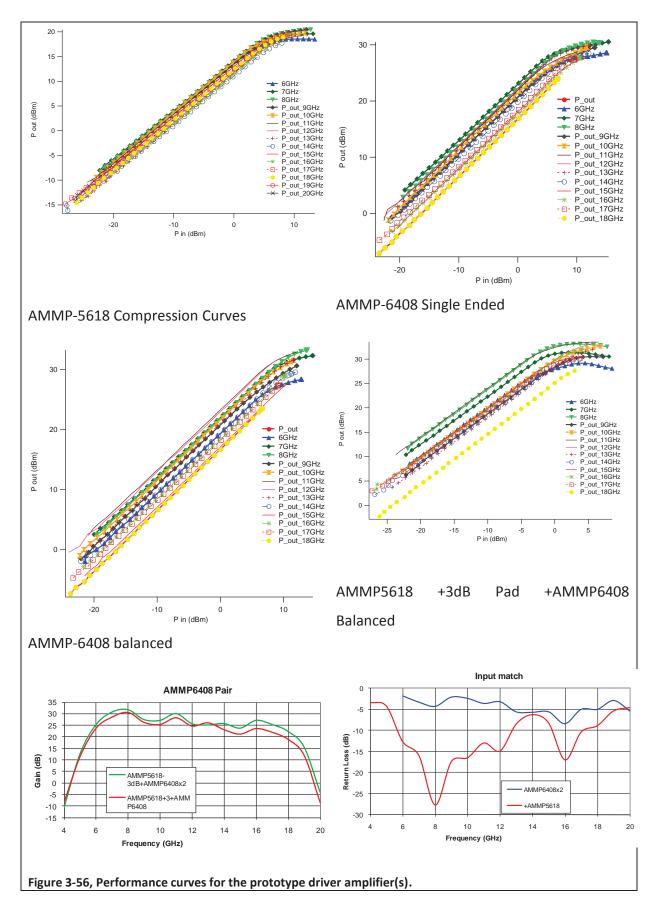

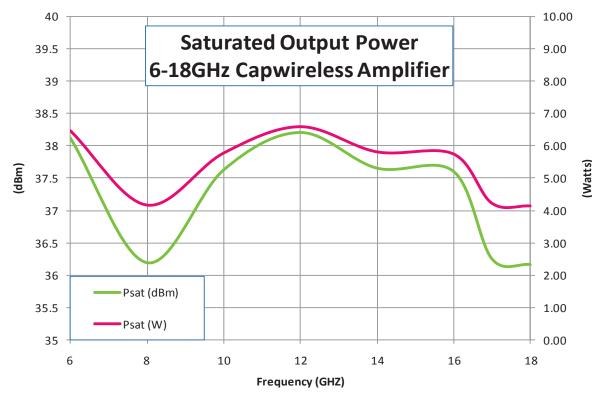

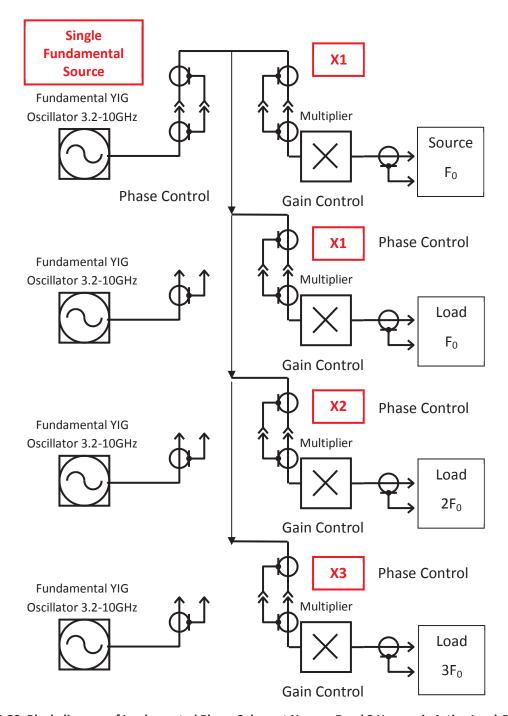

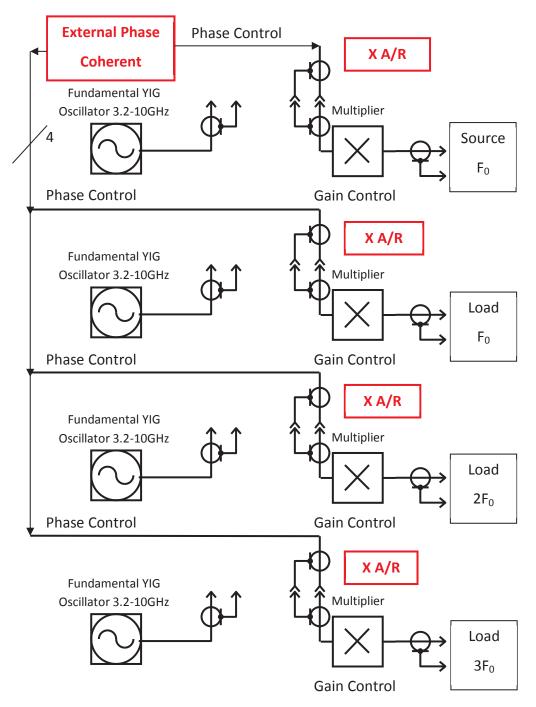

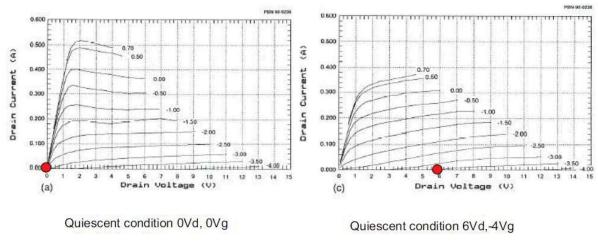

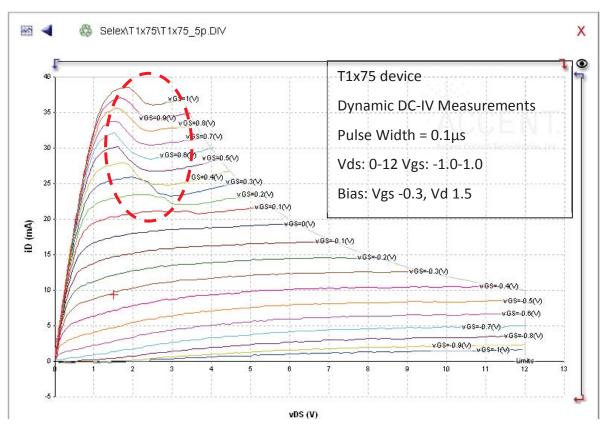

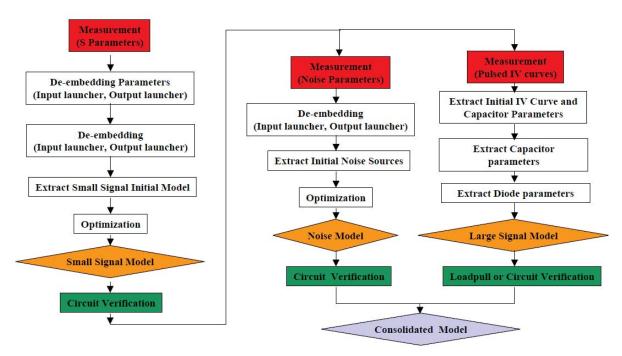

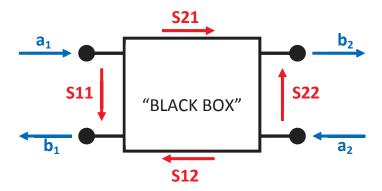

One of the problems with introducing feedback to discrete PAs is that of incorporating the feedback elements within the available physical space. Not only are the gate and drains separated by several mm, but there is also usually a large flange. Sometimes it is possible to construct the feedback network in three dimensions, going over the top of the device rather