# DESIGN, CHARACTERIZATION AND REALIZATION OF THIN FILM PACKAGING FOR BOTH BROADBAND AND HIGH POWER APPLICATIONS

A thesis submitted to the University of Wales, Cardiff

In candidature for the degree of

**Doctor of Philosophy**

By

Zaid Emmanuel Aboush

Division of Electronics

School of Engineering

Cardiff University

United Kingdom

September 2007

UMI Number: U584995

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U584995

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# DECLARATION

| This work has not previously been accepted in substance for any degree and is not concurrently submitted in candidature for any degree.                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signed Candidate) (Candidate)                                                                                                                                                                            |

| Date 21/9/2007                                                                                                                                                                                           |

|                                                                                                                                                                                                          |

| STATEMENT 1                                                                                                                                                                                              |

| This thesis is being submitted in partial fulfilment of the requirements for the degree of PhD.                                                                                                          |

| Signed (Candidate)                                                                                                                                                                                       |

| Date 21/9/2007                                                                                                                                                                                           |

|                                                                                                                                                                                                          |

| STATEMENT 2                                                                                                                                                                                              |

| This thesis is the result of my own independent work/investigation, except where otherwise stated. Other sources are acknowledged by explicit references.                                                |

| Signed (Candidate)                                                                                                                                                                                       |

|                                                                                                                                                                                                          |

| Date 21/9/2007                                                                                                                                                                                           |

|                                                                                                                                                                                                          |

| STATEMENT 3                                                                                                                                                                                              |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations. |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations. |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside                |

# To my Parents Alia and Emmanuel

# **ABSTRACT**

In recent years, high frequency MMICs have witnessed rapid development in terms of miniaturization, higher powers and increasing functionality, whilst the cost per unit has been simultaneously reduced. Cost-wise, modern packages have been unable to follow the same trend as the reduction seen in semiconductor costs and in some cases the package cost has even become a significant part of the overall module cost.

Historically, the diverse range of MMIC applications has always demanded electrically transparent packages to house the on-chip circuits and isolate them from the hostile ambient environment. The other vital role for MMIC packages is to provide good thermal dissipation for the circuits they contain. Thermal issues associated with most packages have led to the invention of different kinds of thermal pastes and strips to help dissipate the excessive heat generated by active devices. However, the thermal design of the package itself remains the basic foundation for a package with good thermal behaviour.

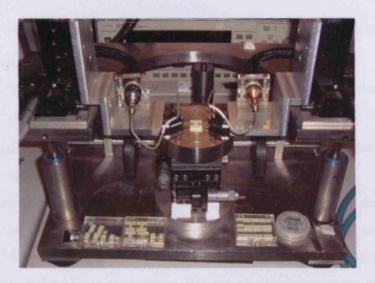

To evaluate the performance of high frequency semiconductor packaging a number of different electrical and thermal measurement setups have been developed. Passive electrical measurements are the most common and easiest measurements to perform as the package is tested without an active device inside. Active measurements involve measuring the package with an active device inside and can become problematic, especially when characterizing high power transistors with low output impedances, such as Si LDMOS transistors with output powers in excess of 30 Watts.

This thesis deals with three main issues central to the problems encountered in modern high frequency MMIC packaging. Firstly, the development of new low-power low cost packages utilising cutting edge materials such as liquid crystal polymer (LCP) to compete with the traditional ceramic substrate packages. Secondly, the development of new high power laminate based packages optimised for electrical and thermal characteristics. Finally, the development of passive and active measurement systems used to characterize the developed packages. The active measurement system is based on the load-pull concept to measure and characterise high power packaged transistors. This system is also capable of measuring the waveforms at the device reference plane, which enables the optimised design of Power Amplifiers (PAs).

# **ACKNOWLEDGEMENTS**

I would like to express my deep and sincere gratitude to my supervisor, Prof. Paul J. Tasker for his continuous and unlimited support throughout my time at Cardiff University, and in particular during my PhD. His seemingly unlimited knowledge has continuously inspired me and has made me believe that there is nothing impossible in science. I would also like to thank my second supervisor Dr. Johannes Benedikt for his support and for keeping me focused and on-track. He always helped me to consider the bigger picture with the richness of his ideas and industrial experience.

I would like to thank Prof. Adrian Porch, who has always been there to advise and guide me in both technical and non-technical related matters, and in particular, for providing the valuable opportunity for me to work with Physics group at Cardiff University.

I would like to thank Labtech Ltd for sponsoring this work and, in particular, Mr. John Priday for his endless support, and Dr. Brian Mazonas for driving the activity. I would also like to thank John Leaf, Gary Morgan, David Gittins and Gil Edwards for their support while I was at Labtech.

During my study at Cardiff University I have been fortunate to meet people whom I now consider very good friends, in particular Dr. Jonathan Lees whose early support and subsequent proof reading of this thesis I particularly appreciate. More recently, Tudor Williams, Peter McGovern, Aamir Sheikh, Hao Qi and Chris Roff (who has also helped in the proof reading of this thesis). Within the Physics department, I have met a number of people who have become friends of mine; Simon Doyle, Dr Philip Mauskof, Giampaolo Pisano, Bruno Maffei and Luca Pietranera have all inspired me with their deep knowledge linking engineering to physics.

I would like to say a **big thanks** to my late mother who looked after me all the way through my PhD study until my last days at Cardiff University. I thank her for her patience, prayer and good wishes; she was always praying and wishing to see me reach this stage which unfortunately has not been able to witness. I would also like to thank my father for his unlimited support and wise advice. Being my father he is also my best friend, whom I always ask for the right advice. I would like to thank my brother for his continuous support and encouragement, and for encouraging me to achieve my goals during difficult times.

# LIST OF PUBLICATIONS

# **Peer Reviewed Publications**

- Z. Aboush, J. Benedikt, and P. Tasker, "DC-50 GHz Low Loss Thermally Enhanced Low Cost LCP Package Process Utilizing Micro Via Technology," IEEE MTT-S International Microwave Symposium Digest, pp. 961-964, June 2006.

- Z. Aboush, C. Jones, G. Knight, A. Sheikh, H. Lee, J. Lees, J. Benedikt, and P. J. Tasker, "High power active harmonic load-pull system for characterization of high power 100-watt transistors," *European Microwave Conference*, vol. 1, pp. 4-6, October 2005.

- 3. **Z. Aboush**, J. Lees, J. Benedikt, and P. Tasker, "Active Harmonic Load-pull for Characterizing Highly Mismatched High Power Transistors," *IEEE MTT-S International Microwave Symposium Digest*, pp. 1311-1314, June 2005.

# **Publications**

- 4. **Z. Aboush**, J. Benedikt, J. Priday, and P. Tasker, "Novel cost-efficient packaging technology for high-power LDMOS devices," *IEEE High Frequency Postgraduate Student Colloquium*, pp. 15-18, September 2005.

- 5. **Z. Aboush**, J. Benedikt, and P. Tasker, "High power harmonic active load-pull using broadband impedance transformers," *IEEE High Frequency Postgraduate Student Colloquium*, pp. 145-150, September 2004.

# **Other Publications**

6. **Z. Aboush** and A. Porch, "Compact, Narrow Bandwidth, Lumped Element Bandstop Resonators," *IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS*, vol. 15, pp. 524-526, August 2005.

# **PhD Achievements**

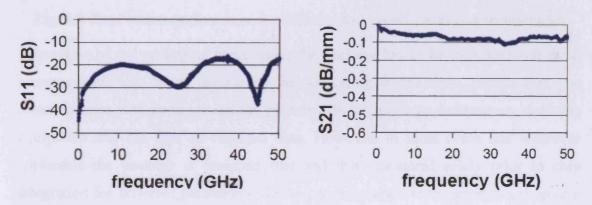

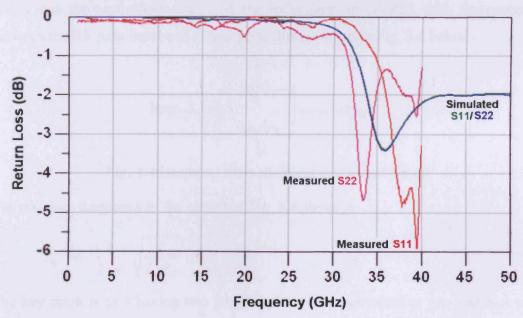

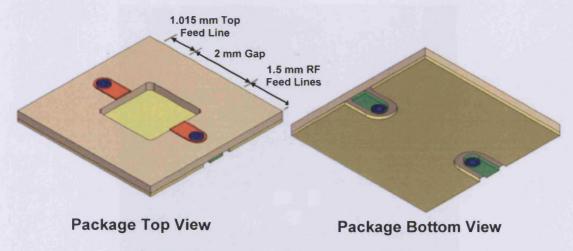

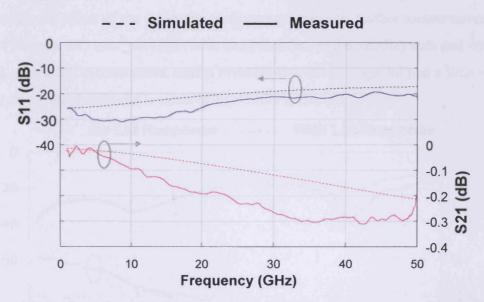

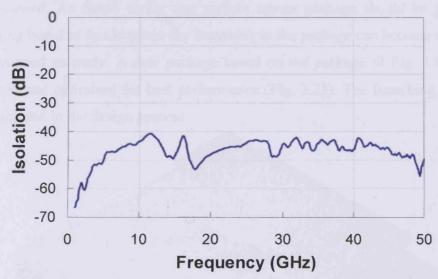

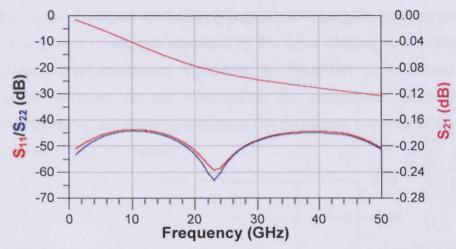

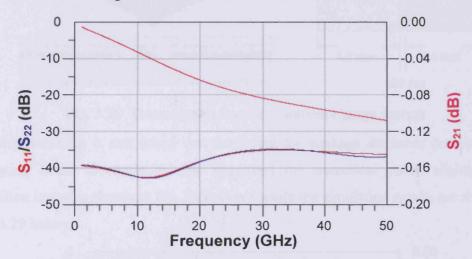

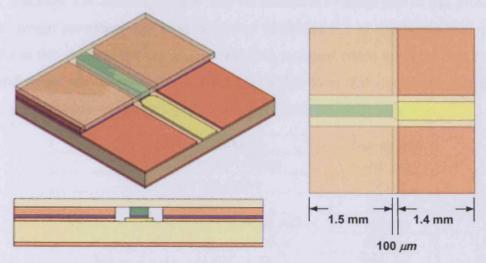

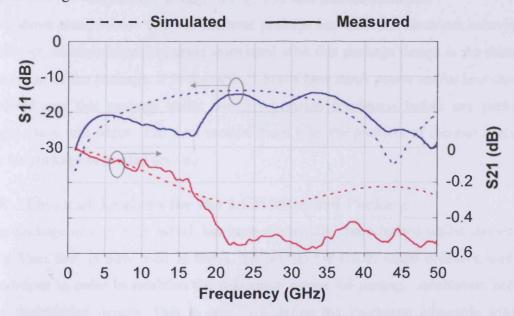

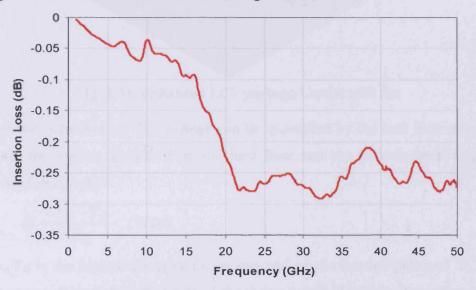

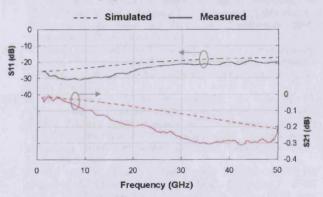

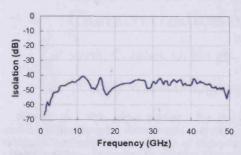

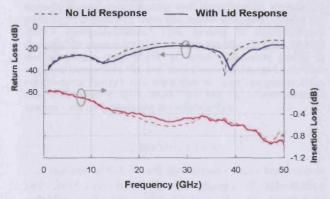

The work carried out in this thesis resulted in significant published achievements. The first achievement of this work was the design and development of new broadband DC-50GHz low power package using liquid crystal polymer laminate material. The resultant package sustained less than 0.3dB of insertion loss and more than 15dB of return loss across the whole bandwidth, including the package as well as the mounting structure. This was achieved by developing a logical design methodology which enabled via transition and package-to-mounting structure optimisations. The newly designed package offered significant cost reduction compared to its corresponding ceramic packages.

The second achievement was the development of an advanced linear measurement system using multi-tier calibration techniques. This enabled the accurate calibration of the measurement system using traceable standards while shifting the measurement reference plane up to the package plane(s) and consequently a true package model was extracted.

The third achievement was the design and development of new high power package utilising laminate technology. This approach enabled the use of low cost printed circuit board (PCB) manufacturing process to produce these packages. The resultant package offered competitive performance to ceramic packages at much lower cost.

The final achievement was the development of a new and powerful non-linear measurement system capable of characterising high power transistors in excess of 100W CW power. The system was equipped with multi-tier calibration feature which enable accurate measurement system calibration at the coaxial reference plane using traceable standards while shifting the measurement reference plane up to the device under test (DUT) plane using second tier calibration. The system is also capable of measuring waveforms at different reference planes which helps giving deep understanding of the DUT behavior. Also the measurement system imperfection was studied in more details and used to further improve measurement system performance.

# **Glossary of Terms and Acronyms**

| Term         | Description                                         |

|--------------|-----------------------------------------------------|

| ADS          | Advanced Design System                              |

| BGA          | Ball Grid Array                                     |

| CAD          | Computer Aided Design                               |

| CPWG         | Conductor Backed Coplanar Waveguide                 |

| CTE          | Coefficient of Thermal Expansion                    |

| D.K.         | Dielectric Constant                                 |

| DUT          | Device Under Test                                   |

| EM           | Electromagnetic                                     |

| GSG          | Ground Signal Ground                                |

| HFSS         | High Frequency Structure Simulator                  |

| IPD          | Integrated Passive Devices                          |

| LCP          | Liquid Crystal Polymer                              |

| LDMOS        | Laterally Diffused Metal Oxide Semiconductor        |

| LRL          | Line, Reflect and Line                              |

| LRM          | Line, Reflect and Match                             |

| LTCC         | Low Temperature Co-fired Ceramic                    |

| MMIC         | Monolithic Microwave Integrated Circuit             |

| MOSFET       | Metal Oxide Silicon Field Effect Transistor         |

| MTA          | Microwave Transition Analyser                       |

| PA           | Power Amplifier                                     |

| PCB          | Printed Circuit Board                               |

| PoP          | Package on Package                                  |

| QFN          | Quadrature Flat no-Lead                             |

| RF           | Radio Frequency                                     |

| RLGC         | Resistance, Inductance, Conductance and Capacitance |

| Rth          | Thermal Resistance                                  |

| Si           | Silicon                                             |

| SiP          | System in Package                                   |

| SMD          | Surface Mount Devices                               |

| SMT          | Surface Mount Technology                            |

| SOL          | Short, Open and Load                                |

| SOLT         | Short, Open, Load and Thru                          |

| S-Parameters | Scattering Parameters                               |

| SP-CSP       | Stacked Package Chip-Size Package                   |

| SPICE        | Simulation Program with Integrated Circuit Emphasis |

| SWR          | Standing Wave Ratio                                 |

| TMM          | Temperature Stable Circuit Board Materials          |

| T-Parameters | Transmission Parameters                             |

| TRL          | Thru, Reflect and Line                              |

| TRM          | Thru, Reflect and Match                             |

| VNA          | Vector Network Analyser                             |

| VSWR         | Voltage Standing Wave Ratio                         |

| WALN         | Wireless Local Area Network                         |

| WLCSP        | Wafer Level Chip Scale Package                      |

# **TABLE OF CONTENTS**

| ADSTRACT                                                       |     |

|----------------------------------------------------------------|-----|

| Acknowledgement                                                |     |

| List of Publications                                           |     |

| PhD Achievements                                               |     |

| Glossary of Terms and Acronyms                                 |     |

| Table of Contents                                              |     |

| Chapter 1. Introduction                                        |     |

| 1.1 Package Design Objectives and Limitations                  |     |

| 1.2 Thesis Objectives                                          |     |

| 1.3 Thesis Structure                                           |     |

| 1.4 References                                                 |     |

| Chapter 2. Low-Power Low Cost Packages Characterization        |     |

| and Evaluation                                                 |     |

| 2.1 Low Power Package Literature Survey                        |     |

| 2.2 Packaging Technologies                                     |     |

| 2.3 Package Measurement Techniques Overview                    |     |

| 2.4 Electrical Measurement System Setup for Passive Package    |     |

| Measurements                                                   |     |

| 2.5 Measurement System Calibration Procedures (Multi-tier Cal) |     |

| 2.5.1 SOLT Calibration                                         |     |

| 2.5.2 TRL/TRM Calibration                                      |     |

| 2.5.3 Embedding and De-embedding Techniques                    |     |

| 2.6 Summary                                                    |     |

| 2.7 References                                                 |     |

| Chapter 3. Design, Realization and Measurements of Lamina      | ıte |

| Based Low-Power Packages                                       |     |

| 3.1 Package Design Basis                                       |     |

| 3.2 Reduced Capacitance Package Design and Measurement         |     |

| 3.3 LCP Package Design and Modelling                           |     |

| 3.4 Package Realization                                           | 50 |

|-------------------------------------------------------------------|----|

| 3.5 LCP Package Measurement                                       | 51 |

| 3.6 LCP Package Design with Launching Structure                   | 54 |

| 3.6.1 Mounting Board Design                                       | 55 |

| 3.6.2 Package Bottom (Buried) Conductor-backed Coplanar           |    |

| Transmission Line Design                                          | 56 |

| 3.6.3 Transmission Line Impedance Environment Change Interface    | 57 |

| 3.6.4 Package Top Microstrip Transmission Line                    | 59 |

| 3.6.5 Package Via Section Design                                  | 59 |

| 3.7 LCP Mounted Package Measurement                               | 60 |

| 3.8 Thermal Analysis for the LCP Mounted Package                  | 63 |

| 3.9 Summary                                                       | 68 |

| 3.10 References                                                   | 69 |

|                                                                   |    |

| Chapter 4. High-Power Packages and Their Characterization         |    |

| Techniques                                                        | 70 |

| 4.1 High-Power Package Technologies                               | 70 |

| 4.1.1 High Power Ceramic Packages                                 | 70 |

| 4.1.2 High Power Plastic Packages                                 | 72 |

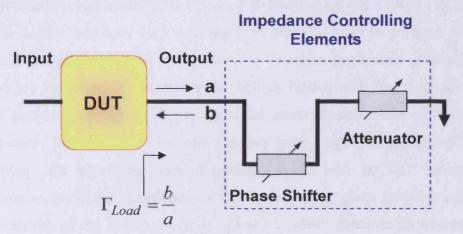

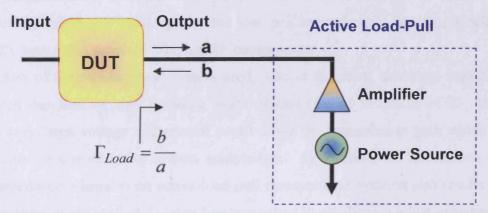

| 4.2 Measurement Techniques for High Power Packages                | 76 |

| 4.3 High-Power Time-Domain Active Harmonic Load-pull Measuremen   | nt |

| System Overview                                                   | 80 |

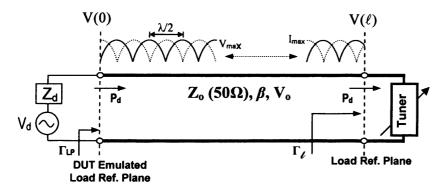

| 4.3.1 Load-pull Measurement Systems Limitations                   | 81 |

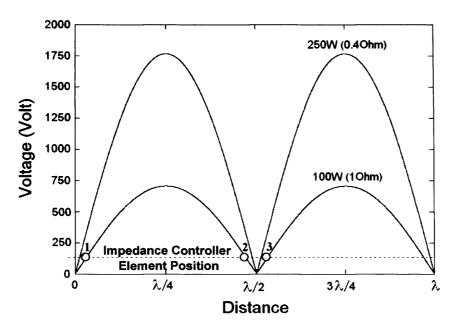

| 4.3.2 Voltage Standing Wave Effect in Load-pull Systems           | 81 |

| 4.3.3 Load-pull Power Levels Associated with the Active Load-pull |    |

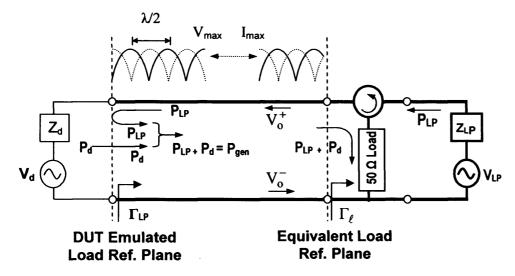

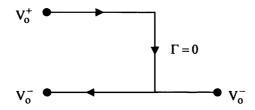

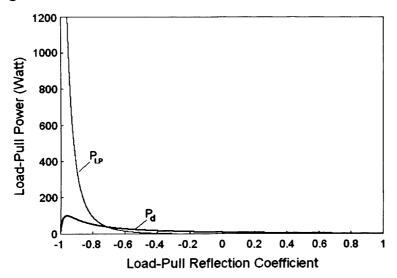

| Measurement Systems                                               | 84 |

| 4.4 New Measurement System Description                            | 87 |

| 4.5 Impedance Transformation Solution                             | 88 |

| 4.5.1 Narrowband vs Broadband Impedance Transformers              | 92 |

| 4.5.2 Optimum Impedance Transformer Design                        | 93 |

| 4.6 System Mismatch Issue                                         | 94 |

| 4.7 Hybrid Load-pull Measurement System                           | 96 |

| 4.8 Measurement System Calibration                                | 98 |

| 4.9 Measurement System Verification                                     |     |  |

|-------------------------------------------------------------------------|-----|--|

| <b>4.10</b> Summary                                                     | 106 |  |

| 4.11 References                                                         | 107 |  |

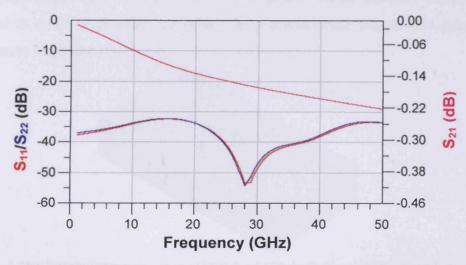

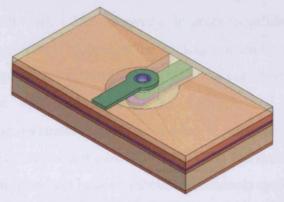

| Chapter 5. High-Power Package Design and Measurements                   | 109 |  |

| 5.1 High Power Package Description                                      | 109 |  |

| 5.2 Package Design                                                      | 110 |  |

| 5.2.1 Electrical Design                                                 | 110 |  |

| 5.2.2 Thermal Analysis                                                  | 112 |  |

| 5.3 Package Realization and Measurement                                 | 114 |  |

| 5.4 Summary                                                             | 119 |  |

| 5.5 References                                                          | 120 |  |

| Chapter 6. Conclusion and Future Work                                   | 121 |  |

| 6.1 Conclusion                                                          | 121 |  |

| 6.2 Future Work                                                         | 123 |  |

| Appendices                                                              | 125 |  |

| Appendix A. Two-port Calibration Using Thu, Reflect and Line (TRL)      | 126 |  |

| Appendix B. Lossless Reciprocal Network Analysis                        | 136 |  |

| Appendix C. Standing Wave Analysis in Load-pull Measurement Systems     | 139 |  |

| Appendix D. Load-pull Power Analysis for non 50 Ohm Measurement Systems | 143 |  |

| Appendix E. Klopfenstein Taper Design                                   | 145 |  |

| Appendix F. Impedance Transformer Characteristic Impedance Measurements | 149 |  |

| Appendix G. Publications                                                | 157 |  |

# CHAPTER 1

# **INTRODUCTION**

Semiconductor technologies have undergone rapid development over recent decades, and the electronic packaging industry in particular has faced many challenges due to ever increasing device performance, levels of device integration and reductions in physical size. The problems lay in the fact that while semiconductor devices are getting smaller, their functionality is increasing significantly. Operational speed is also increasing rapidly due to the ever-increasing demand for bandwidth, resulting in ever-increasing electrical performance requirements which implied higher levels of power consumption. From the packaging perspective, the smaller the package; the less heat it can dissipate. Also the smaller size of for example signal tracks, results in increased losses which scale with increasing frequency. Stacked-dies in system-inpackage (SiP) modules and stacked package-on-package (PoP) technologies are also placing an additional burden on the overall package performance due to the need for vertical expansion which requires a significant amount of routing and interconnect optimisation. As a result, good quality RF substrate materials and small and efficient interconnect geometries are under continuous demand to fulfil current and future semiconductor packaging requirements. The improvement in semiconductor device performance and cost has been a facilitating factor in a huge range of technological advances. Numerous applications have been made possible largely due to the availability of cheap, reliable and high performance electronic circuits. Perhaps the most important of these applications has been radio frequency communication.

In a typical RF device package, multiple dies can be used in order to realise a complete solution (module). These packages must fulfil the requirements for small size, high power, multi-functional, broadband, and most importantly low cost RF devices and modules.

Although the semiconductor dies can be placed directly into the PCB board for example in mobile phone, this option is very limited for a number of reasons. The first reason is that high-technology vendors cannot make much profit from unpackaged devices. The other important factors are manufacturability and reliability. On the manufacturing side, high-end applications companies (e.g. mobile phone

manufacturers) do not normally prefer to bring all the manufacturing processes inhouse since it makes mass-production very expensive and the manufacturing lead times can become significant.

From a reliability point of view, the PCB board, by nature is a good moisture absorber and is also easily bent. Therefore, if the PCB board is dropped or is exposed to frequent mechanical shock, this can cause the die to detach from the board.

The other factor is that mounting the die directly will limit its suitability to different vendors who deal with end applications due to the inability to perform routing for different customer PCB boards. In reality, PCB boards are multilayer and, for complex circuits like Bluetooth and WLAN modules where the simplest die has around 80 to 90 Input / Output (I/O) pins, these pins have to be routed to make contact with different layers, which can only be done using packages.

The basic requirements for any package are to physically protect and provide a near electrically transparent housing for the MMIC inside. The ideal package should pass the electrical signal with minimum degradation while perfectly dissipating any heat generated by the semiconductor; all this to be achieved at a fraction of the cost of the MMIC inside. Therefore, much research has gone into creating packaging solutions that fulfil stringent demands on electrical, thermal, protective and financial performances.

Unfortunately, the financial cost of the best performing ceramic RF package technology is prohibitive for many commercial applications. While ceramic based packages have been shown to offer the best performance [1, 2] for RF and millimetre wave MMIC packaging, the cost of these packages is becoming a significant part of the overall RF module cost, and in some cases even exceeding the price of the MMIC itself. Therefore, many solutions have been introduced in the past which sacrifice performance in order to cut the package cost. An example of this trend has been the popularity of molded plastic packages.

More advanced technologies such as Ball Grid Array (BGA) and the Wafer Level Chip Scale packaging (WLCSP) can provide a compact environment for the MMIC while achieving good electrical performance. Unfortunately, these kinds of packages are more prone to thermal issues.

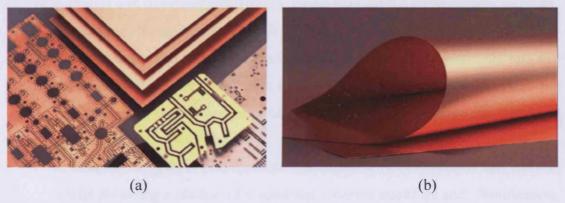

Other technologies introduced in recent years include the laminate based surface mount packages. Laminates (Fig. 1) usually have copper on both sides, providing flexibility in manufacturing since patterns can be created on both sides at once which also make it suitable for multilayer package substrate as well as different package sizes can be realized. Laminate packages are fabricated using standard, well established PCB manufacturing technologies. These processes have been optimised for cost which means that manufacturing costs of such packages is very low. In addition, the laminate itself is relatively low-cost.

These laminate based surface mount packages require wire bonding to connect to the MMIC and are also slightly bigger than the BGA and WLCSP equivalents. Their advantages lie in competitive electrical performance compared to ceramic solutions, and their significantly lower cost. This technology holds great promise to replace the high performance ceramic packages, especially with the emergence of the new crystalline filled polymers or so called Liquid Crystal Polymer or LCP (Fig. 1.b) which have dual properties of low electrical loss and associated cost that is significantly less than ceramic. Indeed, with the existence of different laminate materials to suite different power levels, the laminate based packaging technology has recently been extended to include high-power (>30W) RF transistors [3].

**Fig. 1** Laminate substrates - a) Standard high frequency laminate and b) Liquid crystal polymer (LCP) laminate.

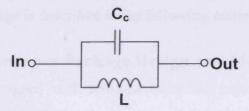

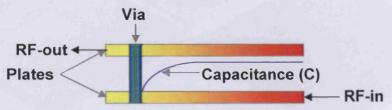

Another interesting feature associated with laminate is the ability to embed passive circuits on the same package substrate (laminate) which can replace some of the external passive components attached to the packaged device. This technology is known as Integrated (embedded) Passive Devices (IPD) and can offer cost reduction and module size reduction through the elimination of the external passive components.

One challenging future packaging technology that is yet to emerge is stacked wafer chip scale package (CSP) packages which includes massive routing on each silicon layer. The in-silicon via is probably one of the most critical passive components for future packaging and routing technologies (the smaller and more numerous the vias, the more useful the package; this comes at a cost of increased loss and cost however). This new technology will increase the challenge faced by RF package engineers in maintaining a clean, transparent path for RF and high-speed digital signals alike.

When the die pads become high in number, the on-die routing can become extremely difficult, therefore a routing PCB layer (package substrate) can become necessary which represents the package itself. This kind of architecture will possibly to be used and expanded in the foreseeable future where one package is mounted onto another, with the routing being performed on the package level as well as the silicon level.

## 1.1 Package Design Objectives and Limitations

The packaging objective is not only to protect the die from the external environment, but also to provide an electrical connection to the external world and a thermal path to dissipate the heat introduced by the device. In fact, packaging can be a critical factor in achieving high performance whilst meeting the cost objectives in many microelectronics and computer systems [4]. Essentially, an RF package must provide:

- 1. Connections to the mounted dies for power (DC) and signal (RF) lines.

- 2. An electrically and thermally conductive base to attach the active die and any associated components. However in technologies such as flip-chip, where the die is 'flipped' over, a heat sink can be attached to the package top surface to dissipate the excessive heat.

- 3. A structure to protect and maintain the integrity of connections and the die, whilst providing a platform for handling, external markings and identification; this is basically the package cap or lid.

For the first point the ultimate goal is to design a package with an all-pass filter with a frequency response similar to that of a transmission line. This is a challenging task since the package normally contains components other than transmission lines, such as vias and launching points, where changes in impedance environments exist, requiring careful matching design. The bonding wires themselves will also affect the RF signal and therefore wire bonding compensation circuitry becomes necessary.

For the second point, the package base serves two functions: the first is to provide a good electrical contact to ground with minimum ground inductance (which adds to the transistor's source inductance), and secondly to provide a good thermal path to dissipate the heat associated with the device. Combining these two objectives into one

is quite difficult. However, with the emergence of special electrically and thermally conductive pastes, and by using bare copper as a package base, this objective can be met to some extent.

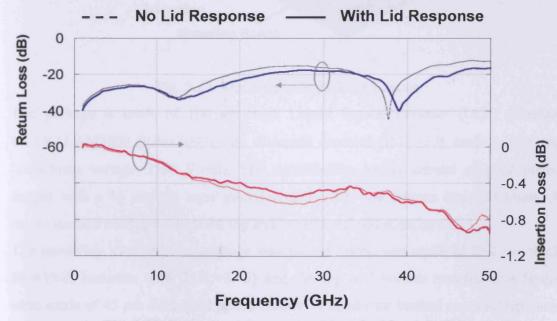

The third and final point is the package cap which can be realised either by using a metal lid or plastic lid. The metal lid can cause significant side effects since it can trigger cavity resonance effects leading to device oscillation and instability. However, both metal and plastic lids can change the package RF performance since they provide an RF path for interactions between the package components. As a result, the package lid has to be taken into account during the design process.

## 1.2 Thesis Objectives

The objectives of this work were to investigate the use of low cost laminates that exhibit very low electrical losses and excellent thermal properties in the design and realisation of two kinds of package. The first objective is to design a DC to 50 GHz broadband low power surface mount package utilising liquid crystal polymer (LCP) laminate as an alternative cost effective technology, with properties similar to those of ceramic equivalents. For this design, micro-via technology will be used as a form of transition between metallization layers. Micro-vias are attractive due to their small physical size and the flexibility in controlling their geometries. This kind of via helps with package miniaturisation as well as allowing hermeticity

The second objective is to design a laminate based, high-power package suitable for high-power transistors, especially the popular LDMOS devices with power rating exceeding 30 Watts of CW power. In this application, the laminate based package process provides a significant cost reduction compared to corresponding ceramic based packages.

In order to develop these high-power packages, it was necessary to conceive and develop a new measurement system capable of characterising high-power devices (>30 Watt CW).

#### 1.3 Thesis Structure

This thesis is divided into two main parts; low-power package design and characterization (Chapters 2 and 3), and the high-power package design and characterization (Chapters 4 and 5).

Chapter 2 presents a thorough literature survey, summarising the available low power packaging technologies, their applications and their measurement techniques. The measurement system used to characterise the packages presented in this thesis, including low power packages is discussed in detail. Different measurement setups are explained along with their associated calibration procedures, including multi-tier calibration approaches.

Moving forward to Chapter 3, the package design evolution is presented, starting with a basic package used at the beginning of this work, provided by Labtech Ltd, and then going through multiple iterations of analysis and package optimisation in order to achieve a logical and coherent method for designing broadband, high frequency, low-loss packages. Package modelling has been tackled and is used as a design aid to design new LCP packages with the ultimate package being mounted onto a PCB board. All packages presented in this chapter are measured using the measurement system discussed in Chapter 2.

Thermal analysis is also presented for the ultimate mounted LCP package in order to determine the maximum device power rating that can be accommodated inside these packages.

Chapter 4 deals with the high-power packages and their characterization techniques. Here, a literature search on high-power packages is presented which includes the ceramic and over-molded plastic packages. Also a review of the available measurement techniques, specifically passive and active load-pull measurement systems and their suitability for characterising high-power packages is presented. High-power, time-domain active harmonic load-pull measurement systems, their limitations and the problems associated with measuring high-power, low-impedance devices are discussed. Specifically, the need for increased load-pull power levels and the problems of very-high VSWR associated with increased load-pull power are presented in great detail.

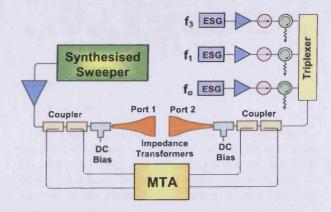

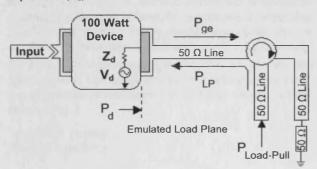

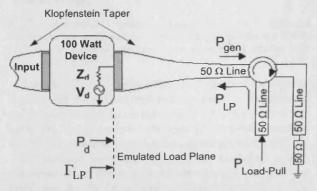

In this chapter, a new time domain, active harmonic load-pull measurement system is described. The new system utilises broadband impedance transformers to solve the problems associated with active load-pull measurement systems when characterising packaged high-power, low impedance devices.

Also in this chapter, the system characteristic impedance mismatch associated with the high-power active load-pull measurement systems is studied and analysed. This impedance mismatch problem exploited in order to design a new, powerful hybrid load-pull measurement system which is capable of characterising high-power, low impedance devices with a minimum amount of load-pull power.

The measurement system calibration techniques are also described in detail and the measurement system has been verified by measuring a 100 Watt LDMOS device which confirmed the validity of the analysis presented in this chapter.

In Chapter 5, a high-power package suitable for high power devices (e.g. 30 Watt LDMOS device) has been designed, the electrical and thermal design analysis are presented in full. The package was manufactured and verified with a 30 Watt Philips LDMOS device. The packaged device was then characterised using the newly developed measurement system described in Chapter 4 of this thesis and compared to similar device in a standard commercially available package.

Finally, conclusions and future work are presented in Chapter 7.

#### 1.4 References:

- [1] K. Yoshida, T. Shirasaki, S. Matsuzono, and C. Makihara, "50 GHz Broadband SMT package for microwave applications," *Electronic Components and Technology Conference Proceedings*, 51st, pp. 744 749, 2001.

- [2] H. C. Huang, A. Ezzeddine, A. Darwish, B. Hsu, J. Williams, and S. Peak, "Ku-Band MMIC in low-cost, SMT compatible packages," *IEEE MTT-S International Microwave Symposium Digest*, 2002, vol. 1, pp. 27 30, June 2002.

- [3] Z. Aboush, J. Benedikt, J. Priday, and P. Tasker, "Novel cost-efficient packaging technology for high-power LDMOS devices," *IEEE High Frequency Postgraduate Student Colloquium*, pp. 15-18, September 2005.

- [4] D. Boulin and H. Safar, "Plastic Packages Take On High-Power Devices," *Microwave and RF Online Journal*, pp. 1-2, February 2004.

# CHAPTER 2

# LOW-POWER LOW COST PACKAGES CHARACTERIZATION AND EVALUATION

In this chapter, a thorough literature survey summarising the available low power packaging technologies, future trends and measurement techniques will be presented. Additionally, detailed discussions are presented for a passive measurement system used to measure the low power packages introduced in this thesis along with the calibration procedures to allow parameters to be measured at the package plane for the various package structures.

## 2.1 Low-Power Package Literature Survey

Low power packages have gone through a long development process and although it has been slow compared to semiconductor research, the advances have been significant and the costs have been significantly reduced. The basic requirements for any package are to physically protect and provide a near electrically transparent housing for the MMIC inside. The ideal package should pass the electrical signal with minimum degradation while perfectly dissipating any heat generated by the semiconductor. However this ideal is not the case for the current packaging technologies, where the package usually degrades the electrical signal to some extent and the package is usually unable to fully dissipate the heat associated with the MMIC inside. This causes the package temperature to increase which in turn leads to mechanical problems; namely package expansion when hot and contraction when cold. The hot-cold cycle will gradually degrade the package mechanical stability and reliability. Choosing proper package materials with comparable thermal coefficients will minimize this effect, although it is not practicably feasible, because there is no such dielectric with a similar coefficient of thermal expansion (CTE) to Silicon and Copper. Ultimately the package has to be optimized for heat dissipation design which can also minimize the above effects while maintaining low manufacturing cost rather than using expensive materials.

Combining a high performance dielectric with a good thermal design will give the opportunity to come up with a high performance package at a fairly reduced cost.

In this work liquid crystal polymer (LCP) material, which represents the cutting edge technology in high frequency dielectric materials, has been used as the material of choice in which to design and fabricate high performance low power packages delivering low cost solutions. Good thermal management in the designed package may insure optimum electrical and thermal performance at reduced substrate and manufacturing cost.

## 2.2 Packaging Technologies

Due to the diversity of semiconductor applications, a wide range of packages have been developed to accommodate different MMICs. Irrespective of the package shape, there are recognisable packaging architectures and topologies which can be summarised into the following main categories:

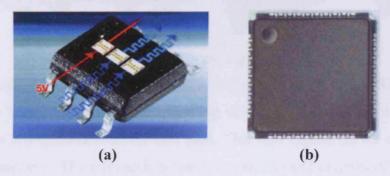

Plastic RFIC Packages: Plastic package technology (Fig. 2.1) has been the workhorse of the integrated circuit industry for many years, and this will continue for the foreseeable future [1]. The major advantages of these kinds of packages are the cost, since they are extremely cheap with relatively high performance. Two major kinds of plastic package are available; these are the Lead-frame packages (Fig. 2.1.a) and Quad Flat no-Lead packages (Fig. 2.1.b).

Fig. 2.1 Plastic packages (a) Lead frame, (b) Quad Flat no-Lead (QFN) packages The main disadvantage with the Lead-frame packages is that they have limited number of pin counts in addition their RF frequency handling is limited to few GHz, which is mainly due to the inductance rise associated with the lead frame at increasing frequencies. One of the solutions aimed at increasing the bandwidth of this kind of package up to 10 GHz, is to modify the lead frame to maintain 50 Ohm impedance environment[2]. This approach holds great promise for increasing the performance of such RF packages at higher microwave frequencies.

However, quadrature flat-no-lead (QFN) packages are even cheaper and their pin counts[3] are higher than the lead-frame packages although it is still low compared to

flip-chip or BGA packages discussed below. Again, the RF performance of these packages is quite limited.

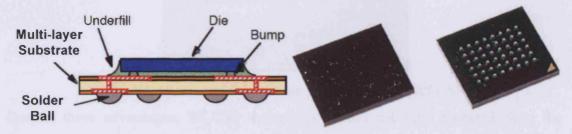

Flip-Chip Technology: In this technology the die pads are bumped with solder balls and the whole die is flipped over a double sided (multi-layer) substrate usually made of FR4 or similar cheap material (Fig. 2.2). The routing can be made on both substrate metallization layers with the solder bumps being attached to the substrate bottom side. The key advantage of flip chip technology is size, flip chip packages do not require peripheral space for the wire bonds thus, they can be made smaller than wire bond packages with a similar I/O count. For dies with a high I/O count, flip chip technology offers large space savings since the I/O can be arranged in an array on both the die and the substrate. At the substrate level, routings can be directed through multiple internal layers [4]. The short signal paths associated with the flip chip technology provide low inductance, resistance and capacitance, resulting in faster signal propagation and better high frequency performance.

Fig. 2.2 Flip chip package example

The major disadvantage of this technology is the poor heat dissipation. Since the die is flipped over when attached to the mounting substrate, the back of the die is left unattached to any good heat dissipation path. This also applies on the coefficient of thermal expansion (CTE) mismatch between the silicon and organic PCB leading to cracking of the solder bumps.

Different thermal dissipation techniques have been introduced to enhance this kind of package's thermal properties, [5] including leaving an air cavity between the die and the lid (instead of direct lid-die contact) to aid heat dissipation as well as introducing a special metal heat spreader onto the top of the package. Determining an optimum metal thickness for the heat spreader can improve the thermal management at the package level; hence the die junction temperature can be maintained at a minimum level. An added attraction is that the heat spreader also acts as an environmental protection to the die [5].

The other limiting factor associated with this technology is the cost, which is roughly 2-3 times that of an equivalent wire bond attachment on a per-pin basis [1].

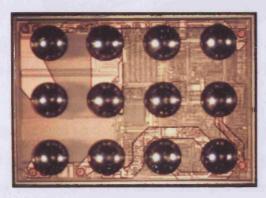

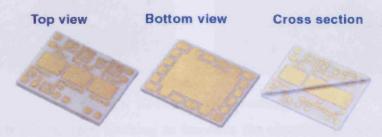

Wafer Level Chip Scale Packages (WLCSP): This package (Fig. 2.3) is an extension of the flip chip technology [6, 7] in the essence that the routing being performed on the die itself (no substrate is required) with the advantages of real die size packaging, high electrical performance and low manufacturing cost.

This kind of package architecture supports a high level of integration and multi-layer capability using a technology called stacked package-chip size package (SP-CSP) [8], where multiple dies are routed and stacked on top of each other to form a multilayer die structure.

Fig. 2.3 Wafer level chip scale package layout (WLCSP)

Despite these advantages, WLCSP technology is still not fully accepted since the mechanical reliability of a large die cannot be guaranteed. The main drawback of this technology is that it doesn't scale well with increasing die power and increasing temperature due to the mismatch in the thermal expansion coefficients between the silicon chip and the metallization and associated solder bumps (made of 95% tin) which reduce the package reliability. From the electrical point of view, an RF die should contain some RF circuitry and on-chip passive component(s) (e.g. inductors and de-coupling capacitors). Unfortunately since the routing in this technology is done on the silicon die after applying a thin layer of polymer on top of it therefore no routing is preferred on top of the critical RF chip components which will limit the routing area and the total number of balls.

With the mechanical issue, several researchers [9-11] have dealt with the issue of optimizing the solder bump shape and height (profile) to increase the package reliability against temperature cycles, including the incorporation of an underfill material to enhance the package's mechanical stability.

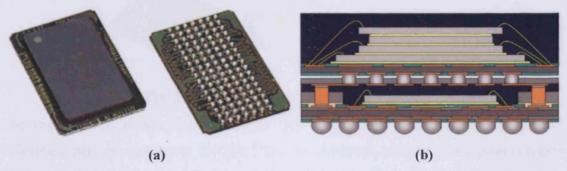

Ball Grid Array (BGA): This technology is similar to the Flip-chip technology in the essence that the die is mounted onto a substrate but here the die isn't flipped but mounted on its back onto the package substrate, the die pads are then connected to the package substrate through bonding wires from which the traces can be routed on the substrate top and bottom metallization layers and connected to the balls on the substrate bottom layer; BGA package examples are shown in Fig. 2.4.a below,

**Fig. 2.4** BGA package (a) finished package, (b) Stacked chips in stacked package-on-package (PoP) [12]

This technology allows multiple packages with multiple dies to be stacked on top of each other and bonded to the package substrate as shown in Fig. 2.4.b. In this example two BGA packages are stacked on top of each other in a technology called Package-on-Package (PoP). However there is a limit on the number of dies and packages which can be stacked on top of each other, this is because every time a die is attached the whole package has to be baked. Therefore there is maximum number of times the silicon can be exposed to heat (baked) without damaging its circuitry (usually this is specified by the silicon manufacturer).

The major disadvantage associated with this technology is the package poor ability to dissipate heat therefore thermal vias and centre thermal balls have to be used to provide sufficient thermal escape path. The manufacturing cost of BGA package is more than WLCSP and the plastic packages. However the assembly cost of BGA package is much less than the WLCSP which bring the cost of BGA solution well below the WLCSP solution.

Low Temperature Co-fired Ceramic (LTCC) Packages: This technology was originally developed for military applications where high performance and reliability are of the uppermost importance. The technology has subsequently established itself in a variety of commercial applications. LTCC layers are built up on individual layers of flexible ceramic tape which are pressed together and fired at 900°C, resulting in a

multi-layered ceramic structure which exhibits relatively low loss and shrinkage [1]. The other ceramic substrate types are made of Alumina which, thanks to its crystalline structure, can also provide a very low loss substrate suitable for use in RF and millimeter wave applications.

Fig. 2.5 Alumina ceramic package example

Several surface mount type packages (Fig. 2.5) have demonstrated very good electrical performance up to 50 GHz [13, 14]. However, thermal dissipation is a key challenge facing this kind of package which has always attempted to treat the problem at the package design level rather than optimizing the materials themselves [13]. Unfortunately, the cost for these packages is rather expensive due to the fact that the ceramic material and its manufacturing process is expensive and also the package tooling can be expensive since these substrates are brittle and therefore it is difficult to shape and saw. However when the package performance cannot be compromised, then this package is currently the best solution.

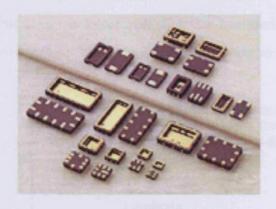

Laminate Based SMT/D Packages: Laminate based surface mount technology (SMT) packages (Fig. 2.6), or sometimes so called surface mount devices (SMD), is a new technology which targets the package cost issue by replacing the costly ceramic substrate with normal high frequency substrates (e.g. glass reinforced ceramic laminate).

Due to its flexibility when integrating it with other electronic components this kind of package has found its way into a number of current applications, such as mixers [15], millimeter-wave transceiver module [16], low noise amplifiers [17] and other MMIC applications [18, 19].

Although the cost of these packages is low compared to a corresponding ceramic packages and its frequency range can go up to 40 GHz, the electrical performance of these packages represents a challenge for package designers.

Fig. 2.6 SMT/D package examples

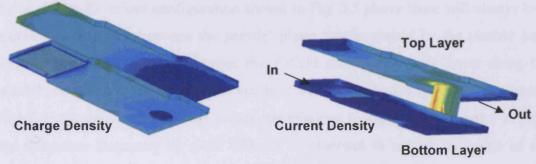

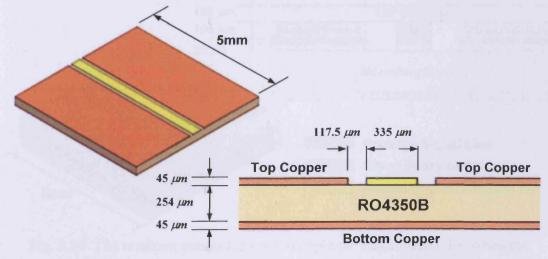

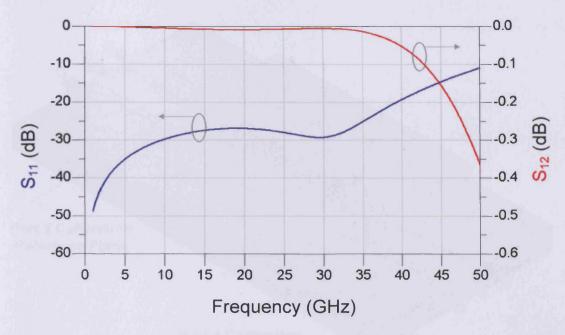

Many researches have been working to improve the electrical performance of these packages, including optimization of the transitions inside the package and the launching to the package from the PCB [13, 20-22]. Indeed, some researchers have started investigation into replacing the traditional laminates (e.g glass reinforced ceramic laminate) with high performance laminate materials such as liquid crystal polymers (LCP) [23-25]. These materials represent the cutting edge of MMIC packaging technology, and have shown that they are broadband and capable of competing with the expensive traditional ceramic substrates [25], a 50 Ohm, 1 cm LCP coplanar transmission line can have the frequency response shown in Fig. 2.7.

Fig. 2.7 Measured return and insertion loss of a CPW line on a 125 μm thick LCP substrate (width=235.5 μm, gap=50 μm) [25]

This material holds a great promise to significantly impact the packaging market, with the only problem associated with it being its high z-axis expansion. Novel DC-60GHz packages made of LCP substrate have been reported [26] with 0.5dB of insertion loss and more than 10 dB of return loss. The design of such packages relies on normal through vias coupled with complex in-package matching techniques.

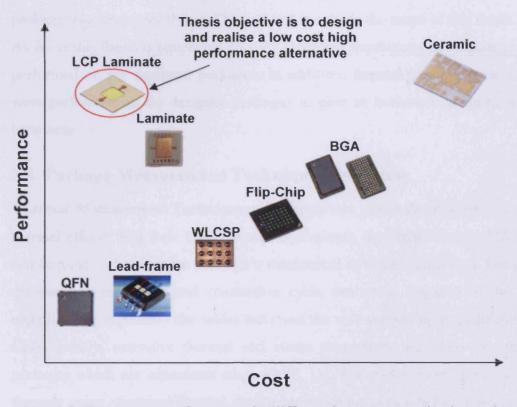

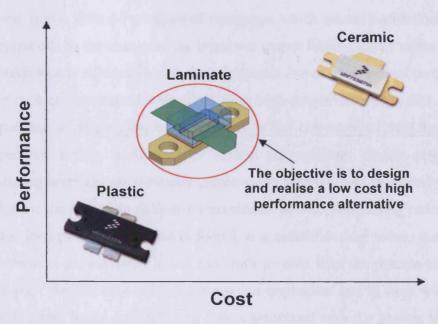

The objective of this work on low power packages is to develop a high performance low power package with similar performance to the best performing ceramic packages but at much lower cost. Fig. 2.8 summarises the low power packaging technologies cost and performance and identifies where the objective package should be located.

Fig. 2.8 Cost versus performance for different low power packaging technologies

Regardless of the packaging technology, the package has to be measured and these measurements can be as diverse as the packaging technologies themselves. The measurements performed are usually governed by the package architecture, available equipment and the type of required data. However, in most cases and wherever applicable the package is designed first and then measured solely prior to chip integration for different parameters. These pre-integration measurements can give a clear indication about the package overall performance and reliability when it will be under operation. Among these measurements are the electrical measurements where the package is tested for its RF (analogue) and/or signal integrity (digital) performance (e.g. insertion loss, return loss, cross talk, cavity resonance, leakage current, RLGC model,...etc) to make sure that the RF and digital paths are well designed and therefore optimised. Other measurements involve measuring the package thermal performance which also describes the package's mechanical stability under thermal cycle tests (i.e. to make sure no cracks will develop when the package is exposed to thermal cycles). Other industry standard tests include a drop-test, which

involves the package being attached to a PCB board and then the whole board is dropped in test chamber at specific speed and acceleration to emulate the physical drop effect; this test is very useful to check the package to PCB connection and die to package attachment reliability. This last test is outside the scope of this thesis.

As far as this thesis is concerned only RF electrical simulations and measurements are performed on the designed packages. In addition, thermal simulations and analysis were performed on the designed packages to give an indication about their thermal behaviour.

#### 2.3 Package Measurement Techniques Overview

Thermal Measurement Techniques: Although low power devices are less prone to thermal effects than their higher power equivalents, the higher density MMIC chips can become so hot that the package's mechanical structure is affected. For example, the package expansion and contraction cycle can cause fractures in the package metallization, especially the solder balls and the vias connecting metallization layers. Consequently, extensive thermal and stress simulations are often carried out on packages which are considered adequate [9, 11]. The package design process can go through many electrical/thermal design optimisation cycles before passing them to production.

Novel algorithms have been reported, which optimise the height and shape of the solder balls for BGA and WLCSP packages, [9, 10]. Other researchers went as far as to measure the package degradation after a number of temperature cycles (1000-2000 cycles) [5]. The published results from these tests show that the package degradation due to thermal expansion and contraction could be significant if not properly taken into account in the design process.

Electrical Measurement Techniques: A variety of different measurement setups have been utilised by researchers in the past in order to measure the various packaging architectures. For this work, only measurement techniques suitable for the laminate based SMT packages are discussed.

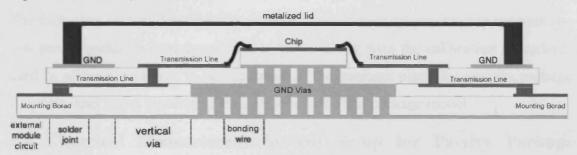

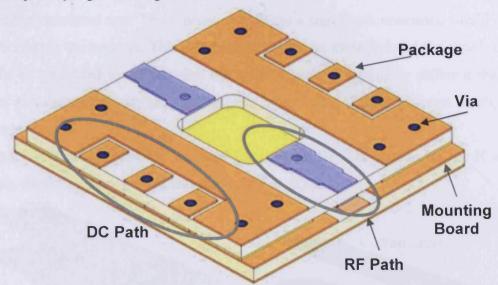

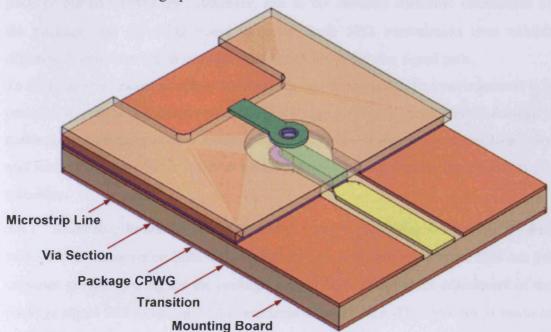

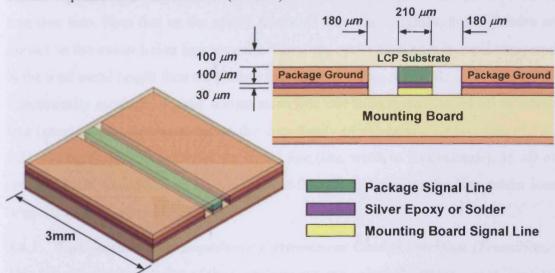

In the generic case, the packages are mounted on a PCB board which provides the launching terminal to the package as shown in Fig. 2.9 [26]. The package ground is presented through the use of multiple vias underneath the die to ensure low ground resistance and inductance while providing thermal escape path. Depending on the

transmission line environment employed in the package design (normally coplanar or conductor backed coplanar structures) the easiest test is to use on wafer probes to measure directly a package shorted with a thru line, this measurement will give a very basic (crude) knowledge about the package itself (no launching effect is taken into account). Another method involves placing the package on a test board and probing the package from one side (on the package top surface) while probing the test board (which is connected to the package bottom surface) from the other side [14]. This method can work provided that the package top surface transmission line configuration is suitable for probe measurement (e.g. Coplanar or conductor backed coplanar structures).

Fig. 2.9 Package mounted on mounting board and the die is placed inside the package and bonded[26]

Another method which tests the package quality is to bond up a precision load inside the package and by observing the package return loss, the package quality can be estimated [27]. Other tests involve placing a piece of transmission line in the package cavity and bonding it to the package using one or two (V-shape) bonding wires [28]. This test will give a rough estimation of the package's behaviour and will verify that no resonances occur at the frequency of interest.

More advanced techniques are available which involve mounting on wafer calibration standards in the place where the device is mounted and bonding them to the package. This approach is capable of giving a complete model for the package, including the launching transition and any via transition in the package transmission path [26]. However there is an increased level of measurement uncertainty associated with this technique due to the bonding wire discontinuity which might resonate at different frequencies depending on the standards attached to them and the wire bond length and profile. Add to that each calibration standard requires a separate package.

The ultimate package measurement requires the placement of an active device (MMIC) with complete bonding and a lid placed on top. The measured device

characteristics for this structure can then be compared to a reference dataset, for example an on-wafer measurement or a well known high quality packaged device of the same type [16-19].

From the above overview it is clear that placing simple Thru transmission line inside the package isn't adequate to reveal the package performance accurately. In order to generate an accurate model for the package to be used in a CAD environment (e.g. s-parameters model) a more complex measurement has to be performed. This implies the development of an accurate and robust measurement system calibrated using traceable standards and utilising multi-tier calibration techniques to shift the measurement reference plane up to the package plane.

The following section describes the passive measurement system used to measure the low power packages introduced in this thesis, along with the calibration procedures used to allow parameters to be measured at the package plane for various package structures and hence facilitating the extraction of a full package model.

# 2.4 Electrical Measurement System Setup for Passive Package Measurements

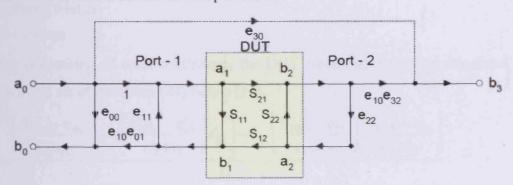

A test bench has been set up to enable the measurement and characterisation of the packages presented in chapter 3 of this thesis. This measurement setup is versatile enough to passively characterise the majority of packages.

Since the packages are normally mounted onto a test board with small feature sizes and were to be measured up to 50 GHz, on-wafer probing was considered the most suitable method to connect the packages and/or any associated mounting board to the measurement system.

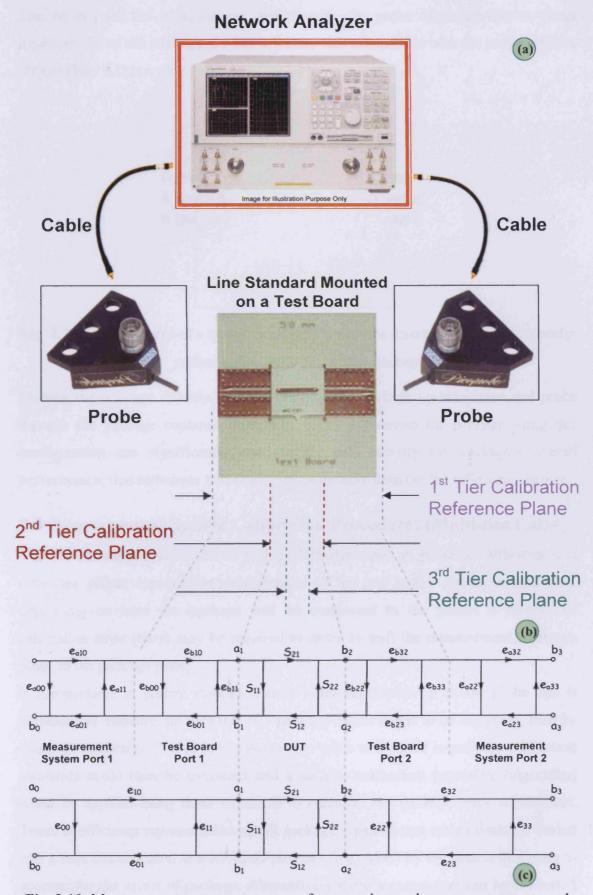

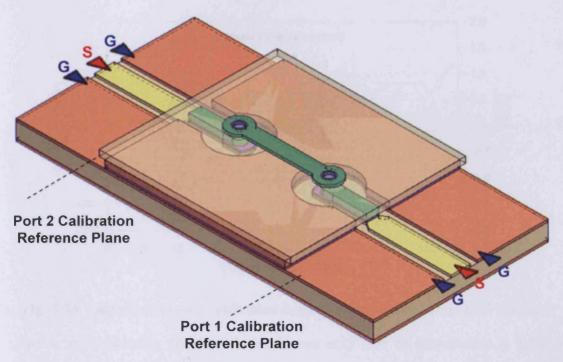

The measurement system was configured as shown in Fig. 2.10.a; in this measurement setup a Vector Network Analyser (VNA) was used as only linear measurements were required and no active devices were involved. High quality phase-stable, low-loss cables have been used to attach the VNA to a pair of DC-50 GHz GSG probes with 400 um pitch.

Thus, by probing onto a mounting board which is suitable for the probe pitch, and by applying a suitable calibration procedure(s), the measurement reference plane can be shifted to the package plane (Fig. 2.10.b,c).

Fig. 2.10 Measurement system setup to perform passive package measurements and the system equivalent error flow graphs

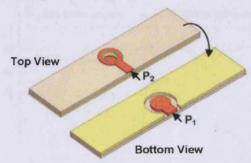

The novelty of the measurement system with the probe approach allows direct measurement of the package if it has a feature size compatible with the probe pitch of 400um (Fig. 2.11).

Fig. 2.11 Measurement of a typical package through the direct placement of on-wafer probes on the back side of the package

Probing the package directly involves flipping the package up-side-down and probe through the package coplanar lines (Fig. 2.11). Measuring the package using this configuration can significantly and quickly help identify the package's overall performance; this technique will be discussed in more detail in the following chapter.

# 2.5 Measurement System Calibration Procedures (Multi-tier Cal)

The measurement system shown in Fig. 2.10 describes all possible calibration and reference planes involved in measurement of the low power packages. However, depending on how the package will be connected to the probes a number of calibration steps (tiers) may be required in order to shift the measurement reference plane to the package plane.

If the package is probed directly then a 1-tier calibration up to the probe tips is sufficient to measure the package. If a package model needs to be extracted, then by using the calibrated probes (up to the probes tip) a new set of in-package calibration standards could then be measured and a suitable calibration procedure (algorithm) could be applied using these standards to calculate the package error coefficients. These coefficients represents the actual package s-parameters which could be buried into a data file and used in a RF CAD program (e.g. ADS) by the system designers to account for the effect of package. Alternatively these s-parameters can be converted

into RLGC model or SPICE model which then can be used by both the analogue and digital designers to include in their designs.

Since packages are normally attached to a mounting board therefore measuring an unmounted package on its own will not reveal the package actual performance although it can be used as a design aid to help optimise the package performance (e.g. to check the overall package performance, to identify if it is resonating at any specific frequency and determine the total loss the package exhibits before mounting it to any mounting board). The bare package and the data obtained from the bare package measurements can be considered as a platform for the next design step which is the package with mounting board. Therefore, in order to quantify the performance of the package to be used in the end application, the frequency response of the mounting board must also be included in the measurements. In order to achieve the necessary measurements at the package reference plane there are various kinds of calibration setups which can be adopted.

**Setup 1** - Is to calibrate the measurement system up to the probe tips (referred to as 1<sup>st</sup>-tier calibration) then perform another calibration using mounting board calibration standards to shift the measurement reference plane up to the package plane this is referred to as 2<sup>nd</sup>-tier calibration. A 3<sup>rd</sup>-tier calibration can also be implemented by measuring in-package standards. This calibration can reveal the actual package sparameters from which a package model can be extracted.

Setup 2 - The measurement system can be calibrated at once up to the package plane using a number of mounting board calibration standards (these can be made by fabricating different standards attached to the mounting board similar to the one which will be used to mount the package onto) which in this case represents the 1<sup>st</sup>-tier calibration. Again in order to generate a package model a 2<sup>nd</sup>-tier calibration is required where a range of in-package calibration standards are measured and the responses are used in a suitable calibration algorithm to calculate the package error coefficients and hence the actual response of the package (s-parameters).

Regardless of the package launching topology, the measurement system has to be calibrated up to a certain reference plane. This is done by measuring known calibration standards (e.g. Line, Thru, Open, Offset Open, Short, Offset Short, load, etc...) as part of a calibration procedure, such as SOLT, TRL, TRM, LRL, LRM,

etc... calibration procedures. The most popular standard calibration procedures are described briefly below:

**2.5.1 SOLT Calibration:** SOLT calibration stands for Short-Open-Load-Thru and in this kind of calibration a SOL calibration is performed on each port to fully calibrate out each port individually. The remaining Thru standard is then used to relate (link) the transmission error coefficients of both ports in a coherent way and also to compensate for any switching effect. The accuracy of this calibration is heavily dependant on the calibration standards definition, in other words the calibration uncertainty depends on how accurate the standards can be defined. The calibration standard manufacturer characterises each standard and generates a model which is converted into polynomial coefficients that are normally entered into the VNA. Unfortunately, when the on-wafer calibration standards are measured and remeasured numerous times (over the course of a number of different calibrations) they experience a change in their characteristics and consequently the coefficients stored in the VNA will not be as accurate. Ideally at this point these coefficients should be adjusted within the VNA definition. This requires a re-characterisation of the calibration substrate to generate the new polynomial coefficients which is difficult to achieve with a high degree of accuracy.

2.5.2 TRL/TRM Calibration: TRL calibration and TRM calibration (which is a specific example of a TRL calibration) are the most popular calibration procedures for on wafer calibration because they can give a very good [29, 30] calibration accuracy over a wide bandwidth. They achieve this because they rely on the accuracy of the Line (or Match for TRM) and Thru standard impedances which are normally set to 50 Ohm. These two calibration methods are described briefly below,

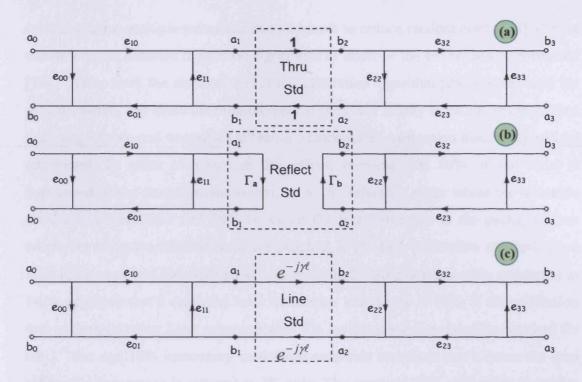

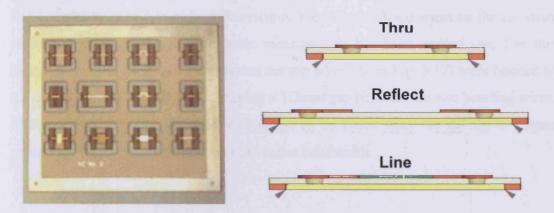

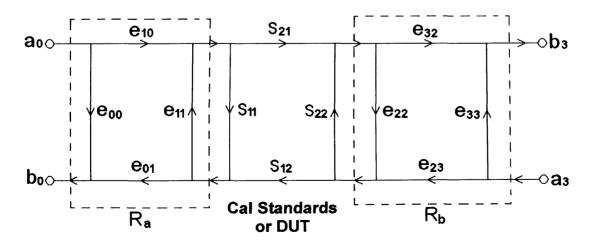

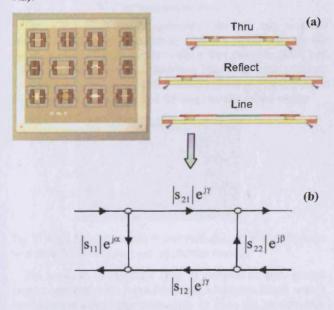

**TRL/LRL Calibration:** TRL calibration (Fig. 2.12) stands for Thru-Reflect-Line where the Thru standard is a line with 0 mm length, the Reflect standard can take different kinds (e.g. Open, Offset Open, Short, Offset Short), and the Line standard is a line similar to the Thru standard but of a different length.

Fig. 2.12 TRL calibration error flow graphs when calibration standards are attached

LRL stands for Line-Reflect-Line where the first Line standard represents a non zero length Thru standard, the Reflect standard is similar to TRL reflect and finally the second Line standard should be longer than the first Line (non zero length Thru) standard.

However in both TRL/LRL methods the Reflect standard has to be the same on both calibration ports and the reflect type should be known in order to solve for the calibration phase ambiguity.

Generally speaking TRL/LRL calibration is one of the most accurate calibration procedures since it relies solely on the impedance of the calibration lines and no standard definitions are required. Clearly, good quality and symmetrical lines with different lengths are essential to obtain a good calibration; it is therefore important that the line impedance is known prior to calibration. A great deal of research work has dealt with impedance measurement techniques [31, 32] where the impedance is calculated based on the measurement of the transmission line propagation constant. As far as this work is concerned, the calibration line impedance is determined from the direct measurement of the calibration lines after calibrating the measurement system up to the probe tips.

There has been a range of publications exploring the quality of TRL/LRL calibration techniques. Many publications have dealt with the issue of increasing the calibration

accuracy using multiple redundant line standards to reduce random errors [33]. Others use orthogonal distance regression algorithms to improve the calibration performance [30]. In this work the standard TRL/LRL calibration algorithm [29, 34] was used for measurements, and since the measurement system will mostly be calibrated in its first tier using known and traceable calibration standards the calibration inaccuracy will be minimised. In order to visualize this effect, consider that 80% of the error is introduced in the measurement system up to the reference plane where the traceable standards are attached and 20% is within the test fixture up to the package plane where the non-traceable standards are attached, if the TRL calibration standards have 10% inaccuracy and the calibration was performed (using non-traceable standards) in 1-tier approach that's mean the total calibration inaccuracy is 10%. If the calibration was performed using 2-tier approach with 0% inaccuracy in the traceable standard for the 1<sup>st</sup> tier and 10% inaccuracy in the non-traceable standards that's mean the total calibration inaccuracy is reduced to 2% only. The standard TRL calibration algorithm is described in details in appendix A of this thesis [34].

The other important issue associated with TRL/LRL calibration is the determination of the calibration line lengths. Several publications have dealt with this issue [35, 36] and a summery of the line length calculations is given below.

Assuming a transmission media which supports a linear phase, the following expressions can be used to select a Line with ¼ wavelength length at the desired centre frequency.

Electrical Length=

$$V_f$$

\* Free Space Length \* Line Wavelength (2.1)

Where

$$V_f$$

(Velocity factor %) =  $\frac{1}{\sqrt{\varepsilon_e}}$

Line Wave Length =  $\frac{1}{4}$ ,  $\frac{1}{2}$  etc.

Free Space Electrical Length =

$$\frac{C}{f}$$

C (Speed of light) =  $2.997925 * 10^8$  m/s and f (Frequency) in GHz For a Line wavelength of  $\frac{1}{4}$ , substituting into equation (2.1):

Electrical Length =

$$V_f * \frac{C}{f} * \frac{1}{4}$$

(2.2)

In order to cover the whole desired frequency range  $(f_1 \text{ to } f_2)$ , f should be the centre frequency of the range, Therefore equation (2.2) can be written as:

Electrical Length (*l*) =

$$V_f * \frac{2.997925*10^8}{\frac{f_1 + f_2}{2}} * \frac{1}{4}$$

[m]

Electrical Length (l) =

$$V_f * \frac{14.989625}{f_1 (GHz) + f_2 (GHz)}$$

[cm] (2.3)

To determine whether the Line meets the conditions of the acceptable insertion phase (an 8:1 frequency span, harmonic frequencies bandwidth) the following equation is used to check the boundary frequencies (i.e.  $f_1$  and  $f_2$ ).

Phase (degrees) =

$$360 * f * l * \sqrt{\varepsilon_e} / C$$

(2.4)

Note that a phase difference between  $18^{\circ}$  and  $162^{\circ}$  has proven to be adequate in some cases. However the National Institute of Standards Technology (NIST) and Hewlett-Packard (HP) both recommend that the phase difference should remain between  $30^{\circ}$  and  $150^{\circ}$ . In order to cover greater than an 8:1 frequency span, multiple lines might be used. To do that, the desired frequency span must be divided, allowing ½ wavelength LINE to be used over the lower portion of the frequency span and another one to be used for the upper band. The optimal break frequency is the geometric mean frequency ( $\sqrt{f_1 * f_2}$ ).

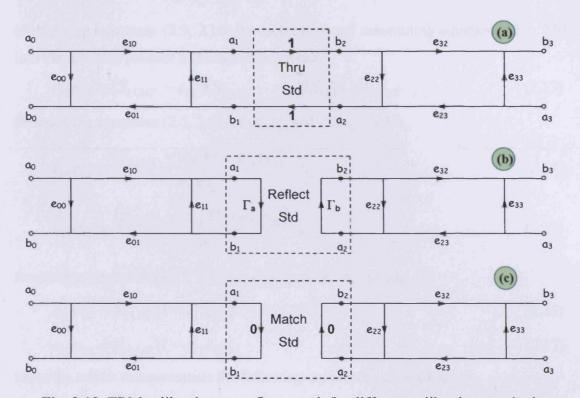

**TRM/LRM Calibration:** TRM/LRM calibration has the same definition as TRL/LRL calibration except that the Line standard is replaced by a Match (Load) standard.

This kind of calibration is much easier to implement compared to the TRL calibration. The accuracy of this calibration procedure depends on the Thru standard impedance and the Match standard quality. Again in order for the algorithm to work it is essential to have symmetrical reflects on both measurement system ports.

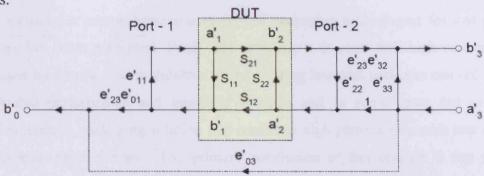

The TRM algorithm could be easily formalised by depicting the error flow graph of Fig. 2.10.c while replacing the DUT with the calibration standards, this is shown in Fig. 2.13 below,

**Fig. 2.13** TRM calibration error flow graph for different calibration standards From the Thru standard measurement the following four equations can be written,

$$S_{11MT} = e_{00} + \frac{e_{01}e_{10} \cdot e_{22}}{1 - e_{11}e_{22}} \tag{2.5}$$

$$S_{22MT} = e_{33} + \frac{e_{23}e_{32} \cdot e_{11}}{1 - e_{11}e_{22}}$$

(2.6)

$$S_{21MT} = \frac{e_{23}e_{10}}{1 - e_{11}e_{22}} \tag{2.7}$$

$$S_{12MT} = \frac{e_{32}e_{01}}{1 - e_{11}e_{22}} \tag{2.8}$$

Rearranging (2.5 and 2.6) yields

$$S_{11MT} - e_{00} = \frac{e_{01}e_{10} \cdot e_{22}}{1 - e_{11}e_{22}} \tag{2.9}$$

$$S_{22MT} - e_{33} = \frac{e_{23}e_{32} \cdot e_{11}}{1 - e_{11}e_{22}} \tag{2.10}$$

From the match measurements the following can be obtained

$$S_{11MM} = e_{00} (2.11)$$

$$S_{22MM} = e_{33} (2.12)$$

Multiplying equations (2.9, 2.10) by each other and substituting equations (2.7, 2.8) into the resultant product and simplifying yields,

$$e_{11}e_{22} = (S_{11MT} - e_{00})(S_{22MT} - e_{33})/S_{12MT} \cdot S_{21MT}$$

(2.13)

Rearranging equations (2.5, 2.6) for  $e_{01}e_{10}$  and  $e_{23}e_{32}$  yields,

$$e_{01}e_{10} = \frac{\left(S_{11MT} - e_{00}\right)\left(1 - e_{11}e_{22}\right)}{e_{11}e_{22}} \cdot e_{11}$$

(2.14)

$$e_{23}e_{32} = \frac{\left(S_{22MT} - e_{33}\right)\left(1 - e_{11}e_{22}\right)}{e_{11}e_{22}} \cdot e_{22} \tag{2.15}$$

Rearranging equations (2.7, 2.8) for  $e_{23}e_{10}$  and  $e_{32}e_{01}$  yields

$$e_{23}e_{10} = S_{21MT}(1 - e_{11}e_{22}) (2.16)$$

$$e_{32}e_{01} = S_{12MT}(1 - e_{11}e_{22}) (2.17)$$

From the reflect measurements the following equations can be obtained,

$$S_{11MG} = e_{00} + \frac{e_{01}e_{10} \cdot \Gamma_a}{1 - e_{11} \cdot \Gamma_a}$$

(2.18)

$$S_{22MG} = e_{33} + \frac{e_{23}e_{32} \cdot \Gamma_b}{1 - e_{22} \cdot \Gamma_b}$$

(2.19)

Solving equations (2.18, 2.19) for  $\Gamma_a$  and  $\Gamma_b$  yields,

$$\Gamma_a = \frac{S_{11MG} - e_{00}}{e_{11} \left( \frac{e_{01}e_{10}}{e_{11}} - e_{00} + S_{11MG} \right)}$$

(2.20)

$$\Gamma_b = \frac{S_{221MG} - e_{33}}{e_{22} \left(\frac{e_{23}e_{32}}{e_{22}} - e_{33} + S_{22MG}\right)}$$

(2.21)

Assuming that the reflect standards on both ports are similar to each other, therefore equating equations (2.20, 2.21) and solving for  $e_{11}$  yields,

$$e_{11} = e_{22} \frac{\left(\frac{e_{23}e_{32}}{e_{22}} - e_{33} + S_{22MG}\right) \cdot \left(S_{11MG} - e_{00}\right)}{\left(\frac{e_{01}e_{10}}{e_{11}} - e_{00} + S_{11MG}\right) \cdot \left(S_{221MG} - e_{33}\right)}$$

(2.22)

Substituting equation (2.13) into (2.22) and solving for  $e_{11}$  yields,

$$e_{11}^{2} = \frac{\left(\frac{e_{23}e_{32}}{e_{22}} - e_{33} + S_{22MG}\right) \cdot \left(S_{11MG} - e_{00}\right)}{\left(\frac{e_{01}e_{10}}{e_{11}} - e_{00} + S_{11MG}\right) \cdot \left(S_{221MG} - e_{33}\right)} \cdot \frac{\left(S_{11MT} - e_{00}\right)\left(S_{22MT} - e_{33}\right)}{S_{12MT} \cdot S_{21MT}}$$

(2.23)

In order to solve equation (2.23) for  $e_{11}$  the magnitude of  $e_{11}$  can be revealed by taking its square root. The phase ambiguity can be solved by substituting  $e_{11}$  into equation (2.20) provided that the reflect type is specified prior to calibration. Having solved for  $e_{11}$  all error coefficients can be revealed.

# 2.5.3 Embedding and De-embedding Techniques

Embedding Techniques: If the calibration procedures are done in two tier steps (Fig. 2.10.a) then the equivalent error flow graph (Fig. 2.10.b) can be combined to form a single flow graph which includes the error coefficients from the two tier calibration (Fig. 2.10.c). Using flow graph analysis [37], the error flow graph model of Fig. 2.10.b can be converted into the error model of Fig. 2.10.c using the following set of equations,

#### Port 1:

$$\begin{split} e_{00} &= e_{a00} + \frac{e_{a01}e_{a10}e_{b00}}{1 - e_{a11}e_{b00}} \\ e_{11} &= e_{b11} + \frac{e_{b01}e_{b10}e_{a11}}{1 - e_{a11}e_{b00}} \\ e_{21} &= \frac{e_{b10}e_{a10}}{1 - e_{a11}e_{b00}} \\ e_{12} &= \frac{e_{a01}e_{b01}}{1 - e_{a11}e_{b00}} \end{split}$$

#### Port 2:

$$e_{22} = e_{b22} + \frac{e_{b32}e_{b23}e_{a22}}{1 - e_{b33}e_{a22}}$$

$$e_{33} = e_{a33} + \frac{e_{a32}e_{a23}e_{b33}}{1 - e_{b33}e_{a22}}$$

$$e_{32} = \frac{e_{b32}e_{a32}}{1 - e_{b33}e_{a22}}$$

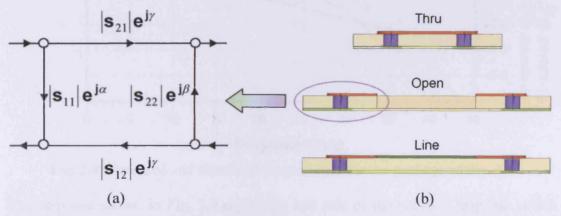

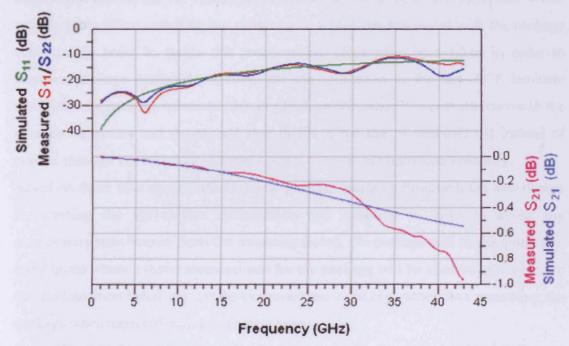

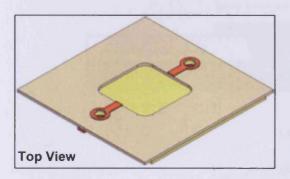

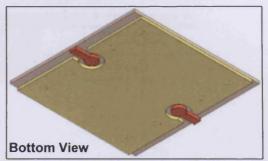

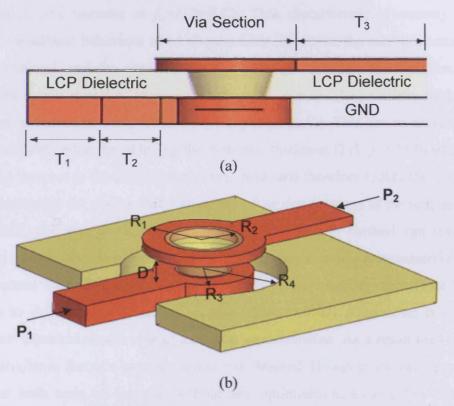

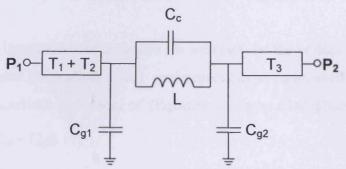

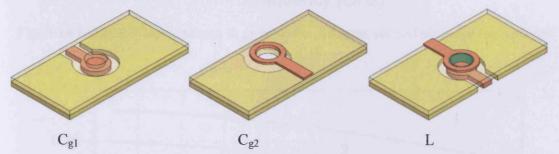

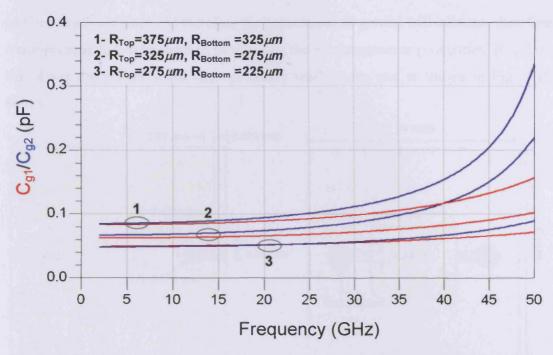

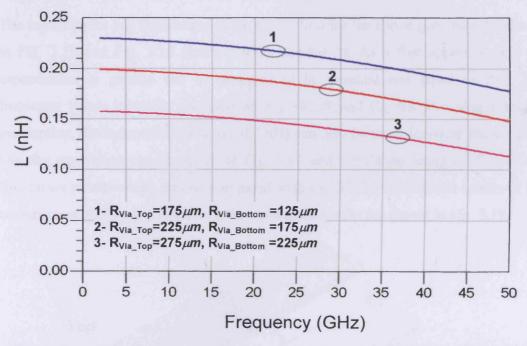

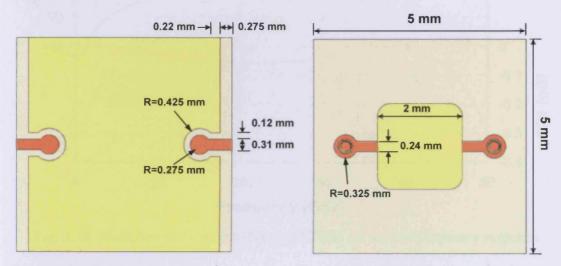

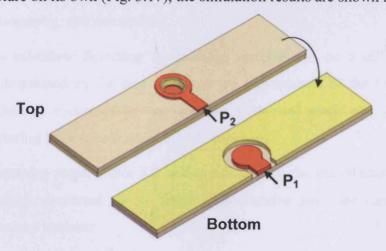

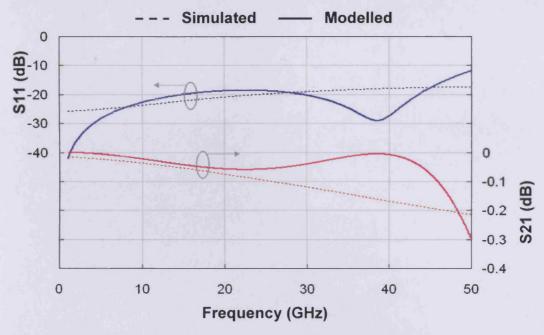

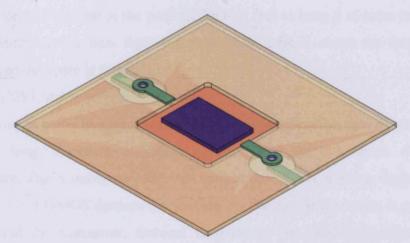

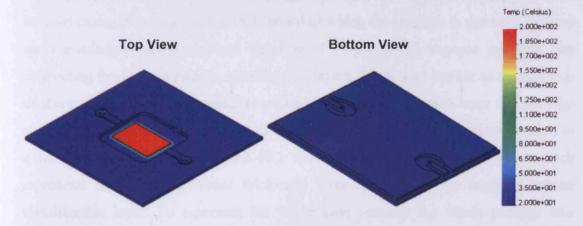

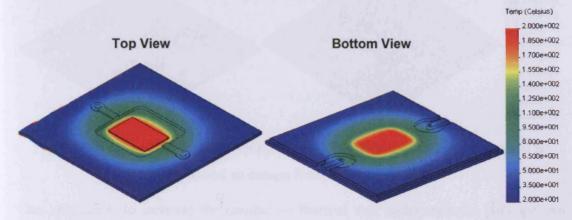

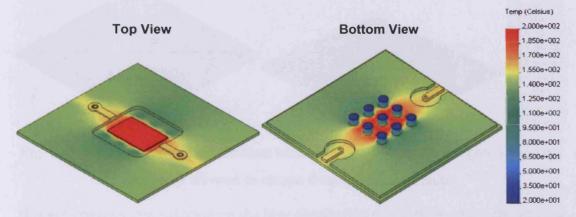

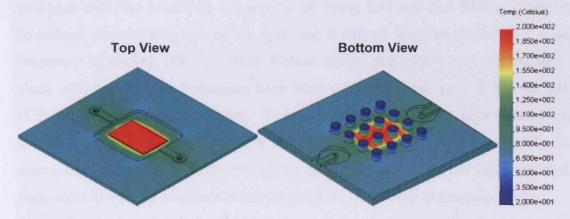

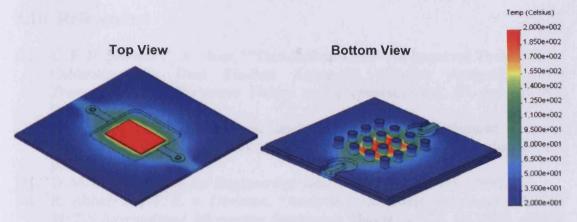

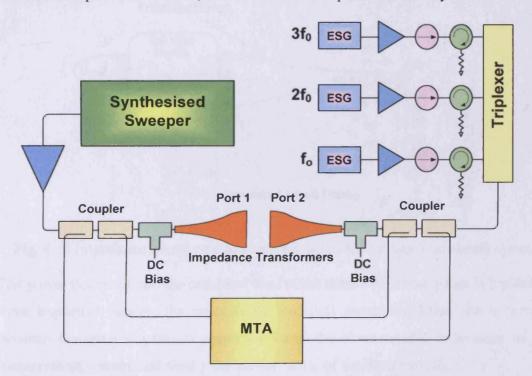

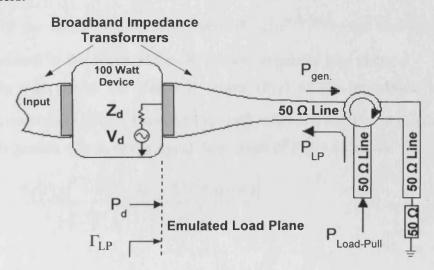

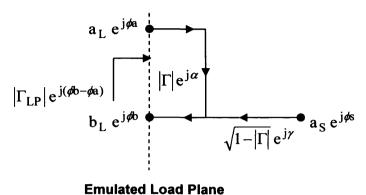

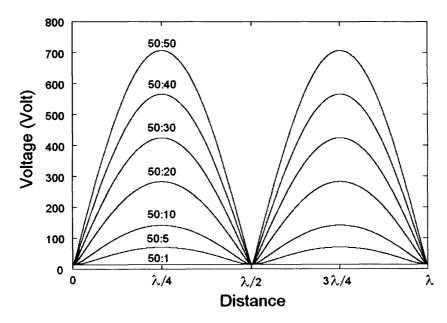

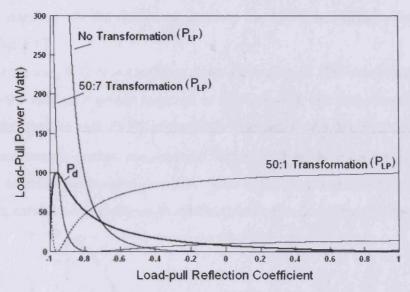

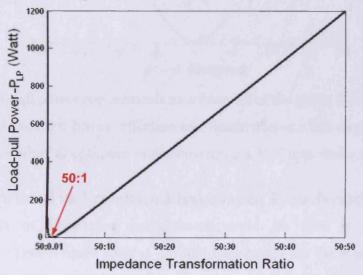

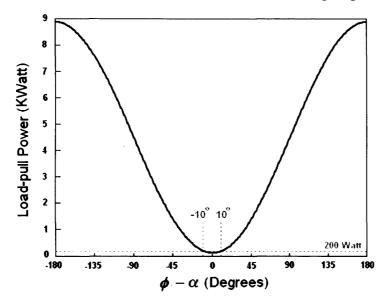

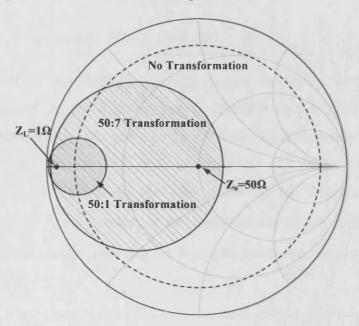

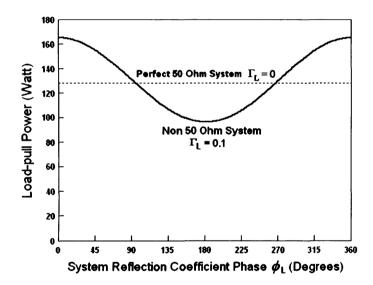

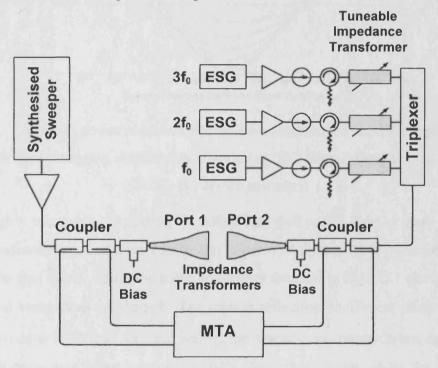

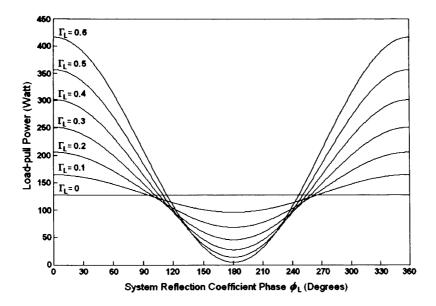

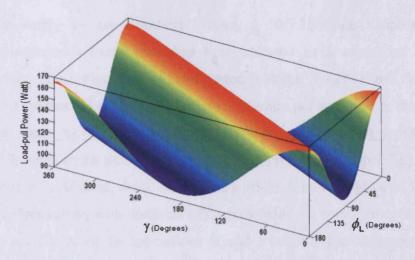

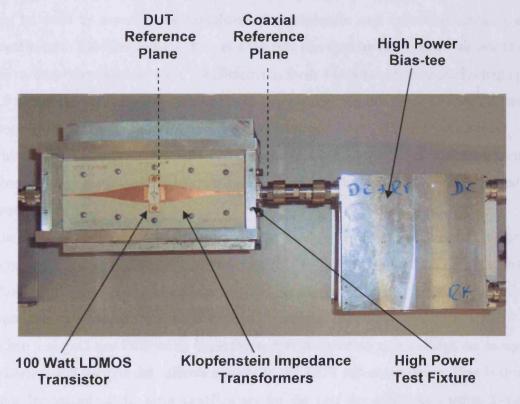

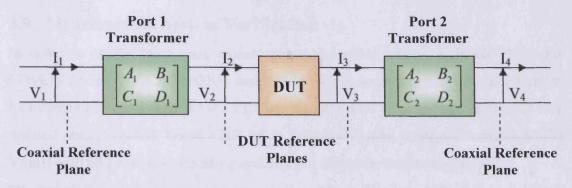

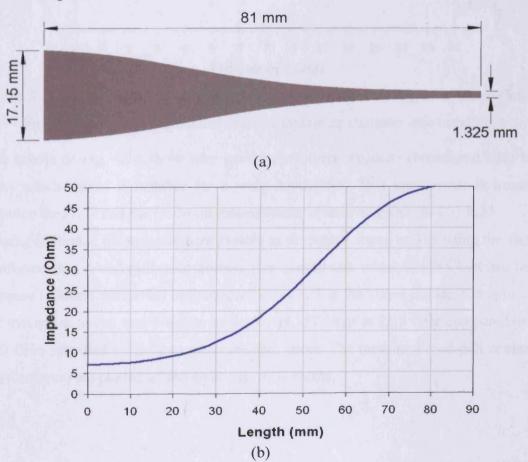

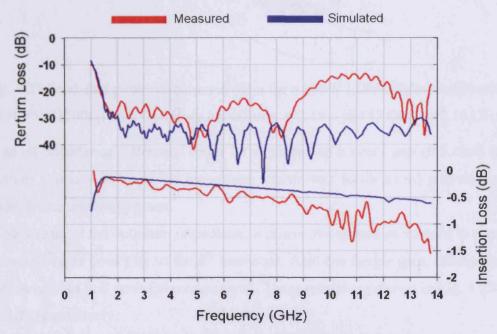

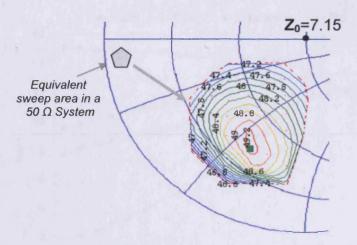

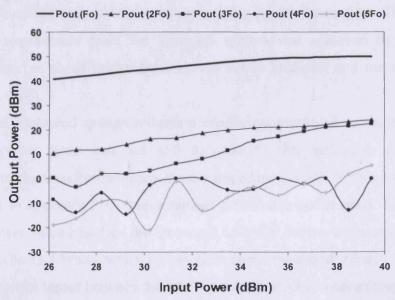

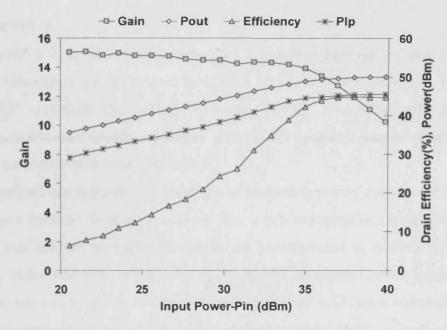

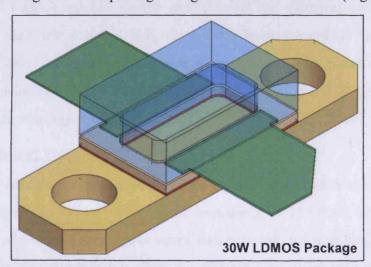

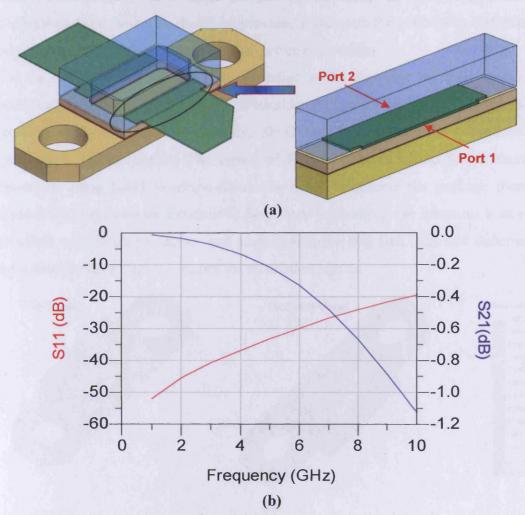

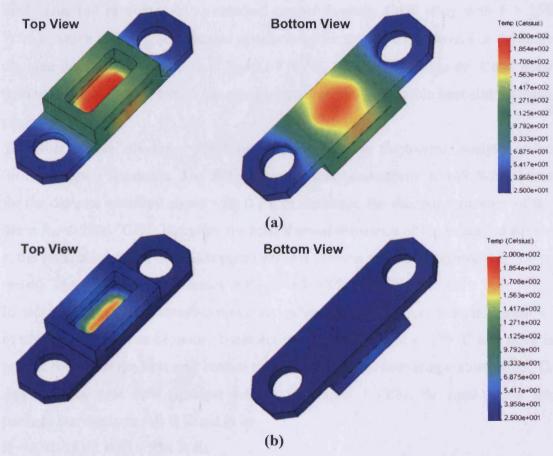

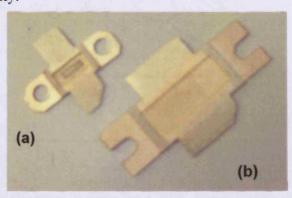

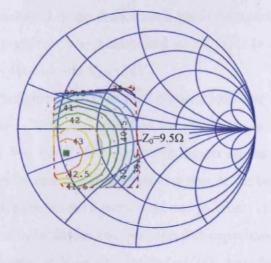

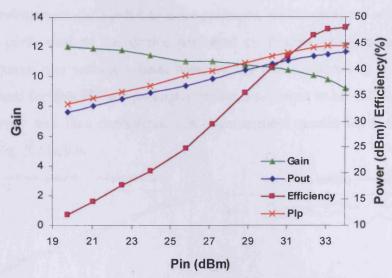

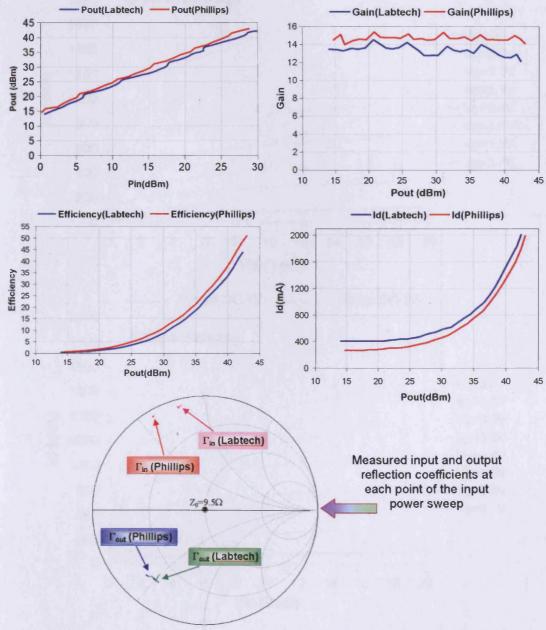

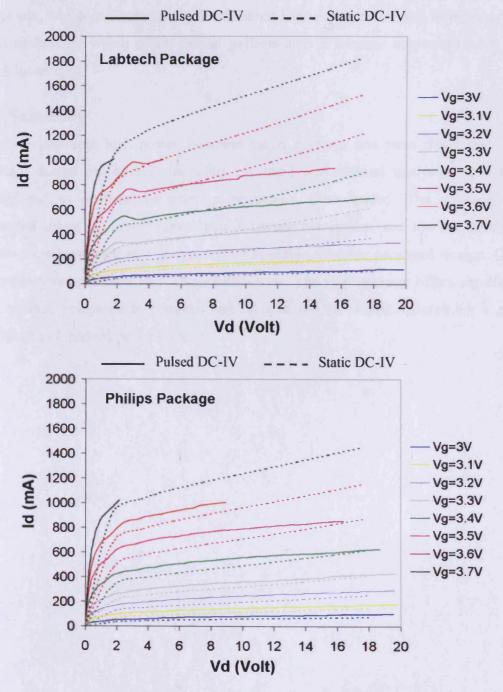

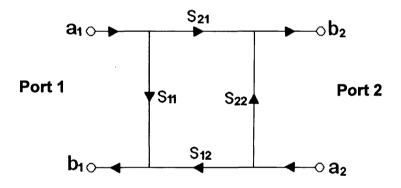

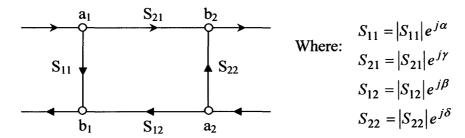

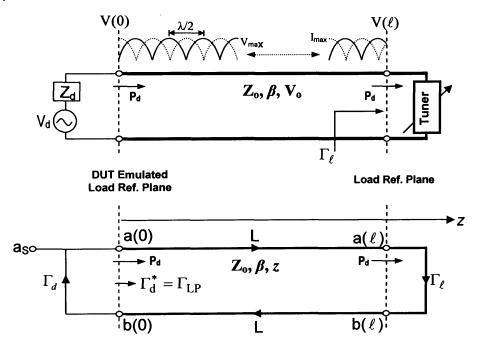

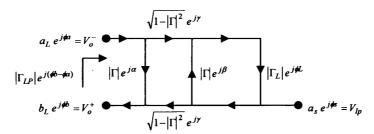

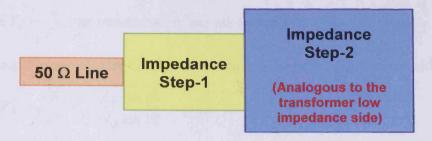

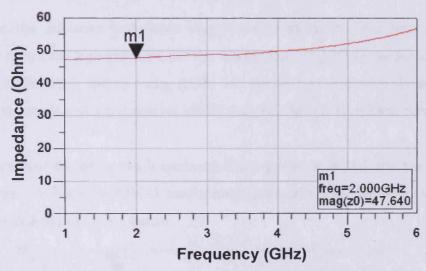

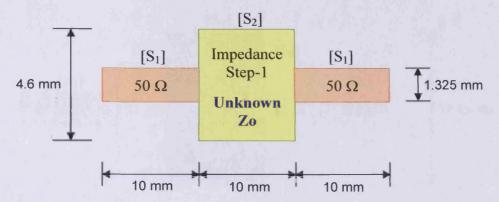

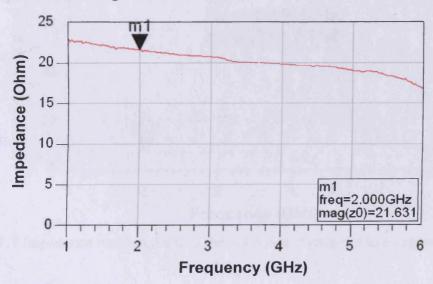

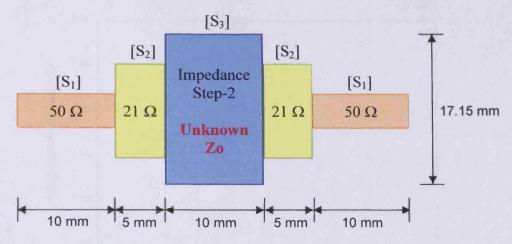

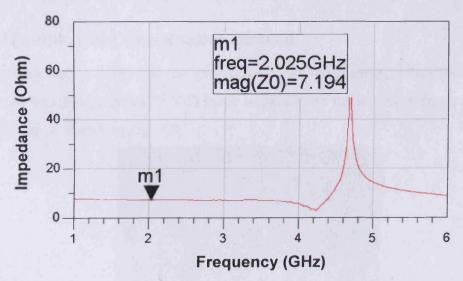

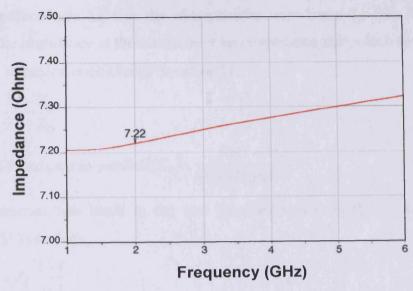

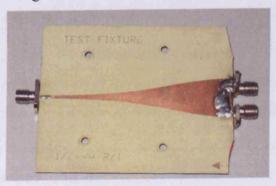

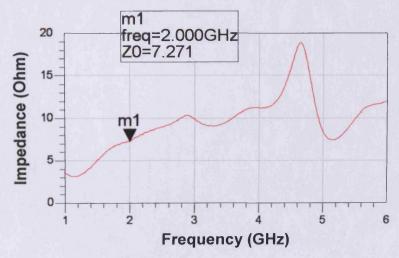

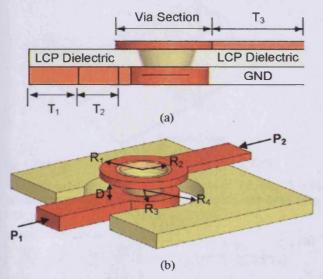

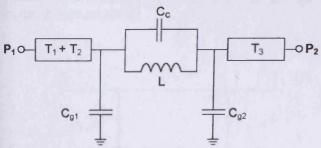

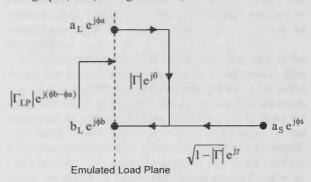

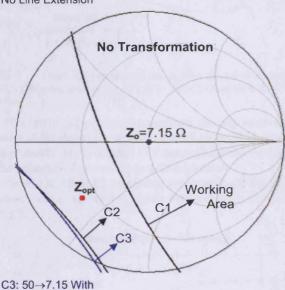

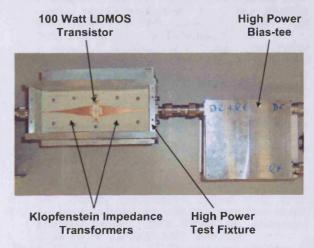

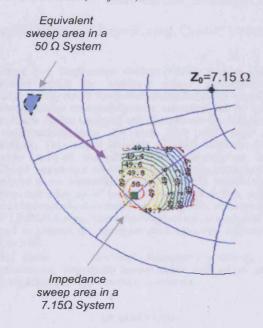

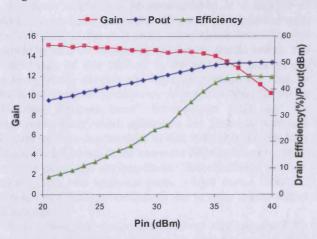

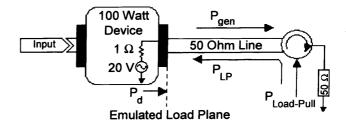

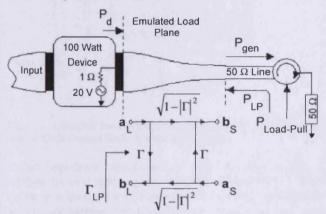

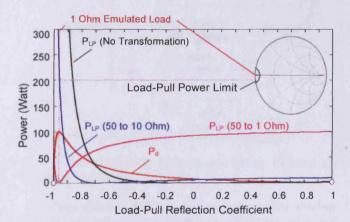

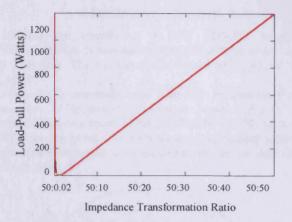

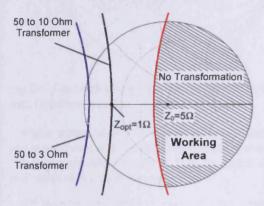

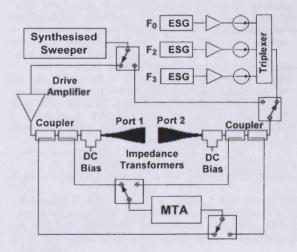

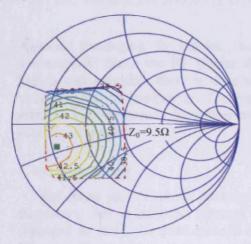

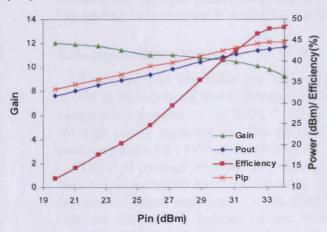

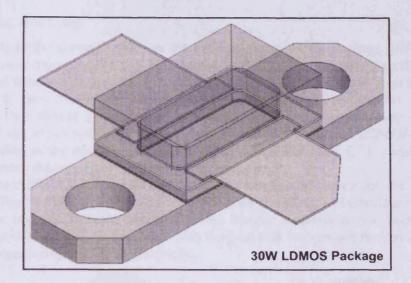

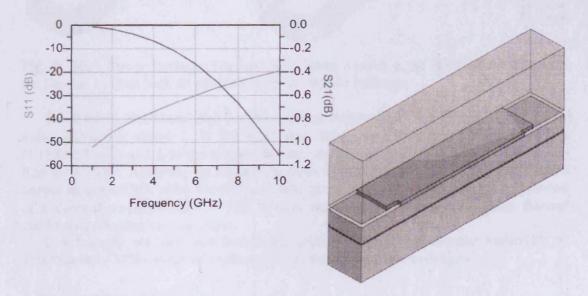

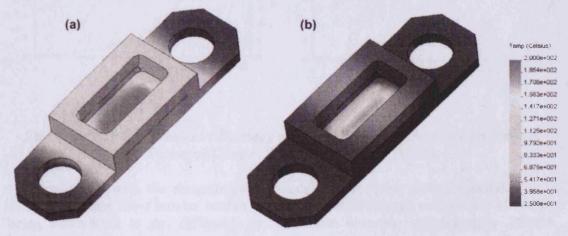

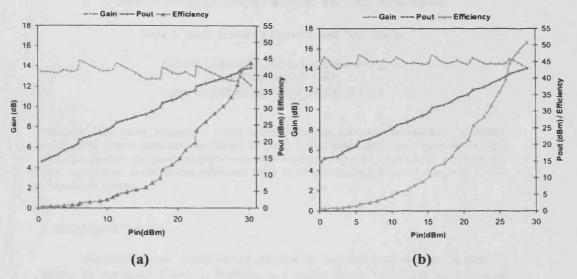

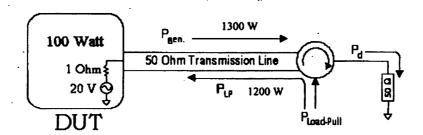

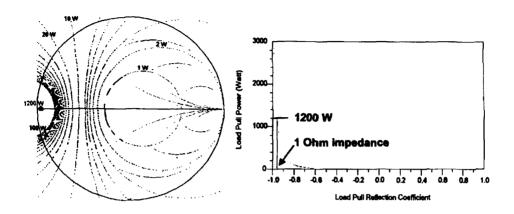

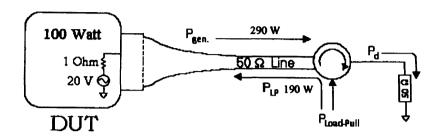

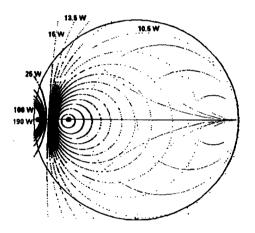

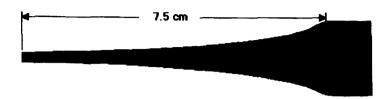

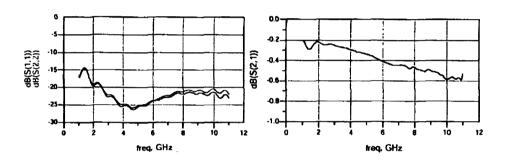

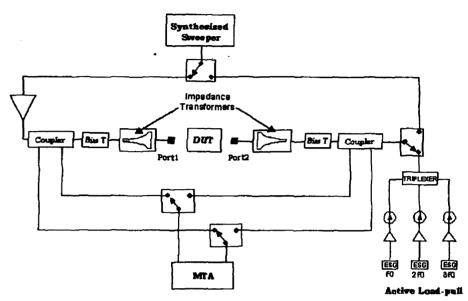

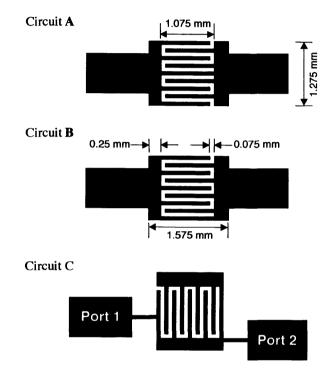

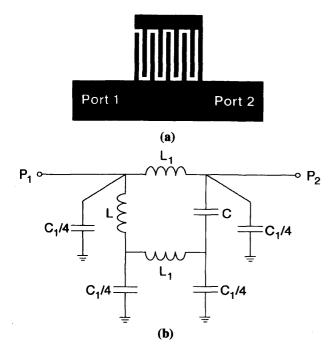

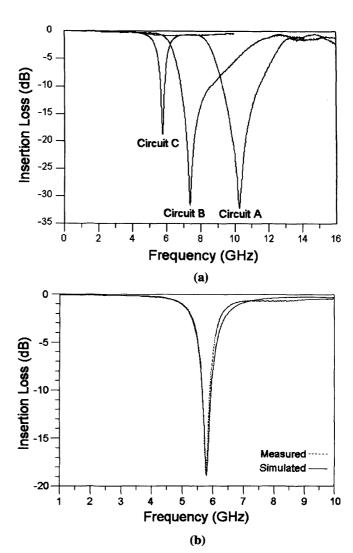

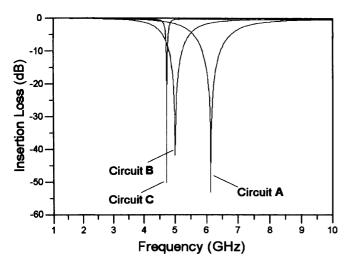

$$e_{23} = \frac{e_{b23}e_{a23}}{1 - e_{b33}e_{a22}}$$