# High Power Waveform Engineering

A thesis submitted to the University of Wales, Cardiff In candidature for the degree of

**Doctor of Philosophy**

**By**Aamir Sheikh

Centre for High Frequency Engineering

School of Engineering

Cardiff University

United Kingdom

**June 2010**

UMI Number: U585425

### All rights reserved

### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

### UMI U585425

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### **Acknowledgements**

In the name of Allah, the most merciful and most beneficient.

I would first like to thank Allah (swt) for giving me the opportunity to work with the most interesting and deeply devoted people to RF I am likely to meet in my life. I would like to thank Prof. Paul Tasker for his highly valued support, enthusiasm and for the many hours of conversations that have helped me develop a great love and appreciation of not only the topic of this thesis but also for the subject of RF at large. I would also like to thank Prof. Johannes Benedikt, for guiding me in this work and for keeping me on track. I would also like to extend my gratitude towards Nokia Siemens Networks for sponsoring my PhD in particular Samu Saarinen and Freescale Semiconductor in particular Peter Aaen, for providing me the opportunity to work within the modelling group.

During my PhD, I have had the opportunity to work with a large group of colleagues and friends. I would firstly like to thank Dr. Jonathan Lees for providing me early guidance in Doherty amplifiers and always being my first source of help. I would also like to thank Chris Roff, Tudor Williams, Peter Wright and Simon Woodington for their many hours of company in and out of the RF lab as well as the numerous others for their help, guidance and hours of conversations. I hope to meet you all in my future career.

I would finally like to give a big thank you to my parents and two sisters for their unending support and encouragement during the busy extremely very busy times during my PhD. They have always been there for me and I hope that I am there for them whenever the opportunity arises.

# Contents

| 1 |                                                               |                                                                      |            |  |  |

|---|---------------------------------------------------------------|----------------------------------------------------------------------|------------|--|--|

| 2 | List of Publications                                          |                                                                      |            |  |  |

| 3 | Glossary o                                                    | of Terms                                                             | .10        |  |  |

| 4 | Introduction                                                  | on                                                                   | .11        |  |  |

| 5 | Time Dom                                                      | nain De-embedding                                                    | .20        |  |  |

|   |                                                               | affect of Parasitic Components to Time-Domain Waveforms              |            |  |  |

|   |                                                               | ntrinsic and Extrinsic Lumped Component Passive Device               |            |  |  |

|   |                                                               |                                                                      | .24        |  |  |

|   |                                                               | Packaging Components Passive Device Modelling                        |            |  |  |

|   |                                                               | Circuit combinations and some possible side-effects                  |            |  |  |

|   |                                                               | Domain De-embedding of a Medium Power Device                         |            |  |  |

|   |                                                               | Passive modeling of the device                                       |            |  |  |

|   |                                                               | Obtaining waveforms at the I-gen plane                               |            |  |  |

|   | 5.2.3                                                         | Quantifying the effects of feedback in a real device                 | 49         |  |  |

|   | 5.3 Uncer                                                     | tainty Analysistainty Analysis                                       | . 17<br>51 |  |  |

|   |                                                               | Domain De-embedding of a High Power Device                           |            |  |  |

|   |                                                               | Potential issues with high power de-embedding                        |            |  |  |

|   |                                                               | De-embedding a high power device                                     |            |  |  |

|   |                                                               | usionsusions                                                         |            |  |  |

| 6 |                                                               | t of System Impedance on High Power Measurements                     |            |  |  |

| U |                                                               | th Power Device Measurement in Two Different Impedance               |            |  |  |

|   | Environments                                                  | •                                                                    | 61         |  |  |

|   |                                                               | ffect of Higher Harmonic Terminations (Real only)                    |            |  |  |

|   |                                                               |                                                                      | .04        |  |  |

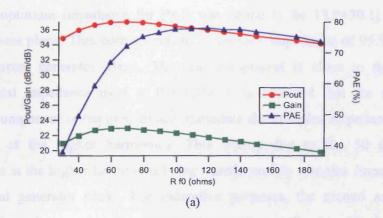

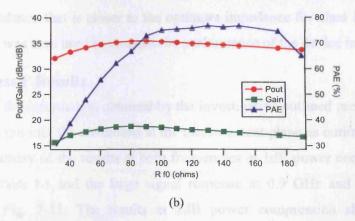

|   |                                                               | The Effect of System Impedance in a High Power Si LDMOS              |            |  |  |

|   |                                                               | (0)                                                                  | 71         |  |  |

|   |                                                               | ffect of the Higher Harmonics (Reactive only)                        |            |  |  |

|   |                                                               |                                                                      |            |  |  |

|   |                                                               | Theory                                                               |            |  |  |

|   |                                                               | Measurement Comparison                                               |            |  |  |

| _ |                                                               | usions                                                               | .82        |  |  |

| 7 | waveform ripphoanons waveform Basea ringh Bineformy wiedes of |                                                                      |            |  |  |

|   | -                                                             |                                                                      |            |  |  |

|   |                                                               | ency Enhancement                                                     |            |  |  |

|   |                                                               | Class D                                                              |            |  |  |

|   |                                                               | Class E                                                              | .87        |  |  |

|   |                                                               | Class F and Inverse Class F (F <sup>-1</sup> )                       |            |  |  |

|   |                                                               | Summary                                                              | .90        |  |  |

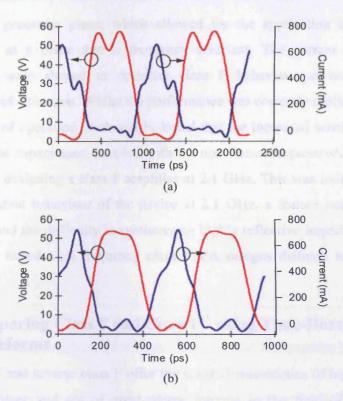

|   |                                                               | form Engineering of Si LDMOS Devices for High Efficiency             |            |  |  |

|   |                                                               | eration                                                              |            |  |  |

|   |                                                               | De-embedding to the Current Generator Plane                          |            |  |  |

|   |                                                               | Class F Investigation                                                |            |  |  |

|   |                                                               | Class F Results1                                                     |            |  |  |

|   |                                                               | Conclusions1                                                         |            |  |  |

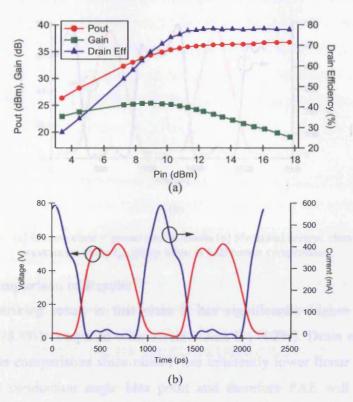

|   |                                                               | aring Class F and Class F <sup>-1</sup> using Time-Domain Waveforms1 |            |  |  |

|   |                                                               | The Effect of Limited Bandwidth1                                     |            |  |  |

|   | 7.3.2 R                                                       | Results1                                                             | 07         |  |  |

|                                                                  | 7.3.3     | .3 Inverse Class F Perform      | ance Optimisation1             | 10  |

|------------------------------------------------------------------|-----------|---------------------------------|--------------------------------|-----|

|                                                                  | 7.4       | 1                               | 11                             |     |

| 8 Waveform Applications – Waveform Based Verification of a Charg |           |                                 |                                |     |

| Conservative Model                                               |           |                                 |                                |     |

|                                                                  | 8.1       |                                 |                                |     |

| 8.2 The Benef                                                    |           | The Benefits of Time Domain     | n Model Validation1            | 15  |

|                                                                  |           | Measurement and Model Und       | certainties1                   | 16  |

|                                                                  | 8.4       | Model Validation Results        |                                | 18  |

|                                                                  | 8.4.      | .1 Results comparison at th     | e transistor output terminals1 | 19  |

|                                                                  | 8.4.2     | .2 Results comparison at the    | e intrinsic device plane1      | 21  |

|                                                                  | 8.5       | Further Analysis of the Mode    | l's Individual Components1     | 22  |

| <b>▼</b>                                                         |           |                                 | uct High Efficiency Waveform   |     |

|                                                                  |           | eering                          | 1                              | 24  |

|                                                                  | 8.6.      |                                 | 1                              | 24  |

|                                                                  | 8.6.2     | .2 Inverse Class F              | 1                              | 26  |

|                                                                  | 8.7       |                                 |                                |     |

| 9                                                                | Wa        | aveform Applications – Wavef    | orm Based Doherty Design1      | .32 |

|                                                                  | 9.1       | Conclusions                     |                                |     |

|                                                                  | 9.2       | Design of a High Power Doh      | erty Amplifierl                | 39  |

|                                                                  | 9.2.      |                                 |                                |     |

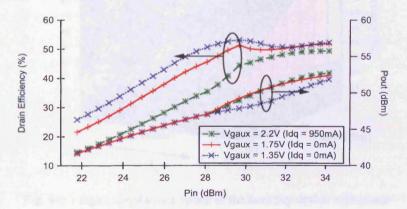

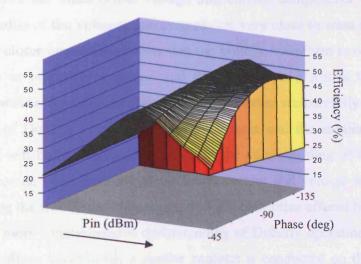

|                                                                  | 9.2.      | .2 Results                      |                                | 142 |

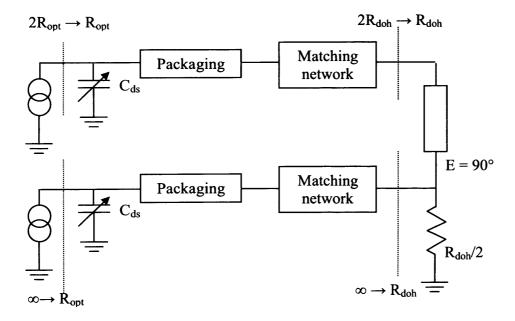

|                                                                  | 9.3       | Waveform Based Doherty Do       | Model                          |     |

|                                                                  |           |                                 |                                |     |

|                                                                  | 9.3.2     | .2 Results                      |                                | 147 |

| 9.4 Measurement Driven Doherty PA Design                         |           |                                 |                                |     |

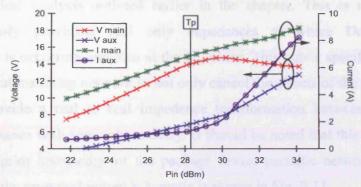

|                                                                  | 9.4.      | .1 Main Device                  |                                | 150 |

|                                                                  | 9.4.2     | .2 Auxiliary Device             |                                | 152 |

|                                                                  | 9.5       | Conclusion                      |                                | 161 |

| 1(                                                               | ) Cor     | nclusions                       |                                | 163 |

| 11                                                               | l Fut     | ture Work                       |                                | 168 |

|                                                                  | 11.1      | Further Developments in Hig     | h Power Modelling1             | 168 |

|                                                                  | 11.2      | Doherty Reliability Investiga   | tions1                         | 70  |

|                                                                  |           |                                 |                                |     |

| A                                                                | $1 - S_1$ | Small Signal Verification of Ch | arge Conservative Model1       | 79  |

|                                                                  | A1.1      |                                 |                                |     |

|                                                                  | A1.2      |                                 |                                |     |

| A                                                                | 2 - Si    |                                 |                                |     |

### 1 Summary

For many years industry has considered RF PA design to be a "black art". This perception has been held due to the lack of availability of meaningful information for analysis and design. Due to the emergence of large signal waveform based measurements and increased understanding in the literature, it is now possible to characterise devices and correlate the information for enhanced PA design in terms of efficiency, linearity and/or reliability. This has been well documented and demonstrated using on-wafer devices but where this thesis work begins, little work had been done in expanding this capability to higher more meaningful power levels using packaged devices.

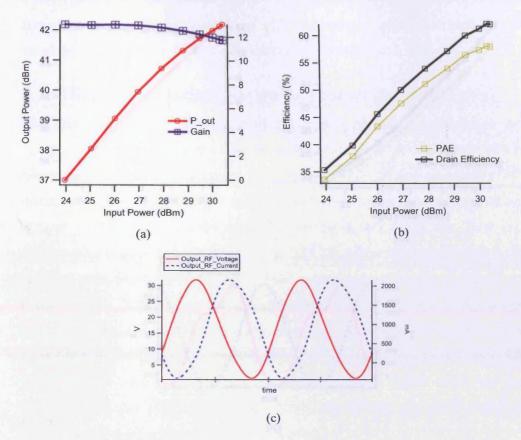

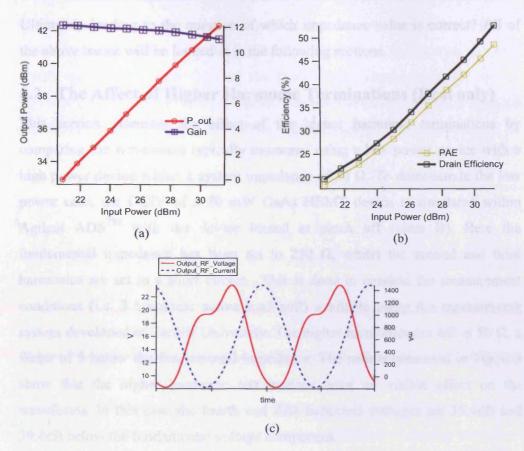

This work has successfully addressed both of these limitations and extended visibility of time domain waveform data to higher power levels. Thus, allowing for the uncovering of world record efficiency levels of 77 % (4W output power) for Si LDMOS devices at S band frequencies using waveform engineering based procedures, in this case Class F. A feat previously only reported at L-band frequencies. Other waveform based designs such as inverse Class F and Doherty modes of operation are also successfully demonstrated in this thesis. In both of these cases, voltage related issues affecting reliability were uncovered that merit further consideration in the design process.

Waveform engineering was made possible by applying de-embedding the measured current and voltage waveforms to the current generator plane. That is the plane at which the device is free from any device and package parasitics with the current and voltage waveforms seen to be in good agreement with those typically found in literature. These were successfully applied at high power levels (110W) previously not reported.

To further demonstrate the relevance of waveform de-embedding, a non-linear charge conservative model based on industry standard modelling techniques was compared against time-domain measurements conducted in several classes of operation. This form of model verification is often overlooked and provides a unique insight into the model's accuracy highlighting new areas of improvement. In most cases the model was shown to be in good agreement with measured data, providing a high level of confidence in the application of waveform engineering principles within the CAD domain. Thus providing the PA designer the facility to apply waveform engineering on both the test bench and within the CAD domain.

# 2 List of Publications

I. Aamir Sheikh, Chris Roff, Johannes Benedikt, Paul J. Tasker, Basim Noori, John Wood, Peter H. Aaen, "Peak Class F and Inverse Class F Drain Efficiencies Using Si LDMOS in a Limited Bandwidth Design", *IEEE Mi & Wire. Comp. Letters*, vol. 19, iss. 7, pp. 473-475.

Abstract - This paper compares two popular high power, high efficiency modes of operation, class F and inverse class F, and assesses the peak obtainable drain efficiencies when using Si LDMOS devices in a limited bandwidth design. Optimum class F and inverse class F conditions are presented using active harmonic load-pull measurements, and it was found that a higher drain efficiency was achieved in the class F configuration. This result is due to the limitations imposed by the soft voltage breakdown occurring due to the extended voltage swings inherent to inverse class F, as a consequence generating unwanted current content during the off cycle. This significantly reduces the peak measured efficiency using Si LDMOS devices when implementing an inverse class F design with a drain bias of 28V. By reducing the drain bias to 18V, to accommodate the voltage extension of inverse class F, it became possible to achieve peak measured efficiencies much closer to what theory predicted.

II. Aamir Sheikh, Jonathan Lees, J. Benedikt, P. J. Tasker "Utilization of a Measurement Based CAD Tool for Enhanced PA Design Investigations", *Proceedings of the 38<sup>th</sup> European Microwave Conference*, pp. 1671-1674, Oct 2008.

Abstract - This paper outlines the use of a measurement based waveform CAD tool for enhanced PA design. Two measurement based models have been used to simulate a complete Doherty power amplifier together with output matching. The output matching network and auxiliary bias were optimised to produce a region of high efficiency typical of Doherty power amplifiers. Through the incorporation of a large signal de-embedding network, the current and ation of power amplifiers using well established waveform devoltage waveforms were accessed at the current generator plane. This allowed for the confirmation of Doherty operation on an individual device basis. This powerful tool allows for further optimissign procedures, previously not possible at high power levels.

III. **Aamir Sheikh**, Chris Roff, J. Benedikt, P. J. Tasker, B. Noori<sup>, 2</sup>, P. Aaen and J. Wood, "Systematic waveform engineering enabling high efficiency modes of operation in Si LDMOS at both L-band and S-band frequencies," *IEEE MTT-S Int. Microwave Symp. Digest*, pp. 1143-1146, June 2008.

**Abstract** - This paper demonstrates that by robust waveform engineering it is possible for high power Si LDMOS to achieve very high efficiency at frequencies up to 2.1GHz. Class F amplifier operation was realized in a

5W LDMOS device by the successful application of robust waveform engineering procedures; undertaken at the current generator plane. The peak power added efficiency was found to be 78% at 0.9GHz and 77% at 2.1GHz. In both cases the RF waveforms were optimized in terms of the gate voltage, fundamental and harmonic impedances. The main difference at 2.1GHz was the change in fundamental impedance to a more reactive impedance to compensate for the dynamic device output capacitance. To the authors' knowledge this is the highest efficiencies reported in the literature for Si LDMOS devices at 2.1GHz.

IV. A. Sheikh, P. J. Tasker, J. Lees, and J. Benedikt, "The impact of system impedance on the characterization of high power devices," *Proceedings of the 37<sup>th</sup> European Microwave Conference*, pp. 949-952, Oct 2007.

Abstract - This paper focuses on the extension of the successful application of current and voltage waveform engineering of on-wafer devices to power levels relevant to both handset and basestation markets. Effects on the measured waveforms caused by a  $50\Omega$  characteristic impedance of the measurement system are investigated showing a significant effect at the lower and crucially at higher harmonics, which is in contrast to the current school of thought. For the first time a waveform based analysis of packaging affects is presented, allowing the effects of the system's higher harmonic impedances to be studied and considered in the context of de-embedding measured waveforms. Measured de-embedded waveforms are compared with simulated equivalents model and are found to be in good agreement.

# 3 Glossary of Terms

### In order of appearance

RF Radio frequency

TDMA Time division multiple access

FDMA Frequency division multiple access

CDMA Code division multiple access

LTE Long term evolution

OFDM Orthogonal frequency division multiplexing

PA Power amplifier

CAD Computer aided design

VNA Vector network analyzer

DUT Device under test

POI Points of interest

CW Continuous wave

FET Field effect transistor

BJT Biplolar junction transistor

LDMOS Laterally diffused metal-oxide semiconductor

HEMT High electron mobility transistor

Si Silicon

GaN Gallium Nitride

MOSCAP Metal-oxide semiconductor capacitor

MAG Maximum available gain

MSG Maximum stable gain

EM Electro-magnetic

F<sub>T</sub> Frequency at unity small signal gain

NVNA Non linear vector network analyzer

EER Envelope elimination and restoration

ET Envelope tracking

R<sub>opt</sub> Optimum resistance for output power

T<sub>p</sub> Transition point

## 4 Introduction

Over the last ten years, the wireless communications industry has grown exponentially with ever increasing users and applications. At the centre of this growth has been the constant requirement for communication and trade within a global "24/7" environment. The consequence of this has been the need for instant access to voice and internet services at home, the office and on the move with an estimated 2.5 billion mobile users worldwide [1]. This has been enabled by the combination of improvements in hardware and software as well as the injection of large amounts of financial investment within the mobile infrastructure.

The hardware improvements in digital processing power, speed, memory capacity and device miniaturisation allows for the implementation of complex algorithms at speeds previously not possible in a case size no larger than the palm of an individual's hand. This has been supplemented with improvements in active radio frequency (RF) technology such as power transistors, with higher gain values and higher frequencies of operation. In parallel, software and algorithm improvements and an increased effectiveness in the application of these processes in hardware have allowed for the quick transfer of mathematical processes into a commercially viable solution. This has led to the introduction of enhanced communications systems that simultaneously boost the numbers of users and data rates. This initially started with GSM leading to its enhanced version GSM Edge, both of which are still highly prevalent within the developed and developing world. These were based on time division multiple access (TDMA) based techniques that allowed for a vast enhancement in user compared to it's predecessor, frequency domain multiple access (FDMA), but the vast increase in network users led to the implementation of code division multiple access (CDMA) based techniques.

The introduction of CDMA allowed for vast increases in users and data rates typically around the hundreds of kilobytes to a couple of megabytes per second,

and is currently being used in developed countries with an estimated 400 million mobile internet users worldwide [2]. Future systems such as long term evolution (LTE) and mobile Wi-Max now based on orthogonal frequency division modulation (OFDM) based techniques allow for even higher data rates in the hundreds of megabytes per second. With these increases in data rates, the wireless communications industry has brought in significant shifts in not only mobile but also fixed infrastructure.

This has reduced the need for extensive optical based fibre networks, previously touted as the best method of achieving high data rates to each home. The data rates offered by optical based communications systems still far supersede that offered by the wireless systems but the added costs and major planning requirements in the building of a complete fibre based infrastructure make it prohibitive to cover every household. This has led to a newer model for improved communications whereby a fibre based back bone network is supplemented by a local wireless network that will deliver data to the end user.

As the numbers of users and requirements have increased the design and implementation complexities have also increased. In addition to that, the wireless communications systems designer has also had to contend with outside factors, such as costing and energy consumption to ensure the product not only has mass appeal but is also seen to be working at the peak in efficiency. This is because of the great infrastructure power consumption levels which account for approximately 2-3 % of the total global carbon emissions [2] and due to the high demands of these networks, this is expected to double by 2020. This has also been supplemented by significant increases in electricity costs. One of the components found to be the most power consuming is the power amplifier [3].

The power amplifier (PA) is the last stage prior to the antenna that amplifies the output signal to output power levels typically in excess of 100W for mobile base stations. The added complexity of modulation signals with large peak to average power ratios (PAPR) and increasing signal bandwidth have to be optimised,

whilst working within the tight controls on spectrum space [4]. This spectral requirement takes precedent in the design process, resulting in the power amplifier being operated in a backed off 'linear' mode of operation. The average efficiency of these amplifiers in these modes of operation are usually in the region of 20-30 %, which leads to the requirement of approximately 400 W of DC power plus the additional power required for cooling the amplifier in the form of air or liquid based systems. This makes the power amplifier one of the most power consuming circuits within the entire communications system and with around 51,000 base stations currently in deployment around the UK [5] the potential savings both in carbon and electricity costs are immense.

As outlined earlier, the design of efficient power amplifiers is a pivotal topic and has attracted a large amount of interest in both academic and industrial research and development centres. The research in efficiency enhancement techniques can be split into two distinct brackets [6]. The first can be identified as peak power efficiency enhancement techniques, whereby the amplifier is operating as close as possible to the ideal figure of 100 % efficiency at peak output power. This is when all of the inserted DC energy is transferred to the output of the transistor at RF. The second group of efficiency enhancement techniques are described as efficiency enhancement with dynamic range in power, whereby the amplifier is operated at a higher level of efficiency over an extended range of power levels. There is also the possibility of an amalgamation of the two previously explained research threads but little work has been achieved in this regard. In all cases, the design of efficient power amplifiers has one consequence and that is an increased amount of non-linear distortion in both harmonic and "in band" intermediate frequency (IF) components. However, with the introduction of adaptive digital signal processing techniques it has been possible to produce linearization techniques that can adhere to the strict government controls on spectrum on PAs which were previously deemed unusable [7]. With these developments in mind, it provides encouragement to look further into high efficiency PA design.

In general, the theory behind PA design has always centred on the analysis of input and output current and voltage waveforms. For simplification purposes, the input stimulus is always assumed to contain content at just the fundamental. However, the output will invariably contain signals at the desired fundamental frequency and its higher harmonics, which will distort the output current and voltage waveforms. However, whilst it is not desirable to distort the PA for linearity purposes, in the case of efficiency it is the manipulation of higher harmonic current and voltage components that produce significant strides towards the desired target of 100 % operating efficiency. The first mode of high efficiency operation was first demonstrated by Snyder [8]. Snyder, mathematically demonstrated that by applying Fourier series analysis to the desired output current and voltage waveforms it was possible to achieve 100 % operating efficiency in a mode referred to as class F. This emphasis on the waveforms provided a unique and rational insight not previously discussed in the literature. Further work has been done on other high efficiency modes of operation such as inverse class F and class E [9]. In the case of class E, high efficiency operation was achieved through the design of a charge storage circuit that operated similar to a switch. However, the explanation of class E operation is best described using the output current and voltage waveforms. These two examples emphasize the unique insight that waveforms present into PA design in explaining high efficiency operation.

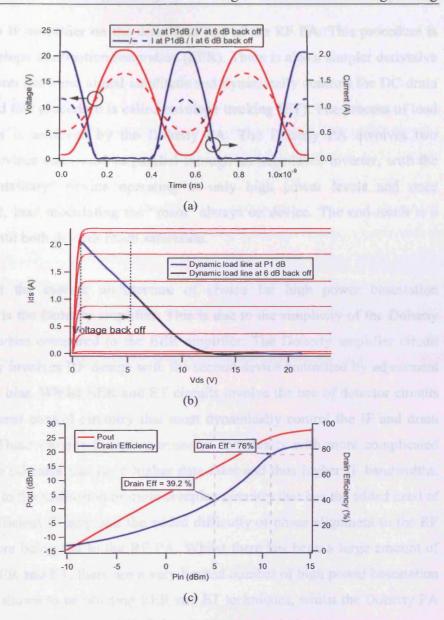

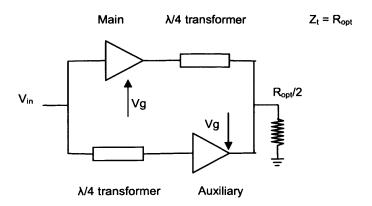

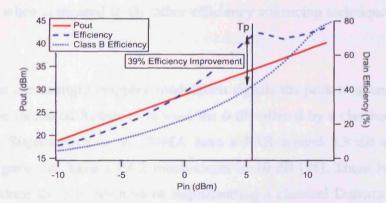

The second stream of efficiency enhancement is focussed on improving efficiency over a large range of output power. This form of efficiency enhancement has attracted more interest in the commercial communications domain due to the large peak to average ratios exhibited in 3G and 4G signals. One of the first proposed methods was demonstrated by Doherty [13] in the Doherty PA. The Doherty PA produced a region of high efficiency over the peak 6 dB of output power through the process of active load pull. This is done by controlling the ratio of the two currents being generated at the output node of each device, which consequently alters the load impedance being seen by either device. Other techniques have also been investigated such as the Chireix out

phasing amplifier as well as envelope elimination and restoration [2]. Again in both cases the use of waveform analysis provides a unique insight in the design and optimisation process.

In recent times, the PA designer has shifted away from analysing the output current and voltage waveforms. Part of the reason is due to the design process focussing more on providing high output power and linearity and with a smaller focus on efficiency. More recent effort has been put into high efficiency PA design, however, without the use of waveforms it becomes difficult to confirm whether the optimum mode of operation is achieved in the design. This is because an overdriven amplifier biased in class B can produce efficiencies in excess of 70 % together with high output power and gain [3]. Producing a design that is only 10% percent lower than the optimised designs typically reported in the literature [10-12]. Whilst this difference is not majorly significant in terms of efficiency, there could be other consequences such as reliability. By looking at the input and output waveforms it becomes possible to not only quantify the performance but also more precisely account for other factors that may be overlooked in the design process.

Another reason for the lack of use of waveforms, is due to the lack of access to non-linear components in both the measurement and computed aided design (CAD) domains. Historically, power meters and spectrum analysers have been used to collect RF data, which are scalar measurements. These are typically combined with the use of vector network analyzers (VNA), to allow for sparameter measurements. Whilst this data provides a good insight into device and PA behaviour there is not enough information present to extract waveforms. To achieve this nonlinear VNA functionality, the forward and reverse travelling wave data collected must be fully vectorial and referred to a common phase reference for correct alignment of the current and voltage waveforms. In addition to that the data must be collected over a large enough bandwidth spanning multiple harmonics. Such systems are only available in a handful of locations and the costs involved in procuring such equipment can be three to five times

higher than more traditional characterization facilities. This consequently affects the CAD simulations, where the device models are only fully validated against pseudo scalar/vector measurements, questioning the use of these models within a full vector based domain.

Having access to waveform data will allow the PA designer to investigate the device's performance in a more thorough and detailed manner. Through a process of current and voltage analysis and control at the input and output terminals it is possible to apply procedures such as class F. The application of these theoretical procedures in the field of PA design is called waveform engineering. Waveform engineering is a topic of high recent interest [14] and has provided the missing information about how high efficiencies are attainable device and frequency independent [11, 15].

Waveform engineering has typically been demonstrated on small devices usually in an on-wafer environment where package and device parasitics are kept to a minimum. This allows for the direct application of waveform based procedures such as [8] and has led to further developments as outlined in [16]. However, small devices have a limited application domain such as mobile handsets or other short range systems where the added complexity in design yields a small saving of power.

When these procedures are applied at higher power levels the savings in power become more tangible. However, the application of these procedures at high power, have yielded limited results [10] with high efficiencies so far achieved in medium power devices and at L-band frequencies. Part of the reason for this is due to the higher losses at high frequencies but the more significant reason is the lack of access to the appropriate current and voltage waveforms in the design process. For this to successfully occur, the waveform data has to be taken at the correct reference plane. The waveform data captured in time-domain based measurement systems [17] and in commercially available CAD based models are at a calibrated reference plane at the input and output tabs of the device. The

waveforms captured at this plane are altered by the device parasitics, which in this case consist of inductances and capacitances that add reactive content to the generated current and voltage waveforms. As the device size and frequency of operation increase, the size of the parasitic elements and their effect on the waveforms escalate rendering the waveforms of little or no use for waveform engineering. This is especially the case in high power devices, where direct probing the die is not possible and measurements have to be taken at the output of package. It is to be noted that the waveforms still contain all of the information required for design, such as the power and efficiency as well as impedances for matching network design. To cancel these effects, it is required to move to a reference plane within the device where waveform engineering can be more effectively applied. This and the validation of the de-embedded results, forms the first main body chapter of this thesis. There has been a lot of effort put into passive modelling of the package [18], however what has not been established is the complexity of package modelling required for accurate waveforms with regards to increasing size and operating frequency. Another factor for consideration is the extent of de-embedding necessary. Classical sparameter based modelling techniques [19] have found it necessary to separate out the passive and active components to fully describe the transistor's behaviour. However, waveform engineering has typically been applied on-wafer yielding positive results. This provides a first reference point for de-embedding the waveforms, but with larger devices the actual device parastics such as the output capacitance C<sub>ds</sub> scale linearly with size and could have a greater effect in high power devices. Two particular examples are cited, a 5 W device and a high power 110 W device.

To enable confidence in the use of waveforms at an internal reference plane, there is also a need for validating the results. For initial purposes, this is done by comparing the de-embedded current and voltage waveforms with theory. Whilst this provides a start point, this work has highlighted that high power devices can be affected by outside issues previously not considered necessary, such as the system impedance and how they generate higher harmonic content. Without

taking these factors into consideration, the valid de-embedded results can produce waveforms that initially look incorrect, which can cause an unnecessary repeat exercise in device and package network validation. One particular example discussed in Chapter 6, is the affect of the measurement system impedance environment, which stays constant at 50  $\Omega$  whilst the optimum impedances of the devices reduce to below 1  $\Omega$ . This is further investigated when the impedance transformation of the package network, transforms the 50  $\Omega$  system impedance to complex impedances at an internal plane of reference. These complex impedances can have substantial effects on the waveforms and the fundamental performance of the device.

Now with increased confidence in the resultant de-embedded waveforms, waveform engineering is demonstrated using Si LDMOS devices. Chapters 7 and 9 focus on providing evidence of the increased awareness and design knowledge waveform engineering provides to the PA designer. Chapter 7 is based on implementing high efficiency waveform engineering, in particular class F and inverse class F modes of operation. Chapter 9 focuses on the Doherty amplifier, looking at how the de-embedded waveforms can be utilised for firstly confirming Doherty modes of operation and for enhanced single device investigations that provide the designer all of the relevant information for matching network design. Both chapters showcase the enhanced insight waveform engineering provides the designer that can subsequently be used for design.

Chapter 8, validates a commercially available large signal model against measured time-domain data. To date large signal models have only been validated and evaluated using scalar measurements such as output power and operating efficiency. There has been little or no validation of models in the time domain especially at power levels more relevant for base-station applications. Large signal models consist of many layers, the intrinsic device, the extrinsic device parasitics and the package. This provides several reference points at which to validate the entire model.

Overall, the focus of this work is to forward the concept of waveform engineering to high power devices to provide a more thorough understanding of the PA mode of operation. This will provide the designer with more information and allow for more prompt optimisation of designs for efficiency and/or linearity in both the measurement and simulation domains.

### 5 Time Domain De-embedding

To date high power devices have typically been characterised using load-pull/source-pull based measurement systems that are used to locate points of interest (POI) such as the impedance for maximum output power, maximum efficiency and maximum gain [20]. These impedance points can be found by conducting continuous wave (CW) load pull measurements, with the addition of multi-tone load pull features, the linearity of a device can also be measured [17, 21]. This form of characterisation can be done over a large input power dynamic range offering the PA designer vital information as to how the device will function with load and source impedance and input drive. More importantly, this data gives ample information to the RF PA designer, to design full input and output matching networks that should enable "first run" success. More recently, load pull has been used for sensitivity analysis, to aid in calculating the minimum tolerance levels of matching networks in the production phase.

Whilst load pull information has led to many successful PA designs [22, 23], there is very little information being presented in terms of describing device behaviour. Using data collected from load pull, the behaviour of a device can at best be "inferred" by cross analysing the DC parameters with the RF measurements at the fundamental and higher harmonics. For example it can be assumed that the device is functioning in class A, if the gain is rolling off steadily with increasing drive, the harmonic content is very low and the efficiency is typically no higher than 30% at 1dB gain compression. However, if the device was originally biased at a lower quiescent current value and the efficiency performance is lower than expected, it will be difficult to explain why the device is operating as inefficiently as these numbers suggest unless there is access to the RF dynamic current and voltage waveforms.

Access to the dynamic current and voltage waveforms allows for the identification of many device features, such as RF knee walkout [24] typically found in Gallium Nitride (GaN) HEMTs (High Electron Mobility Transistors).

This is when the RF current and voltage characteristics no longer correspond with the boundaries defined by the static DCIV characteristics of the device. There are also many other interesting features, such as determining the effect of feedback at the input. However, to date these investigations have typically been conducted using on wafer devices that are more often than not very small in both size and output power.

Whilst this information is useful and in most cases scalable [18], there are some extra factors that need to be taken into account. The first is related to the thermal effects of larger devices and its affect on the performance of the device. The second is the affect of the packaging with regards to the splitting of the input RF signal at the input tab of the device and the combining of the amplified RF output signal at the output tab. The third is the supplementary affect of the increased packaging, which increases the undesired displacement currents and voltages introduced by the parasitics in the transistor. The result being significantly altered current and voltage waveforms at the output tab of the device, rendering them almost useless for immediate waveform analysis.

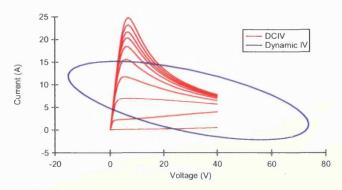

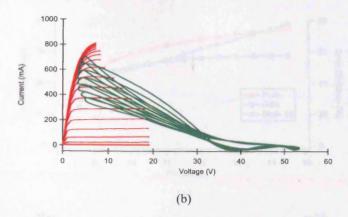

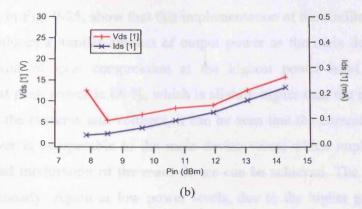

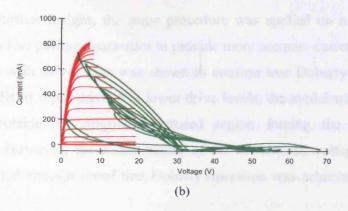

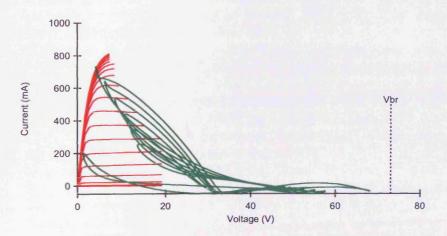

This is shown in Fig. 5-1, which consists of a measured dynamic drain current vs. drain voltage (load line) waveform of an 110W Si LDMOS device (taken at the output tab) clearly transgressing beyond the bounds of the DCIV [25] of the device. These measurements were done using the high power waveform measurement system developed at Cardiff University [17]. The dynamic IV is shown to go well beyond the knee voltage of the device showing inductance induced displacement voltage and the current is shown to dip below zero Amps, which shows the presence of capacitance induced displacement current. In addition to these lossless charge storing components the package could also contain losses such as resistive losses in the bonding wires, package tab and the transistor itself.

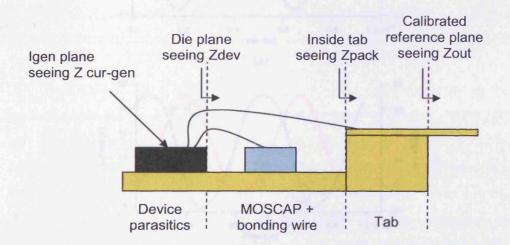

Fig. 5-1 Measured dynamic IV taken at the output tab, overlaid against the static DC IV obtained via simulation of the MET model

For design or analysis purposes the waveforms shown in Fig. 5-1 are of little or no use. This issue can be overcome with the introduction of large signal deembedding procedures that mathematically negate the effects of these parasitic components introduced by the package and the device imperfections. This allows for the visualisation of waveforms at a plane within the packaged device, such as the device plane or the current generator plane (I<sub>gen</sub>). The resultant waveforms can then be used to characterise and optimise device performance for efficient or linear modes of operation using procedures currently being applied on smaller devices.

Chapter 5 looks at how certain components typically found in packaged devices affect the current and voltage waveforms based on an ideal transistor and then moves onto de-embedding a 5W Si LDMOS device. After this, time-domain deembedding is applied to a high power 110W Si LDMOS device.

# 5.1 The Affect of Parasitic Components to Time-Domain Waveforms

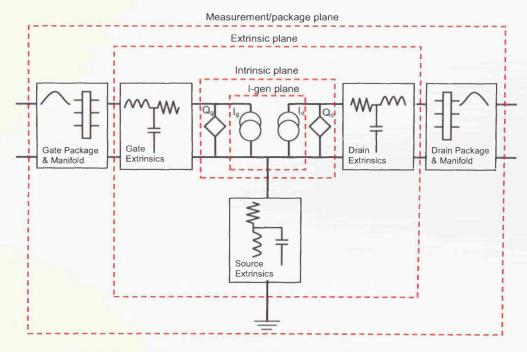

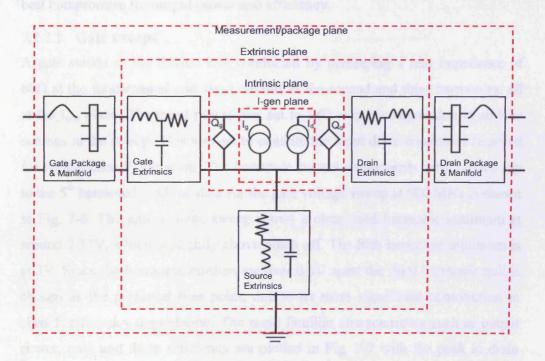

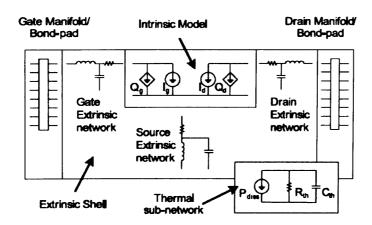

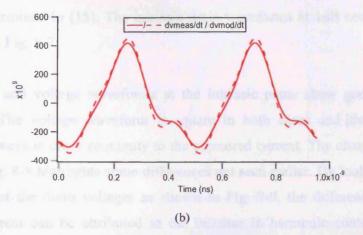

Packaged transistors can be broken into two main components, the package and the device or die. In terms of the device, there are many proposed networks used for modelling FET based devices [18, 19, 26-27]. These components are combined using a segmented approach that allows for complete characterization of the input, output and feedback components present in the transistor. This is shown in Fig. 5-2 which breaks down the individual components of the device. At the measurement/package plane the device contains all of the parasitic

components but by removing the package layer, it is possible to obtain access to the waveforms at the extrinsic device plane. This is similar to where low power on-wafer measurements take place. Similarly, by cancelling the effects of the extrinsic and intrinsic network, it is possible to obtain access to the current generator, which is where the currents and voltages can be directly compared to the boundaries defined by the device. With access to this plane it is possible to directly apply waveform based engineering procedures often shown in literature [3].

The extrinsic and intrinsic components are typically modelled as lumped components and made to fit s-parameter measurements. The transistor package can similarly be modelled using lumped components but a lot of recent work has focussed on modelling these components using 3D or planar electro-magnetic (E-M) based simulators [18, 28-29]. This section focuses on providing a description of the effects of these components in terms of the current and voltage waveforms.

Fig. 5-2 Block diagram of a FET and the various reference planes accessible for waveform engineering

# 5.1.1 Intrinsic and Extrinsic Lumped Component Passive Device Modelling

There has been a large amount of work presented in the literature, relating to the equivalent circuit models typically used in device modelling [18, 19, 26-27]. This section focuses on the lumped components typically found in devices, such as capacitors, inductors and resistors and looks at their effects at the input, output and in terms of feedback.

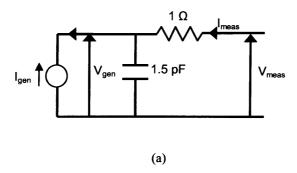

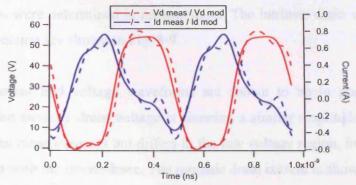

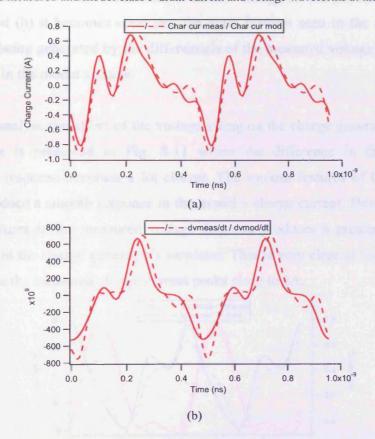

### 5.1.1.1 Capacitors

Capacitors are common parasitic components found within transistors that store charge and release it as displacement current. This is modelled as a function of the time derivative of the voltage flowing across its capacitance (charge) as shown in (5-1). This is added onto the generated current I<sub>gen</sub> from the transistor's current source to form I<sub>meas</sub>, which is the current at the measurement port as shown in (5-2). The capacitance typically found in solid-state devices is dependent on the semiconductor material and the physical size of the device [3]. Some semiconductor materials have shown to contain a variable capacitance that is dependent on the drain and gate voltages. This has been widely reported in Si LDMOS devices [28, 30] and is discussed later.

$$I_{disp} = C \frac{dv}{dt} \tag{5-1}$$

$$I_{meas} = I_{disp} + I_{gen} \tag{5-2}$$

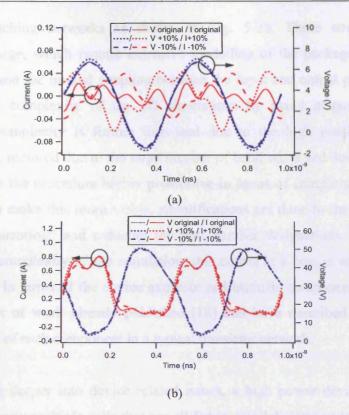

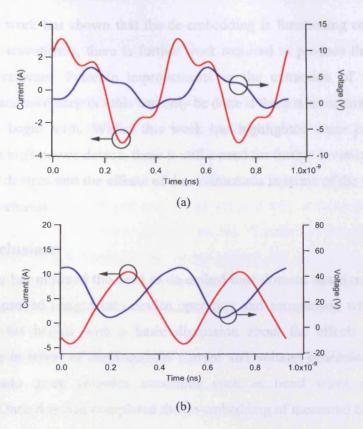

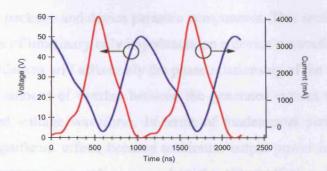

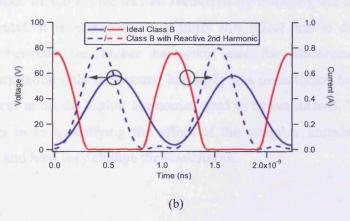

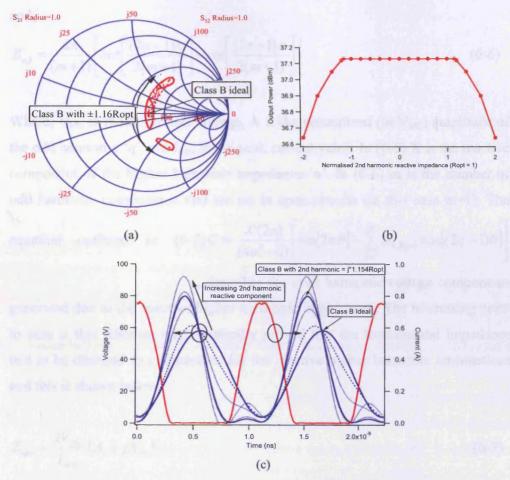

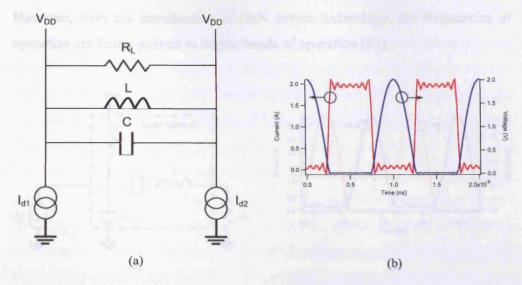

In terms of the waveforms, the measured current at the output of the device will now contain the extra displacement current generated by the capacitor. To demonstrate this more clearly a simulation is done with an ideal device (no parasitic components) operating in class B (all higher harmonics set to short circuit). This is shown in Fig. 5-3(b) where the measured current waveform of a device operating in ideal class B drops below 0mA and follows the displacement current curve generated by the capacitor when in the off-state part of the RF cycle. In other words, the capacitor is effectively "smoothing" the current waveform where the displacement current is the smoothing component. It is

interesting to note that if the capacitance is increased further it is possible to produce a measured current waveform that no longer resembles the initial generated current waveform. This could be the case for high power transistors where the intrinsic capacitance can be in the tens of pico-Farads. The inserted capacitor has no effect on the voltage waveform.

Fig. 5-3 (a) The circuit diagram denoting the currents at various parts of the circuit (b) The current and voltage waveforms before and after the capacitor

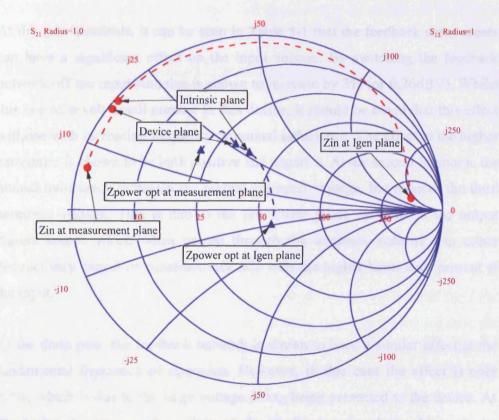

For optimum performance in terms of power at the  $I_{gen}$  plane, it is required to cancel the effects of the capacitor. If this is not done the output power of the device drops according to the phase offset at the  $I_{gen}$  plane given by the reactive component, which in this case is the capacitor [16]. To compensate for this, the impedance at the measurement plane is adjusted to negate the reactive effect of the capacitor as shown in Fig. 5-4. Since the capacitor is a parallel component, the impedance will vary along a contour of constant admittance. In this case an impedance of  $8.69 + 1.59j~\Omega$  is required to produce a real impedance of  $9~\Omega$  at the  $I_{gen}$  plane.

Fig. 5-4 The optimum impedance for power at the  $I_{gen}$  plane and at the measurement plane with a capacitor connected at the output of the current generator ( $Y_0 = 1/9$  S)

Now, considering a "non-linear" capacitor sensitive to the drain voltage. Nonlinear capacitors are typically used to model the intrinsic capacitors of semiconductor devices. The profile of the capacitor varies according to the device technology and the physical layout of the device. For analytical purposes, consider a capacitor modelled as a function of the reciprocal of the drain voltage (as shown in Fig. 5-5(a)). This dynamic capacitance behaviour is then simulated in the same environment described earlier with the results Fig. 5-5(b) showing a more significant deviation to the originally generated current waveform. The difference in the current waveform is highlighted more clearly in the displacement current generated when the RF current is high. This coincides with a low drain voltage, which causes an increase in the dynamic capacitance that generates a larger displacement current component. Despite the dynamic behaviour of the capacitor it is still possible to match to the "average" capacitance, which can be determined with respect to the voltage waveform being applied across it. For example in the case of a sinusoidal voltage waveform this results in a slight increase in capacitance.

Fig. 5-5 (a) The dynamic capacitance's sensitivity to voltage (b) The current waveforms at the I<sub>gen</sub> plane and at the measurement plane with a linear and non-linear capacitor.

Typically, device models consist of intrinsic charge generators (otherwise known as trans-capacitance) [18]. These charge generators behave in a capacitive manner but are functions of both the gate and drain voltages and are usually very complex. A specific implementation of a charge generator will be discussed later.

#### 5.1.1.2 Inductors

Similar to capacitors, all semiconductor devices contain some form of inductance due to device metallization. The inductance found in devices are series components, which store charge to release it as displacement voltage. This is modelled as a function of the inductance and the time differential of the current waveform (5-3), leaving the current component unperturbed. The displacement voltage ( $V_{gen}$ ) is then added onto the voltage presented at the  $I_{gen}$  plane to form  $V_{meas}$  as shown in (5-4). The inductance in semiconductor devices

is typically linear and usually accompanied with some resistive loss which will be discussed later.

$$V_{disp} = L \frac{di}{dt} \tag{5-3}$$

$$V_{meas} = V_{gen} + V_{disp} \tag{5-4}$$

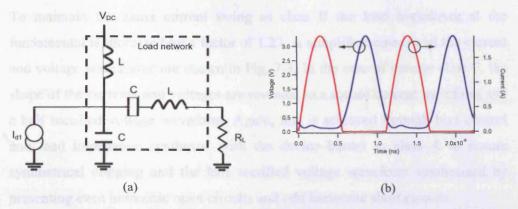

Fig. 5-6 (a) The circuit diagram denoting the voltages at various parts of the circuit (b) The current and voltage waveforms before and after the inductor

A simulation is done with an ideal device biased in class B and sinusoidal voltage being applied at the current source. The voltage waveforms in Fig. 5-6(b) highlight the affect of the displacement voltage on the output voltage waveform (Vmeas). The displacement voltage discharges when the RF current is turned on and has no affect when the RF current is off. It is important to note that the voltage waveform at the measurement plane (Vmeas) is sinusoidal in shape and not at the I<sub>gen</sub> plane (Vgen). This is because of the real only impedance (at f<sub>0</sub>, short circuit at higher harmonics) being presented at the measurement plane,

which forces the voltage to be sinusoidal. The inductance then alters the impedance being presented at the  $I_{\text{gen}}$  plane, which forces the voltage to become non-sinusoidal.

The reactive component introduced by the inductor can be negated by inserting a negative reactive impedance along a contour of constant resistance. In this case to produce a real impedance of 9  $\Omega$  at the I<sub>gen</sub> plane, it is required to present 9 – 2.7j  $\Omega$  at the measurement plane as shown in Fig. 5-7. In reality, the first instance of inductance occurs in the extrinsic circuit of the device model after the intrinsic capacitances. This makes the displacement voltage a function of the total current at the intrinsic plane.

Fig. 5-7 The optimum impedance for power at the  $I_{gen}$  plane and at the measurement plane with an inductor connected at the output of the current generator ( $Z_0 = 9 \Omega$ )

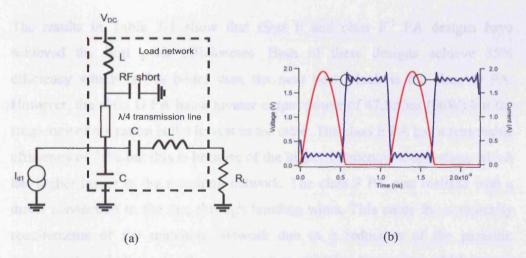

### 5.1.1.3 Resistors

Resistors are used to model the series loss of the line metallization and are placed in the extrinsic part of the device model. Since it is placed in series the resistor drops voltage as a function of current as determined by Ohm's law as shown in (5-7) and (5-8) as well as Fig. 5-8(b). This loss of voltage across the resistor reduces the output power and efficiency being measured. However, the resistance is typically small in high power devices due to the large number of cells connected in parallel. It is also important to note that the series resistor is

the only component that affects the DC content of the waveforms. Due to the DC source originating from an outside source, the actual DC voltage at the  $I_{\text{gen}}$  plane is the supply voltage  $V_{\text{DD}}$  subtracted against the DC voltage loss across the resistor.

$$V_{loss} = iR ag{5-6}$$

$$V_{meas} = V_{gen} + V_{loss} \tag{5-7}$$

To compensate for the resistance it is required to reduce the resistance along a contour of constant reactance. In this case, this is done by reducing the impedance at the measurement plane from 9  $\Omega$  to 7  $\Omega$ .

Fig. 5-8 (a) The circuit diagram denoting the voltages at various parts of the circuit (b) The current and voltage waveforms before and after the resistor

### 5.1.1.4 Feedback / Feed forward Components

The feedback / feed forward components in a device are lumped component based capacitors, inductors, mutual inductances and resistors. The types of

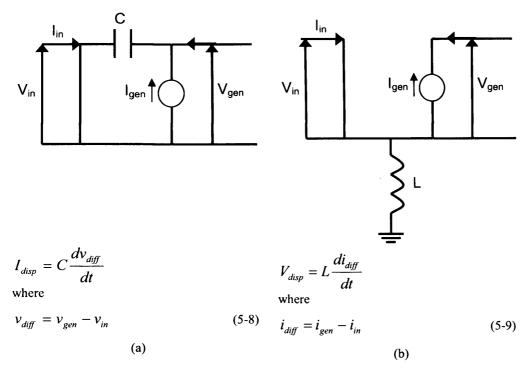

feedback are limited to what is typically reported in literature [18, 19, 26-27]. However, it is important to note that when used in a feedback orientation the voltage and current used in the calculation is now the difference between the two connecting ports. This is shown in Fig. 5-9.

The feedback components can have a significant effect at the input port. Due to the large current and voltage swings at the output port of the device, the expressions  $v_{diff}$  and  $i_{diff}$  can be significantly larger than the currents and voltages at the input port. In this case the effect of feedback can be separated into two components, the fundamental and the higher harmonics. At the fundamental frequency of operation the feedback often negates the input stimulus resulting in a drop of gain. At the higher harmonics, the feedback introduces unwanted higher harmonics in the input stimulus that could have a positive or negative effect on the device's performance.

### 5.1.2 Packaging Components Passive Device Modelling

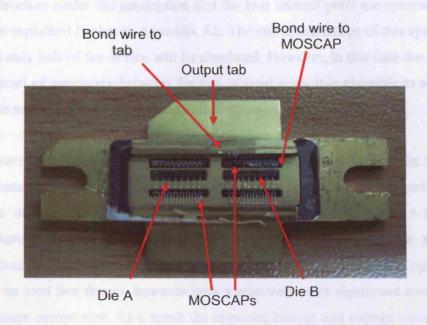

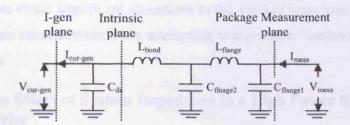

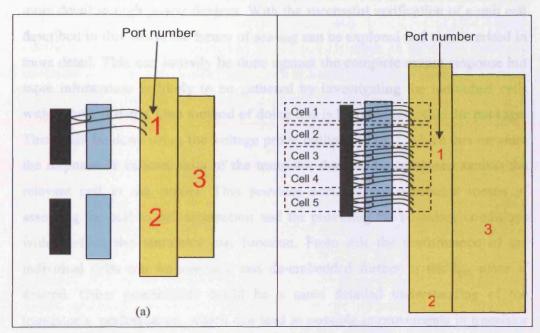

The package is a critical component of high power devices for thermal dissipation of heat and for electrical addition of the current from separate transistor cell blocks. The aim of the package is to have low loss to ensure maximum power transfer from the transistor die to the output tab, which is where measurements typically take place [18]. In medium power transistors, this includes the use of bonding wires, which bridges the transistor die and the output tab. In high power Si LDMOS devices, there is also the addition of metal-oxide-semiconductor (MOS) capacitors, which eases the requirements for matching network design [18, 23]. Recent work done by Wood et al [18, 26], has shown that there is also a need to incorporate the device manifold. Again, this is especially applicable to high power Si LDMOS devices, due to their large device periphery, which produces a large spread in phase of the load being presented to the individual transistor cells.

Fig. 5-9 (a) The circuit diagram denoting currents and voltages for a capacitive feedback circuit (b) The circuit diagram denoting currents and voltages for an inductive feedback circuit

### 5.1.2.1 Device Manifold

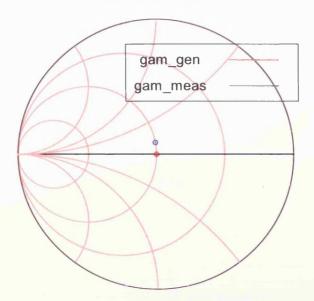

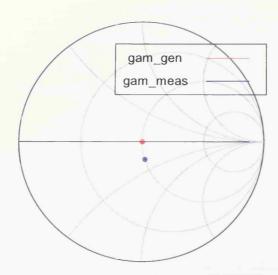

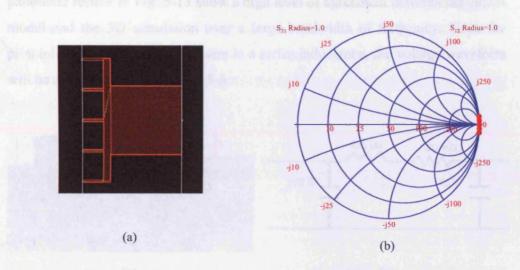

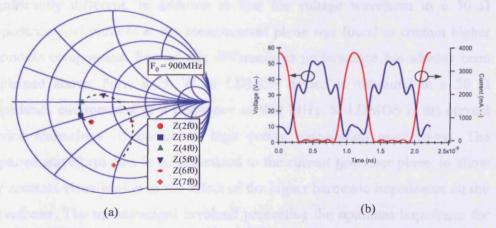

The device manifold connects the individual transistor cells and acts as a signal separator at the input and a signal combiner at the output and exists as part of the die. The device manifold is behaves like a transmission line with some small amounts of loss with increasing frequency. This in theory has very little effect on the waveforms other than a phase delay. In practice due to the large device periphery of high power transistors, the device manifold becomes very large and produces a spread in phase between individual cells in a transistor die [18]. This spread in phase at the output terminals makes it difficult to provide a constant impedance to each of the transistor dies, which makes it problematic in providing specific impedance terminations such as short and open circuits typically used in high efficiency PA design. To illustrate this, a simulation is done in Agilent ADS<sup>TM</sup> planar simulator Momentum<sup>TM</sup> of a device manifold for a 4.8mm Si LDMOS device supplied by Freescale Semiconductor Inc. The results in Fig. 5-10 show the phase variation that would happen if an open circuit was provided at the output port of the manifold at 6GHz. The impedances being

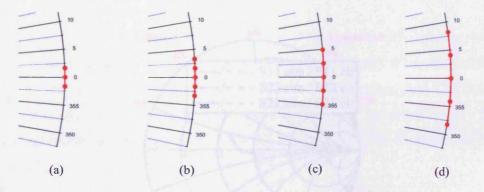

provided to the device is shown to vary by  $0.3 \pm 1500$ j  $\Omega$ . The zoomed in polar plots in Fig. 5-11, show the phase spreading with increasing frequency. The phase difference at 2GHz is 3°, which provides a "good enough" open circuit to the device, but at 10GHz the phase difference is approximately 16°. This consequently increases the difficulty in providing the fixed impedances typically required for high efficiency PA design [29].

Fig. 5-10 (a) Device manifold layout within ADS Momentum<sup>TM</sup> (b) The phase difference between ports at 6GHz with an open circuit presented at the output of the device manifold

Fig. 5-11 (a) Zoomed in polar plot of the phase difference at 2GHz (b) Zoomed in polar plot of the phase difference at 4GHz (c) Zoomed in polar plot of the phase difference at 6GHz (d)

Zoomed in polar plot of the phase difference at 10GHz

### 5.1.2.2 Bondwires

Bondwires are utilised to connect the device to the device output tab or to internal matching networks within the package. A bondwire is a metal wire with

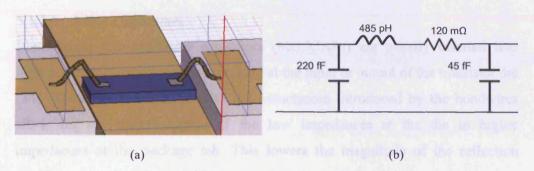

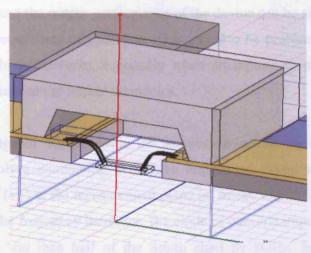

a small radius, usually made of gold for high conductivity or for cost cutting purposes made of aluminium. At high frequencies, the bondwire can be modelled as a series inductance with a small of amount of resistance and a capacitance to ground to model the contact with the tab or die [18]. This is shown in Fig. 5-12, where a 3D simulation of the input and output bondwires within an H-block fixture [18, 32] is conducted in Ansoft HFSS<sup>TM</sup>. The sparameter results in Fig. 5-13 show a high level of agreement between the circuit model and the 3D simulation over a large bandwidth of frequency. Since the principle component of a bondwire is a series inductance, the voltage waveform will be altered as shown in Fig. 5-6.

Fig. 5-12 (a) HFSS simulation of the input and output bondwires (b) Equivalent circuit of a single bondwire

Fig. 5-13 S-parameters of the 3-D EM simulation and the equivalent circuit model

In high power transistors, multiple bondwires are necessary due to the large amounts of current present at the drain terminal of the device. These bond wires then start to interact in the form of mutual inductance. This has been shown to slightly increase the overall inductance of the sub-network [18]. Mutual inductance is also present between the input and output bondwires which as a consequence increases the amount of feedback present within the device. With all of these complex interactions, the level of difficulty in modelling these structures using lumped models increases significantly. Instead, it is preferred to conduct 3D E-M simulations that allow for the drawing of arbitrary shapes [33] or to conduct s-parameter measurements of the structures within a controlled measurement environment [7].

### 5.1.2.3 MOS Capacitors

Metal-oxide semiconductor capacitors (MOSCAPs) are usually inserted into high power transistors for pre-matching at the input or output of the transistor die [34]. These in combination with the inductances introduced by the bondwires allow for the transformation of the low impedances at the die to higher impedances at the package tab. This lowers the magnitude of the reflection coefficient required for matching network design, which eases the design process especially for communications based applications where the bandwidth of operation is in the tens of megahertz.

The behaviour of a MOSCAP is defined in [33] which is effectively a lossy capacitance. In terms of the waveforms the MOSCAP will affect the current waveform when used in series. Some high power devices utilize the MOSCAP in parallel with the output tab. MOSCAPs are usually modelled using 3-D simulations due to the complexity of the substrates and the skin depth effects that occur at high frequencies.

### 5.1.2.4 Package Tab and Lid

The device package is a critical component in high power devices. The package consists of a metal tab that connects to the measurement or PA fixture and the bondwires and can be modelled as a wide microstrip line with low characteristic impedance [18]. The effect on the waveforms is similar to the device manifold, with a small phase perturbation and a spreading of phase to each of the

individual bondwires. In addition to that the package has a ceramic lid that encloses the device as shown in Fig. 5-14. This introduces some feedback between the input and output ports of the package. Newer high power devices are housed in plastic packages, which reduces the cost of the overall package but as a consequence the feedback is shown to increase [18].

Fig. 5-14 Cross section of a packaged device, shown within Ansoft HFSS<sup>TM</sup>

### 5.1.3 Circuit combinations and some possible side-effects

So far the discussion of parasitic components has been centred on one component at a time. However, in reality due to the sequential cascading of these components, the overall package network may feature unexpected properties that will not be obvious at first sight.

### 5.1.3.1 Low Pass Filtering

The first and most commonly found possible circuit combination is the low pass filter. This is often found in transistors and is the primary cause for the drop in maximum available gain (MAG) of transistors with frequency. This feature is usually attributed to the input series network  $r_g$ ,  $c_{gs}$ . At the output port, there is another low pass filter network which coupled with the input filter network defines the overall transistor gain drop with frequency. However, the output filter network has a second effect, which is more visible in large signal measurements. At higher frequencies, the drain low pass filtering network starts

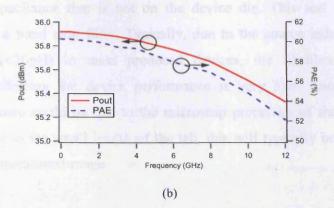

to dissipate power, which as a consequence lowers the fundamental output power and drain efficiency at the output measurement port. This is shown in Fig. 5-15(b), where a 0.5 dB loss in power and a 5% drop in efficiency occurs over the frequency sweep, using the network in Fig. 5-15(a). In this simulation the input stimulus has been held constant and the same impedance of 9  $\Omega$  ( $R_{opt}$ ) has been presented at the  $I_{gen}$  plane. This can have a major effect in broadband applications where the output performance of the device can be significantly less at the higher frequencies of operation. This can also be problematic for multi-harmonic matching networks, especially when attempting to provide specific circuit terminations at the higher harmonics.

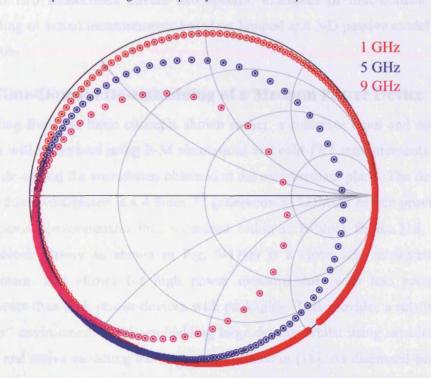

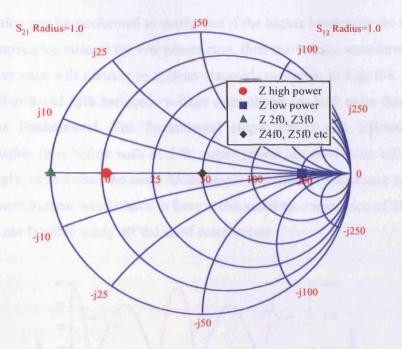

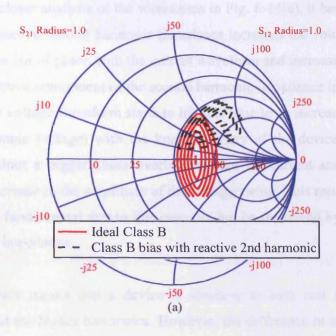

This is investigated further with the simulation results in Fig. 5-16, the simulation involves conducting a reactive impedance sweep with a constant magnitude of  $\Gamma$  (=1) at the measurement plane (at Imeas/Vmeas) as a function of frequency. As the frequency increases, the circle of possible impedances reduces significantly to less than half of the Smith chart by 9GHz. In this case, the network inhibits the ability to provide high impedances at the  $I_{gen}$  plane, at higher frequencies. This could have severe implications for certain high efficiency modes of operation such as class F where an open circuit is required at the third harmonic.

Fig. 5-15(a) The output network being simulated (b) The output power and efficiency performance against frequency with constant input stimulus

Fig. 5-16 Smith chart at the I<sub>gen</sub> plane outlining the reduction in impedance matching capabilities with increasing frequency

#### 5.1.3.2 Circuit Resonances

The two circuit resonances possible are either series or parallel LC networks. Series LC networks can occur between the output drain-source capacitance and the source inductance within the device or intentionally inserted in the form of internal matching networks [23]. Parallel LC networks can occur between the source inductance and the any external capacitance, for example in the form of a

bond pad capacitance that is not on the device die. This sort of resonance behaves like a band stop filter. Typically, due to the source inductance being very small (<20pH) in mass produced devices, the likelihood of circuit resonances effecting the device performance is very low. Another possible circuit resonance could be due to the microstrip properties of the device tabs. However, due to the small length of the tab, this will typically be well beyond the device's operational range.

This concludes the summary of device and package components. The work in the next two subsections covers two specific examples of time-domain deembedding of actual measurements based on lumped and 3-D passive modelling techniques.

## 5.2 Time-Domain De-embedding of a Medium Power Device

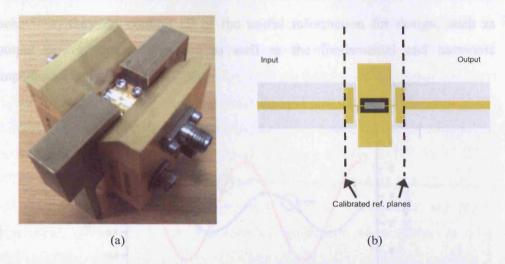

Expanding from the basic concepts shown earlier, a complete input and output network will be derived using E-M simulations and cold-FET measurements and used to de-embed the waveforms obtained at the measurement plane. The device used in this investigation is a 4.8mm 7<sup>th</sup> generation Si LDMOS device provided by Freescale Semiconductor Inc., measured within an H-block fixture [18, 32]. The H-block fixture as shown in Fig. 5-17(a) is a clean safe measurement environment, that allows for high power measurements with less parasitic components than high power devices with packaging. This provides a relatively "simpler" environment for de-embedding large devices whilst using established passive and active modeling techniques as outlined in [18]. As discussed earlier the de-embedding is separated into two stages, the package and the device. These are all constructed together using the segmented approach outlined in [18]. The waveform based measurements were taken at the plane outlined in Fig. 5-17(b), this was done using a multi-line TRL calibration [35] to allow for a wide frequency bandwidth of measurements covering multiple harmonics.

Fig. 5-17 (a) A picture of the H-block measurement fixture (b) The calibrated plane at which time-domain measurements were taken

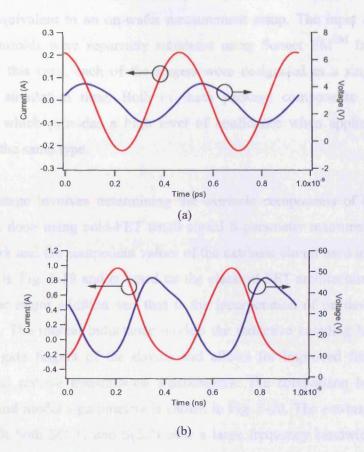

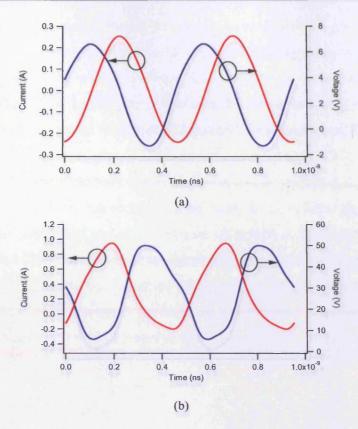

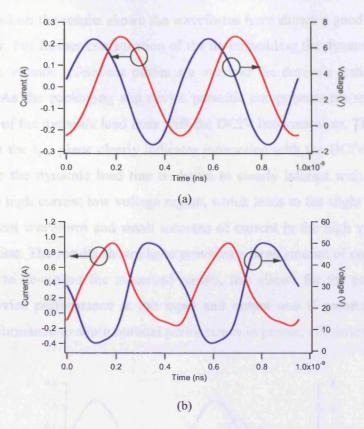

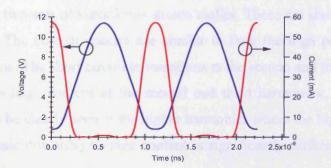

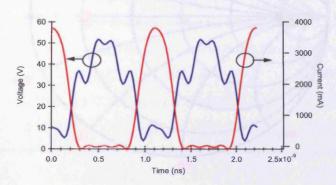

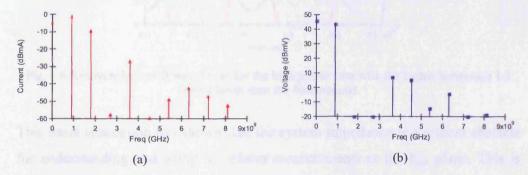

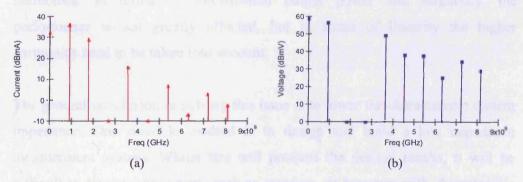

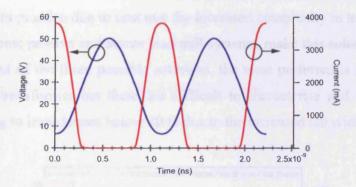

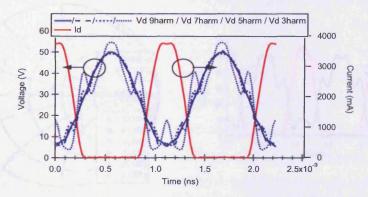

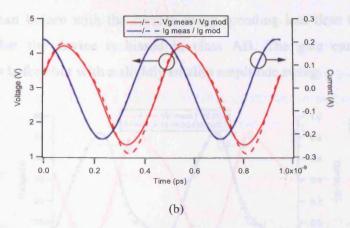

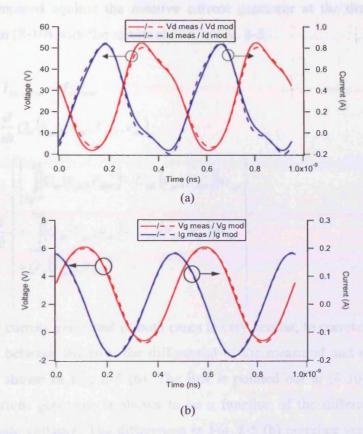

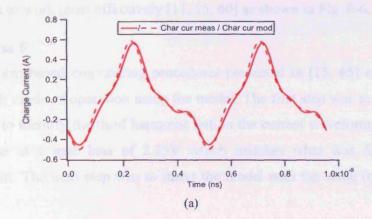

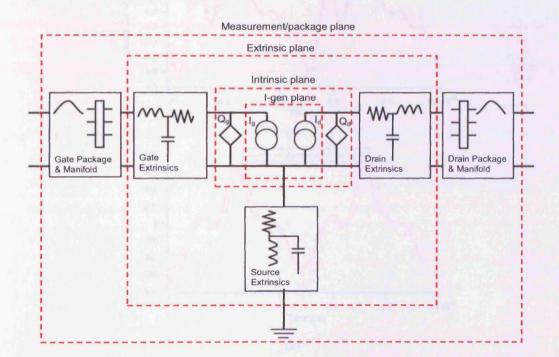

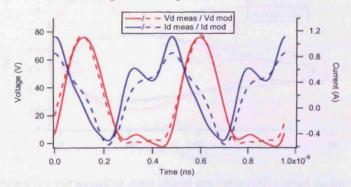

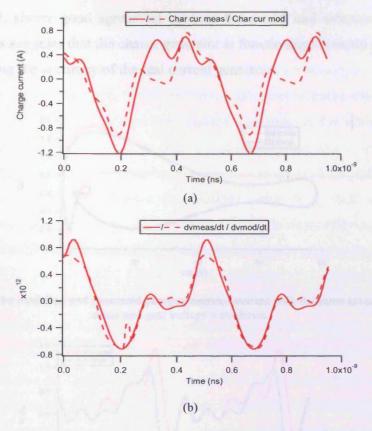

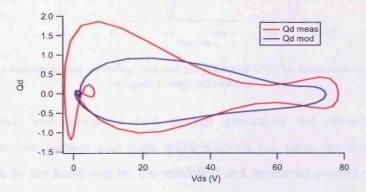

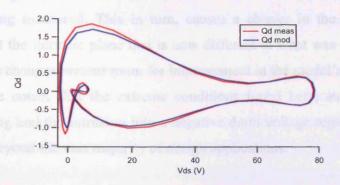

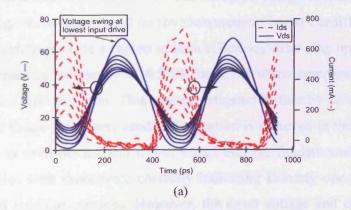

Before applying any de-embedding, it is worth looking at the currents and voltages being measured. This allows for a qualitative measure of the effects of the parasitic components on the waveforms compared to what would be expected in literature. This is done using measured time domain data collected with the high power measurement system developed at Cardiff University [17]. The measured current and voltage waveforms are taken at the impedance for peak output power at 1dB compression with the device biased at  $I_{dq} = 5$  mA/mm. The measured waveforms in Fig. 5-18, show a sinusoidal drain current waveform dropping below zero Amps and a drain voltage waveform centred around the drain bias voltage of 28V with a large fundamental component and some noticeable amounts of higher harmonic content. The sinusoidal current swing provides ample evidence of a sizeable amount of capacitance, which is significantly altered from the expected half-rectified voltage. Whilst the shape of the voltage swing is close to what is expected in theory, the amplitude of the swing is a lot smaller than what would have been predicted using load-line theory [3].

At the gate terminals both the current and voltage are sinusoidal in shape, which suggests the presence of little or no feedback. However, the voltage swing is shown to be smaller than would have been expected. However, it is still worth noting that whilst these waveforms are not showing the expected theoretical

behaviour, they do contain all of the useful information for design, such as output power, drain efficiency as well as the fundamental and harmonic impedances.

Fig. 5-18 (a) Measured current and voltage waveforms at the input terminals (b) Measured current and voltage waveforms at the output terminals

#### 5.2.1 Passive modeling of the device

The passive model of the entire device is begun by modeling the package. In this case the package network consists of an input and output bonding wire with a small wide-microstrip feed line as shown in Fig. 5-17. To model this accurately, the dimensions of the bondwire were measured under a precision microscope in the "x", "y" and "z" directions. This 3-D structure was then simulated using HFSS as shown in Fig. 5-12(a) over a wide frequency bandwidth (300MHz – 12GHz). The simulation was set to model the features of the individual bonding wires as well as the mutual inductance between the input and output bonding

wires [26] using internal ports in the simulator. Due to the difficulty in simulating these structures at lower frequencies, the BONDW tool in ADS<sup>TM</sup> was used to predict the DC performance of the bondwires. By removing these effects the measurements are effectively being conducted at the device plane, which is equivalent to an on-wafer measurement setup. The input and output device manifolds were separately simulated using Sonnet EM<sup>TM</sup> from DC to 12GHz. In this case, each of the fingers were designated as a single port to reduce to simulation time. Both of these package components are highly repeatable which provides a high level of confidence when applied to other devices of the same type.

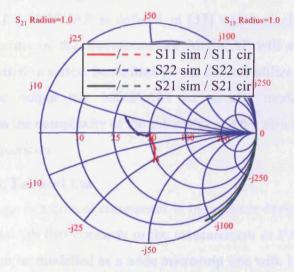

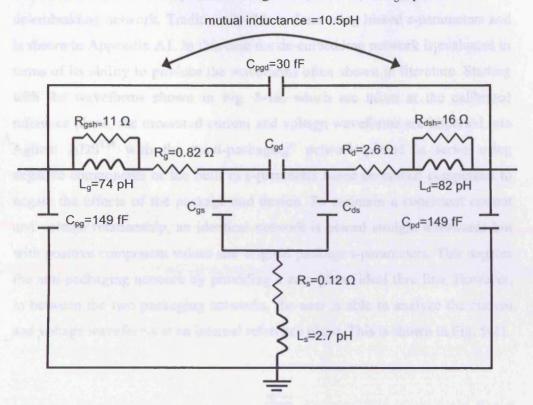

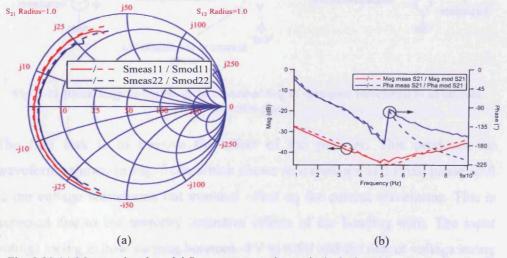

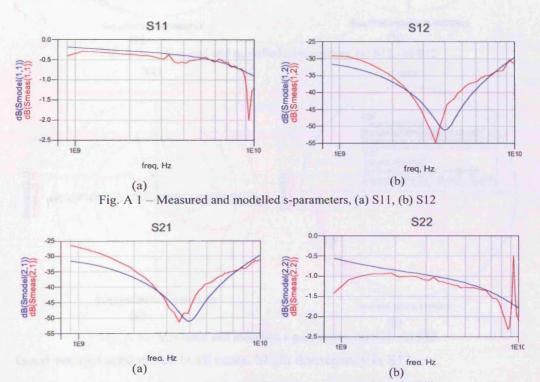

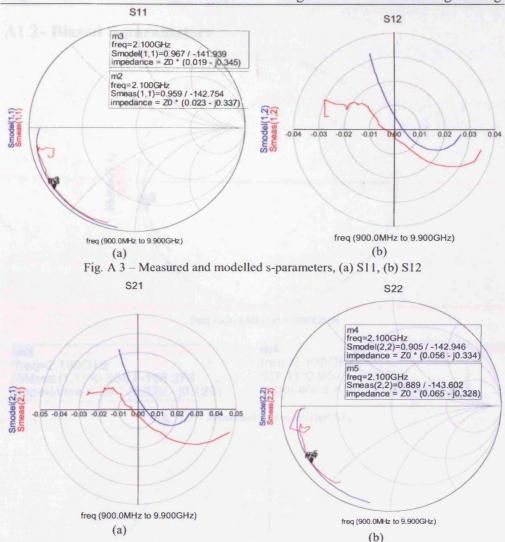

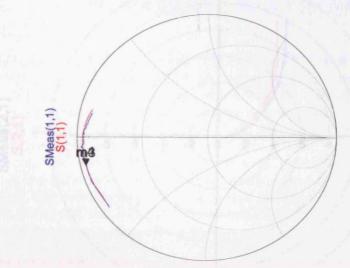

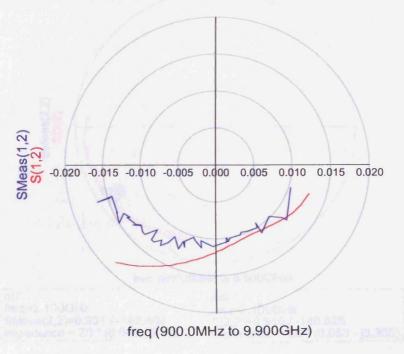

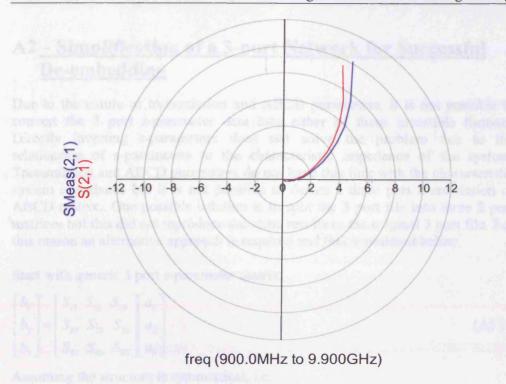

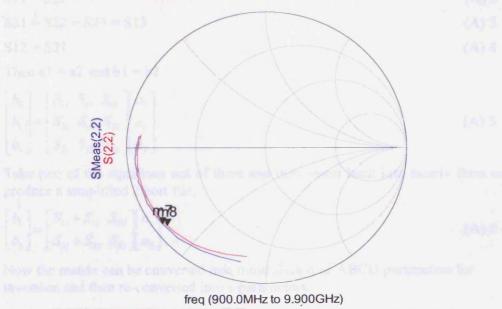

The next stage involves determining the extrinsic components of the device, which was done using cold-FET small signal S-parameter measurements [26]. The network and the component values of the extrinsic circuit used in the model are shown in Fig. 5-19 and is based on the classical FET architecture. However there is one major addition and that is the incorporation of on device mutual inductance. The mutual inductance models the inductive coupling between the drain and gate fingers of the device and allows for improved fitting of the forward and reverse transmission s-parameters. The comparison between the measured and model s-parameters is shown in Fig. 5-20. The extrinsic model is shown to fit both S(1,1) and S(2,2) over a large frequency bandwidth. In turn S(2,1) and S(1,2) are shown to agree with measured data from 2GHz up to 6GHz. After that there is shown to be an increasing difference between the measured and model S(1,2) and S(2,1) phase. After further optimizing the values it was found that these component values represented the best overall fit in Sparameters considering the fundamental frequency of operation of 2.1GHz. Whilst it is important to note this difference in phase, the actual effect of this inaccuracy is not expected to be large due to a low f<sub>T</sub> of 7.5GHz [15].

The drain and gate charges were then determined by conducting Root model based measurements [36] and fitting the charges to the measured data as outlined in [37]. This form of charge extraction incorporates the effects of both the input

and output voltages in a fully charge conservative manner. This part of the deembedding procedure was completed by Freescale Semiconductor Inc and now allows for access to the current and voltage waveforms at the  $I_{\text{gen}}$  plane.

Fig. 5-19 Cold FET circuit diagram that is used to model the extrinsic components of the device [26]

Fig. 5-20 (a) Measured and model S-parameters at the extrinsic device plane shown on a Smith chart (b) Forward and reverse transmission measured and model S-parameters at the extrinsic device plane

#### 5.2.2 Obtaining waveforms at the I-gen plane

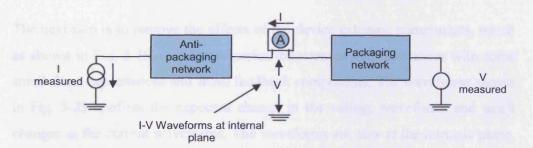

Now that a suitable network has been developed for the package and the device extrinsic and intrinsic components, the next step in the process is to validate the de-embedding network. Traditionally this is done using biased s-parameters and is shown in Appendix A1. In this case the de-embedding network is evaluated in terms of its ability to produce the waveforms often shown in literature. Starting with the waveforms shown in Fig. 5-18, which are taken at the calibrated reference plane, the measured current and voltage waveforms are imported into Agilent ADS<sup>TM</sup> with the "anti-packaging" network placed in series using negative components or the built in s-parameter based de-embed component to negate the effects of the package and device. To maintain a consistent current and voltage relationship, an identical network is placed straight afterwards but with positive component values and original package s-parameters. This negates the anti-packaging network by providing a zero phase ideal thru line. However, in between the two packaging networks, the user is able to analyze the current and voltage waveforms at an internal reference plane. This is shown in Fig. 5-21.

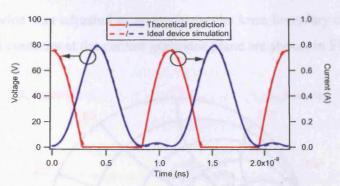

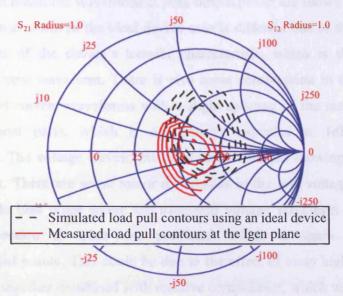

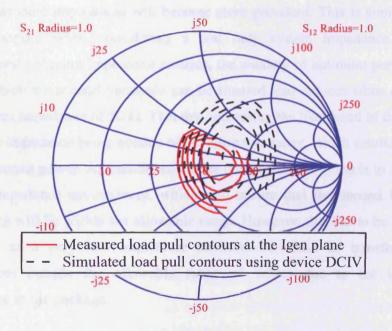

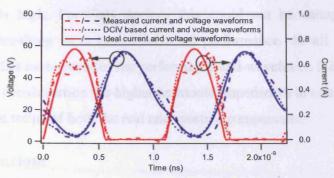

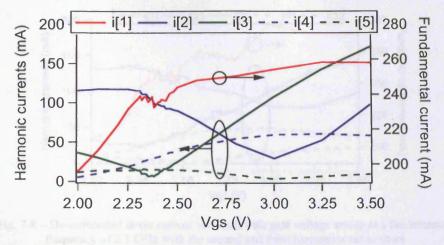

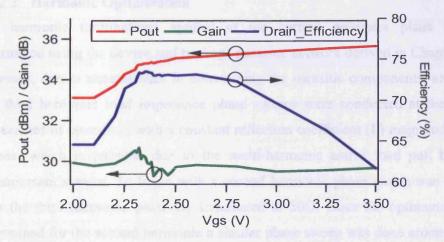

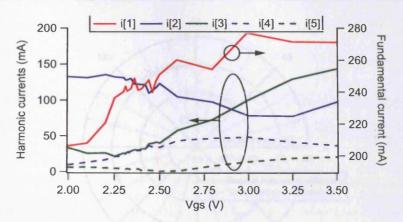

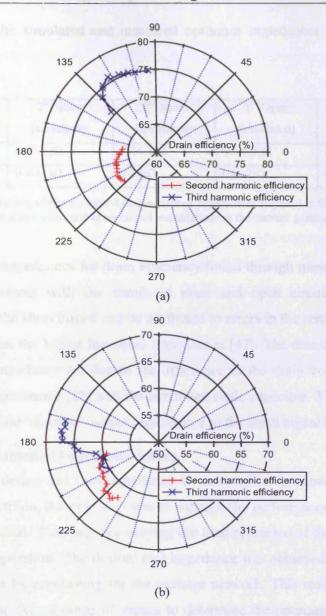

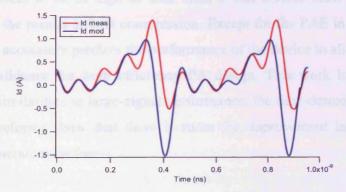

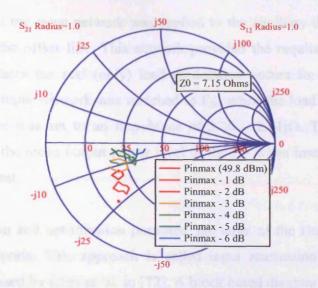

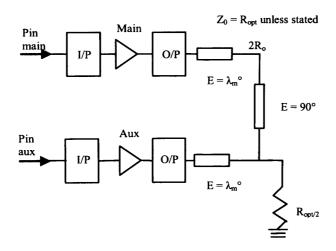

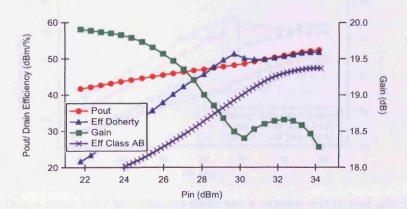

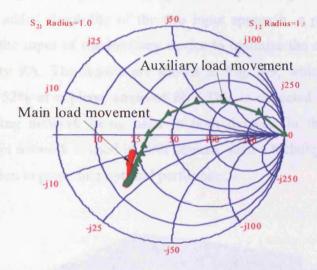

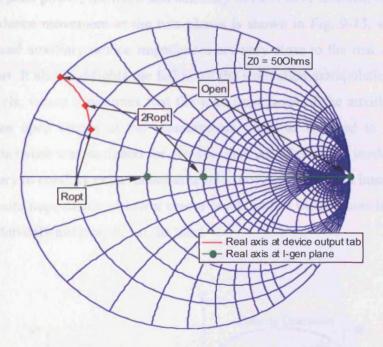

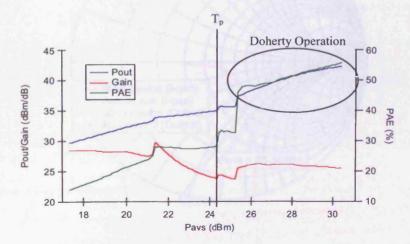

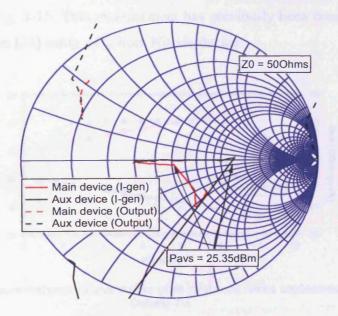

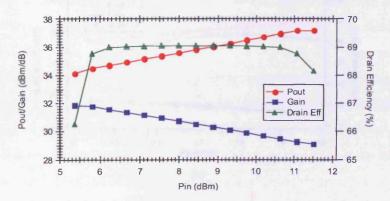

Fig. 5-21 Block diagram outlining the de-embedding of measured waveforms to an internal reference plane