# **Application Acceleration:**

An Investigation of Automatic Porting Methods for Application Accelerators

A thesis submitted in partial fulfilment of the requirement for the degree of Doctor of Philosophy

Thomas Henry Outram Beach

Cardiff University

School of Computer Science &

Informatics

September 2010

UMI Number: U585458

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U585458

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# **Abstract**

Future HPC systems will contain both large collections of multi-core processors and specialist many-core co-processors. These specialised many-core co-processors are typically classified as Application Accelerators. More specifically, Application Accelerations are devices such as GPUs, CELL Processors, FPGAs and custom application specific integrated circuit devices(ASICs). These devices present new challenges to overcome, including their programming difficulties, their diversity and lack of commonality of programming approach between them and the issue of selecting the most appropriate device for an application.

This thesis attempts to tackle these problems by examining the suitability of automatic porting methods.

In the course of this research, relevant software, both academic and commercial, has been analysed to determine how it attempts to solve the problems relating to the use of application acceleration devices. A new approach is then constructed, this approach is an Automatic Self-Modifying Application Porting system that is able to not only port code to an acceleration device, but, using performance data, predict the appropriate device for the code being ported. Additionally, this system is also able to use the performance data that are gathered by the system to modify its own decision making model and improve its future predictions.

Once the system has been developed, a series of applications are trialled and their performance, both in terms of execution time and the accuracy of the systems predictions, are analysed.

This analysis has shown that, although the system is not able to flawlessly predict the correct device for an unseen application, it is able to achieve an accuracy of over 80% and, just as importantly, the code it produces is within  $\approx 15\%$  of that produced by an experienced human programmer. This analysis has also shown that while automatically ported code performs favourably in

nearly all cases when compared to a single-core CPU, automatically ported code only out performs a quad-core CPU in three out of seven application case studies. From these results, it is also shown that the system is able to utilise this performance data and build a decision model allowing the users to determine if an automatically ported version of their application will provide performance improvement compared to both CPU types considered.

The availability of such a system may prove valuable in allowing a diverse range of users to utilise the performance supplied by many-core devices within next generation HPC systems.

# To my Dad,

Who constantly helped me, encouraged me and even proof read early chapters of this thesis, but did not live long enough to see it completed.

# Acknowledgements

Firstly, I would like to thank my supervisor; Professor Nick Avis for his help, encouragement, and advice over the course of this project. Secondly I would like to thank Dr Ian Grimstead for all his advice, proof reading, and putting up with my frequent badgering and discussion of ideas (Especially regarding ClearSpeed!)

I would also like to thank other members of the Cardiff Computer Science PGR community, especially those who have been involved in organising the various "FTS" student social events and seminars which have been a welcome break and a pleasant distraction.

Finally, I would like to thank my family and personal friends. My Mum and Dad for supporting me and my elder brother Daniel for providing several valuable pieces of inspiration.

Funded by

# List of Publications

- Abstraction of Programming Models Across Multi-Core and GPGPU

Architectures [17]

- Euro GPU Mini Symposium as part of the International Conference on Parallel Computing(PARCO) 2009

- 2. An Intelligent Semi-Automatic Application Porting System for Application Accelerators [18]

UnConventional High Performance Computing Workshop as part of Conference on Computing Frontiers 2009

**3.** Poster: An Intelligent Semi-Automatic Application Porting System for Reconfigurable Devices - [16]

Many-core and Reconfigurable Supercomputing Conference (MRSC) 2008

# **Table of Contents**

| 1 | Intr | roduction                                              | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Introduction                                           | 1  |

|   | 1.2  | Hypothesis                                             | 5  |

|   | 1.3  | Scope                                                  | 5  |

|   | 1.4  | Contributions                                          | 6  |

|   | 1.5  | Thesis Summary                                         | 7  |

| 2 | Bac  | kground                                                | 10 |

|   | 2.1  | Introduction                                           | 10 |

|   | 2.2  | Graphics Processing Units                              | 11 |

|   |      | 2.2.1 Device Architecture                              | 11 |

|   |      | 2.2.2 General Purpose Computation on Graphics Hardware | 14 |

|   |      | 2.2.3 The future of GPGPU                              | 23 |

|   | 2.3  | ClearSpeed Acceleration Architecture                   | 26 |

|   |      | 2.3.1 Device Architecture                              | 27 |

|   |      | 2.3.2 Programming Tools                                | 28 |

|   | 2.4  | Field Programmable Gate Arrays                         | 31 |

|   | 2.5  | IBM Cell Broadband Engine                              | 37 |

|   | 2.6  | Computational Libraries                                | 39 |

|   | 2.7  | Existing Application Acceleration Porting Methods      | 42 |

|   |      | 2.7.1 Portland Group Accelerator Compiler              | 46 |

| $T\Delta$ | RI | Æ | OF | CON | ITEN | 2T |

|-----------|----|---|----|-----|------|----|

|           |    |   |    |     |      |    |

|   | ٠ | • |   |

|---|---|---|---|

| v | 1 | 1 | 1 |

|   |     | 2.7.2  | Sieve Multicore Programming System           | 48  |

|---|-----|--------|----------------------------------------------|-----|

|   |     | 2.7.3  | HMPP                                         | 49  |

|   |     | 2.7.4  | Rapidmind and Ct: C for Throughput Computing | 51  |

|   |     | 2.7.5  | Peakstream                                   | 53  |

|   |     | 2.7.6  | Evaluation of Existing Methodologies         | 53  |

|   | 2.8 | Chapt  | er Summary                                   | 56  |

| 3 | Ove | rview  | of the Application Porting System            | 58  |

|   | 3.1 | Introd | luction                                      | 58  |

|   | 3.2 | Overa  | ll System Architecture                       | 60  |

|   | 3.3 | Overv  | iew of System Client                         | 64  |

|   | 3.4 | Source | e Parsing and Validation                     | 65  |

|   | 3.5 | Kerne  | l Extraction                                 | 67  |

|   | 3.6 | Kerne  | l Analysis                                   | 72  |

|   | 3.7 | Valida | ation of Input Kernels                       | 73  |

|   | 3.8 | Applio | cation Packaging                             | 77  |

|   | 3.9 | Chapt  | er Summary                                   | 77  |

| 4 | Cod | le Gen | eration                                      | 80  |

|   | 4.1 | Introd | luction                                      | 80  |

|   | 4.2 | Kerne  | l Selection                                  | 81  |

|   | 4.3 | Portin | ng to CUDA for the GPU                       | 82  |

|   |     | 4.3.1  | Generation of Host Code                      | 83  |

|   |     | 4.3.2  | Generation of Kernel Code                    | 90  |

|   |     | 4.3.3  | Calculating the execution configuration      | 93  |

|   | 4.4 | Portin | ng to $C_N$                                  | 99  |

|   |     | 4.4.1  | Generation of Host Code                      | 100 |

|   |     | 4.4.2  | Generation of Device Kernel Template         | 109 |

|   |     | 4.4.3  | Non-Buffered Kernels                         | 110 |

| $\mathbf{T}_{A}$ | Δ | R | T | F. | OF | 7 ( | $\mathbf{C}$ | 1   | ${f JT}$ | $\mathbf{E}$ | V   | $\mathbf{T}$ | S |

|------------------|---|---|---|----|----|-----|--------------|-----|----------|--------------|-----|--------------|---|

|                  | _ | _ |   |    | ~1 |     | -            | , , | •        |              | . 1 |              | _ |

| • |   |

|---|---|

|   | X |

|   |     | 1.4.4 Buffered Kernels                                 | 5 |

|---|-----|--------------------------------------------------------|---|

|   |     | 1.4.5 Determining Buffer sizes                         | 9 |

|   | 4.5 | Creating Build Scripts                                 | 1 |

|   | 4.6 | Code Generation Example - GEMM                         | 2 |

|   | 4.7 | Chapter Summary                                        | 4 |

| 5 | Dev | ce Selection, Self-modification and Expandability 12'  | 7 |

|   | 5.1 | Introduction                                           | 7 |

|   | 5.2 | Architecture of the Applicat on Classifier             | 8 |

|   | 5.3 | Gathering Metrics                                      | 1 |

|   | 5.4 | Matching Applications to Devices                       | 2 |

|   |     | 5.4.1 Making Decisions                                 | 4 |

|   | 5.5 | Validating Decisions                                   | 7 |

|   | 5.6 | System Evolution                                       | 8 |

|   |     | 5.6.1 Gathering Performance Data                       | 1 |

|   |     | 5.6.2 Integration of New Devices                       | 3 |

|   | 5.7 | Chapter Summary                                        | 4 |

| 6 | App | ication Case Studies 14'                               | 7 |

|   | 6.1 | Introduction                                           | 7 |

|   | 6.2 | Seed Applications                                      | 3 |

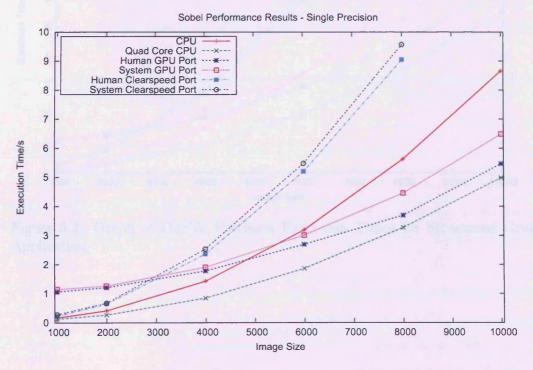

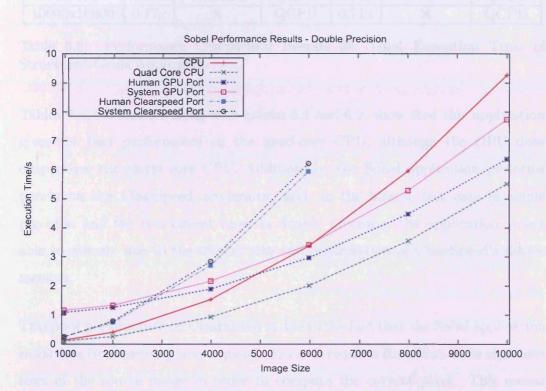

|   |     | 5.2.1 Structured Grids - Sobel Edge Detector           | 4 |

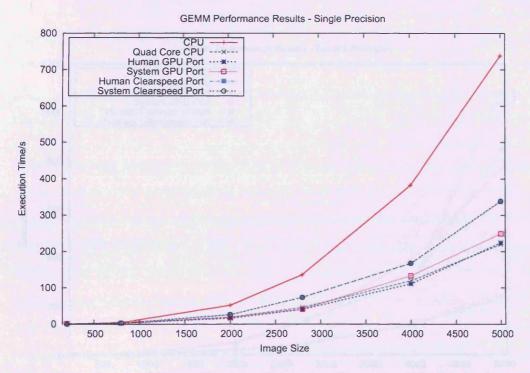

|   |     | 5.2.2 Dense Linear Algebra - Matrix Multiplication 159 | 9 |

|   |     | 5.2.3 N Body Methods                                   | 5 |

|   |     | 5.2.4 Monte Carlo Methods                              | 1 |

|   | 6.3 | Test Applications                                      | 7 |

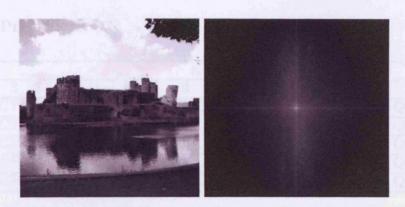

|   |     | 6.3.1 Fast Fourier Transform                           | 7 |

|   |     | 6.3.2 Canny Edge Detector                              | 8 |

|   |     | 6.3.3 Iterative Ray Tracer                             | 8 |

| $T\Delta$ | RI | .E. ( | $\mathbf{OF}$ | $\mathbf{CON}$ | TEN | TS |

|-----------|----|-------|---------------|----------------|-----|----|

|           |    |       |               |                |     |    |

| v |

|---|

| л |

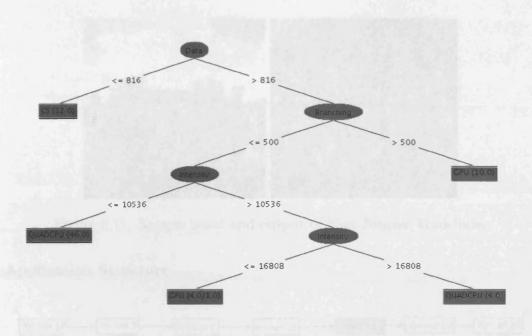

|   | 6.4      | Classification of Known Applications    |

|---|----------|-----------------------------------------|

|   | 6.5      | Chapter Summary                         |

| _ | <b>~</b> | 1 '                                     |

| 7 | Con      | clusions 215                            |

|   | 7.1      | Introduction                            |

|   | 7.2      | Research Hypothesis                     |

|   | 7.3      | Contributions                           |

|   | 7.4      | Relation to Current Work                |

|   |          | 7.4.1 HMPP                              |

|   |          | 7.4.2 PGI Accelerator Compiler          |

|   |          | 7.4.3 Conclusions                       |

|   | 7.5      | Evaluation of Metrics                   |

|   | 7.6      | ClearSpeed vs NVIDIA GPU                |

|   | 7.7      | Evaluation                              |

|   | 7.8      | Chapter Summary                         |

| 8 | Furt     | ther Work 232                           |

| O | 8.1      |                                         |

|   |          | Introduction                            |

|   | 8.2      | Making decisions based on other factors |

|   | 8.3      | Code Optimisations                      |

|   |          | 8.3.1 ClearSpeed:                       |

|   |          | 8.3.2 CUDA                              |

|   | 8.4      | Supporting larger data-sets             |

|   | 8.5      | Supporting Multi-Cards Accelerators     |

|   | 8.6      | Scheduling                              |

|   | 8.7      | Mapping code to computation libraries   |

|   | 8.8      | Cloud computing                         |

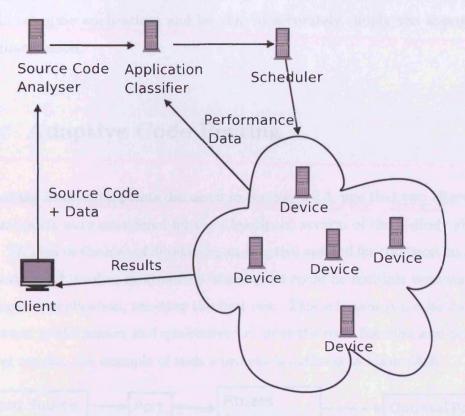

|   | 8.9      | Adaptive Code Porting                   |

|   | 8.10     | Chapter Summary                         |

| 17                        | ABLI | E OF CONTENTS                                    | X1  |

|---------------------------|------|--------------------------------------------------|-----|

| $\mathbf{A}_{\mathrm{I}}$ | ppen | dices                                            | 258 |

| A                         | Por  | ting Example: GEMM                               | 258 |

|                           | A.1  | Input Source                                     | 258 |

|                           | A.2  | Code Executing on CPU                            | 261 |

|                           | A.3  | CUDA                                             | 263 |

|                           |      | A.3.1 Generated Host Code                        | 263 |

|                           |      | A.3.2 Generated Device Code                      | 264 |

|                           | A.4  | $C_N$                                            | 265 |

|                           |      | A.4.1 Generated Host Code                        | 265 |

|                           |      | A.4.2 Generated Device Code: Non Buffered Kernel | 270 |

|                           |      | A.4.3 Generated Device Code: Buffered Kernel     | 272 |

278

B Kernel Description Metrics for FFT Application

# List of Figures

| 1.1  | Examples of Acceleration Devices: a) CELL B.E [4] b) FPGA from      |    |

|------|---------------------------------------------------------------------|----|

|      | Nallatech [7] c) NVIDIA Tesla [101] d) ClearSpeed [1]               | 2  |

| 1.2  | Application Accelerators as Co-processors                           | 3  |

| 2.1  | The GPU Rendering Pipeline                                          | 12 |

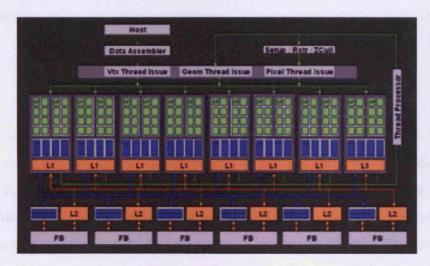

| 2.2  | The NVIDIA GeForce 8800 Architecture. Adopted from $[45]$           | 13 |

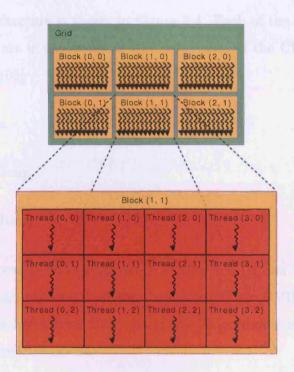

| 2.3  | NVIDIA CUDA Architecture. Adopted from [46]                         | 20 |

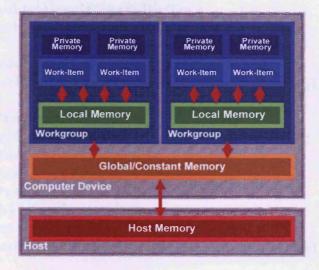

| 2.4  | The OpenCL Architecture. Adopted from [60]                          | 21 |

| 2.5  | The Larrabee Architecture, showing 8 CPU like cores, adopted        |    |

|      | from [122]                                                          | 25 |

| 2.6  | The ClearSpeed CSX Architecture. Adopted from [36]                  | 28 |

| 2.7  | A FPGA Internal Structure adopted from [25]                         | 31 |

| 2.8  | Typical FPGA design flow adopted from [25]                          | 33 |

| 2.9  | The CELL/B.E. Architecture adopted from [119]                       | 37 |

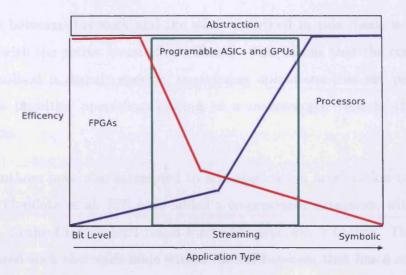

| 2.10 | An Ideal Abstraction for Application Accelerators adopted from [29] | 44 |

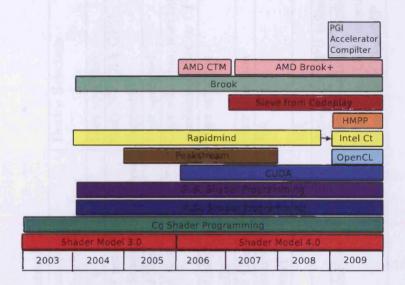

| 2.11 | A time line of software released to facilitate development on       |    |

|      | Application Accelerators                                            | 54 |

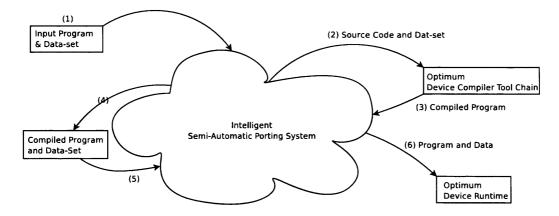

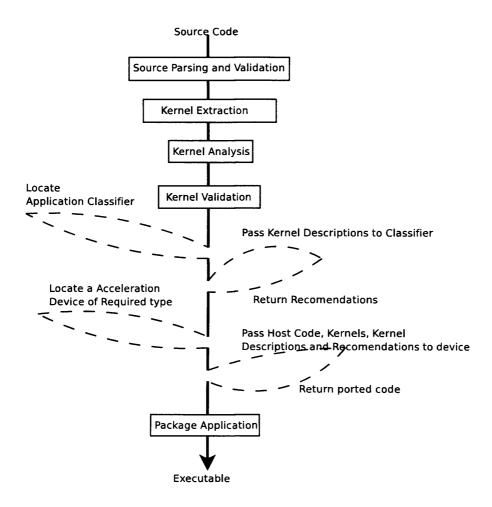

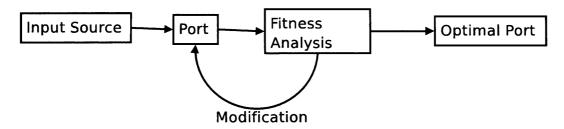

| 3.1  | High level design of the Porting system                             | 59 |

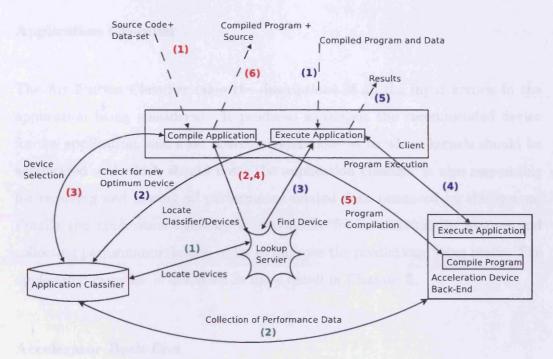

| 3.2  | The Application Porting system                                      | 62 |

| 3.3  | Client in the Compiler Mode                                         | 66 |

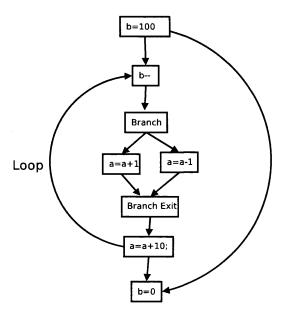

| 3.4  | A Control Flow Graph                                                | 68 |

### LIST OF FIGURES

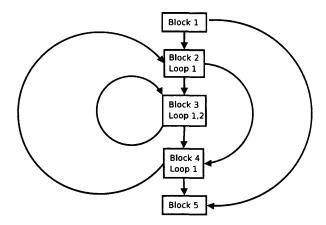

| 3.5  | A Control Flow Graph, labelled with loop IDs                          |

|------|-----------------------------------------------------------------------|

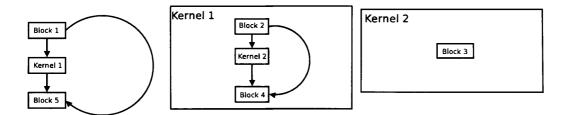

| 3.6  | A Control Flow Graph, with Kernels Separated                          |

| 3.7  | A Kernel Description File                                             |

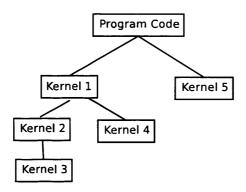

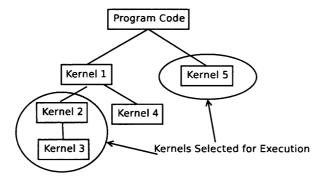

| 3.8  | A Kernel Tree                                                         |

| 3.9  | Client Output                                                         |

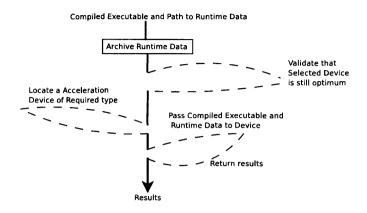

| 3.10 | Client in the Execution Step                                          |

| 4.1  | A Kernel Tree                                                         |

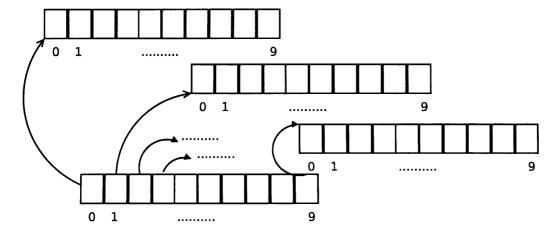

| 4.2  | A Multi-Dimensional Array                                             |

| 4.3  | A CUBIN file                                                          |

| 4.4  | ClearSpeed: Memory buffer layout                                      |

| 4.5  | GEMM: Example Kernel Tree                                             |

| 5.1  | Internal Structure of Application Classifier                          |

| 5.2  | The Database of Performance Data                                      |

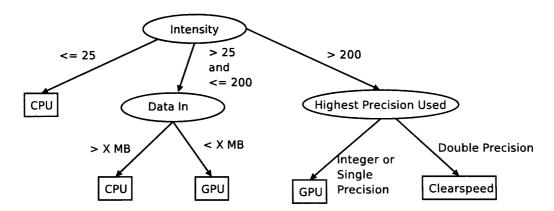

| 5.3  | An Example Decision Tree                                              |

| 6.1  | Graph of Single Precision Execution Times for Structured Grids        |

|      | Application                                                           |

| 6.2  | Graph of Double Precision Execution Times for Structured Grids        |

|      | Application                                                           |

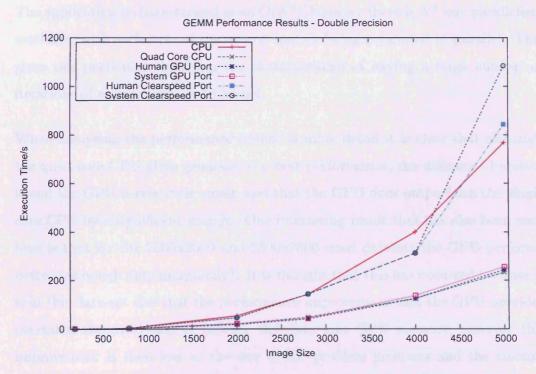

| 6.3  | Graph of Single Precision Execution Times for GEMM Application. 160   |

| 6.4  | Graph of Double Precision Execution Times for GEMM Application. 161   |

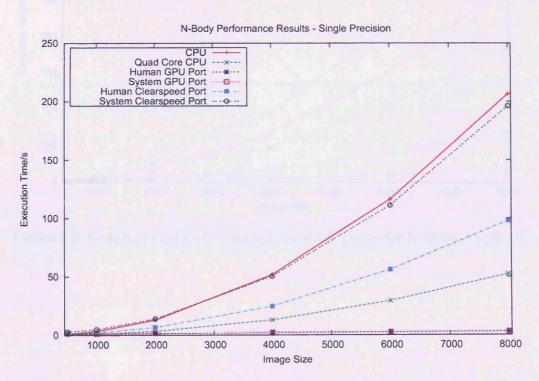

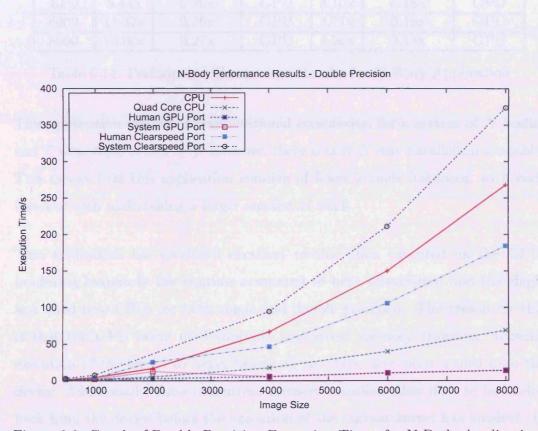

| 6.5  | Graph of Single Precision Execution Times for N-Body Application. 166 |

| 6.6  | Graph of Double Precision Execution Times for N-Body Application. 167 |

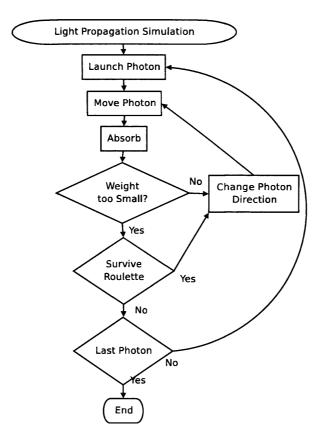

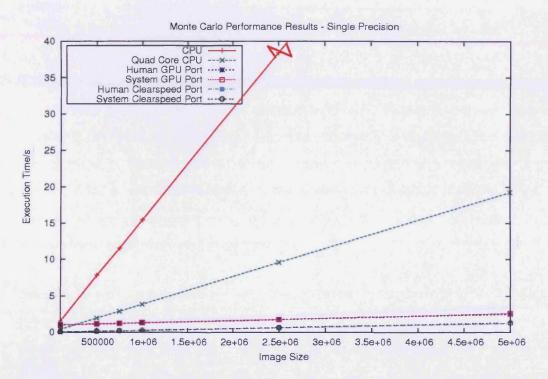

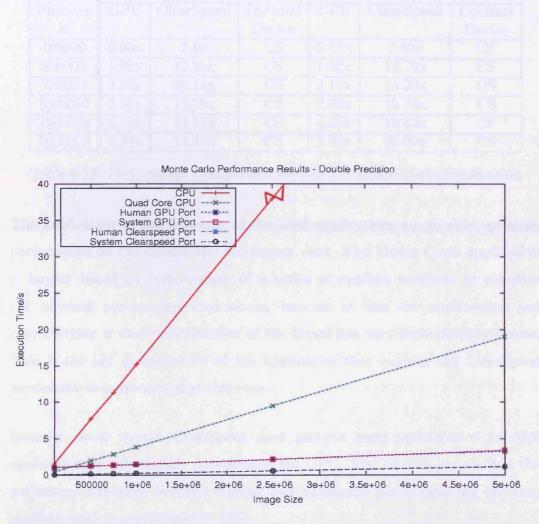

| 6.7  | Flowchart of the Monte Carlo Technique used based on [115] 172        |

| 6.8  | Graph of Single Precision Execution Times for Monte Carlo             |

|      | Application                                                           |

| 6.9  | Graph of Double Precision Execution Times for Monte Carlo             |

|      | Application                                                           |

| 6.10 | Classification Model Produced after Seed Applications 178               |

|------|-------------------------------------------------------------------------|

| 6.11 | Sample input and output of Fast Fourier Transform 179                   |

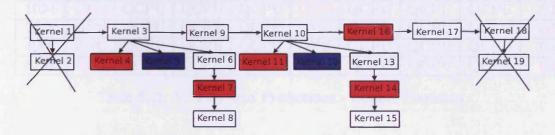

| 6.12 | Fast Fourier Transform Application Structure                            |

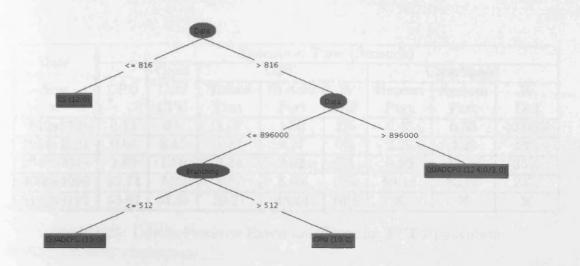

| 6.13 | Classification Model Produced after FFT Application has been            |

|      | profiled                                                                |

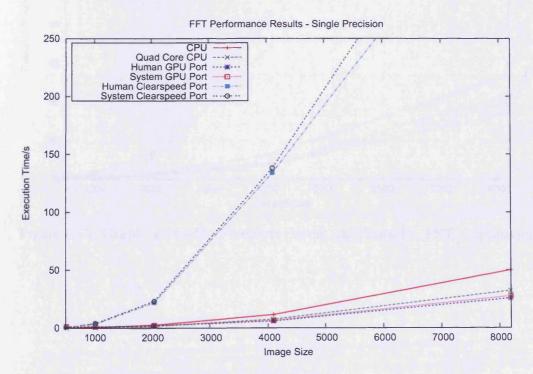

| 6.14 | Graph of Single Precision Execution Times for FFT Application $184$     |

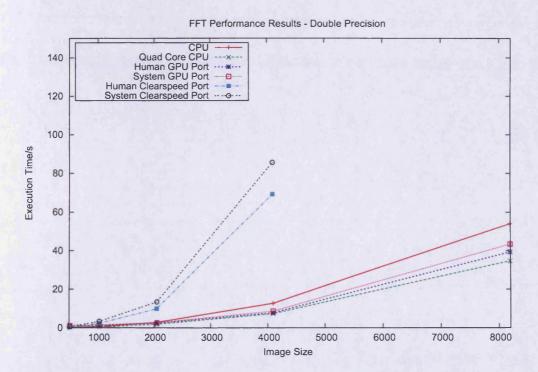

| 6.15 | Graph of Double Precision Execution Times for FFT Application. 185      |

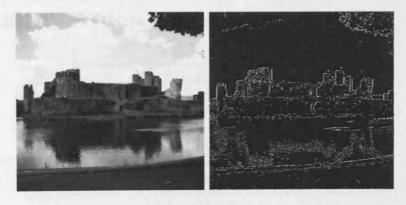

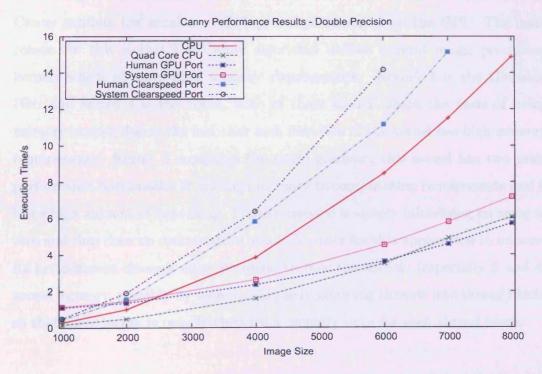

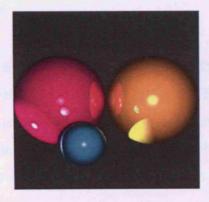

| 6.16 | Sample input and output of a Canny Edge Detector 190                    |

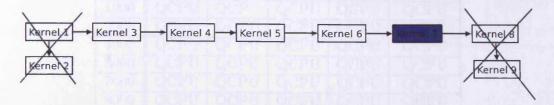

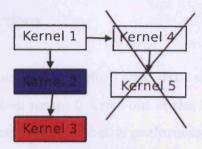

| 6.17 | Canny Application Structure                                             |

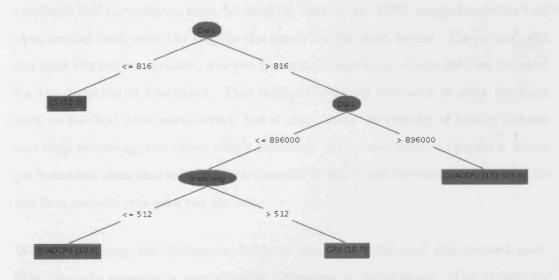

| 6.18 | Classification Model Produced after Canny Application has been          |

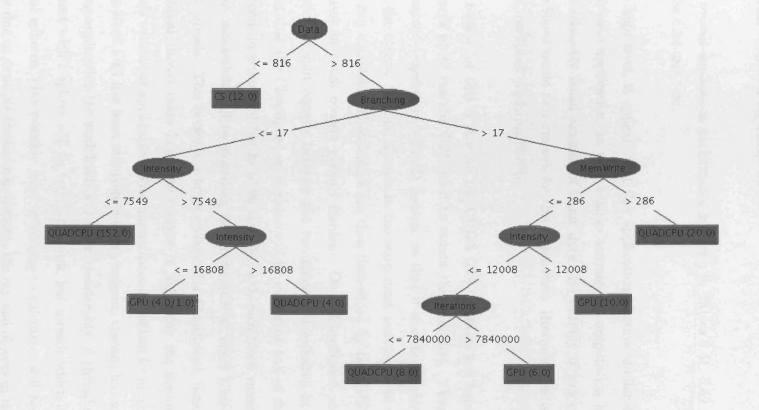

|      | profiled                                                                |

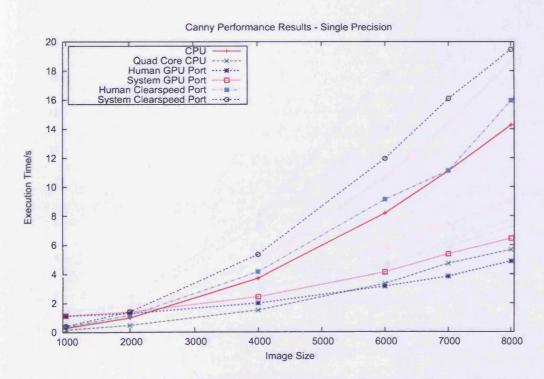

| 6.19 | Graph of Single Precision Execution Times for Canny Application. 195    |

| 6.20 | Graph of Double Precision Execution Times for Canny Application. 196    |

| 6.21 | Sample output of Iterative Ray Tracer                                   |

| 6.22 | Ray Tracer Application Structure                                        |

| 6.23 | Final Classification Model                                              |

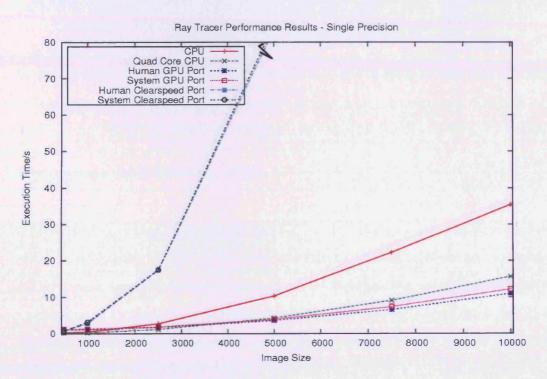

| 6.24 | Graph of Single Precision Execution Times for Iterative Ray Tracer.206  |

| 6.25 | Graph of Double Precision Execution Times for Iterative Ray Tracer. 207 |

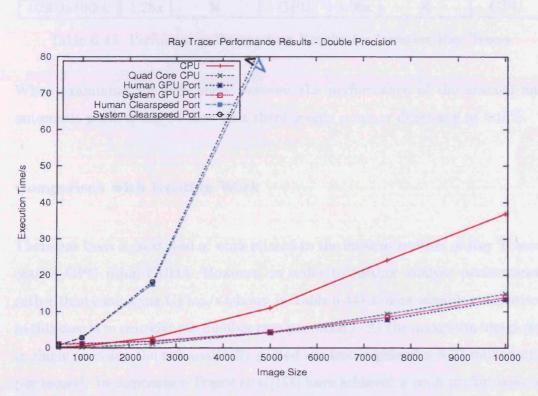

| 8.1  | Cloud Computing                                                         |

| 8.2  | Adaptive Porting                                                        |

# Listings

| 2.1  | Example of Cg Code adopted from [85]                           | 15 |

|------|----------------------------------------------------------------|----|

| 2.2  | Example of Brook Code Adopted from [24]                        | 17 |

| 2.3  | Example of C for CUDA Code Adopted from [46]                   | 19 |

| 2.4  | OpenCL version of CUDA Code shown in Listing 2.3 based on [70] | 22 |

| 2.5  | Example of $C_N$ Code                                          | 30 |

| 2.6  | Mitrion-C Code - Line numbers added for clarity                | 35 |

| 2.7  | PGI Accelerator Compiler Example adopted from $[134]$          | 47 |

| 2.8  | Sieve Example                                                  | 49 |

| 2.9  | HMPP Example Codelet Definition                                | 50 |

| 2.10 | HMPP Codelet Callsite                                          | 50 |

| 2.11 | Rapidmind Example                                              | 52 |

| 2.12 | Ct Code Example                                                | 52 |

| 3.1  | Code Example for Control Flow Graph                            | 68 |

| 3.2  | Algorithm for Loop Identification                              | 70 |

| 3.3  | Source code that generated Figure 3.5                          | 71 |

| 4.1  | CUDA: Initialisation Code                                      | 84 |

| 4.2  | CUDA: Allocating memory                                        | 85 |

| 4.3  | CUDA: Loading a single dimensional array onto the device       | 85 |

| 4.4  | CUDA: Loading a multi-dimensional array                        | 87 |

| 4.5  | CUDA: Calling the device code                                  | 87 |

| 4.6  | CUDA:Loop counter look-up code                                 | 88 |

LISTINGS 1

| 4.7  | CUDA: Loading data back to host for Single Dimensional Arrays 89  |

|------|-------------------------------------------------------------------|

| 4.8  | CUDA: Loading data back to host for a two dimensional array $$ 89 |

| 4.9  | CUDA: Random Number Generation                                    |

| 4.10 | CUDA: The Kernel Template                                         |

| 4.11 | ClearSpeed: Initialisation Code                                   |

| 4.12 | ClearSpeed: Declaring Process Handles                             |

| 4.13 | ClearSpeed: Declaring Variable Pointers                           |

| 4.14 | ClearSpeed: Loading the Device Code                               |

| 4.15 | ClearSpeed: Loading Single Variables                              |

| 4.16 | ClearSpeed: Loading Arrays                                        |

| 4.17 | ClearSpeed: Allocating Memory                                     |

| 4.18 | ClearSpeed: Calling a Kernel                                      |

| 4.19 | ClearSpeed: Wait for execution to finish                          |

| 4.20 | ClearSpeed: Loading Data Back onto the Host                       |

| 4.21 | ClearSpeed: Cleanup                                               |

| 4.22 | ClearSpeed: Declaring Global Variables                            |

| 4.23 | ClearSpeed: Kernel Template                                       |

| 4.24 | Clear<br>Speed: Multiple Iterations per PE                        |

| 4.25 | ClearSpeed: Random Number Generation                              |

| 4.26 | ClearSpeed: Reading from mono memory                              |

| 4.27 | ClearSpeed: Writing to mono memory                                |

| 4.28 | ClearSpeed: Buffered Kernel Template                              |

| 4.29 | CUDA: Makefile                                                    |

| 4.30 | ClearSpeed: Makefile                                              |

| 5.1  | Algorithm for Integration of New Devices                          |

| 5.2  | Timing Code: Starting the Timer                                   |

| 5.3  | Timing Code: Stopping the Timer                                   |

| 5.4  | Ensuring CUDA execution finished before stopping the timer 14     |

| LISTINGS |                             |       |

|----------|-----------------------------|-------|

|          |                             |       |

| 6.1      | Ray Tracing Algorithm [127] | . 199 |

# Chapter 1

# Introduction

# 1.1 Introduction

The research described in this thesis centres around the use of Application Acceleration Devices. A device can be classified as an Application Accelerator if it can be added to a computing system to increase the performance of applications running on that system. There are a wide variety of these devices currently available, including:

- Graphics Processing Units (GPU).

- Field Programmable Gate Arrays(FPGA).

- CELL Processors.

- Physics Accelerators.

- Programmable Application Specific Integrated Circuits (ASICS) of which ClearSpeed is an example.

- Audio Processing Accelerators.

With such a wide variety of devices fitting the classification of Application Accelerators, only a subset of these will be considered in this thesis. These are illustrated in Figure 1.1 and will be discussed in more detail in Chapter 2.

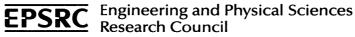

Figure 1.1: Examples of Acceleration Devices: a) CELL B.E [4] b) FPGA from Nallatech [7] c) NVIDIA Tesla [101] d) ClearSpeed [1].

Application Accelerators are generally added to a computing system via the PCI bus and act as co-processors, this has the advantage that tasks executed on the application accelerator are decoupled and can run in parallel with traditional CPU tasks. However, connection via the PCI bus also has several disadvantages:

- Devices are unable to access main memory.

- Devices are unable to access Input or Output devices.

1.1. Introduction 3

- Devices are unable to access network interfaces.

- Devices are unable to access non-volatile storage devices.

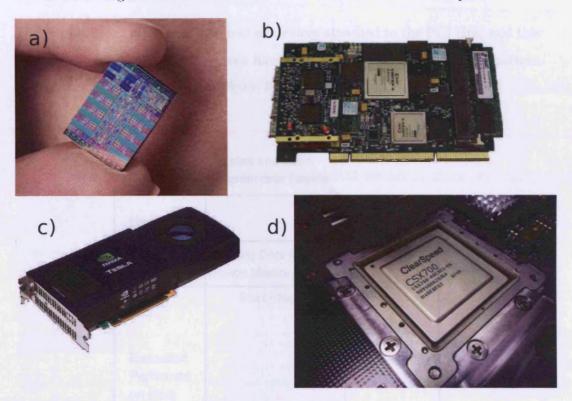

These limitations are common across all devices attached to the PCI Bus, and this means that all Acceleration devices have, at the highest level, a similar pattern of execution. This is shown in Figure 1.2.

Figure 1.2: Application Accelerators as Co-processors.

Figure 1.2 shows that Application Accelerators have the following overheads compared to standard CPU execution: Device Configuration, transfer of data

1.1. Introduction 4

from host memory to device memory and transfer of results back to host memory from device memory. All of these overheads add latency and have a detrimental effect on an application's performance. This means that application developers must be mindful of these overheads when developing applications to ensure that the speed-up attained from the use of an application accelerator is sufficient to overcome these overheads.

Additionally, developers using application accelerators must consider that each type of accelerator has a different architecture and different programming style. This can lead to different applications favouring different device types, depending largely on the characteristics of the application and the device.

Finally, a particular device type may have additional advantages/disadvantages that are not related to performance, these could include power usage, compatibility with existing hardware, cost, software development environment and support offered.

These variations between devices and even between manufacturers of the same device, are further discussed in Chapter 2. This wide variations of characteristics does however mean that an application developer must ask themselves the following questions before starting development:

- What device is suitable for accelerating my application?

- What device is suitable for my non-performance based requirements i.e. power requirements?

- Will the performance improvement that results from using this device be worth the time/monetary expenditure?

### 1.2 Hypothesis

The research hypothesis is:

It is possible to construct a self-modifying and expandable automatic code porting system that can, based on heuristics, select the most appropriate application acceleration device and provide comparable performance to that achievable by an experienced human programmer.

In this hypothesis the term "self-modifying" refers to the ability of the system to improve the heuristic model that it uses to determine the most appropriate device. Additionally, the term "expandable" refers to the ability of the system to be expanded to utilise new acceleration devices, or newer versions of existing acceleration devices.

# 1.3 Scope

The scope of the research conducted in this thesis can be broken down into three key sections:

Target Users: The level of abstraction provided by the developed system will be targeted specifically at non computer science users. These users will have programming experience but will not be familiar with the intricacies of acceleration devices or their programming methods. The motivation of these users will be to simply achieve application speedup.

**Target Applications:** The applications considered by the system must already contain at least one section of code that is capable of being executed in parallel.

The research described by this thesis focuses on the locating of parallel code within the input application, deciding on the appropriate method for acceleration of this code and then porting the selected code to the acceleration device. The parallelisation of sequential code is not considered and is deemed beyond the scope of this work.

Target Devices: The target devices that are considered in this thesis are restricted by currently available hardware. The FPGA, CELL, GPU and ClearSpeed accelerators have all been considered, however, due to hardware limitations, only the NVIDIA GPU, and the ClearSpeed accelerator device have been taken forward for development.

### 1.4 Contributions

This section lists the major contributions of this thesis. The four main contributions are:

- 1. A novel distributed system and architecture that is able to analyse and port input applications to an acceleration device and, with a reasonable success rate, predict the most appropriate device for the application concerned.

- 2. Demonstration that the system is able to modify itself, in that it is able, from experience, to adapt the model that is used to select an acceleration device and that it is able to adapt to the introduction of the new devices, or improved versions of existing devices.

- 3. The ability to demonstrate, through the use of well understood and developed machine learning techniques, a set of explicit parameters and features that can be used to describe the selection of an appropriate acceleration device.

4. The provision of a route to application acceleration to non-computer science users. This may be the porting of an application, generating an efficient initial port from which further performance improvements can be made by experienced human programmers, or determining in a quick and simple manner, whether the users application is suitable for acceleration.

### 1.5 Thesis Summary

#### Chapter 2: Background

Chapter 2 introduces the field of application accelerators, outlining the different devices that are currently available and showing the differences between them. This chapter also examines the programming methods that these devices support and shows that the differences between these programming methods can vary from as little as a different API to having to use a different programming paradigm. Using this knowledge, this chapter then describes the problems that are associated with programming acceleration devices, namely: the difficulty in programming such devices and the lack of abstraction between devices. Finally, this chapter will describe and compare current academic and commercial systems that are also aiming to tackle these problems and discuss their successes and failures.

#### Chapter 3: Overview of the Application Porting System

Chapter 3 outlines the overall structure of the system that has been constructed to validate the hypothesis outlined in Section 1.2. This chapter will describe the distributed nature of the system and how the components of the system fit together. Additionally, this Chapter will describe the client that has been developed to allow users to interface with the porting system.

#### Chapter 4: Code Generation

Chapter 4 describes the code generation functionality of the system. This chapter will describe the process that is used to port code to  $C_N$  for ClearSpeed and CUDA-C for NVIDIA GPUs. This chapter will also illustrate the differences between these two programming methods.

#### Chapter 5: Device Selection, Self-Modification and Expandability

Chapter 5 will describe the remaining functionality of the application porting system. This chapter will explain how the system is able perform the decision making required to match an application to the most appropriate acceleration device. Secondly, this chapter will describe how the system is able to achieve its goals of being "self-modifying" and "expandable".

#### Chapter 6: Application Case Studies

Chapter 6 describes a series of applications that have been selected to test the system. These applications are divided into two categories. A series of relatively simple "seed" applications are trialled in order to provide a base of knowledge for the system to operate with more complex examples.

Three more complicated applications are also executed. For each of these applications the performance and the decisions taken are analysed in order to judge the effectiveness of the system. Additionally, by the execution of these applications in sequence, the ability of the system to modify its classification model will be tested. Finally, the performance of the generated code will be tested against the performance of an optimised, but not re-factored, hand port produced by the developer.

#### Chapter 7: Conclusions

Chapter 7 will outline the overall conclusions that can be drawn from this work. This chapter will analyse the results from Chapter 6 against the hypothesis presented in Chapter 1 and then validate the contributions that were also presented in Chapter 1.

Secondly, this chapter will evaluate the work done in this thesis, examining the relative strengths and weaknesses of the work in isolation and in comparison to the two most relevant commercial products.

Finally, this chapter will also present conclusions on the relative differences between the two acceleration devices that have been utilised in the course of this research.

#### Chapter 8: Future Work

Chapter 8 will describe ideas for the future development of this work. This will largely centre around suggestions for the future development of the application porting system that has been developed. In addition to suggested modifications it will present early thoughts on how the system can be deployed in a cloud computing environment.

# Chapter 2

# Background

#### 2.1 Introduction

This chapter aims to introduce the key elements of this research, focusing specifically on prior work and approaches related to the work that is presented in this thesis. This chapter will outline the types of acceleration devices that are currently available, expanding on the brief introduction presented in Chapter 1. In particular this chapter will cover the development of the hardware architecture of these devices. It will also provide an overview of the software tools, both academic and commercial, that have been developed to facilitate their use in the field of High Performance Computing. This chapter will then discuss some of the successes that have been achieved in porting algorithms to these devices and developing numerical libraries to support the work of other developers. Finally, this chapter will state the key issues currently preventing the adoption of these devices and examine the currently available industrial and academic solutions. This examination of existing technology will enable a comparison of the available solutions and the identification of key areas for improvement.

### 2.2 Graphics Processing Units

While probably the most recent device to find acceptance as a viable Application Accelerator for High Performance Computing (HPC) applications, the Graphics Processing Unit (GPU) has experienced an explosion of interest, driven by the fact that currently GPUs represent some of the most computationally powerful hardware for the dollar [111]. This has caused a vibrant community of developers to emerge. For example, considering only the use of NVIDIA's tools, there have already been over 2700 citations on Google Scholar and 300 universities worldwide are now teaching GPU programming using NVIDIA CUDA [50].

The GPU market is dominated currently by two companies: NVIDIA and AMD (formerly ATI), although Intel were, for a time, attempting to compete with their Larrabee [122] architecture, although this product, as a GPU, has now been cancelled. This section will examine the development of the GPU architectures and programming models employed by both NVIDIA and AMD. It will also discuss briefly existing work that has been conducted in the use of the GPU in accelerating HPC applications.

#### 2.2.1 Device Architecture

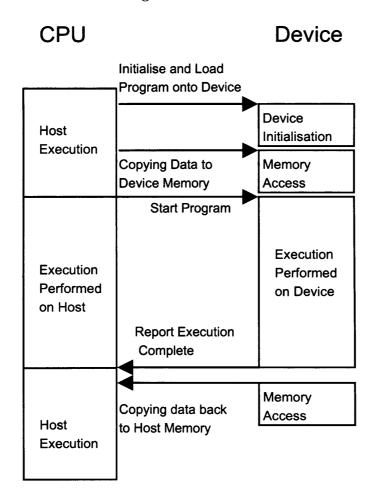

The Graphics Processing Unit (GPU) was originally designed as a fixed function rendering pipeline (shown in Figure 2.1). Within this pipeline the Vertex and Fragment processing units have been historically configurable but not programmable [110]. As GPUs have evolved each new generation has added to the functionality of these Vertex and Fragment processing stages. The first programmable stage was introduced in 1999 when NVIDIA added support for register combiner operations which allowed a limited programmability [111]. A

Figure 2.1: The GPU Rendering Pipeline.

further key development was the introduction of an assembly language that allowed the specification of programs that run on a per vertex basis [84]. With the addition of support for fragment (pixel) shading as well as vertex shaders, this programmability was formally defined as a Shader Model. Shader Models have improved through several iterations, with more complete instruction sets, more flexible control-flow operations and larger limits on the size and resource consumption of their programs [110]. This process of improvement, without radically altering the architecture, continued until the development of Shader Model 3.0 in 2004.

Shader Model 4.0, first made public in 2006, was the first shader model to present a unified architecture rather than utilising separate vertex and fragment processing units. This new architecture allowed the unification of the instruction sets by defining a single common core, with a virtual machine, as the base for each of the programmable stages. This new unified model is considerably closer to providing all the arithmetic, logic and flow control constructs available on a standard CPU [20].

The first GPU to utilise the unified shader architecture defined by Shader Model 4.0 was the Xenos chip by AMD in 2005. This chip was used solely in the XBox 360 [110]. However NVIDIA were the first to make Shader Model 4.0 cards widely available with their GeForce 8800 in 2006. The GTX version of this card comprised 128 of these unified processors (dubbed stream processors by NVIDIA) [45]. All the programmable and fixed function aspects of the graphics pipeline

are now computed on these stream processors. This allows more complex load balancing to take place, allowing any stage of the pipeline to consume more of the available stream processors dependent on its requirements. This load balancing is critical to prevent bottlenecks caused by stages of the graphics pipeline taking longer to compute than others.

Currently all new GPUs produced by the two main vendors, NVIDIA and AMD, utilise this unified architecture, of which NVIDIA's version is shown in Figure 2.2.

Figure 2.2: The NVIDIA GeForce 8800 Architecture. Adopted from [45]

One the most recent developments in graphics hardware was the addition of support for double precision floating point arithmetic. The FireStream 9170, launched in 2007, was the first card on the market to support double precision. NVIDIA soon followed with their double precision chipset, the GTX 200 [47] and double precision support has now become the standard for high end, professional level GPUs. However, it should be noted that utilising double precision comes with a performance penalty as all current model GPUs have fewer double precision processing units when compared to single precision processing units. e.g. the

NVIDIA Tesla C1070's double precision performance is approximately 10% of its single precision performance [44].

GPUs have advanced considerably, even in the last few years. Current GPU architectures bear little resemblance to those of ten years ago and GPUs are now no longer a fixed function implementations of the graphics pipeline but are now fully programmable devices with supporting fixed functionality enabling it to carry out its primary role as a rendering engine.

# 2.2.2 General Purpose Computation on Graphics Hardware

One of the first uses of the Graphics Processing Unit as a General Purpose computation device can be found in [26], published in 1994. In this paper, Cabral et al implemented Filtered Backprojection, a tomographic reconstruction algorithm, on the GPU by utilising available texture mapping hardware. In order to achieve this, Cabral was forced to re-factor the Filtered Backprojection algorithm into a graphics problem, within the constraints of the fixed-function OpenGL pipeline available at the time. The result of this was a two pass rendering algorithm that utilising the GPU's hardware accelerated texture mapping and frame buffer accumulation functions. This new approach gave performance in excess of 100x faster than executing on the CPU.

Despite these early uses of the GPU for general purpose computing, general purpose graphics processing units(GPGPU) were still largely impractical for developers. At the time, there were simply no available tools to allow developers to leverage the power of a GPU unless their application was able to be refactored to leverage on the fixed-function OpenGL pipeline. Interest was renewed with the

development of programmable shaders and the formalisation of these as Shader Models. Several high level programming languages for shaders originated from this formalisation process. HLSL from Microsoft [113], GLSL for OpenGL [76] and Cg from Nvidia [85].

Listing 2.1: Example of Cg Code adopted from [85]

```

float4 main(appin IN, out float4 COUT, uniform Light

lights[]) {

for (int i=0; i < lights.Length; i++) {

Cl=lights[i].illuminate(IN.pos,L);

color+=Cl * Plastic(texcolor,L,Nn,In,30);

}

COUT=color;

}</pre>

```

An example of Cg code is shown in listing 2.1 and the resemblance to C can be easily seen. Both HLSL and GLSL are locked to their respective graphics implementations while Cg provides the ability to compile to other targets. However, all these languages share one main disadvantage: they are at their core, shading languages. So all general purpose programming must be mapped onto graphical concepts [64] i.e.:

- Textures  $\rightarrow$  Arrays.

- Render to Texture  $\rightarrow$  Feedback.

- Fragment Programs  $\rightarrow$  Inner loops.

- Geometry Rasterization  $\rightarrow$  Computation Invocation.

- Texture Coordinates → Computation Domain.

- Vertex Coordinates  $\rightarrow$  Computation Range.

This means that programming using these languages is vastly different from standard programming methodologies and requires programmers, unless already familiar with graphical programming, to undertake various unfamiliar tasks such as drawing geometry and manipulation of the camera to achieve the desired computation steps.

Despite these problems, the promise of increased performance made by the GPU encouraged a considerable amount of work in the field and a large community grew up around the "GPGPU" (General Purpose Graphics Processing Units) phenomena.

Many items of literature have dealt with the porting of applications to the GPGPU using Shader Model 3.0 methods. In 2003 Moreland et al, ported the Fast Fourier Transform to the GPU [94] and their implementation performed competitively with highly optimised CPU implementations. Other applications that have been successfully implemented on the GPU include Ray Tracing [118], Volume Rendering [124] [126] and a re-implementation of earlier work on Filtered Backprojection using commodity hardware and more modern Shader Model 3.0 techniques [135].

It was commonly accepted that shader programming was a woefully inadequate solution for General Purpose Computation on GPUs and several pieces of work were conducted in an attempt to resolve this. Lefohn has designed Glift which defines a set of high level GPU data structures [82]. Glift builds on Cg from NVIDIA to provide a set of random access data structures, similar to those provided the STL(Standard Template Library) for C++. The Brook streaming language was developed as a further attempt to solve these problems. The Brook language presents a streaming model to the programmer with the Brook compiler

and runtime system provides the mapping onto the previous discussed GPU APIs [24]. The Brook language enables the programmer to represent their program in terms of streams and kernels. The language also supports many additional features often desired by newcomers to GPGPU programming such as reductions. An example of the Brook programming language is shown in listing 2.2

Listing 2.2: Example of Brook Code Adopted from [24]

Brook was generally successful and several applications were successfully ported using it. In 2006 Elsen et al, ported a N-Body simulation to the GPU using Brook and they achieved, in some cases, upwards of 25x speedup [53].

Several other abstractions have been developed to fill a similar space of providing translation from high level languages to shader based languages. SH [5] was developed by a team at the University of Waterloo and was eventually commercialised and became Rapidmind, which is discussed in Section 2.7.4. PyGPU was developed to add GPU acceleration to Python [83] and Microsoft developed their Accelerator language which is a set of additions to C# utilising a special data type called Parallel Arrays [129]. While these higher level languages go some way to solving the problems of programming in a shader based environment they cannot escape the fact that the architecture they are

abstracting from is still too specific to GPU concepts to allow true general purpose programming.

However, there were two developments in GPGPU that changed all of this. Firstly, the introduction of Shader Model 4.0, which allowed programming of the GPU in a non shader based way allowed the introduction of new high level tools, such as CUDA and CTM, which are discussed below, and the further improvement of existing tools.

Secondly, one of the first languages to fully utilise this new unified model was introduced: NVIDIA's C for Compute Unified Device Architecture language (C for CUDA). This language leverages on the new functionality provided in Shader Model 4.0 to provide what is probably the most popular language for General Purpose development on GPUs.

C for CUDA allows programming in a full implementation of the C language, with some GPU extensions and an host processor API. C for CUDA provides the programmer with the following features [46]:

- Methods for on card memory management.

- Ability to define methods for execution on CPU or device.

- Kernel Invocation methods.

- A method to specify the allocation of threads across the device.

The CUDA architecture allows the user to declare a kernel which is executed N times by N threads. These threads are grouped together into thread blocks. All threads within a thread block can cooperate together, sharing memory and synchronising. These thread blocks are then arranged into a two dimensional

grid of thread blocks. Each thread block must be able to execute independently of any other. The number of thread blocks directly effects the parallelisation of the application across the multiple processing units available on the GPU. This architecture is shown in Figure 2.3 and an example of C for CUDA is shown in listing 2.3.

Listing 2.3: Example of C for CUDA Code Adopted from [46]

```

--global__ void mul(float * a, float *b, float *c) {

int i = blockIdx.x * blockDim.x + threadIdx.x;

int j = blockIdx.y * blockDim.y + threadIdx.y;

if (i < N && j < N) c[i][j] = a[i][j] + b[i][j];

}

int main() {

cudaSetDevice(0); // use first GPU

cudaMalloc(....); // allocate memory

cudaMemcpy(....); //copy to device

mul<< dimensions of grid, dimensions of each

thread block>>(A,B,C);

cudaMemcpy(....); // copy results from device

cudaFree(....); //free memory from device.

}

```

AMD have also constructed a software stack to utilise the new Shader Model 4.0 architecture. Their initial offering was the Close to the Metal(CTM) assembly language. CTM was designed and marketed as a low level language, with a supporting API; this discouraged its adoption by many programmers who were seeking to develop at a higher level of abstraction. The CTM system allowed direct access by the programmer to the floating point processors inside the card [72] via an assembly language interface. AMD then expanded their offering

Figure 2.3: NVIDIA CUDA Architecture. Adopted from [46]

by producing their Stream Computing Software Stack. This stack consisted of the AMD Compute Abstraction Layer, a development of CTM and a high level language based on Brook called Brook+ [71].

In addition to NVIDIA CUDA and Brook+ from AMD, one of the more recent developments has been the introduction of OpenCL. OpenCL(Open Computing Language) is an open, royalty free standard for general purpose programming across CPUs, GPUs and other processors. It has been developed by the Khronos Group [61].

The OpenCL standard is based on C99 and aims to allow programming of computation devices while abstracting from the underlying hardware. In general design terms OpenCL is similar to CUDA, although its API is of a slightly lower level to allow for the differing characteristics of the devices on which it targets.

The OpenCL architecture is shown in Figure 2.4. Each of the basic units of the OpenCL architecture is analogous to the basic units of the CUDA architecture discussed earlier [105]:

- Grid NDRange.

- Block Work-Group.

- Thread Work-Item.

An example of OpenCL code is shown in Listing 2.4. It can be seen from this listing, that although the overall architecture is similar to NVIDIA's CUDA, the API operates at a lower level thus giving the programmer more flexibility to program with alternative devices.

Currently OpenCL is supported by AMD, NVIDIA and Apple. At the time of writing, however, all current OpenCL implementation are for GPUs only.

Figure 2.4: The OpenCL Architecture. Adopted from [60]

Listing 2.4: OpenCL version of CUDA Code shown in Listing 2.3 based on [70]

```

//using runtime compilation so source stored in character

array

char source []=

kernel void mul(global float * a, global float *b, global

float *c) {

int id=get_global_id(0);

c[id] = a[id] + b[id];

}

int main() {

//setting up the device

clGetDeviceIDs(NULL,CL_DEVICE_TYPE_GPU,1,&device,

num_devices_returned);

context=clCreateContext(0,1,device,NULL,NULL,&err

);

queue_gpu=clCreateCommandQueue(context, device, 0,&

err):

//create memory on device

memobjs[0] = clCreateBuffer(...);

memobjs[1] = clCreateBuffer (...);

memobjs[2] = clCreateBuffer (...);

//load the program onto device

program=clCreateProgramWithSource (context, 1, & source

...);

clBuildProgram (program , ....) ;

kernel=clCreateKernel(program, "mul", NULL);

clSetKernelArg(kernel, 0, ....);

clSetKernelArg(kernel,1,...);

clSetKernelArg(kernel, 2, ....);

global_work_size[0] = n;

//run program

clEnqueueNDRangeKernel(cmd_queue, kernel,....);

//read data back

clEnqueueReadBuffer(context, memobjs[2]....);

```

The competing implementations; CUDA, OpenCL and Brook+ have all enjoyed success and have succeeded in making GPGPU programming available to a far wider community than before. However, there are still problems. It is commonly agreed that in order to make GPU computing more accessible higher level APIs are needed [31] and several projects have been undertaking looking into this. Breitbart [23] has developed a C++ framework designed to allow the easy integration of CUDA into existing C++ applications. Additionally Ueng et al [131] have developed CUDA-Lite. CUDA-Lite is a tool that uses a series of programmer supplied annotations within a CUDA C code program that uses only the device's global memory. CUDA-Lite performs a set of automated transformations to this input to produce output code that maximizes memory performance via memory coalescing and ensuring that maximum use is made of all levels of CUDA's memory hierarchy. The different levels of this hierarchy, such as on-chip shared memory, are often ignored by developers due to a lack of understanding of the CUDA memory hierarchy, which is substantially different from a standard CPU, and the possible performance improvements that can be gained from its correct use. This problem of abstraction is currently being addressed in a variety of ways by tools such as HMPP and Rapidmind, which are discussed in detail in section 2.7.

### 2.2.3 The future of GPGPU

As one of the most rapidly advancing application acceleration devices, new and improved GPUs are regularly being developed by the major device vendors to enable them to keep their competitive edge, both in the GPGPU market and in the traditional graphics card market.

The latest development from NVIDIA has been the FERMI architecture. FERMI

is touted as the Next Generation CUDA Architecture and NVIDIA boasts a 4.2x performance improvement over the previous CUDA chipsets [48]. NVIDIA FERMI also promises the following key areas of improvement:

- Improved Double Precision Performance,

- ECC Support,

- Faster Context Switching,

- 4x More CUDA Cores per Multiprocessor,

- An Unified Address Space allowing the support of C++, including pointers,

- Allows the scheduling of up to four concurrent kernels.

If FERMI delivers on these promises, then it is anticipated that it will bring large performance improvements to GPGPU users, however, it is not the architectural leap that was encountered in the transition to Shader Model 4.0.

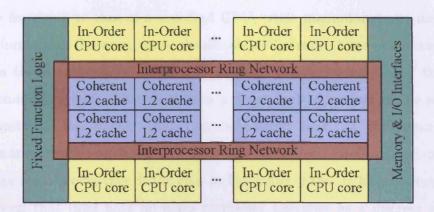

The other highly anticipated development in the field of GPGPU, was the release of the now discontinued Larrabee processor from Intel [122]. The philosophy behind Larrabee was that of a graphics card built up of CPU like cores running an extended version of the x86 instruction set. Intel believed that this CPU-like, x86 based architecture would allow for more flexibility than offered by current GPUs [122]. A diagram of the Larrabee architecture is shown in Figure 2.5.

The Larrabee architecture itself consisted of a set of multiple instantiations of an in-order CPU core that is augmented by a wide vector processor. These cores all communicate via a high bandwidth interconnect network. The Larrabee architecture only contains the minimum amount of fixed function logic to enable

Figure 2.5: The Larrabee Architecture, showing 8 CPU like cores, adopted from [122].

it to perform its graphics based tasks. The only fixed function logic that was expected to be included was texture filtering.

The HPC Development model for Larrabee, known as Larrabee Native, consisted of a complete C/C++ compiler that allowed static compilation of many existing C/C++ applications to Larrabee. However, there are several additional libraries that had to be used to gain the maximum benefit from Larrabee:

- Libraries to provide communication between host and device card. These allowed fast message passing between Larrabee and the host CPU. In addition both synchronous and asynchronous data transfers were to be supported.

- Threading using Larrabee's native software threading capability, exposed via a POSIX Threads API.

- SIMD vectorization. Each of Larrabee's SIMD processors were fully programmable by the programmer, in addition the native Larrabee compiler included a version of Intel's auto-vectorization compiler.

Larrabee promised a major architectural shift for GPUs, bringing their archi-

tecture far closer to that of a standard CPU, while maintaining and improving on performance. However, many details about Larrabee were never confirmed, such as the number of cores on the card and detailed examples of the HPC programming system. There had been a great deal of interest in the scientific community in the impact that Larrabee would have on accelerating high performance computing, however, despite the widespread interest, Intel cancelled the large scale production of the chip in December 2009. It has, however, been announced that Intel have no plans to release Larrabee as a discrete graphics chip, but they will be investigating its use as a HPC product [77] under the name "Knights Ferry" and the forthcoming "Knights Corner" products [52].

# 2.3 ClearSpeed Acceleration Architecture

ClearSpeed Inc. was founded in 2001 and originated from PixelFusion, a company that developed parallel technologies for high end graphics. At the core of ClearSpeed's offering was their acceleration chip, which evolved over several iterations. The CS301 was ClearSpeed's first chip and was released to customers in 2004. This was followed by the CSX600 in 2005 and the CSX700 in 2008 [87]. Through all these iterations ClearSpeed kept a similar architectural model in their chipsets. ClearSpeed accelerators have traditionally had several key advantages over other acceleration devices such as GPUs:

- IEEE 754 floating point compatibility.

- Low power usage  $\approx$ 10W.

- ECC Memory.

These advantages allowed ClearSpeed to achieve some success in the HPC market, with several applications being successfully ported to the device, such as: BUDE, MolPro, Amber 9, Monte Carlo Codes, and CFD(Computational Fluid Dynamics) methods [33] [34] [87].

However, in recent years the GPU manufacturers have released cards that have slowly eroded ClearSpeed's key advantages while offering better performance. ClearSpeed also suffered due to the onset of the recession in 2009, this affected ClearSpeed's largest market, the financial sector. These two factors have led to a sharp decline in business for ClearSpeed in the period up to the end of 2009 and they ceased trading in 2010.

The ClearSpeed architecture along with the Software Development Environment that ClearSpeed provides are now described in more detail in the following sections.

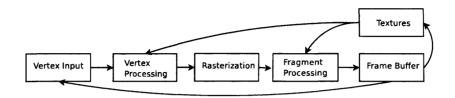

#### 2.3.1 Device Architecture

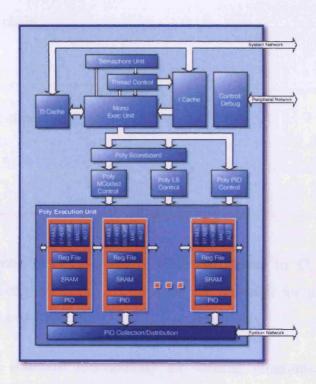

The CSX Chip architecture is illustrated in Figure 2.6. The architecture itself follows a SIMD(Single Instruction Multiple Data) pattern. It consists of a RISC-like control unit and a parallel execution unit. The parallel execution unit consists of a set of 96 Poly Processing Elements. These poly units operate in synchronous mode and are responsible for the execution of instruction in a SIMD manner [36]. Each Poly Processing Element, which provide the parallel processing power of the device, contains several functional units such as: Floating point units, Integer multiply-accumulate units and arithmetic units. Each PE(Processing Element) also contains its own registers, a small amount (6kB) of fast private memory, a data path to the device's main memory and the ability to communicate with neighbouring PE's using an operation known as Swazzle.

Figure 2.6: The ClearSpeed CSX Architecture. Adopted from [36]

Aggregated across all the parallel processing units, the last generation of the CSX chip boasted the following performance statistics [36]:

- Over 25 GFlops processing power, in single or double precision.

- 25,000 MIPS(Millions of Instructions Per Second).

- 96 Gbytes/s internal memory bandwidth.

## 2.3.2 Programming Tools

ClearSpeed provided a very complete development kit for their architecture, consisting of the following components:

- Compiler tool-chain,

- Libraries,

- Instruction set simulator,

- Debugger,

- A disassembler.

Their programming interface consists of an extension to C, called  $C_N$  for programming on-chip programs. Two APIs are provided for programming on the host; CSAPI and CSPX for C and C++ respectively.

CSAPI provides standard functionality for loading programs, copying data to/from the device and querying device characteristics, while CSPX provides several items of additional functionality and a higher level approach, allowing programs on the device to be called using a RPC(Remote Procedure Call) mechanism [75].

The main addition in the  $C_N$  language is the ability to distinguish between variables stored in the device's main menu (mono variables) and in the memory of a specific poly processor (poly variables) using two keywords: mono and poly [74]. An example of a  $C_N$  program is shown in Listing 2.5.

This program illustrates the main features of the  $C_N$  language. It shows how data are loaded from the array data, which is stored in mono memory, into the variable a which is stored in poly memory. The datum is loaded from the correct location in the array by using the  $get\_penum$  method. This method returns a value between 0 and 95 depending on which processing element the code is executing

Listing 2.5: Example of  $C_N$  Code

on. This example also shows how semaphores can be used to cause the program to block while waiting for memory transfers to complete [35].

Additionally the ClearSpeed SDK also contained a set of tools to support programming. A full debugger was available, which included the ability to step-through and monitor the program internals on the device itself. The SDK also contained a cycle accurate simulator, which allowed the testing and debugging of  $C_N$  programs without having a Clearpseed device present.

ClearSpeed, as a fully commercial product, was a uniformly developed application acceleration platform. There is a single card programming API available, with two host APIs. While there have been many applications successfully ported to the device, the commercial nature of the device, and its pricing, has led to it being less widely adopted than accelerators such as the GPU.

# 2.4 Field Programmable Gate Arrays

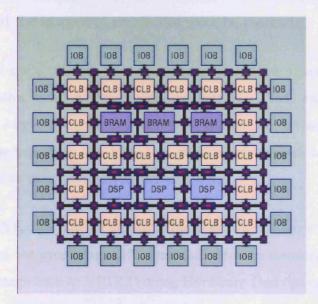

Field Programmable Gate Arrays or FPGAs were invented by Ross Freeman in the mid-1980s [25]. An FPGA is a semiconductor device that consists of programmable logic elements, interconnects and IO(Input/Output) blocks. All of these elements are configurable at run time. This provides the FPGA's key advantage over ASIC(Application Specific Integrated Circuit) devices: allowing complex digital circuits to be constructed on the FPGA at run-time. The internal structure of an FPGA is shown in Figure 2.7.

Figure 2.7: A FPGA Internal Structure adopted from [25]

Initially the FPGA was mainly used for prototyping purposes, however in recent years FPGAs have begun to contain enough programmable logic resources to enable them to be of interest to the HPC community. Many systems companies produce FPGA based supercomputers, including Cray, SRC, and more recently Nallatech [132].

However, as with many Application Acceleration devices, the biggest barrier to adoption is the programming method. FPGAs have arguably the most radically different programming method out of all acceleration devices and there are many additional considerations when developing for the FPGA:

- The internal clock speed of an FPGA is many times slower than that of a standard CPU. The performance has to come from performing many operations in parallel per clock cycle.

- There is only limited logic units available on an FPGA so a balance between program size and the amount of parallelism must be reached.

- Floating point units take up a far larger amount of logic space on the FPGA, so avoiding floating point where possible is desirable. This enables either the execution of a larger program, or more parallelism to be achieved. These characteristics means that the FPGA is particularly suited to integer based algorithms, such as many Bioinformatics problems.

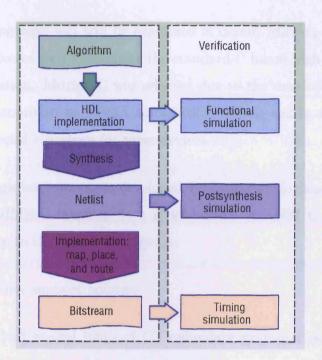

An overall FPGA design flow for an algorithm is shown in Figure 2.8. This design flow assumes that the programming language used by the developer is a hardware description language such as VHDL(Verilog Hardware Description Language). It is important to note that even once the application is in a hardware description language, there is still a large amount of testing and validation to be done before it can run on the device. The key step in this process is the place and route algorithm, this algorithm can take many hours to execute and will not always converge into a valid design, meaning that the process must be repeated.

Programming in VHDL is programming at an individual gate level, which is completely impractical for the majority of the HPC community. This had led the development of many higher level languages and compilers to facilitate general

Figure 2.8: Typical FPGA design flow adopted from [25]

purpose computing using these devices, these include:

- Mitrion-C [92].

- DIME-C [55].

- Handel-C [132].

- Trident C to VHDL Compiler [130].

- Single Assignment C (SA-C) ( A modification of C where each variable may only be assigned once) [95].

- ASC: A Stream Compiler. (C++ with the addition of several user-defined types, macros, operators and function calls) [89].

Two of these languages will now be examined in detail: Mitrion-C and Dime-C. DIME-C was selected as it exemplifies the standard C based high level languages used for compilation. Mitrion-C was selected due to the developers, Mitrionics, taking a novel approach to FPGA compilation that is unlike the majority of languages developed elsewhere for these devices.

DIME-C is a high level language developed by Nallatech for their HPC FPGA devices. The DIME-C language is a strict subset of ANSI C. The following restrictions apply to the DIME-C language:

- DIME-C does not support pointers.

- DIME-C has had several items of C's redundant grammar removed, namely certain switch statements and loops.

DIME-C also had several additions to facilitate compatibility with the FPGA in the form of function calls that allow the following functionality:

- A memory access library that allows efficient access to external SDRAM memories on the FPGA board.

- A math library.

- Functions to provide access to FIFO channels.

In conclusion, DIME-C provides the programmer the ability to develop for the FPGA in a familiar syntax. However, there are still significant differences and limitations that make development of efficient programs in DIME-C a difficult task and, as with all Acceleration devices, an understanding of the underlying hardware is required to selecting an appropriate application for porting and to make maximum use of the device.

Mitrion-C takes a radically different approach to any existing programming method. The Mitrion-C language, while very similar to C syntactically, is closer to a functional language in its method of execution. The Mitrion-C language is a single-assignment language centred around data-dependencies. So the order in which statements appear in the program, is largely irrelevant. A statement is executed as soon as all its data dependencies are available. In the trivial examples shown in Listing 2.6; lines 4 and 6 will be executed in parallel while line 5 will need to wait for line 4 to execute before it can be executed.

Listing 2.6: Mitrion-C Code - Line numbers added for clarity

```

1: int:8 a;

2: int:8 b;

3: int:8 c;

4: c=5*4;

5: a=c*2;

6: b=5*3;

```

As parallelism is implicit in the Mitrion-C language, it provides two different types of loops; for will execute the body of the loop in an iterative manner and foreach will execute a loop in a parallel manner.

Mitrion-C executes its code via a virtual machine. The virtual machine is configured using characteristics extracted from the Mitrion-C source code. The virtual machine code, together with the Mitrion-C program code are then compiled into VHDL and then placed onto the FPGA [91].

In addition to programming languages mentioned above, several other pieces of software have been developed to assist development with FPGAs. Holland et al. [66] have developed a Reconfigurable Amenability Test(RAT) to enable the estimation of the applications compatibility for porting to a FPGA and

Koehler et al [78] have proposed a performance analysis framework, which by using instrumentation of the device code, allows the monitoring of the device's performance at runtime. Andrews et al [13] have developed a system known as HThreads which is a pthreads compatible library that allows specified threads from the pthreads application to be compiled either for the CPU or FPGA. Another library that has been developed to aid FPGA programming is the Vforce library [93]. Vforce is an extension of the Vector Signal and Image Processing Library, that provides a FPGA hardware implementations for the algorithms in the library, encapsulating them beneath the libraries standard API. This allows users of the library to develop for the FPGA without the use of any hardware specific implementation.

One of the most novel developments using FGPA based technology was the Convey HC-1 Computer [41]. The Convey computer integrates a FPGA based processor with a standard Intel 64 processor. The FPGA and the Intel processor share memory and can be dynamically reloaded with different instruction sets, dubbed "personalities". These personalities allow the relatively rapid addition of new instruction sets or machine features which are tailored to specific applications. These specialised instruction sets allow efficient acceleration of applications on the system as they are able to leverage instructions or machine features that have been specifically developed to allow the acceleration of a particular algorithm or class of algorithms.

Despite all of these different programming languages and libraries that are available, no one language has emerged as dominant in the field. The only widespread consensus is that some High Level language is needed and the choice is often largely dependent on developer preference. This diversity of programming languages available for FPGAs has not, however, hampered the work of porting applications to this device and all of the languages have had

applications successfully ported to them.

# 2.5 IBM Cell Broadband Engine

The IBM Cell Broadband Engine (CELL/B.E.) processor was a joint development by Sony, Toshiba and IBM. The CELL itself is a high-performance, multi-core processor with a custom system-on-a-chip (SoC) implementation [121].

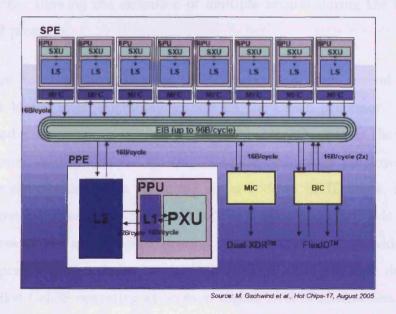

Figure 2.9: The CELL/B.E. Architecture adopted from [119].

Figure 2.9 shows the structure of the IBM CELL processor. The CELL chip itself consists of an IBM 64-bit Power Architecture core, the Power Processing Element, and eight specialised co-processors based on a single-instruction multiple-data (SIMD) architecture, these are the Synerginistic Processing Units (SPE), which provide the parallel processing power of the chip.

The CELL/B.E. architecture is programmed using either a modified version of the GCC toolchain or the IBM XL C/C++ compiler toolchains [42]. Both of

these compilers provide cross compilation from the development architecture to the PowerPC Architecture, for programming on the PPE, or to the custom SPE Architecture. The SPE components for both compilers support a set of extensions for SPE programming.

The executables generated by these compilers contain both the instructions for the PPE and instructions for the SPE units. Each program will contain one set of instructions for execution on PPE, but there may be several sets of instructions for the SPEs, allowing the execution of multiple kernels during the runtime of the overall program.

In addition to these programming tools, there have been several efforts to implement higher level programming tools for the CELL processor. IBM itself has released their compiler system, which has become known as the Octopiler. This compiler leverages on the existing compiler technology employed by IBM to provide optimisation when executing scalar code in SIMD units, and allows the auto generation of vector instructions from a scalar source, this is performed by a process known as Auto-SIMDization. The Octopiler also provides support for the OpenMP programming model [51]. Bellens et al [19] have developed a system called CellSS operating at an even higher level of abstraction. CellSS is not limited to the CELL architecture, although it is the architecture supported by their prototype. CellSS uses a code commenting style, similar to OpenMP, to identify tasks within a sequential program. The compiler uses these annotations to separate the main program code, which will run in the PPE, and the task code, which will run in the SPE. When the subsequent program is executed, the annotated tasks are submitted for execution. The execution of these tasks is controlled by a task list. When all data-dependencies for a task are met, it is added to the task list. The runtime system monitors this tasks list and then matches tasks in the list to available resources (The SPE processors in the case

of the CELL).

The majority of success for the CELL processor has come from its integration into the Sony PS3<sup>TM</sup>(PlayStation 3) and this console is currently the most accessible way for users to gain access to CELL technology. Recently, work has even been done utilising PS3's<sup>TM</sup>as scientific computing machines, essentially becoming acceleration devices in their own right. This has even been extended as far as the creation of PlayStation clusters. [80].

## 2.6 Computational Libraries

The use of computational libraries is a mainstay of development for standard sequential CPUs and multi-core architectures. Many such libraries have been developed such as LAPACK(Linear Algebra PAckage), FFTW and many offerings from the Numerical Algorithms Group(NAG) to name but a few. These libraries allow developers to leverage expertly optimised algorithms in order to achieve the best possible performance for common computational tasks. One common approach that may be taken by developers is the investigation of three possible options for optimising their code:

- Automatic optimisations provided by compilers or similar tools.

- Re-factoring of code.

- Identifying parts of their code that can be replaced by calls to a numerical library.

A similar approach can also be taken by developers utilising acceleration devices, with the main difference being that when considering an acceleration device, the computational libraries are generally device specific, allowing them to optimally utilise the varying architectures of acceleration devices. Although application acceleration is still a rapidly developing technology, many algorithms have been ported and optimised for use on these devices. This section will analyse existing work in this field that is relevant to the remainder of this thesis.

When considering computational libraries that have been developed for application acceleration devices, the libraries developed and shipped with the devices are often the first encountered by developers.

NVIDIA provide developers with a set of libraries including Basic Linear Algebra(BLAS), Fast Fourier Transforms(FFT), sparse matrix routed and random number generation [99] and these libraries in certain circumstance can provide performance approaching the device's maximum level[107]. ClearSpeed also provides users with a similar extensive set of libraries[35] and IBM provide, among others, a BLAS library[4]. AMD also provides developers with their Core Math Library[12] which provides implementations of BLAS, FFT, LAPACK and random number generation algorithms.