# Development of Novel Design Methodologies for the Efficiency Enhancement of RF Power Amplifiers in Wireless Communications

A thesis submitted to Cardiff University in candidature for the degree of

**Doctor of Philosophy**

By

Peter Wright, BEng.

Division of Electronic Engineering

School of Engineering

**Cardiff University**

United Kingdom

September 2010

UMI Number: U585533

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U585533

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# **Abstract**

The research work presented in this thesis sets out to investigate improvements to the power amplifier design cycle through the use of recently developed radio-frequency waveform measurement and characterisation systems. One key objective of this work is to improve the overall efficiency of the modern wireless communication system by focusing on the radio-frequency power amplifier stage. More specifically, the direct utilisation of waveform-engineering techniques in the development of methodologies for the design and realisation of efficiency enhanced radio-frequency power amplifiers was targeted.

In developing these power amplifier design methodologies, work has also led to significant advancements into the possibilities of 'first-pass-design' success. Through the direct import of captured waveform data into a computer-aided design environment, along with efficiency-optimised multi-harmonic and intermediate-frequency impedance information, a stable and highly efficient power amplifier has been realised. This direct implementation of waveform measurements completely by-passes any involvement with potentially unreliable nonlinear device models. Hence this has eliminated the need for multiple iterations of matching networks, resulting in a dramatically more time-efficient design process.

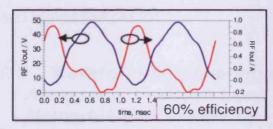

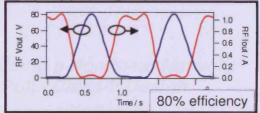

Waveform-engineering-based designs completed in this research have been demonstrated with both very high-efficiency (70-80%), narrowband modes of operation, as well as a high-efficiency (60-70%) broadband mode covering almost an octave bandwidth. All designs throughout have been realised as prototype power amplifiers.

# **Key Contributions**

**Contribution 1:** Development of a novel power amplifier design methodology for achieving record high (up to 84%) efficient modes of device operation in a packaged gallium nitride power transistor.

**Contribution 2:** Right-first-time realisation of very high-efficiency power amplifier prototypes from direct import and utilisation of optimised waveform measurement data in a computer-aided design environment.

**Contribution 3:** Novel investigation, experimentation and practical demonstration of the class-J mode of power amplifier for achieving high-efficiency device operation across more than 50% relative bandwidth.

**Contribution 4:** Overall, furthered research by providing investigations and results which continue to validate 'waveform-engineering' as a useable technique for designing and realising performance-optimised radio-frequency power amplifiers for wireless communications.

# **Acknowledgments**

I would like to thank my supervisor Prof. Johannes Benedikt for his fully committed supervision during my research work. His motivation and close, keen interest in my work gave me the continuing drive throughout this project, for which I am grateful. It has been a privilege also to be supported by Prof. Paul Tasker and Prof. Steve Cripps, and special "thanks" must go to them for their enthusiastic co-operation in such a complex and technical subject area.

I would also like to thank my industrial sponsor Milmega Ltd., Isle of Wight, UK for their support of my research, in particular Pat Moore, Mark Bloom, John Symonds and Andy Koz during my placement periods, guiding and enabling me to experience first hand the industrial-side to radio-frequency power amplifier design and manufacture. The Engineering and Physical Sciences Research Council (EPSRC), and CREE Inc. must also be acknowledged for their contributions during the course of my research.

Whilst working at the Centre for High Frequency Engineering at Cardiff University I have made several good friends, making the tougher times much more bearable, and the easier times thoroughly enjoyable. Here I would like especially to thank Simon Woodington, Chris Roff, Tudor Williams and Aamir Sheikh. Dr. Jonathan Lees has also been a continued source of support and enthusiasm right from the outset of beginning my PhD.

Finally I would like to express a special "thank you" to my family, and all of my friends outside of university; for all of their support and encouragement. My mother and father especially, who have been only too willing to help where they could and have always been there for me when I needed them most.

# **List of Publications**

## **First-Author Conference Papers:**

- P. Wright, J. Lees, P. J. Tasker and J. Benedikt, "GaN Power Transistors in Narrow and Wide Bandwidth Applications", 2008 IET Wideband Receivers & Components Conference, London, UK, May 2008.

- P. Wright, C. Roff, T. Williams, J. Lees, J. Benedikt, and P. J. Tasker, "RF Power Amplifier Design for High Efficiency Applications", 2008 SPIE Europe: Security & Defence Conference, Cardiff, UK, September 2008.

- 3. P. Wright, A. Sheikh, C. Roff, P. J. Tasker, J. Benedikt, "Highly efficient operation modes in GaN power transistors delivering upwards of 81% efficiency and 12W output power," IEEE MTT-S 2008 International Microwave Symposium Digest, pp. 1147-1150, Atlanta, GA, USA, 14-19 June 2008.

- P. Wright, J. Lees, P. J. Tasker, J. Benedikt, S. C. Cripps, "An Efficient, linear, broadband class-J-mode PA realised using waveform engineering," IEEE MTT-S 2009 International Microwave Symposium Digest, pp. 653-656, Boston, MA, USA, 7-12 June 2009.

## **First-Author Transactions Paper:**

P. Wright, J. Lees, P. J. Tasker, J. Benedikt, S. C. Cripps, "A Methodology for Realizing High Efficiency Class-J in a Linear and Broadband PA," IEEE Transactions on Microwave Theory and Techniques, Volume 57, Issue 12, pp. 3196-3204, December 2009.

#### **Other Papers:**

- S. Bensmida, K. Morris, J. Lees, P. Wright, J. Benedikt, P. J. Tasker, M. Beach, J. McGeehan, "Power Amplifier Memory-Less Pre-Distortion for 3GPP LTE Application", IEEE European Microwave Conference, pp. 1433-1436, 29 September-1 October 2009.

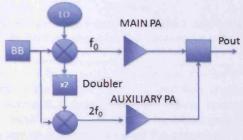

- A. Al-Muhaisen, P. Wright, J. Lees, P. J. Tasker, S. C. Cripps, J. Benedikt, "Novel Wide Band High-Efficiency Active Harmonic Injection Power Amplifier Concept," IEEE MTT-S 2010 International Microwave Symposium Digest, pp. 664-667, Anaheim, CA, USA, May 2010.

## Other Achievements During PhD Course:

Runner-up in the IEEE MTT-5 Student High Efficiency Power Amplifier Design Competition at the International Microwave Symposium 2008, Atlanta, GA, USA. - Measured PAE of 73.01%.

Winner of the IEEE MTT-S Student Paper Competition at the International Microwave Symposium 2009, Boston, MA, USA, for paper entitled: "An efficient, linear, broadband class-J-mode PA realised using waveform engineering."

# **List of Symbols and Abbreviations**

A, mA - Amperes, milli-Amperes

ACP - Adjacent Channel Power

ACPR - Adjacent Channel Power Rejection

ADS - Advanced Design System

AM - Amplitude Modulation

AM-PM - Amplitude-Modulation-to-Phase-Modulation

Avg. Eff./Pout - Average Efficiency/Output Power

BER - Bit Error Rate

C - Capacitance

c - Speed of Light in a Vacuum

CAD - Computer-Aided Design

CF - Centre Frequency

Class-F<sup>-1</sup> - Inverse Class-F

CW - Continuous Wave

d - Dielectric Thickness

dB - Decibels

dBc - Decibels (reference to carrier power)

dBm - Decibels (reference to 1mW)

DC - Direct Current

DUT - Device-Under-Test

ECM - Environment Climate Monitoring

Eq - Energy Gap

eV - Electron Volts

**EVM** - Environment Climate Monitoring

F, pF - Farads, pico-Farads

FET - Field Effect Transistor

Freq., f - Frequency

GaAs - Gallium Arsenide

GaN - Gallium Nitride

H, mH - Henrys, milli-Henrys

Hz, GHz - Hertz, Giga-Hertz

I. i - Current

I<sub>da</sub> - Quiescent Drain Current

I<sub>dss</sub> - Saturation Drain-Source Current

Igen -Plane - Current-Generator Plane

IM - Inter-modulation

j - Denotes the imaginary component of a complex impedance

k<sub>0</sub> - Wave Number

L - Inductance

LDMOS - Laterally Diffused Metal Oxide Semi-conductor

LP - Load-Pull

m, µm - metres, micro-metres

MAG - Maximum Available Gain

NL - Nonlinear

P - Power

P1dB - Output power at 1dB gain compression

PA - Power Amplifier

PAE - Power-Added Efficiency

PAR - Peak-to-Average Ratio

pHEMT, HEMT - Pseudomorphic High Electron Mobility Transistor

PUF - Power Utilisation Factor

R - Resistance

RF - Radio Frequency

S-parameters - Scattering Parameters

Si - Silicon

SiC - Silicon Carbide

TMM® - Thermoset Microwave Laminates

TRL - Thru, Reflect, Line

UAV - Unmanned Aerial Vehicle

V, v - Voltage/Volts

VNA - Vector Network Analyser

W - Transmission-line Width

W. mW - Watts, milli-Watts

WCDMA - Wideband Code Division Multiple Access

X - Reactance

Z - Impedance

ε<sub>r</sub> - Relative Dielectric Constant

ε<sub>e</sub> - Effective Dielectric Constant

η – Efficiency

Ø - Electrical Length

Γ, ρ – Reflection Coefficient

$\Omega$  – Ohms

# **Thesis Table of Contents**

|             | ı                                                                                                              | Page  |

|-------------|----------------------------------------------------------------------------------------------------------------|-------|

| Declaration | on                                                                                                             | i     |

| Abstract.   |                                                                                                                | ii    |

| Key Cont    | ributions                                                                                                      | iii   |

| Acknowle    | edgments                                                                                                       | iv    |

| List of Pu  | blications                                                                                                     | V     |

| List of Sy  | mbols and Abbreviations                                                                                        | .viii |

| Thesis Ta   | able of Contents                                                                                               | Х     |

|             |                                                                                                                |       |

| Chapter 1   | . Introduction                                                                                                 | _ 1   |

| 1.1         | RF Power Amplifiers for Wireless Communications                                                                | 1     |

| 1.2         | Research Objective - Novel Development Cycle<br>Methodologies for Efficiency Enhancement of RFPAs              | 2     |

| 1.3         | Current PA Design Approaches Used in Industry                                                                  | 4     |

| 1.4         | Waveform-Engineering on Power Transistors for the<br>Development of High-Efficiency PA Design<br>Methodologies | 5     |

| 1.5         | Broadband Waveform Measurements for Performance Verification                                                   | 7     |

| 1.6         | Device Technology Potential Applied to PA Design                                                               | 8     |

| 1.7         | Objectives and Thesis Synopsis                                                                                 | 9     |

| 1.8         | References                                                                                                     | 12    |

| Chapter 2. | . Literature Review                                                                                                                                                                                                                                                                                                                                                                 | 14  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                        | 14  |

| 2.2        | Existing PA Design and Realisation Methods and Associated Design Cycle Problems  2.2.1 Basic Passive Matching Network Design Principles  2.2.2 PA Design Based Around S-Parameter Measurements for the Active Device  2.2.3 Nonlinear PA Design for Optimising Absolute Performance Measures  2.2.4 Waveform-Based PA Designs and the Utilisation of Nonlinear Device Models in CAD | 15  |

| 2.3        | Waveform-Engineering Using a Nonlinear Network Analyser with Active Load-Pull - Class-F Design Methodology Case-Study 2.3.1 A Waveform Measurement System for Enabling Waveform-Engineering 2.3.2 Class-F Design Methodology Case-Study                                                                                                                                             | 24  |

| 2.4        | GaN Device Technology and Applications Within PA Design for Wireless Communications 2.4.1 GaN Compared with GaAs and Si LDMOS 2.4.2 Current Applications of GaN Device Technology in RFPAs                                                                                                                                                                                          | 32  |

| 2.5        | Efficiency-Enhancing PA Modes for the Basis of Novel Waveform-Engineering Design Methodologies 2.5.1 The Inverse Class-F Mode of Power Amplifier 2.5.2 Class-J: A Potential for High-Efficiency, Linear and Broadband PAs                                                                                                                                                           | 35  |

| 2.6        | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                     | 39  |

| 2.7        | References                                                                                                                                                                                                                                                                                                                                                                          | 41  |

| Chapter 3. | . High Power Waveform-Engineering-Based<br>High-Efficiency PA Design                                                                                                                                                                                                                                                                                                                | _48 |

| 3.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                        | 48  |

| 3.2        | Measuring High Power Packaged Devices 3.2.1 Device Stability Analysis 3.2.2 Understanding the Device Waveforms                                                                                                                                                                                                                                                                      | 50  |

| 3.3        | Inverse Class-F Theoretical Performance Prediction                                                                                                                                                                                                                                                                                                                                  | 56  |

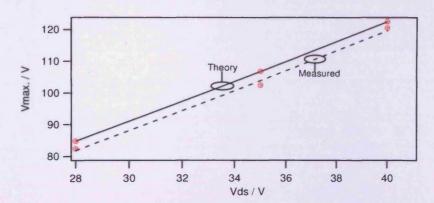

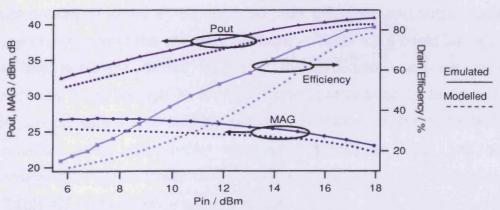

| 3.5.1 General Analysis of Emulated Performance 3.5.2 Class-F Mode Comparison  3.6 Scaling the High-Efficiency PA Design Methodology 3.6.1 High-Efficiency Design at 2.1GHz 3.6.2 Scaling Performance with Increased Drain Voltage 3.6.3 Conclusions on Scalability of the Presented Methodology  3.7 Chapter Summary 3.8 References  Chapter 4. Use of Optimised Waveform Measurement Data for PA Prototyping  4.1 Introduction  4.2 Use of Measurement Data & CAD for PA Prototyping 4.2.1 Collating the required harmonic impedance environment information 4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD 4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA 4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching 4.3.2 Implementation of CAD for Realisation – Input Matching 4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance 4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-FPA | 3.4        | 3.4.1           | Practical Implementation at 0.9GHz The Final Optimised Design                                            | 58   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|----------------------------------------------------------------------------------------------------------|------|

| 3.6.1 High-Efficiency Design at 2.1GHz 3.6.2 Scaling Performance with Increased Drain Voltage 3.6.3 Conclusions on Scalability of the Presented Methodology 3.7 Chapter Summary 3.8 References  Chapter 4. Use of Optimised Waveform Measurement Data for PA Prototyping 4.1 Introduction  4.2 Use of Measurement Data & CAD for PA Prototyping 4.2.1 Collating the required harmonic impedance environment information 4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD 4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA 4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching 4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance 4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                   | 3.5        | 3.5.1           | General Analysis of Emulated Performance                                                                 | 60   |

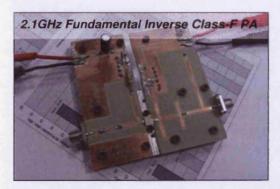

| Methodology  3.7 Chapter Summary  3.8 References  7.0  Chapter 4. Use of Optimised Waveform Measurement Data for PA Prototyping  4.1 Introduction  4.2 Use of Measurement Data & CAD for PA Prototyping  4.2.1 Collating the required harmonic impedance environment information  4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD  4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA  4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching  4.3.2 Implementation of CAD for Realisation – Input Matching  4.3.3 Initial results of PA performance  4.4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs  4.4.1 Initial results of PA performance  4.4.2 Comparison between emulated design and realised PA  4.4.3 Initial realisation conclusions  4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems  4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                       | 3.6        | 3.6.1           | High-Efficiency Design at 2.1GHz Scaling Performance with Increased Drain                                | 67   |

| Chapter 4. Use of Optimised Waveform Measurement Data for PA Prototyping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | 3.6.3           |                                                                                                          |      |

| Chapter 4. Use of Optimised Waveform Measurement Data for PA Prototyping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.7        | Chapte          | er Summary                                                                                               | 75   |

| 4.1 Introduction  4.2 Use of Measurement Data & CAD for PA Prototyping 4.2.1 Collating the required harmonic impedance environment information  4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD  4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA  4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching  4.3.2 Implementation of CAD for Realisation – Input Matching  4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA  4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems  4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                       | 3.8        | Refere          | ences                                                                                                    | 76   |

| 4.2 Use of Measurement Data & CAD for PA Prototyping 4.2.1 Collating the required harmonic impedance environment information 4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD 4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA 4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching 4.3.2 Implementation of CAD for Realisation – Input Matching  4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapter 4. |                 | -                                                                                                        | _ 78 |

| 4.2.1 Collating the required harmonic impedance environment information 4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD 4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA 4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching 4.3.2 Implementation of CAD for Realisation – Input Matching  4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.1        | Introdu         | uction                                                                                                   | 78   |

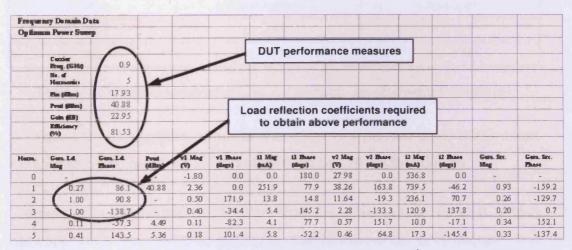

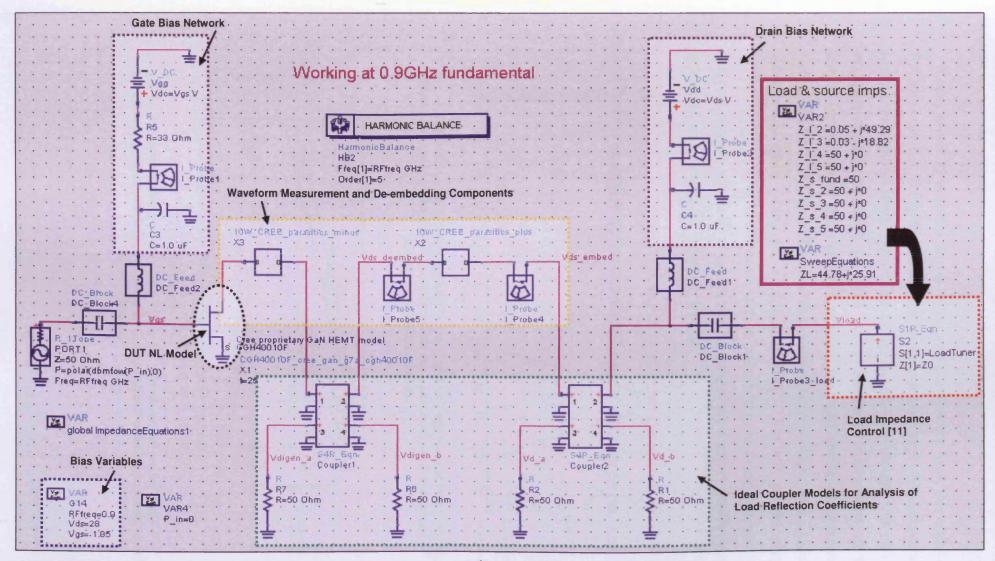

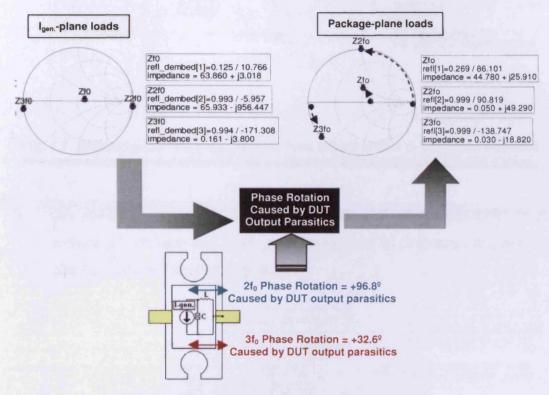

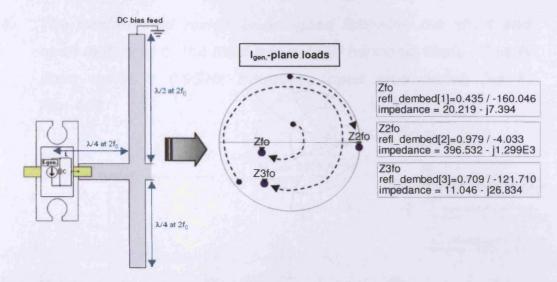

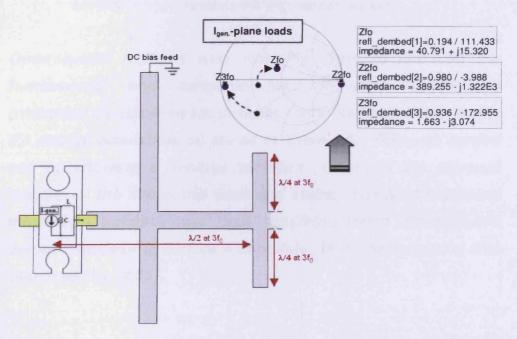

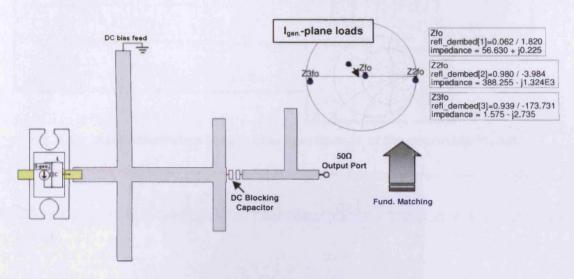

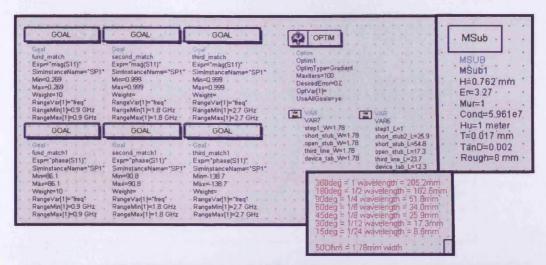

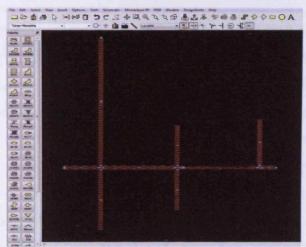

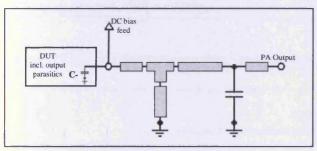

| 4.2.2 Applying optimum impedance environment to device manufacturer's model in CAD 4.2.3 Setting the goals for the required passive matching network  4.3 Right-First-Time Realisation of a Very High-Efficiency Complex PA 4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching 4.3.2 Implementation of CAD for Realisation – Input Matching  4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.2        |                 | Collating the required harmonic impedance                                                                | 80   |

| Complex PA  4.3.1 Implementation of CAD for Realisation – Output Multi-Harmonic Matching  4.3.2 Implementation of CAD for Realisation – Input Matching  4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs  4.4.1 Initial results of PA performance  4.4.2 Comparison between emulated design and realised PA  4.4.3 Initial realisation conclusions  4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems  4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                 | device manufacturer's model in CAD Setting the goals for the required passive                            |      |

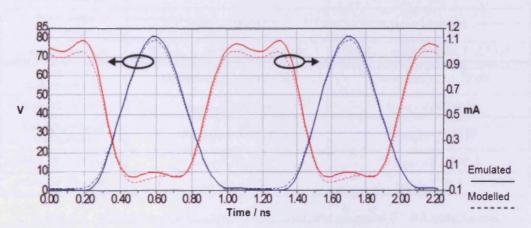

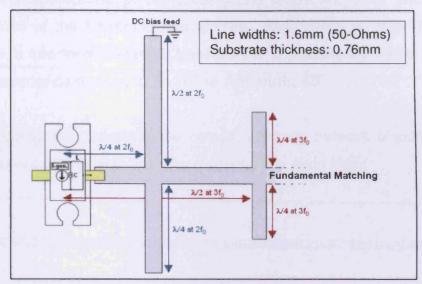

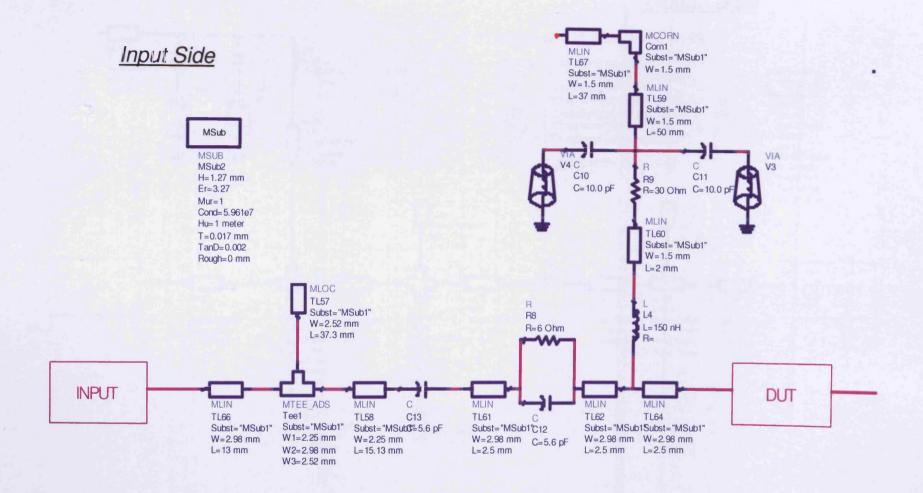

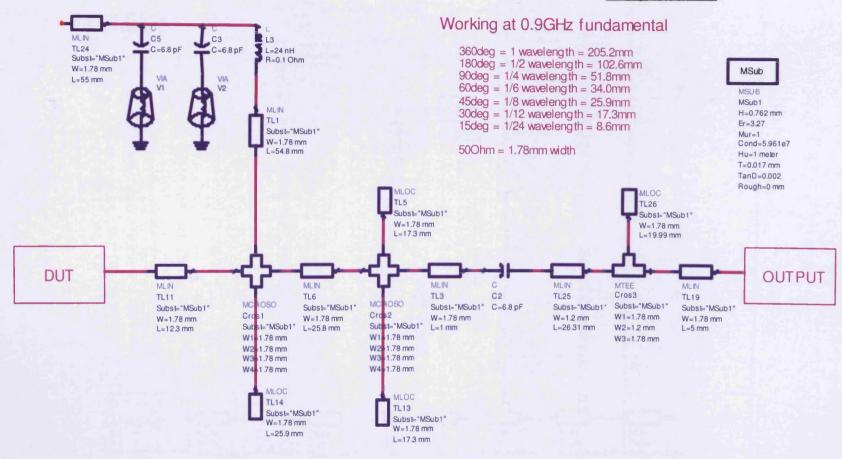

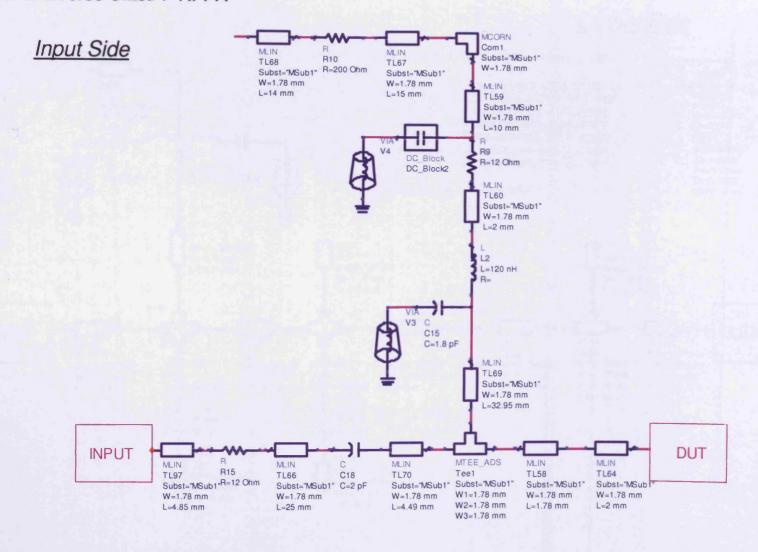

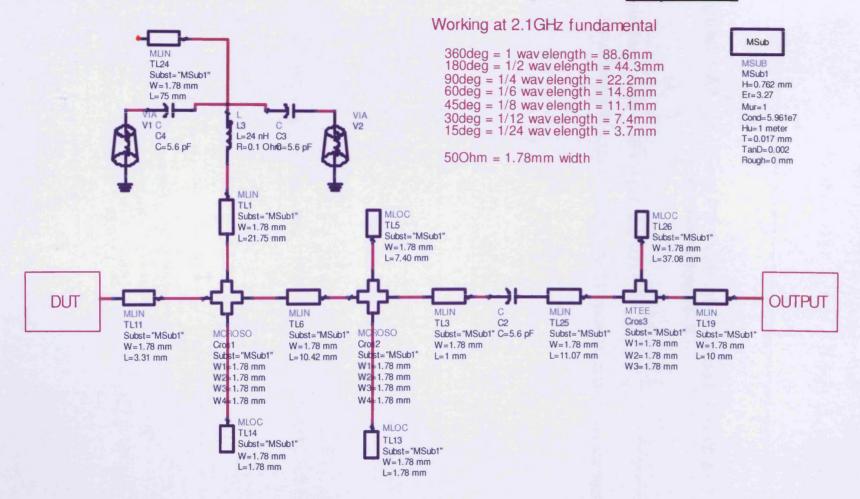

| 4.4 Prototype PA Performance Characterisation and Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.3        | Compl<br>4.3.1  | lex PA Implementation of CAD for Realisation – Output Multi-Harmonic Matching                            | 88   |

| Analysis - 0.9GHz and 2.1GHz Designs 4.4.1 Initial results of PA performance 4.4.2 Comparison between emulated design and realised PA 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | 4.3.2           | •                                                                                                        |      |

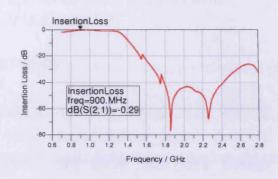

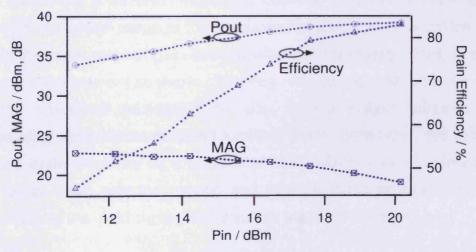

| 4.4.3 Initial realisation conclusions 4.4.4 Efficiency-Bandwidth of PA Performance  4.5 Linearity Characterisation and Applicability to Wireless Communications Systems  4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.4        | Analys<br>4.4.1 | sis - 0.9GHz and 2.1GHz Designs Initial results of PA performance Comparison between emulated design and | 100  |

| Wireless Communications Systems 10 4.5.1 Two-tone linearity performance of realised very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                 | Initial realisation conclusions                                                                          |      |

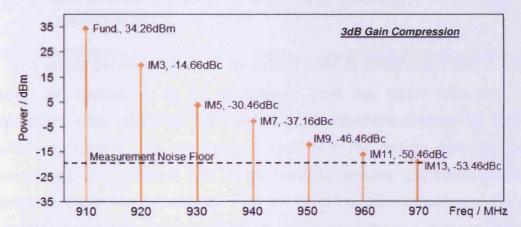

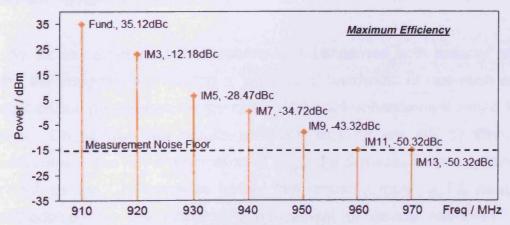

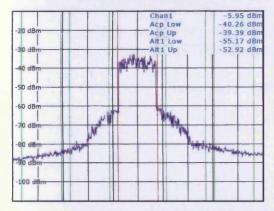

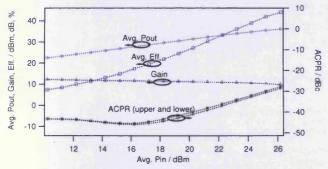

| very high-efficiency inverse class-F PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.5        | Wirele          | ss Communications Systems                                                                                | 109  |

| communications system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                 | very high-efficiency inverse class-F PA Usefulness of design in a modern wireless                        |      |

| 4.6        | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                   | 113        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.7        | References                                                                                                                                                                                                                                                                                                                                                                                                        | 114        |

| Chapter 5. | Extending High-Efficiency, Waveform-<br>Engineered PA Design Towards Broadband<br>Applications                                                                                                                                                                                                                                                                                                                    | 116        |

| 5.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                      | 116        |

| 5.2        | Broadband High-Efficiency With Class-J Mode of PA 5.2.1 Class-J Harmonic Load Terminations 5.2.2 Waveform-Engineering Very High-Efficiency Class-J Operation in a GaN HEMT                                                                                                                                                                                                                                        | 118        |

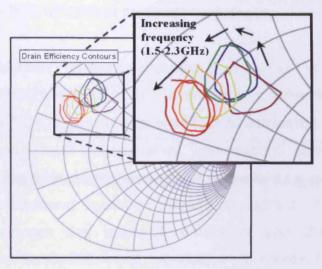

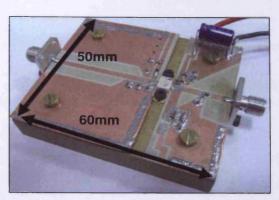

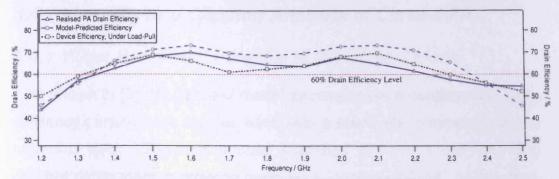

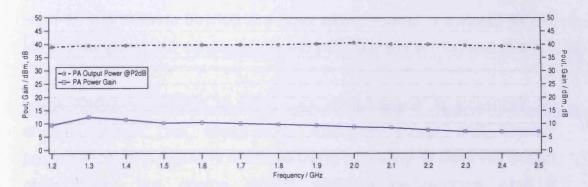

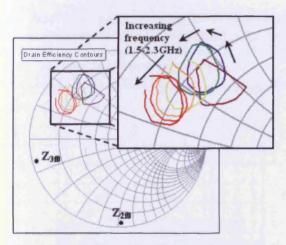

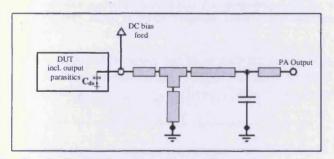

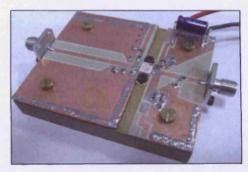

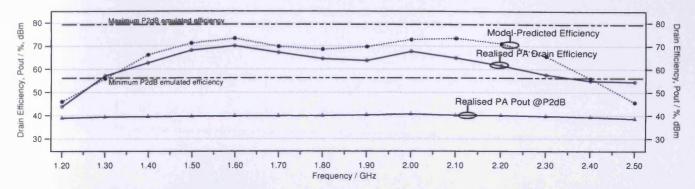

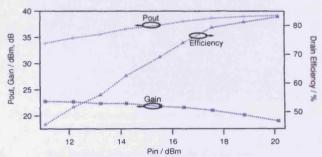

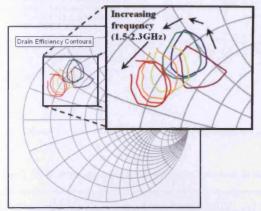

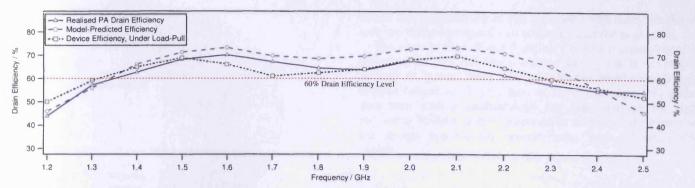

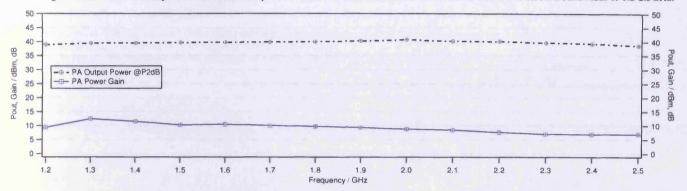

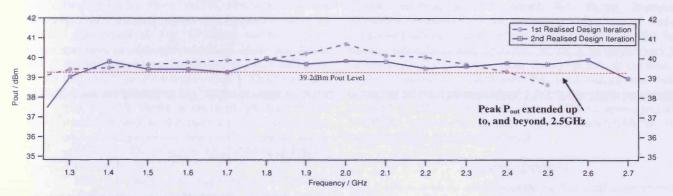

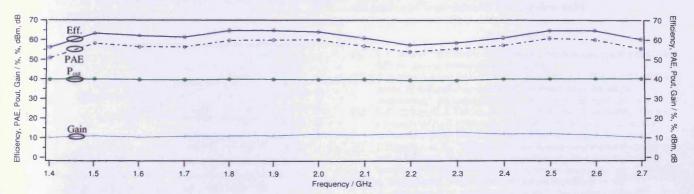

| 5.3        | Broadband, Linear Class-J PA Design Using Waveform Measurements and Multi-Harmonic Active Load-Pull 5.3.1 Broadband Measurements and PA Realisation 5.3.2 Realised Class-J Performance Results - Efficienc and Output Power vs. Frequency 5.3.3 Analysis of Measured PA Performance                                                                                                                               | 122        |

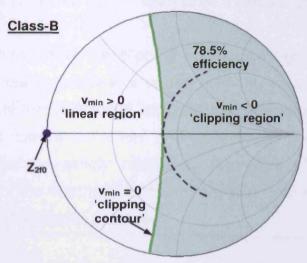

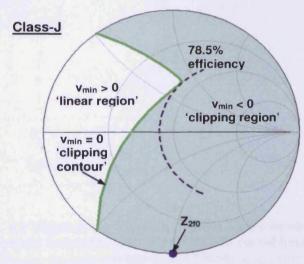

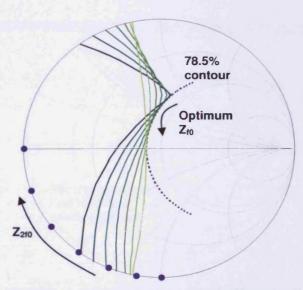

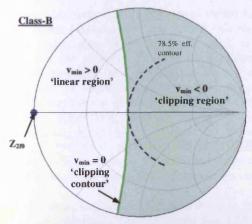

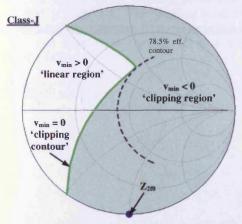

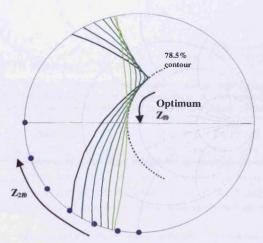

| 5.4        | <ul> <li>Linearity and Clipping Analysis of Class-J PA</li> <li>5.4.1 Wider Bandwidth Potential of the Class-J Mode</li> <li>5.4.2 Use of 'Clipping Contours' for Quasi-Linear Designormal States of Class-J Mode in High Pown Devices - Effect of Second Harmonic (LP measurements)</li> <li>5.4.4 Practical Verification of Class-J Mode in High Pown Devices - Improved Class-J Design Space LP Res</li> </ul> | ver<br>ver |

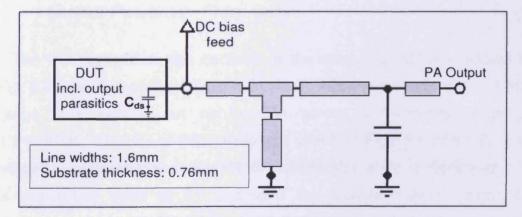

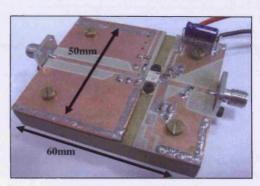

| 5.5        | An Enhanced Design Following Extended Theory 5.5.1 Re-designing the Class-J Output Matching Netwo 5.5.2 Measured PA Performance following Improved Output Matching Network Design                                                                                                                                                                                                                                 | 133<br>ork |

| 5.6        | Input Matching and Effect on PA Performance                                                                                                                                                                                                                                                                                                                                                                       | 135        |

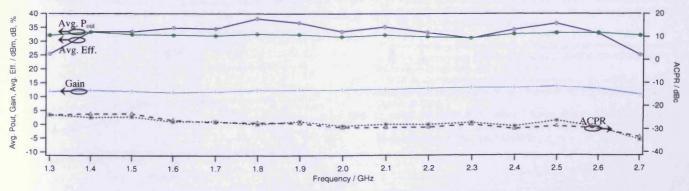

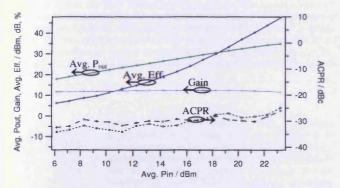

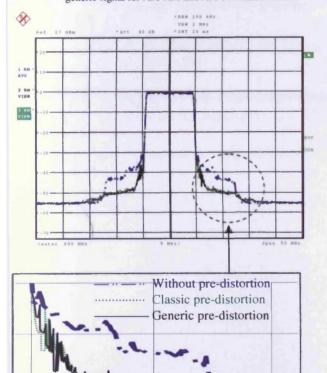

| 5.7        | Linearity and Predistortability of Class-J PA                                                                                                                                                                                                                                                                                                                                                                     |            |

| 5.8        | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                   | 139        |

| 5.9        | References                                                                                                                                                                                                                                                                                                                                                                                                        | 140        |

| Chapter 6. | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                       | 142        |

| Chapt       | er 7. Future Work                                                                       | 146          |

|-------------|-----------------------------------------------------------------------------------------|--------------|

| -           | 7.1 Future Work Extensions                                                              | 146          |

| -           | 7.2 References                                                                          | 149          |

| Appei       | ndices                                                                                  |              |

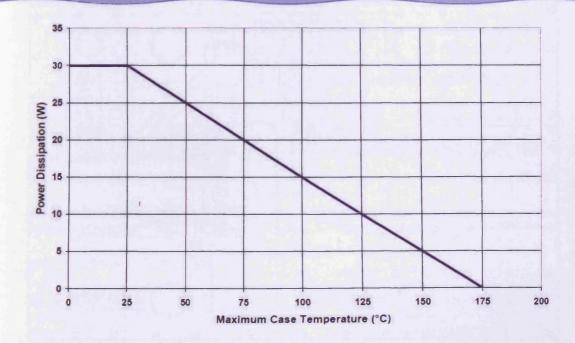

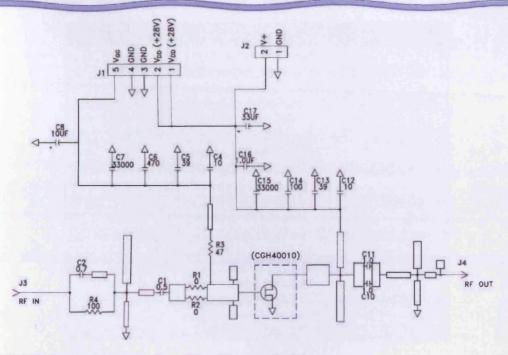

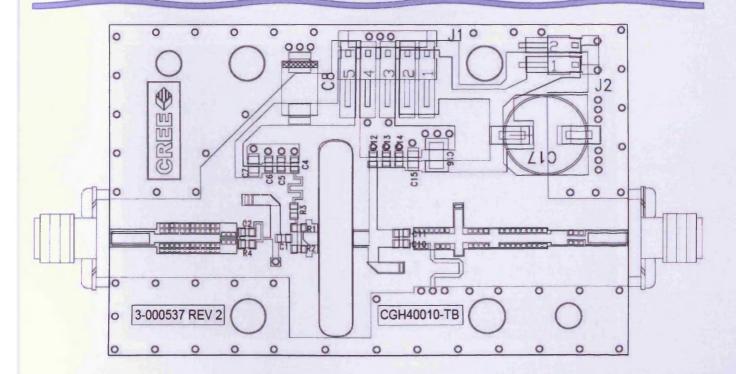

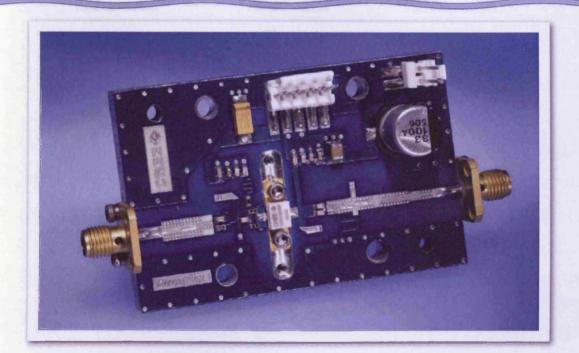

| <b>A</b> 1. | CREE CGH40010F 10W gallium nitride HEMT datasheet.                                      |              |

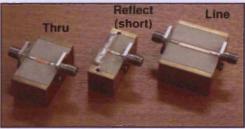

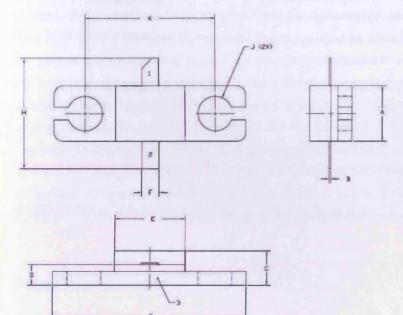

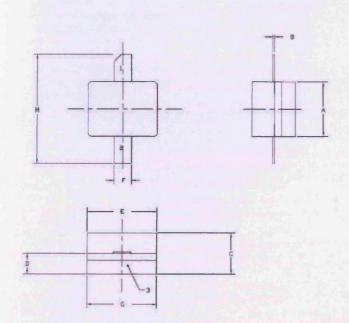

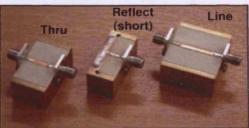

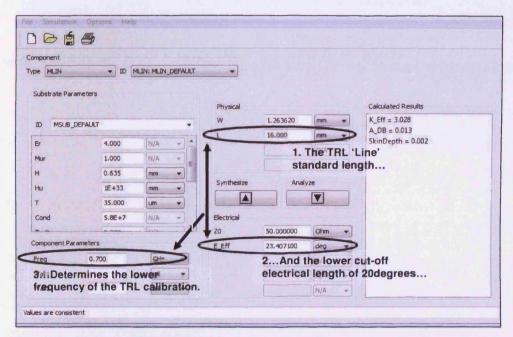

| A2.         | TRL calibration notes.                                                                  |              |

| <b>A3</b> . | Device stability analysis procedures directly from waveform-neased S-parameter capture. | neasurement- |

| <b>A4</b> . | Implementation of de-embedding networks in CAD.                                         |              |

| <b>A</b> 5. | ADS Line Calc. example.                                                                 |              |

| <b>A</b> 6. | Final PA schematics, circuit layouts and components (inverse                            | e class-F).  |

| <b>A</b> 7. | Final PA schematics, circuit layouts and components (class-                             | J).          |

| List o      | f Publications                                                                          |              |

# **Chapter 1. Introduction**

## 1.1 RF Power Amplifiers for Wireless Communications

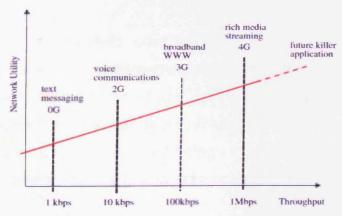

With worldwide mobile communications subscribers ever on the increase, and ongoing advancements in communications services available to these users, the drive for improving the overall efficiency of the modern-day wireless communication system has never been greater. Such industry motivations for power-efficient or 'greener' systems include the demand for increased functionality of mobile handset devices. This directly leads to higher communication data rate requirements (Fig. 1.1) and all whilst maintaining a practical battery life expectancy within the wireless handset. The relatively recent introduction of 'smart-phones' and commercial 3G (3<sup>rd</sup> generation) networks has enabled users to now access broadband internet and basic streaming services whilst on the move - but ultimately at a high financial cost to the network provider and, hence, end subscriber.

Fig. 1.1. Network utility to the user versus the achievable data throughput [1].

Drivers for improved power-efficiency not only come from the mobile handset market, but also from the network provider infrastructures, where the base-station costs are responsible for a very high percentage of the overall communication system cost as a whole. Military communications are also prone to size, weight and portability issues with the added stringent reliability requirements having to be met, above those of commercial handsets.

Ultimately, therefore, it is the power-hungry RFPA (radio-frequency power amplifier) stage which determines the major considerations in terms of efficiency; Whether this be driven by the required portability of mobile wireless handsets containing lower-power amplifiers, the military necessity for highly reliable and durable front-line communications, or the cost of cooling requirements for the very-highpower amplifiers present in fixed base-stations. It is this RFPA (or PA) stage that potentially holds the most gains for efficiency enhancement of the modern wireless communications system.

# 1.2 Research Objective - Novel Development Cycle Methodologies for Efficiency Enhancement of RFPAs

In the age of CAD (computer-aided design) environments, the process of PA design has become potentially much more time-efficient. As a part of this computer-aided design process, nonlinear device models for use in the simulation environment are now widely implemented in PA designs [2-3]. However this method relies very heavily on the accuracy of the device models used. Any discrepancies present in the more-difficult-to-model nonlinear characteristic of any device lead to the inherently time-consuming stage of the PA designers project of multiple design iterations. With new generation device technologies emerging continuously, a means of removing this costly and time-consuming stage of PA design

would be a welcome development. On many occasions the requirement for highly accurate device models for these corresponding new transistor technologies is not met.

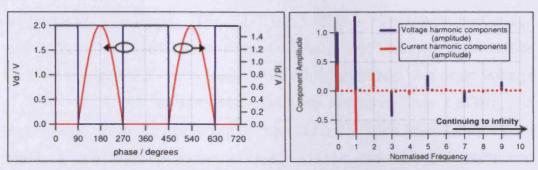

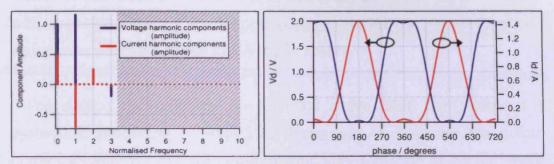

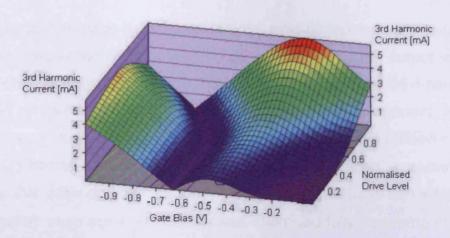

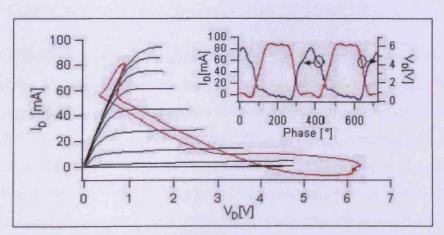

In the majority of RF transmitters the PA usually operates well below a 50% conversion of DC (direct current) to RF power [4]. The total system efficiency will be further reduced by dealing with the DC power not converted to RF power, but dissipated as heat. This situation persists despite the large number of known PA architectures - as discussed by Cripps, Rhodes, Raab, Grebennikov [4-9] - capable of significantly higher average efficiencies. However, these enhanced PA modes of operation rely on an intricate interaction between the fundamental output power and harmonic loading making their design challenging as no design solutions currently exist that allow for this fully. Hence, despite the large number of mathematical descriptions for various highly efficient PA modes, the interesting practical implementations and observations are not being investigated due to the limited availability of waveform capture and combined load-pull measurement systems.

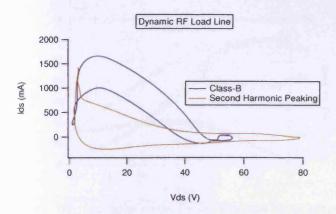

There is a direct need for device waveforms in order to establish procedures for designing and analysing complex PA modes. This therefore includes the need for multi-harmonic (hence, broadband) measurement capability in order to look at device interaction through the use of dynamic load-lines.

Nonlinear measurement solutions are now becoming more prevalent in the PA design industry [10-13]. Thus the availability of measured waveform data and waveform-shaping or 'engineering' techniques will also increase. The result of this trend will likely see a shift in nonlinear PA design techniques, towards systematic waveform-engineering. In order for these measurement systems to be leveraged to their full potential for PA design, a thorough understanding of the procedures involved in 'tuning' for high-efficiency in a nonlinear measurement system will be necessary.

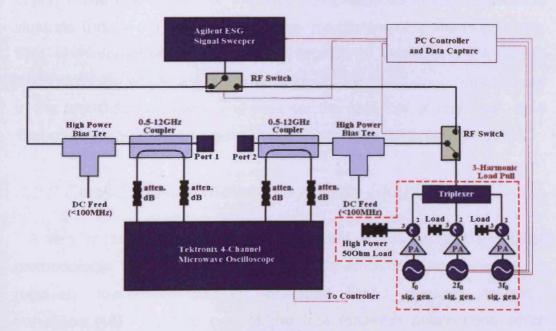

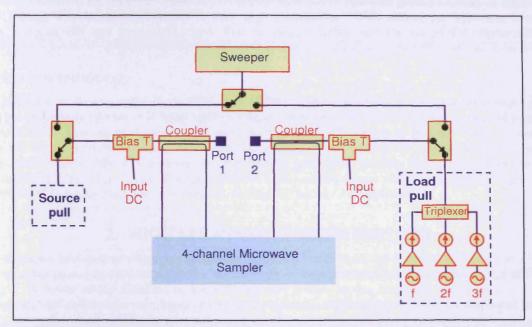

In response to this need, systematic procedures for developing working, high-efficiency PAs using waveform-engineering principles are investigated in this thesis. This research describes investigations set out to find solutions to the PA development cycle issues. Using a high power active load-pull waveform measurement system [10], for characterisation of high power packaged transistor devices, PA topologies can be accurately and precisely measured on actual device samples through engineering the output waveforms. A review of literature, in Chapter 2, specific to this area focuses on a very-high-efficiency class-F amplifier topology that has previously been emulated with on-wafer devices using waveform-engineering design techniques [14]. However, we are yet to see any waveform-engineered designs be followed through and translated directly to a realised amplifier. It is therefore the aim of this research to investigate novel design methodologies for efficiency enhanced high-power amplifiers using waveform-engineering techniques on packaged transistors. To make use of the captured data during the design of suitable matching networks, and develop working PA prototypes for application in the RF industry, is the next major objective.

# 1.3 Current PA Design Approaches Used in Industry

PA design processes take several forms with particular techniques adopted for each individual design specification and requirement. In modern RF communication PA design there has been an increased interest in high-efficiency mode approaches. This re-evaluation has

<sup>&</sup>lt;sup>1</sup> The term "*emulated*" has been used here, and will be throughout this thesis, to describe the use of active load-pull to present specific reflection coefficients to the DUT (device-under-test) in initiating a particular mode of operation in the DUT, without the use of passive matching.

become possible as additional circuit techniques such as digital predistortion and drain modulation have evolved which can be wrapped around PAs operating in these modes to enhance linearity and power back-off performance [4].

Such high-efficiency-mode PAs are commonly classified by the shape of their current and voltage waveforms [4] and denoted as 'complex' modes of operation, often requiring multi-harmonic impedance matching to obtain optimum performance levels. When designing in CAD, the additional harmonic impedance requirements add a further dimension to the level of required accuracy of the designers' device model. A design process, to allow for the rapid optimisation of multi-harmonic impedances in complex modes of RFPAs, requires a systematic strategy in order to overcome further time-consuming multi-iterative PA design.

Taking the design specification of efficiency as an example, the maximum efficiency performance of an active device in a given mode will only occur if the designed circuitry engineers the most efficient output current and voltage waveforms. Therefore, in order to best design for these modes it is highly advantageous to have access to the current and voltage waveforms at the active device terminals. So too the capability to relate circuit parameters to these engineered waveform shapes. This is where the simulation with device models in CAD falls down, and where waveform-engineering practices can hold their advantages.

## 1.4 Waveform-Engineering on Power Transistors for the Development of High-Efficiency PA Design Methodologies

RF waveform measurement and active load-pull systems previously described in [10-13] have been developed with the objective of being able

to accurately characterise transistor device samples in a variety of impedance environments, input drive and bias conditions. Since real samples of semiconductor wafers or packaged power transistors are characterised, one of the main attractions of these systems is the ability to obtain a true measure of performance from the active DUT (device-under-test) when it is set in the environment for which it is intended for a particular application.

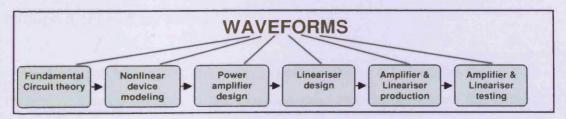

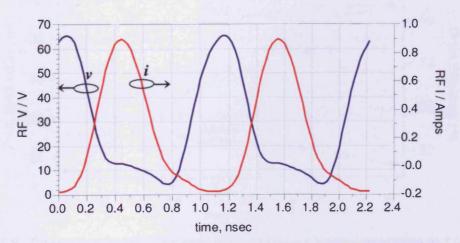

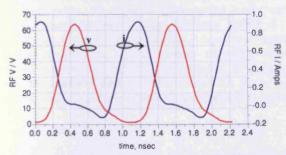

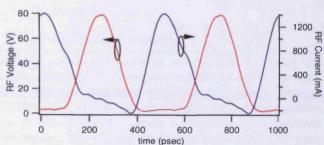

This research has made use of high power waveform measurements and active multi-harmonic load-pull to obtain and analyse RF current and voltage waveforms<sup>2</sup> from the DUT. This gives the designer the ability to 'see' how the device RF characteristics interact with the 'hard' or physical device current-voltage boundaries (DC I-Vs). More importantly, however, this waveform capture enables a powerful means of analysis and device performance manipulation, known as 'waveform-engineering' [15]. This concept is of key importance, underlying the research throughout this thesis by providing the unifying link between fundamental circuit theory, PA prototyping and final performance testing and verification [15].

Using a waveform-engineering design approach, the aim of this research was to investigate how parameters such as bandwidth, linearity, efficiency and power can all be compromised or traded-off in a single design according to the design requirement of the PA. In doing this it has been possible to make advancements in developing methodologies that have resulted in the efficiency optimisation and enhancement of RFPAs. Scalability of these design procedures in terms of frequency and drain voltage bias settings has also been shown.

Much of this research focuses on the use of packaged power

<sup>&</sup>lt;sup>2</sup> From now onwards, the plural use of the word "waveforms" alone in this thesis directly corresponds to the DUT current and/or voltage waveforms that are captured using the measurement system.

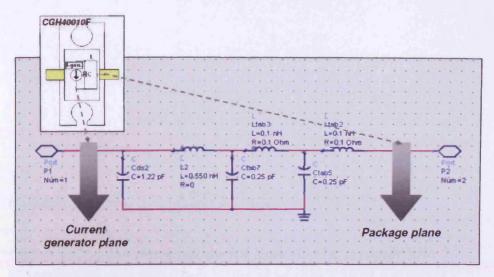

transistors, posing the question over the usefulness of the captured RF waveforms compared with the actual device performance occurring at the intrinsic device plane or 'current-generator plane' (I<sub>gen.</sub>-plane). In these cases the use of parasitic de-embedding has been stated and described [16] and has led to genuine comparisons with, and verifications of, the investigated PA mode theory. This has proved crucial when considering further in-depth analysis and investigation into complex PA modes.

Several prototype PAs have been realised from this research with first-pass-success demonstrated, clearly illustrating an advantage of waveform-engineering design processes for PA design. PA designs developed using the high power waveform measurement system have been followed through to realised PA prototypes for the first time, whilst displaying closely comparable performance to that initially emulated. As a means of obtaining near theoretical-optimum performance from devices, whilst considering the importance of "Watts-per-Dollar", clear improvements, above those previously presented, have been shown when applying the rapid design cycles developed in this research. For the purpose of interest, comparisons with the performance achieved with nonlinear models in CAD are also continuously made.

#### 1.5 Broadband Waveform Measurements for Performance Verification

Research into enhanced-efficiency PA design methodologies demands, by definition, the requirement for broadband frequency consideration. This is due to the requirements for harmonic content information within the DUT's output waveforms which needs to be engineered appropriately in order to limit the overlap in the output current and voltage waves, and thus limit the dissipated DC power [5, 14, 17]. In this research broadband measurement capability has enabled the development of a very-high-

efficiency class-F<sup>-1</sup> (inverse class-F) PA design methodology. Whilst this procedure employed three-harmonic load tuning, many more higher harmonics were able to be measured and analysed. This in fact has facilitated the suggested reasoning behind why a comparable three-harmonically optimised class-F PA design was less efficient.

Continuing this theme, the methodologies discussed previously were adapted for the development of a novel methodology for designing a class-J-mode PA [4, 6]. Broadband measurement capability has provided a means of not only developing the efficient and broadband PA design but also for testing of the built prototype amplifier. This in itself enables a means of performance verification and comparison with the class-J theory from which the initial design stemmed from.

The above are just two examples illustrating the benefit of broadband waveform measurement capability. Its novel use and crucial role, combined with the active multi-harmonic load-pull implemented throughout the research presented in this thesis, has demonstrated a means of furthering the PA development cycle.

# 1.6 Device Technology Potential Applied to PA Design

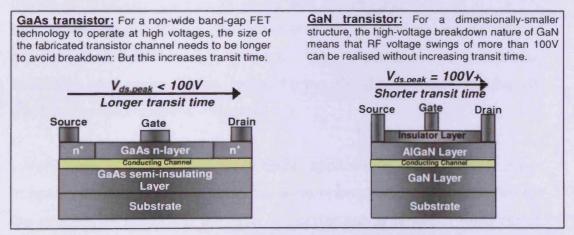

Choosing a device technology for its suitability to a particular application is a vital part of any PA design and design methodology. Previous works have demonstrated the performance degradation observed when a device with relatively low breakdown voltage rating was applied to a PA design with inherent high voltage peaking [18]. The root cause of the result in [18] could be clearly seen when the DUT output waveforms were observed, indicated by an increase in current during the peak in the output voltage waveform cycle. Following on from this result, the importance of selecting an appropriate device technology is

considered, and using waveform measurements this can be done more intuitively. Not only is this an important consideration in terms of device reliability, but when considering the Watts-per-Dollar criteria once again the importance of achieving a worthwhile return from devices is of paramount interest to the designer.

GaN (gallium nitride) transistor technology is used for the majority of the research presented in this thesis; a wide band-gap semiconductor technology enabling very high peak output voltage swings, and thus potentially high power and efficiencies, to be achieved [19]. Such an application of GaN is presented in **Chapter 3**, where a novel class-F<sup>-1</sup> design methodology based on a waveform-engineering approach has yielded not only a highly efficient PA, but one which also has a good output 'power-utilisation factor' (PUF) [4].

## 1.7 Objectives and Thesis Synopsis

This thesis is divided into three main sections. The first describes the development of a PA design methodology implementing waveformengineering for the specification of optimised, very highly efficient device operation. The next main section sees the implementation of the captured waveform measurement data from an emulated PA design, into a CAD environment for the realisation of matching network structures and an overall PA prototype. The third main section investigates a novel broadband PA design in which good efficiency, linearity and output power are also key specifications. This final main section draws on the all aspects of the research presented in the previous sections.

To summarise, **Chapter 2** presents a literature review of current-day, and most recent advancements in, PA design procedures. As a case study, a low-power, on-wafer class-F design in [14] is introduced and its

applicability to higher power packaged transistors also discussed. This chapter also describes in more detail the process of waveformengineering, the applicability of GaN to high power RF amplifiers, and begins to formulate ideas for class-F<sup>-1</sup> and class-J mode PA development by introducing these modes of operation as discussed in the literature.

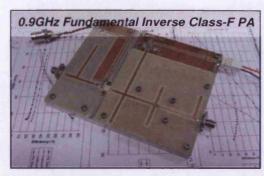

Chapter 3 begins the first main section of this research and presents a PA design methodology for achieving very high-efficiency device operation in a 10W GaN HEMT (high electron mobility transistor). The waveform-engineering-based procedure is explained and demonstrated at two fundamental frequencies; 0.9GHz and 2.1GHz. Verification of the obtained optimised performance is also detailed through the use of RF waveform analysis and comparisons to theoretically predicted figures. Stability analysis considerations are also presented in this chapter.

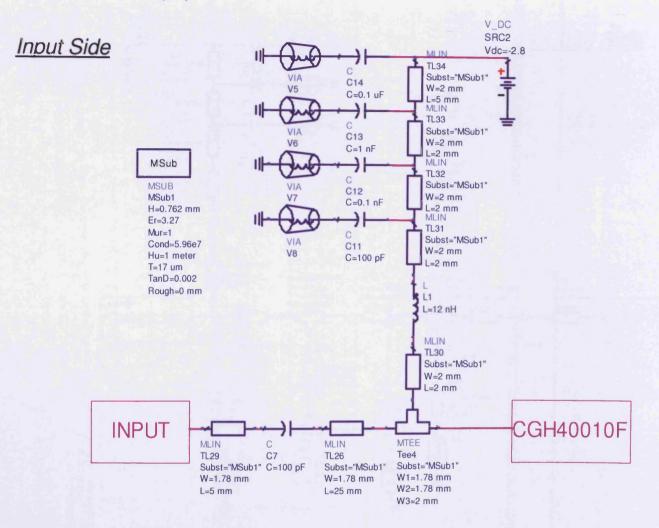

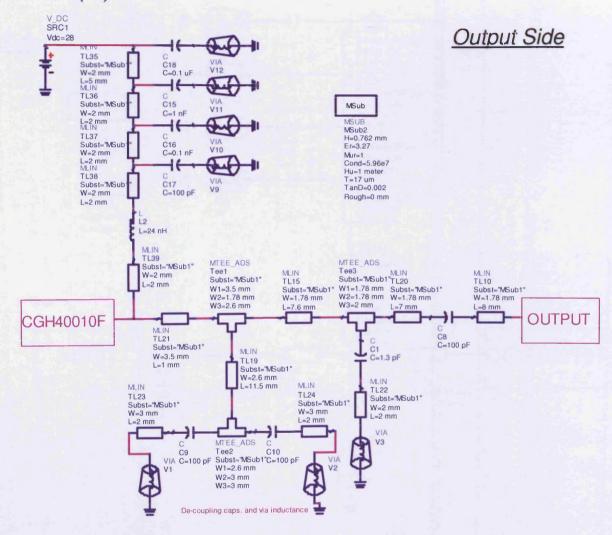

In **Chapter 4**, realisation of the PA prototype is initiated, making use of the measured waveform data obtained in Chapter 3 for import into a CAD environment. Here, direct use of the optimised performance results are implemented in the design of suitable input and output multi-harmonic matching networks in the form of microstrip layouts, enabling a right-first-time PA prototype to be realised. Comparison of the PA performance with the emulated design, and also nonlinear device model simulations, verify the first-pass-success that has been achieved here.

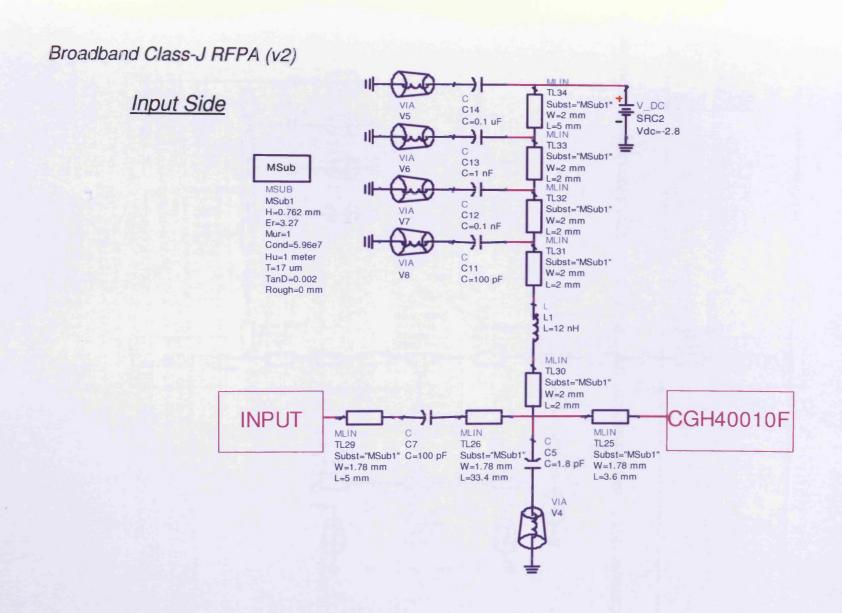

The third main part of this research begins in **Chapter 5**, and introduces the concept of the class-J mode of power amplifier and investigates its potential for broadband high-efficiency, whilst also maintaining good levels of linearity and output power. This developed design methodology is once again centred about the implementation of a high power waveform measurement system and active load-pull capability, and investigates the best level of efficiency achievable across

a 'significant' bandwidth (i.e. more than a 50% relative bandwidth). The class-J mode's suitability for this application is discussed. Drawing on extensive theoretical analysis of class-J, this chapter presents two prototype broadband PAs which have been realised around a GaN device.

**Chapter 6** describes the conclusions from this research and poses questions for discussion, while **Chapter 7** introduces potential future work which could see further improvements to the PA development cycle as an extension to the work in this thesis.

#### 1.8 References

- [1] J. Akhtman, L. Hanzo, "Power Versus Bandwidth Efficiency in Wireless Communication: The Economic Perspective," 2009 IEEE VTC'09 Fall, Anchorage, Alaska, USA, 20-23 September 2009.

- [2] M. C. Curras-Francos et al. "Experimental Demonstration and CAD Investigation of Class B HFET Transistor Operation at Microwave Frequencies," *Proceedings of the 28th IEEE European Microwave Conference*, pp. 1386-1388, Amsterdam, 1998.

- [3] P. Colantonio, F. Giannini, G. Leuzzi, E. Limiti, "Theoretical facet and experimental results of harmonic tuned PAs," *International Journal of RF and Microwave Computer-Aided Engineering*, Volume 13, Issue 6, pp. 459-472, 2003.

- [4] S. C. Cripps, RF Power Amplifiers for Wireless Communications, 2<sup>nd</sup> Edition, Artech House Publishers Inc., ISBN: 0-89006-989-1, 2006.

- [5] F. H. Raab, "Maximum efficiency and output of class-F power amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, Volume 49, Issue 6, pp.1162-1166, June 2001.

- [6] F. H. Raab, "Class-E, Class-C, and Class-F Power Amplifiers Based upon a Finite Number of Harmonics," *IEEE Transactions on Microwave Theory and Techniques*, Volume 49, Issue 8, pp. 1462-1468, August 2001.

- [7] J. D. Rhodes, "Output Universality in Maximum Efficiency Linear Power Amplifiers", *International Journal on Circuit Theory and Applications*, Volume 31, pp. 385-405, 2003.

- [8] A. Grebennikov, "RF and Microwave Power Amplifier Design," McGraw-Hill, ISBN: 9780071444934, 2004.

- [9] A. Grebennikov, N. O. Sokal, Switchmode RF Power Amplifiers, New York: Newnes, 2007.

- [10] J. Benedikt, R. Gaddi, P. J. Tasker, M. Goss, "High-power time-domain measurement system with active harmonic load-pull for high-efficiency base-station amplifier design," *IEEE Transactions on Microwave Theory and Techniques*, Volume 48, Issue 12, pp. 2617-2624, December 2000.

- [11] P. J. Tasker et al., "A vector corrected high power on-wafer measurement system with a frequency range for higher harmonics up to 40GHz," *Proceedings of the 24th European Microwave Conference*, pp. 1367-1372, 1994.

- [12] A. Ferrero, V. Teppati, "A complete measurement Test-Set for non-linear device characterization," *58th ARFTG Conference Digest-Fall*, Volume 40, pp. 1-3, November 2001.

- [13] G. Simpson, J. Horn, D. Gunyan, D. E. Root, "Load-pull + NVNA = enhanced X-parameters for PA designs with high mismatch and technology-independent large-signal device models," *72nd ARFTG Microwave Measurement Symposium 2008*, pp. 88-91, December 2008.

- [14] C. Roff, J. Benedikt, P. J. Tasker, "Design approach for realization of very high efficiency power amplifiers," *IEEE MTT-S International Microwave Symposium Digest*, pp. 143-146, June 2007.

- [15] P. J. Tasker, "Practical waveform engineering," *Microwave Magazine, IEEE*, Volume 10, Issue 7, pp. 65-76, December 2009.

- [16] A. Sheikh et al., "The Impact of System Impedance on the Characterization of High Power Devices," *Proceedings of the 37<sup>th</sup> European Microwave Conference*, pp. 949-952, October 2007.

- [17] Y. Y. Woo, Y. Yang and B. Kim, "Analysis and Experiments for High-Efficiency Class-F and Inverse Class-F Power Amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, Volume 54, Issue 5, pp. 1969-1974, May 2006.

- [18] A. Sheikh, C. Roff, J. Benedikt, P. J. Tasker, B. Noori, J. Wood, P. H. Aaen, "Peak class F and inverse class F drain efficiencies using Si LDMOS in a limited bandwidth design," *IEEE Microwave and Wireless Components Letters*, Volume 19, Issue 7, pp. 473-475, July 2009.

- [19] R. J. Trew, "Wide bandgap semiconductor transistors for microwave power amplifiers," *IEEE Microwave Magazine*, Volume 1, Issue 1, pp. 46-54, March 2000.

# **Chapter 2. Literature Review**

#### 2.1 Introduction

This review chapter presents a look at the currently utilised and most recent advancements in PA design procedures. A description of the process of waveform-engineering, the applicability of GaN in developing high-power RF amplifiers, and the formulation of ideas for class-F<sup>-1</sup> and class-J mode PA development following introduction of these modes of operation are discussed from the literature.

As highlighted in **Chapter 1** - and to be further revealed in detail within this chapter - there is a direct need for RF waveforms in order to establish procedures for designing and analysing complex PA modes. A wide-frequency measurement capability is thus in the forefront of requirements in order to look at DUT RF-dynamics/DC-boundary interactions in these complex modes. Such a measurement system is identified in this chapter, while a case-study covering a low-power, onwafer class-F design procedure (making use of active load-pull and waveform-engineering techniques synonymous with the aforementioned measurement set-up) is also detailed.

The aim of the research described in this thesis is to respond to the revealed need for systematic design procedures for high-efficiency, high-power amplifiers using RF waveform-engineering-based principles.

# 2.2 Existing PA Design and Realisation Methods and Associated Design Cycle Problems

#### 2.2.1 Basic Passive Matching Network Design Principles

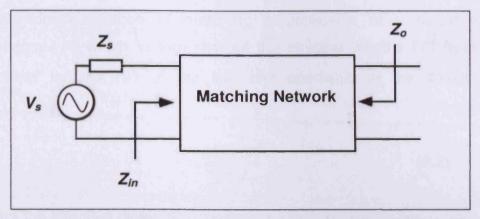

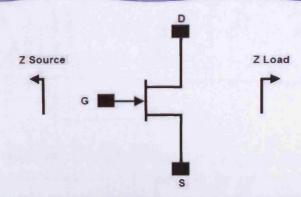

A standardisation for the impedance of most RF and microwave system equipment and apparatus was introduced in the 1930s when the development of microwave coaxial cables required a suitable trade-off between the power-carrying capability and the contributable losses of the resulting coaxial line [1]. It is therefore paramount that every stage in a modern  $50\Omega$  (Ohm)-standardised RF communications system closely follows and matches this standard characteristic impedance in order for RF power transfer from one stage to the next to be completed as efficiently as possible. This inevitably includes the power amplifier stage which, for example, occurs prior to the antenna stage where the wireless transmission of the RF signal takes place.

Several components however - such as the active device(s) in the PA stage - cannot necessarily meet this port impedance requirement directly as a result of their fabrication processes. It is thus the job of the PA designer in this situation to fabricate the necessary passive matching networks around the active device(s) in order to facilitate the efficient transfer of RF power from and to the preceding and subsequent stages respectively. This despite any present mismatch in port impedances between the DUT input/output impedance and the  $50\Omega$  standard.

Fig. 2.1 shows a simple example of the requirement for matching in order to facilitate the maximum transfer of power (Eq. 2.1 [2]) between a source impedance ( $Z_s$ ) of  $10+j25\Omega$  and a characteristic port impedance ( $Z_o$ ) of  $50\Omega$ . The 'j' term denotes the imaginary component of the complex impedance.

Fig. 2.1. Introducing a matching network to facilitate maximum power transfer between the mismatched source and  $50\Omega$  port impedances.

Maximum power transferred [2]:

$$P_{\text{max}} = \frac{1}{2} |V_s|^2 \cdot \frac{1}{4 \cdot \Re(Z_s)} \text{ when; } Z_{in} = Z_s^*$$

(2.1)

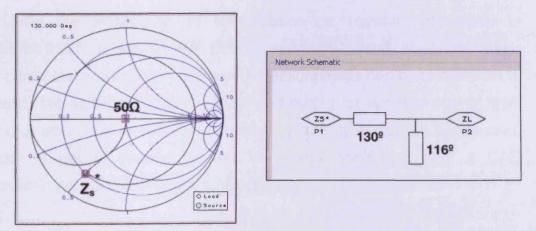

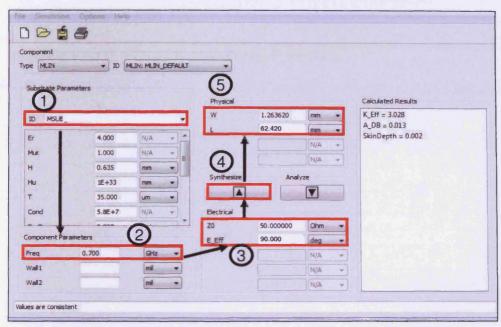

The implementation of a simple open-stub microstrip transmission-line matching network, to meet the requirement of the mismatched source and  $50\Omega$  port impedance, is shown in Fig. 2.2. This was achieved using the Smith-Chart matching tool available in Agilent's ADS (Advanced Design System) simulation environment.

Fig. 2.2. Open-stub microstrip matching (facilitated by Agilent's ADS Smith Chart tool) providing maximum power transfer between source and  $50\Omega$  port example.

This simple method of matching is applicable at a single spot-frequency (f) which in turn defines the physical lengths  $(\ell)$  from the electrical lengths  $(\phi)$  of the line and open-stub in the design, by Eq. (2.2) [2]:

$$\ell = \frac{\phi.(\pi/180)}{\sqrt{\varepsilon_e \cdot k_0}} \tag{2.2}$$

where the effective dielectric constant ( $\varepsilon_e$ ) for a microstrip line is usefully approximated by Eq. (2.3), when the relationship between the microstrip line width (W) and substrate thickness (d) is within the limit  $W/d \ge 1$ ;

$$\varepsilon_{e} = \frac{\varepsilon_{r} + 1}{2} + \frac{\varepsilon_{r} - 1}{2} \cdot \frac{1}{\sqrt{1 + 12d/W}}$$

(2.3)

and where the wave number is given by Eq. (2.4);

$$k_0 = \frac{2\pi \cdot f}{c} \tag{2.4}$$

# 2.2.2 PA Design Based Around S-Parameter Measurements for the Active Device

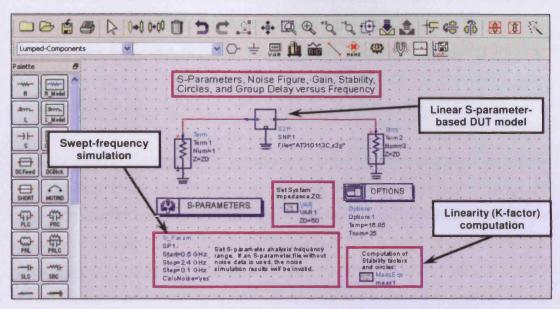

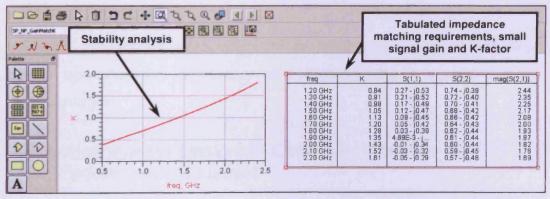

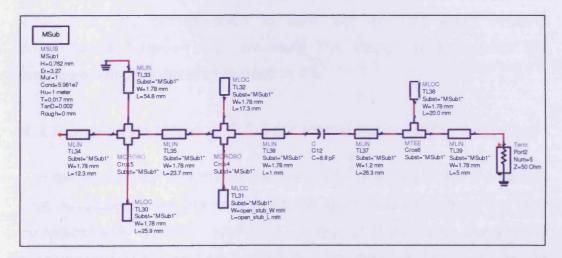

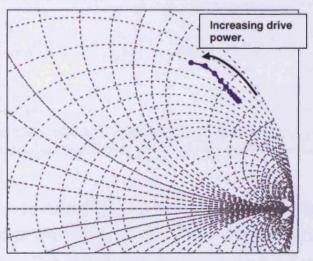

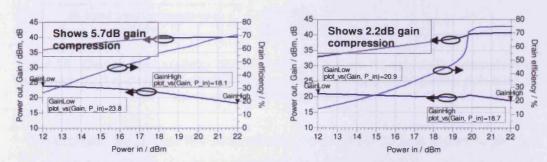

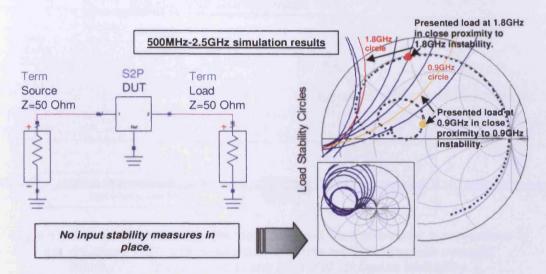

Using the techniques of transmission-line matching described in section 2.2.1, a simple PA design approach based solely on linear S-parameter (scattering-parameter) measurements can be undertaken to match the active DUT at the input and output for optimum power, gain and/or efficiency, whilst also considering stability across all frequencies. Such a design procedure can be rapidly implemented in a CAD environment such as Agilent's ADS [3].

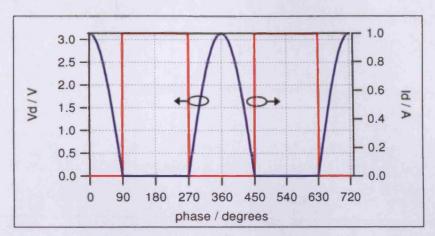

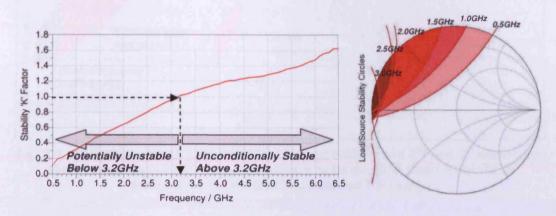

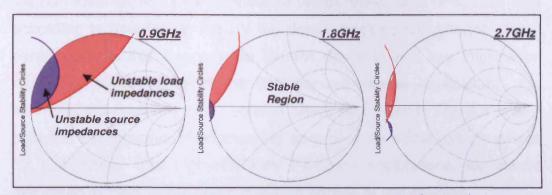

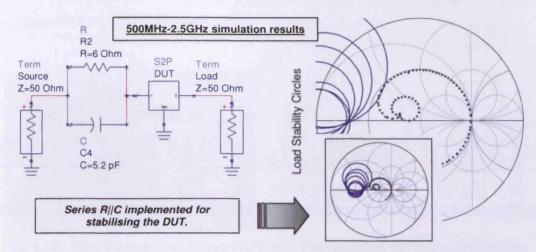

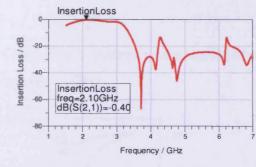

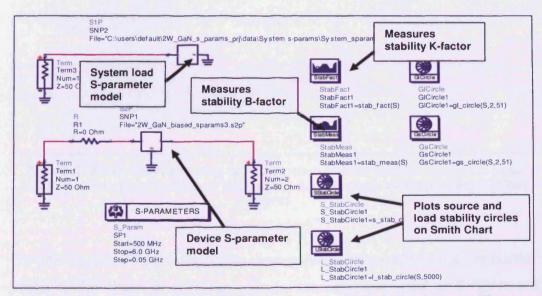

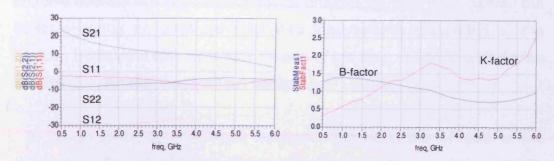

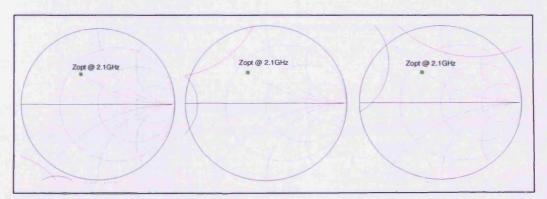

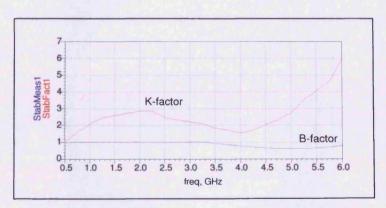

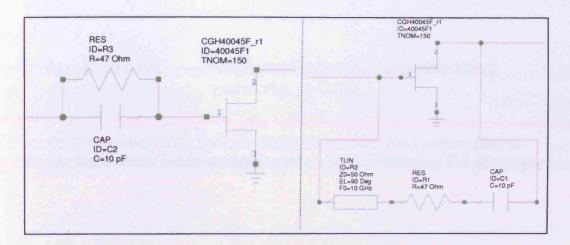

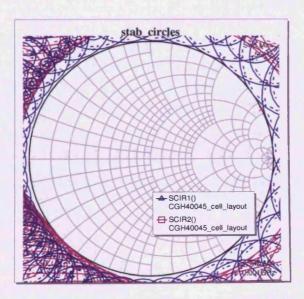

Figs. 2.3 and 2.4 show a couple of the stages of this type of design process; the simulation circuit layout and the data display providing a means of stability analysis and indicating matching impedance

requirements. The matching tool shown previously in Fig. 2.2 can then be implemented to complete the PA design.

Fig. 2.3. ADS design schematic for an example PA design simulation based around a linear S-parameter device model [3].

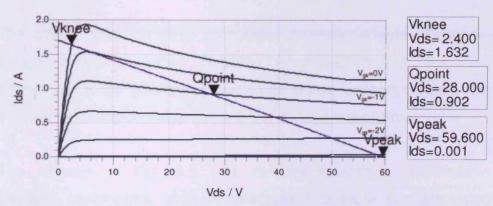

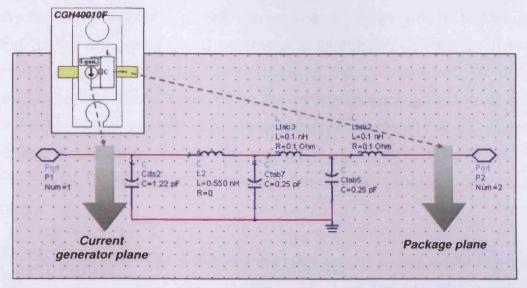

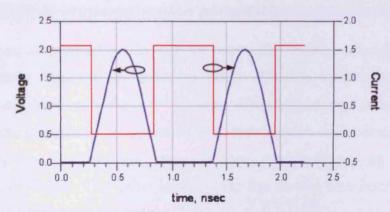

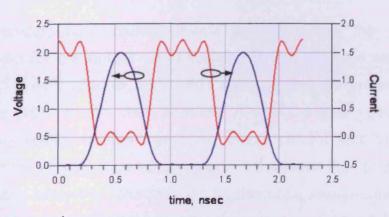

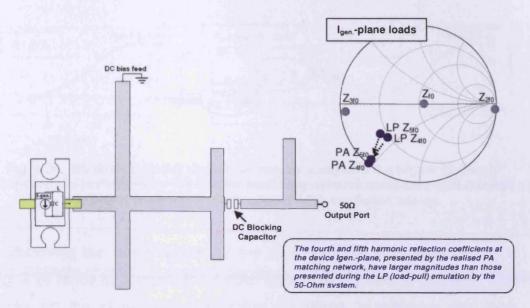

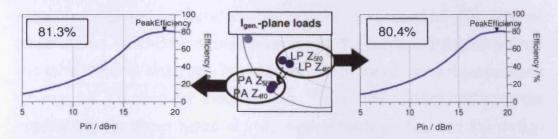

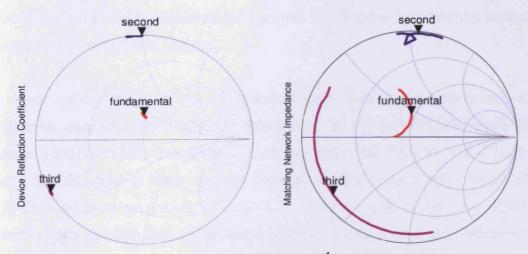

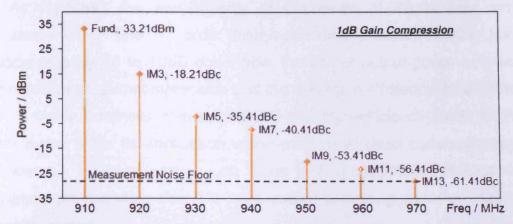

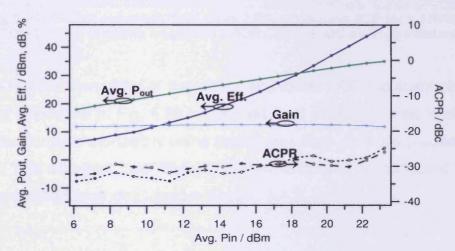

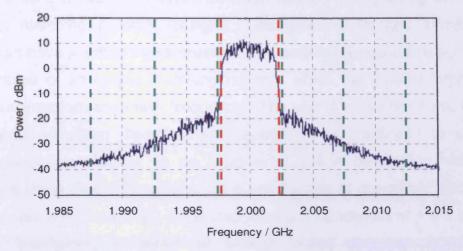

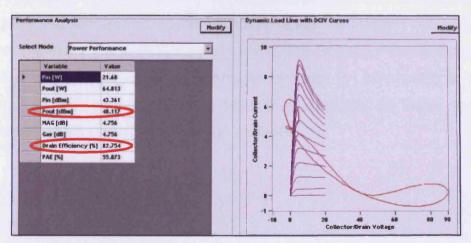

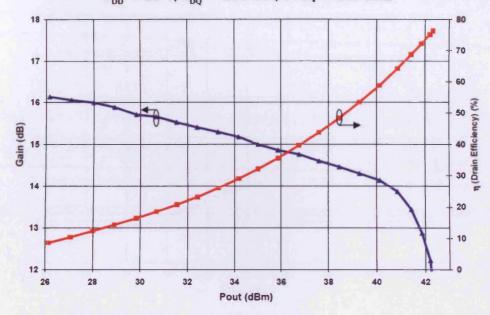

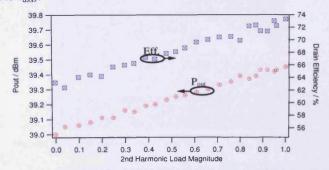

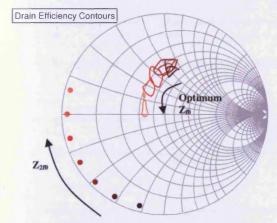

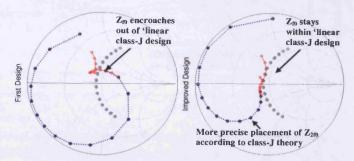

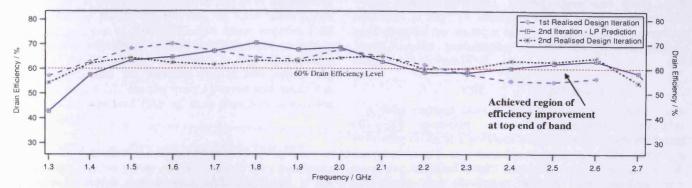

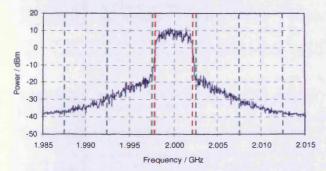

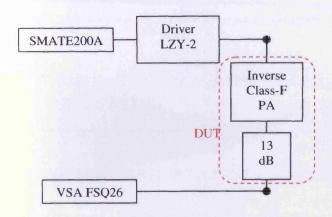

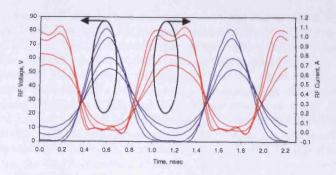

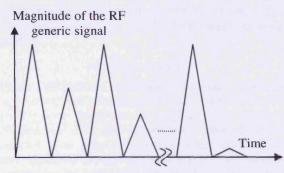

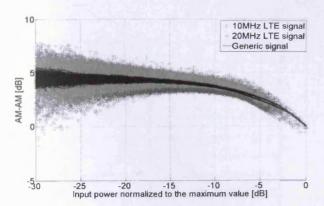

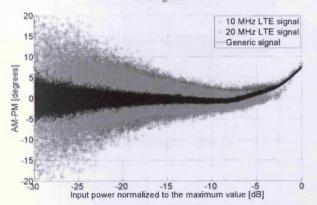

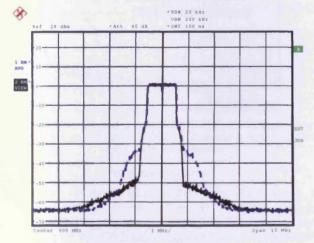

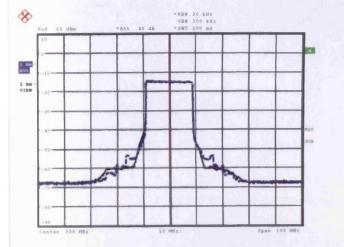

Fig. 2.4. ADS data display reveals the requirements for stabilisation of the device model, the small-signal gain and DUT input and output impedances.