# Nanoscale Properties of Molecular and Oxide Based Thin Film Devices Measured by SPM

Isam Abdullah

School of Physics and Astronomy

Cardiff University

A thesis submitted for the degree of Doctor of Philosophy in Nanophysics May 2016

#### **DECLARATION**

| This work has not been submitted in substance for any other degree or award at this or any other university or place of learning, nor is being submitted concurrently in candidature for any degree or other award.                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signed (candidate) Date                                                                                                                                                                                                                            |

| STATEMENT 1                                                                                                                                                                                                                                        |

| This thesis is being submitted in partial fulfillment of the requirements for the degree ofPhD(insert MCh, MD, MPhil, PhD etc, as appropriate)  Signed                                                                                             |

| STATEMENT 2                                                                                                                                                                                                                                        |

| This thesis is the result of my own independent work/investigation, except where otherwise stated.  Other sources are acknowledged by explicit references. The views expressed are my own.                                                         |

| Signed (candidate) Date                                                                                                                                                                                                                            |

| STATEMENT 3                                                                                                                                                                                                                                        |

| I hereby give consent for my thesis, if accepted, to be available online in the University's Open Access repository and for inter-library loan, and for the title and summary to be made available to outside organisations.                       |

| Signed (candidate) Date                                                                                                                                                                                                                            |

| STATEMENT 4: PREVIOUSLY APPROVED BAR ON ACCESS                                                                                                                                                                                                     |

| I hereby give consent for my thesis, if accepted, to be available online in the University's Open Access repository and for inter-library loans after expiry of a bar on access previously approved by the Academic Standards & Quality Committee. |

| Signed (candidate) Date                                                                                                                                                                                                                            |

# **Table of Contents**

| Declaration                                   | i    |

|-----------------------------------------------|------|

| List of contents                              | ii   |

| List of figures                               | v    |

| List of tables                                | xii  |

| Abbreviations                                 | xiii |

| Acknowledgments                               | xvi  |

| Abstract                                      | xvii |

| 1 Introduction                                | 1    |

| 2 Theoretical background                      | 9    |

| 2.1 Introduction.                             | 9    |

| 2.2 Thin film transistors.                    | 10   |

| 2.3 Thin film transistor structure            | 10   |

| 2.4 Basic operation of TFT                    | 12   |

| 2.5 Basic theory of TFT characteristics       | 14   |

| 2.6 The main components of a TFT              | 16   |

| 2.6.1 The substrate/ gate                     | 16   |

| 2.6.2 Dielectric layer.                       | 16   |

| 2.6.3 Source and drain electrode              | 18   |

| 2.7 Electrical characterization of ETs.       | 19   |

| 2.7.1 Transfer characteristic.                | 19   |

| 2.7.2 Output characteristic                   | 21   |

| 2.8 Contact resistance (CR)                   | 22   |

| 2.9 Organic semiconductor                     | 23   |

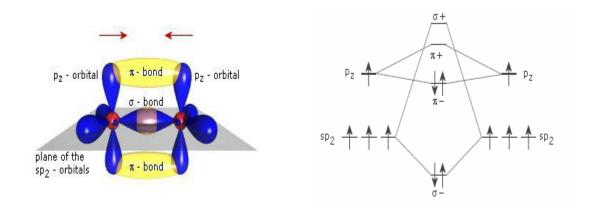

| 2.10 Charge transfer in OS.                   | 26   |

| 2.11 Factors affecting charge transport in OS | 28   |

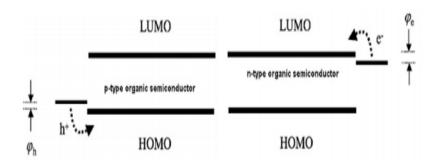

| 2.11.1 HOMO and LUMO level                    | 28   |

| 2.11.2 Molecular structure and packing        | 29   |

| 2.11.3 Material impurities                    | 30   |

| 2.12 Semiconductor Materials investigated     | 31   |

| 2.12.1 Organic small molecules                | 31   |

| 2.12.2 Metal oxide semiconductor                                                                                 | 34           |

|------------------------------------------------------------------------------------------------------------------|--------------|

| 3 Morphology control strategies for solution processed TIPS-PEN thin film.                                       | 36           |

| 3.1 Introduction.                                                                                                | 36           |

| 3.2 Solvent blend casting                                                                                        | 38           |

| 3.2.1 Vitrification                                                                                              | 38           |

| 3.2.2 Phase separation                                                                                           | 38           |

| 3.2.3 Crystal nucleation                                                                                         | 40           |

| 3.3 Solubility parameter and TIPS-pentacene solubility                                                           | 41           |

| 3.4 Experimental details                                                                                         | 42           |

| 3.5 Film casting and evaporation                                                                                 | 45           |

| 3.6 TIPS-PEN crystalline thin film growth                                                                        | 47           |

| 3.7 Evaporation dynamic and crystal growth                                                                       | 54           |

| 3.8 Performance of Pure TIPS-PEN transistor                                                                      | 58           |

| 3.9 Step edge grain statistics                                                                                   | 59           |

| 3.10 Influence of low concentration of polystyrene on crystal grov                                               |              |

| roughness and OFET device performance of TIPS-PEN                                                                |              |

| 3.11 Conclusions                                                                                                 |              |

| 4 In <sub>2</sub> O <sub>3</sub> thin film transistors                                                           |              |

| 4.1 Introduction                                                                                                 |              |

| 4.2 Experimental details                                                                                         |              |

| 4.2.1 Preparation procedure                                                                                      |              |

| 4.2.2 Device Characterization, bonding, and measurements                                                         |              |

| 4.3 Indium oxide Surface morphology                                                                              |              |

| 4.4 Electric characterization of In <sub>2</sub> O <sub>3</sub> TFT                                              |              |

| 4.4.1 The output characteristic                                                                                  |              |

| 4.4.2 The transfer characteristics                                                                               |              |

| 4.5 Gradual channel model for threshold and mobility extraction                                                  | 88           |

| 4.6 Effects of active layer thickness and device dimension                                                       |              |

| 4.7 Bias stress and device instability                                                                           | 93           |

| 4.8 Surface potential images about charge trapping (Spatial distribution charges)                                |              |

| 4.9 Surface potential study of indium oxide TFT                                                                  | 108          |

| 4.10 Mapping of Aluminium diffusion in In <sub>2</sub> O <sub>3</sub> Thin film transistor an potential profiles | nd modelling |

| 4.11 Conclusions                                                                                                 |              |

| 5 High Sptial Resolution Electrostatic Force Microscopy ( EFM)                                                   | 126          |

|   | 5.1 Introduction.                                                    | 127  |

|---|----------------------------------------------------------------------|------|

|   | 5.2 EFM phase measurements and its theory                            | 128  |

|   | 5.3 Experimental details                                             | 132  |

|   | 5.4 Imaging processing and data analysis                             | 135  |

|   | 5.4.1 Study 1 :Effect of scan size                                   | 137  |

|   | 5.4.2 Study 2: Effect of tip height                                  | 137  |

|   | 5.4.3 Study 3: Effect of tip bias                                    | 140  |

|   | 5.4.4 study 4:Effect of signal frequency                             | 141  |

|   | 5.5 Design of a new software for EFM data                            | 145  |

|   | 5.5.1 Au(111)/mica                                                   | 152  |

|   | 5.5.2 MDMO-PPV/PCBM                                                  | 154  |

|   | 5.6 Further improvements in EFM data                                 | 155  |

|   | 5.7 Organizing the new experiment set up for transistor measurements | 157  |

|   | 5.7.1 Study 1: At low drain bias (linear region).                    | 161  |

|   | 5.7.2 Study 2: At high drain bias (saturation region)                | 162  |

|   | 5.8 Comparison between SKPM and EFM (new software) images            | 164  |

|   | 5.9 Conclusions.                                                     | 167  |

| 6 | Conclusions and potential future work.                               | 168  |

| R | eferences                                                            | .175 |

# List of figures

| Figure 1.1: Schematic Atomic Force Microscopy operation                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: The tip-sample interaction as a function of the distance                                                                                                            |

| Figure 1.3: The molecular structure of 6,13-bis(triisopropyl-siylethynyl) pentacene (TIPS-PEN)                                                                                  |

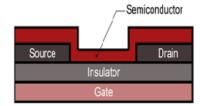

| Figure 2.1: Basic structures for thin film transistor presenting top contact bottom gate and bottom gate bottom contact                                                         |

| Figure 2.2: The flow direction of current in top contact- bottom gate and bottom contact-bottom gate configratios                                                               |

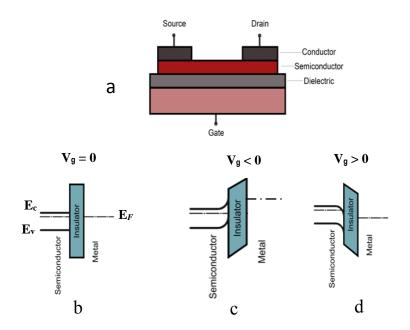

| Figure 2.3: (a) TFT structure and corresponding gate biasing conditions. (b) The equilibrium condition. (c) $V_g < 0V$ . (d) $V_g > 0V$                                         |

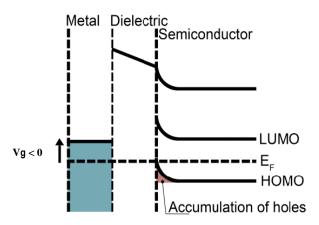

| Figure 2.4: Application of a negative gate bias on p-type organic semiconductor. The $E_F$ of metal raises by gate bias and leads to OS band to bend as they re-equilibrate .14 |

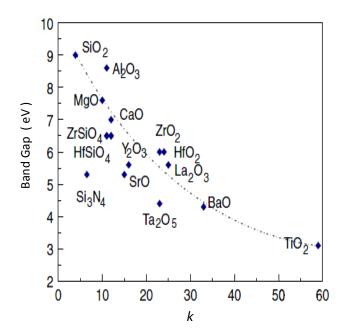

| Figure 2.5: Dielectric constant versus band gap of some gate oxides                                                                                                             |

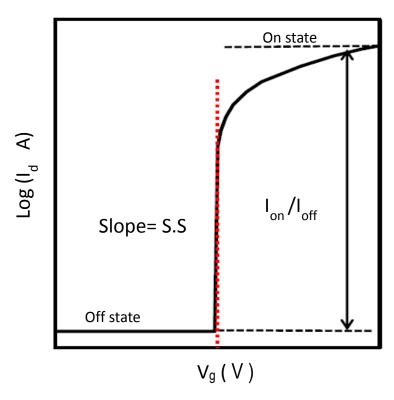

| Figure 2.6 : Schematic diagram for sub-threshod slop and drain current $\textit{I}_{\textit{on}}/\textit{I}_{\textit{off}}$ 20                                                  |

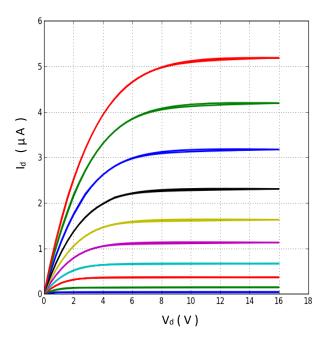

| Figure 2.7: Typical output curves for metal oxide TFT with $V_g$ =1 to 10(step 1V)21                                                                                            |

| Figure 2.8: Schematic diagram for Top contact bottom gate TFT describing channel and interface resistance                                                                       |

| Figure 2.9: Two connected carbon atom with its orbitals, and energy levels of occupied and unoccupied levels for $\sigma$ and $\pi$ levels                                      |

| Figure 2.10: Energy gap dependence on conjugation length                                                                                                                        |

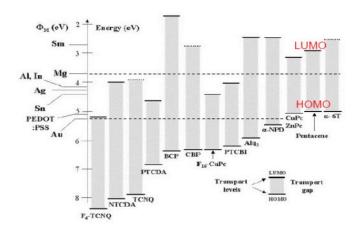

| Figure 2.11: Energy level diagram of charge injection process in OS29                                                                                                           |

| Figure 2.12: Metal work functions relative to HOMO and LUMO for different organic material                                                                                      |

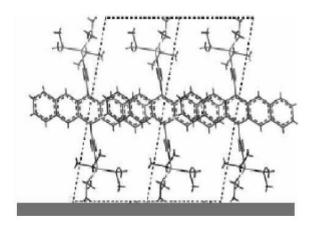

| Figure 2.13: Highly ordered TIPS-PEN molecules on SiO <sub>2</sub> substrate30                                                                                                  |

| Figure 2.14: Chemical structure of impurities found in pentacene31                                                                                                              |

| Figure 2.15: Edge to face herringbone structure                                                                                                                                 |

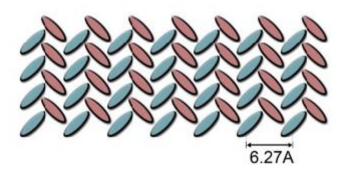

| Figure 2.16: Two dimensional Brickwork arrangements. The arrow refers to the direction of charge transport which can take place                                                 |

| Figure 2.17: Face to face 1D <i>slipped stack</i> arrangements. Again the arrow refers to the charge transport which can take place only in one direction                       |

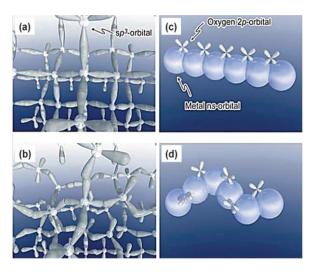

| Figure 2.18: Electron transport and conduction path in [a] crystalline Silicon [b] amorphous Silicon [c] crystalline metal oxide [d] amorphous metal oxide35                    |

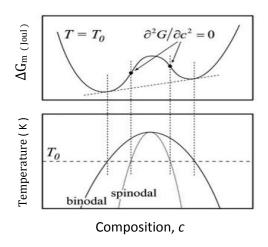

| Figure 3.1: Free energy as a function of composition change and spinodal, binodal curves at various temperatures                                                                |

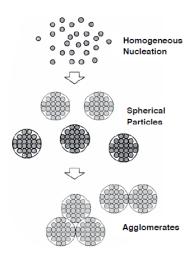

| Figure 3.2: Homogenous nucleation mechanism                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.3: Crystallization starts from seed crystal followed by crystal nucleation and formation of large crystal                                                                                                                                   |

| Figure 3.4: Drop casting TIPS-PEN solution with different composition of anisole and decane on Si wafer                                                                                                                                              |

| Figure 3.5: Specialized Glove box for gold evaporation and deposition of contacts through shadow mask                                                                                                                                                |

| Figure 3.6: Image of microprobe station and semiconductor device analyser44                                                                                                                                                                          |

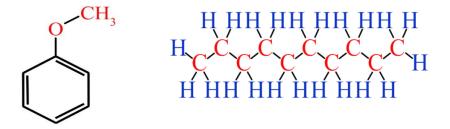

| Figure 3.7: anisole and decane chemical structure                                                                                                                                                                                                    |

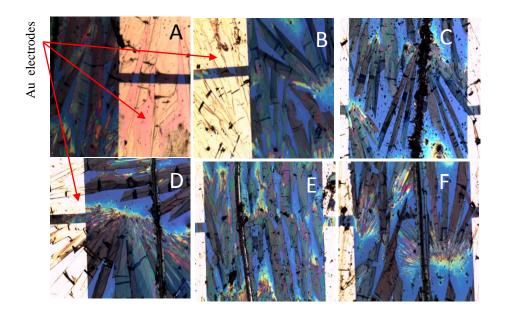

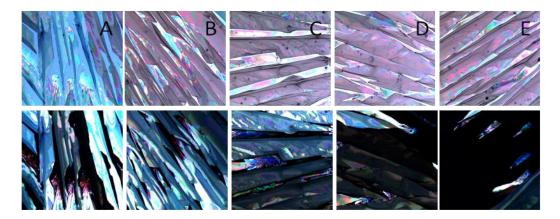

| Figure 3.8: Optical microscope (OM) images of TIPS-PEN droplet with various solvent compositions                                                                                                                                                     |

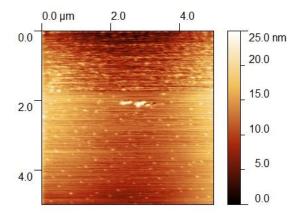

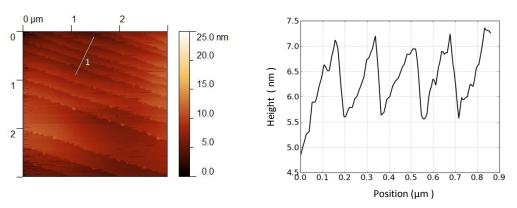

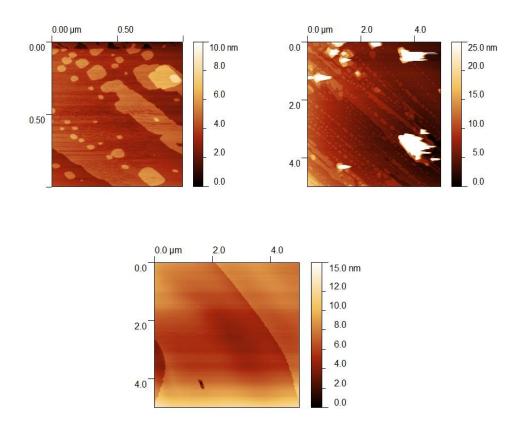

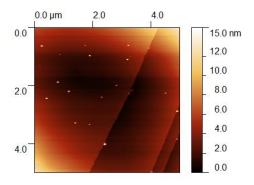

| Figure 3.9: Scanned AFM image in tapping mode of a crystalline domain taken from edge of droplet                                                                                                                                                     |

| Figure 3.10: AFM image taken from centre of droplet and corresponding profile across drown line. The line profile reveals some peaks when the line crossing grains                                                                                   |

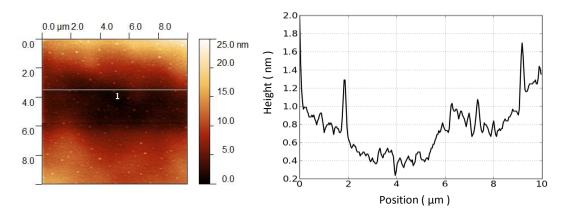

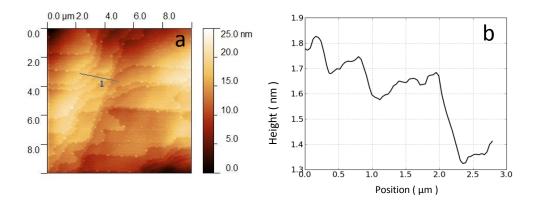

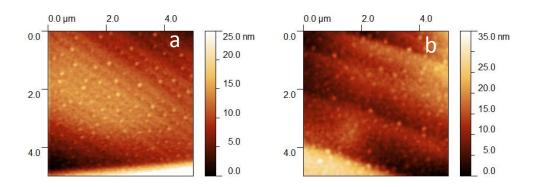

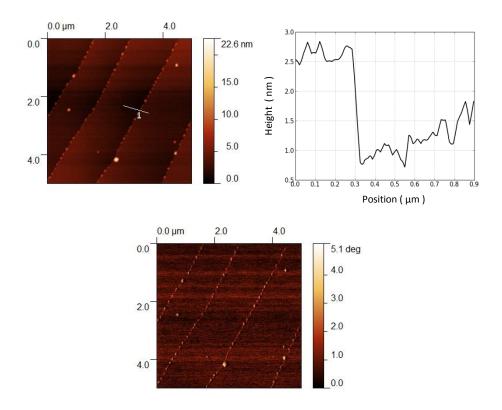

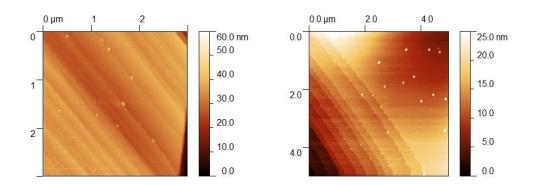

| Figure 3.11: AFM images in tapping mode of TIPS-PEN drop-cast from anisol:decane 95:5 vol/vol with total vertical range 25nm. Line profile across terraces shows step height of $1.53\pm$ 0.09 and $1.61\pm0.11$ nm respectively                     |

| Figure 3.12: A) AFM images of 9% decane concentration and the line presenting step heights (1.41, 1.60 and 3.5nm respectively from left)                                                                                                             |

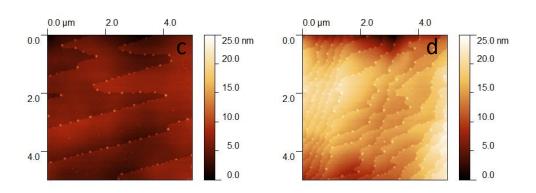

| Figure 3.13: Tapping mode AFM images of A) 15% decane. B) 20 percent of decane, we notice that the steps become unclear or undefined                                                                                                                 |

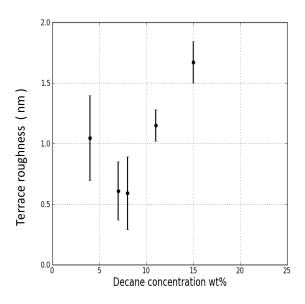

| Figure 3.14: Change of roughness with decane concentration                                                                                                                                                                                           |

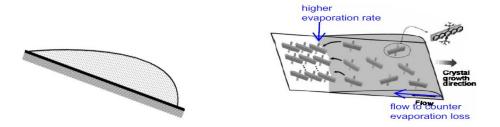

| Figure 3.15: A droplet of TIPS-PEN solution on tilted substrate and the possible growth mechanism                                                                                                                                                    |

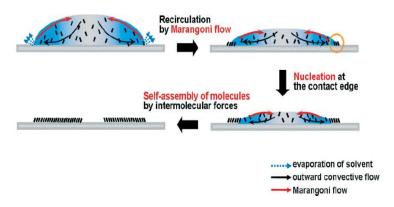

| Figure 3.16: Schematic presentation of film drying by using binary solvents system the dark blue shows solvent with high boiling point                                                                                                               |

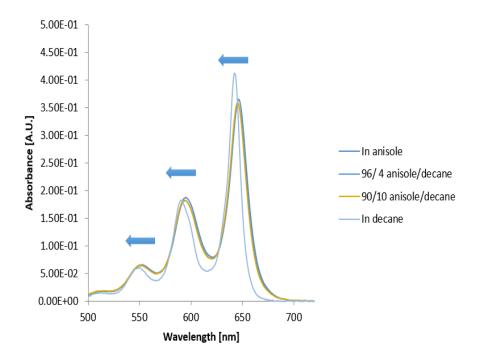

| Figure 3.17: UV/Vis absorption spectra of TIPS-PEN dissolved in different anisole/decane solvent mixtures                                                                                                                                            |

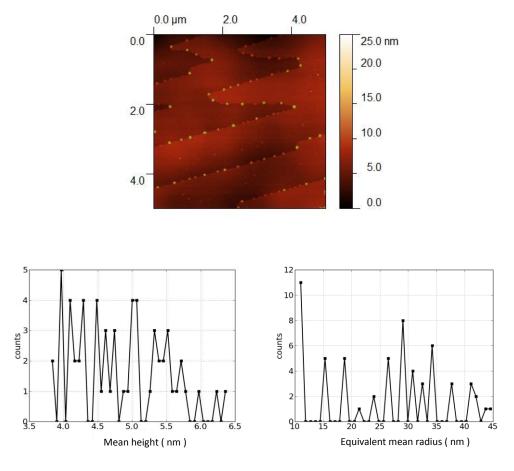

| Figure 3.18: Grains statistic according to their mean height and equivalent mean disc radius                                                                                                                                                         |

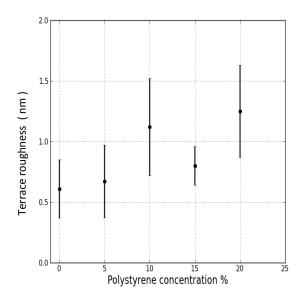

| Figure 3.19: Polarized Optical micrographs for pure TIPS-PEN film and four TIPS-PEN/PS blends ratio at 30C°                                                                                                                                          |

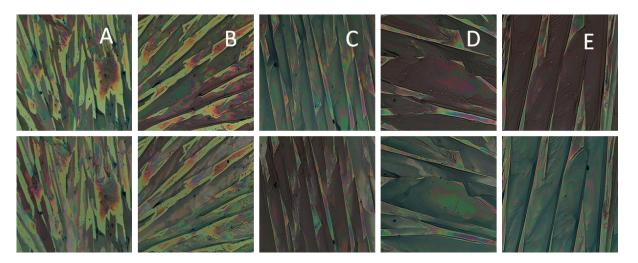

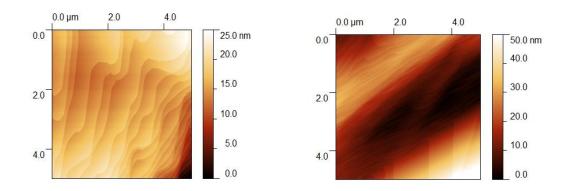

| Figure 3.20: Tapping mode AFM image of 5% Ps shows step height $(1.62\pm0.15)$ 62                                                                                                                                                                    |

| Figure 3.21: AFM height and phase images of 5% polystyrene blend with cross sectional line profile. The measured step height is (1.96±0.11) nm. The phase image shows the appearance of larger grain size suggesting polystyrene visage during phase |

| Figure 3.22:10% polystyrene blends AFM images with dendrite style and wide terrace                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.23: Atomic force microscopy images of drop cast film of TIPS-PEN:15% aPS 2% wt blends                                                                                                                                    |

| Figure 3.24: 20% polystyrene blend. The terraces contain lots of holes or openings sharing only with one white ball                                                                                                               |

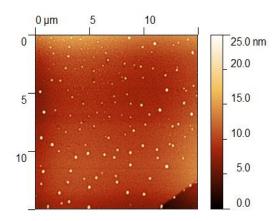

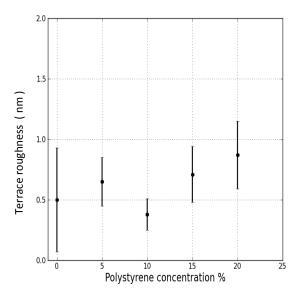

| Figure 3.25: Flat area roughness variations with aPS composition in the blend on $SiO_2$ 65                                                                                                                                       |

| Figure 3.26: Polarized optical microscopy images of pure TIPS-PEN and TIPS-PEN:Polystyrene blends according to Ps weight fraction                                                                                                 |

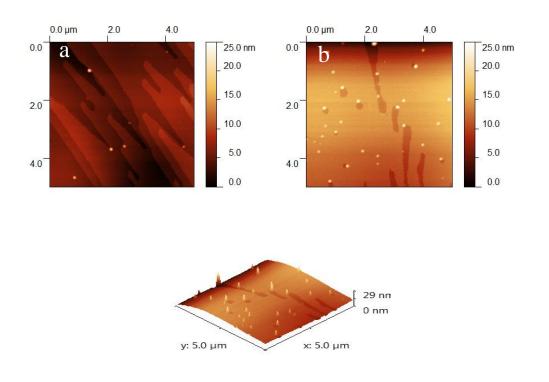

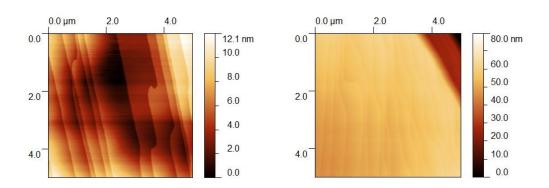

| Figure 3.27: AFM images for pristine TIPS-PEN on PVP dielectric. The top images show TIPS-PEN islands distribution while the bottom image reveals well defined large terraces                                                     |

| Figure 3.28: AFM images for 95:5 of TIPS-PEN/aPS blend. The wavy style of ordered film is clear and the terraces fluctuate between narrow and wide69                                                                              |

| Figure 3.29: AFM images for 10 percent ratio blend composition. The images exhibit straight line ordering and well defined film pattern                                                                                           |

| Figure 3.30: AFM images for TIPS-PEN:PS of 85:15, the appearance of wavy style of molecular ordering again                                                                                                                        |

| Figure 3.31: AFM images for 80/20 TIPS-PEN and Ps ratio. Appearance of wide terraces with white grains again                                                                                                                      |

| Figure 3.32: Flat area roughness of TIPS-PEN/aPS blends on PVP72                                                                                                                                                                  |

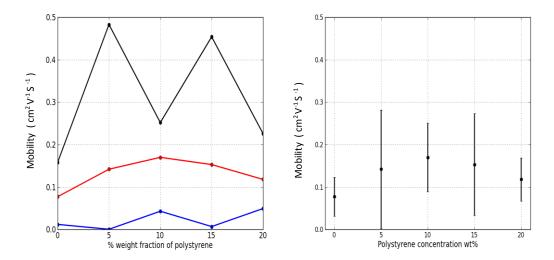

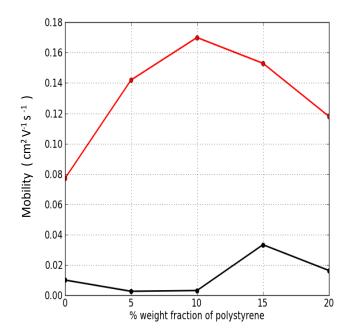

| Figure 3.33: The mobility change according to TIPS-PEN/aPS blends ratio on PVP dielectric. Black graph refer to maximum mobility, red presents average mobility, and the blue is minimum mobility                                 |

| Figure 3.34: Average mobility changes of transistors according to the active layer composition of TIPS-PEN and its blends of polystyrene on PVP and SiO <sub>2</sub> dielectric                                                   |

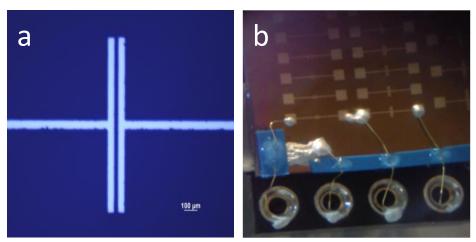

| Figure 4.1: a) The specific transistor before bonding, b) after bonding with gold wire                                                                                                                                            |

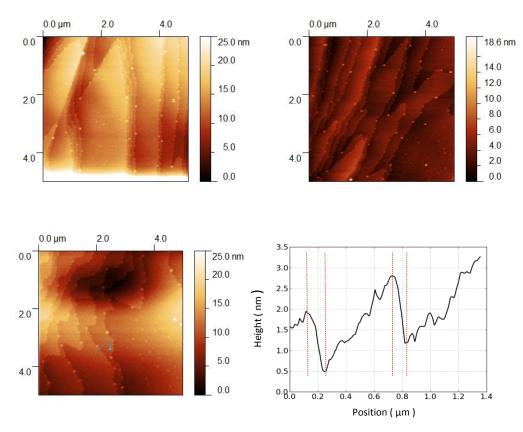

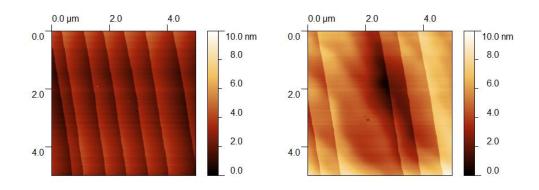

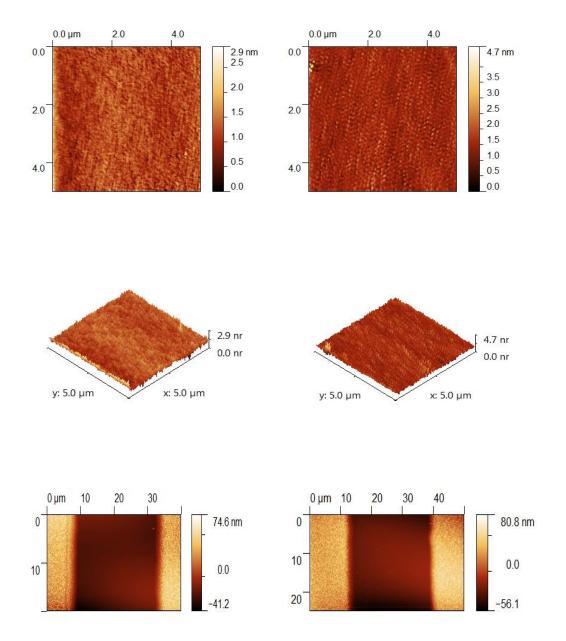

| Figure 4.2: AFM images of single spin coating and double spin coating film of ndium oxide                                                                                                                                         |

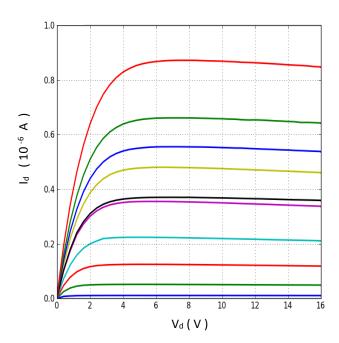

| Figure 4.3: Single spin coating transistor of dimension W1500L40S. The gate bias $Vg$ = 1, 2,10V step 1V bottom images are for corresponding devices with Al electrodes                                                           |

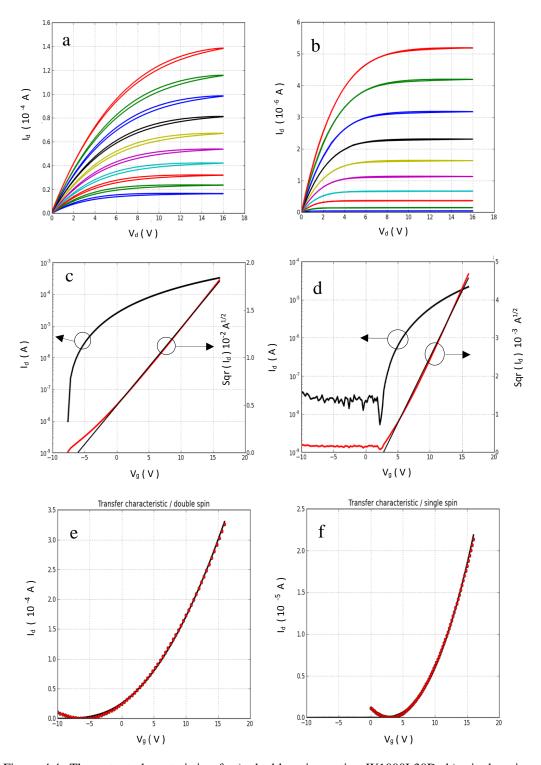

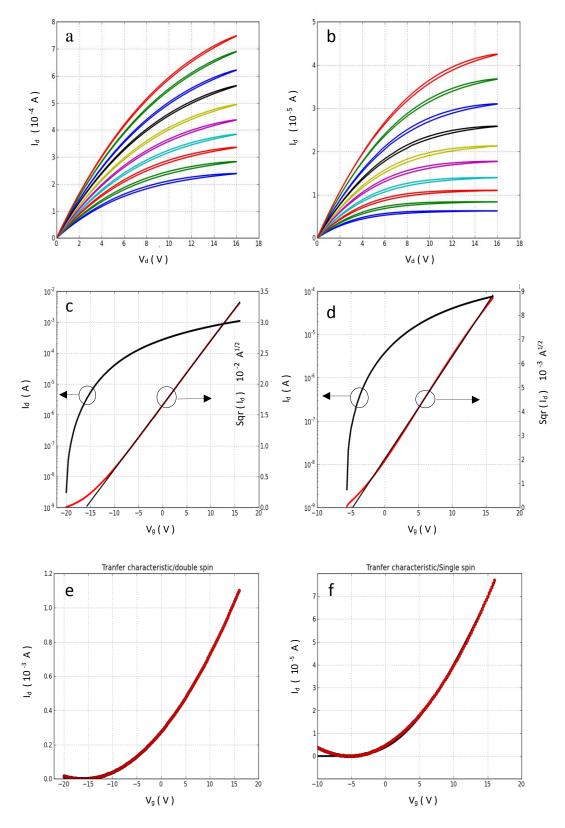

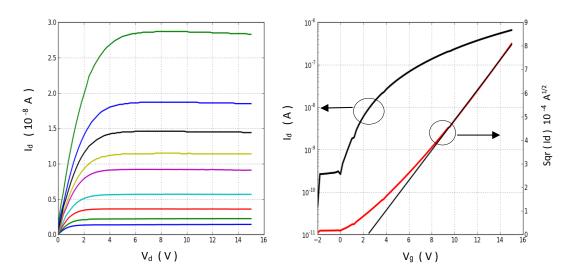

| Figure 4.4: The output and transfer characteristic of: a), double spin coating W1000L30D, b), single spin coating W1000L30S. The gate bias $V_g = 1, 2, 3, 10V$ step 1V for both doable and single spin                           |

| Figure 4.5: The output characteristics at $V_g$ = 1, 2,3,10V step 1 V of double (a) and single (b) spin coating thin film transistor of dimension W1000L20. c and d ), the corresponding transfer characteristics at $V_d$ =10V91 |

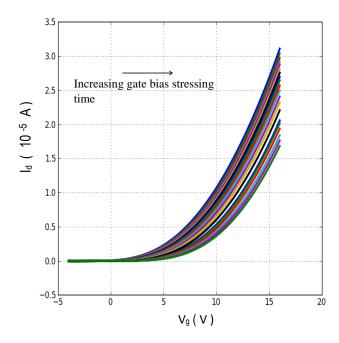

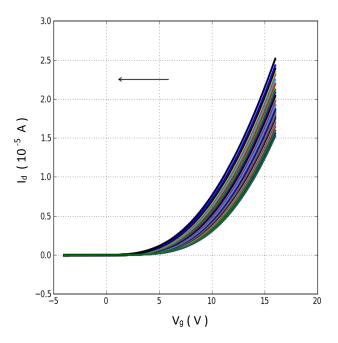

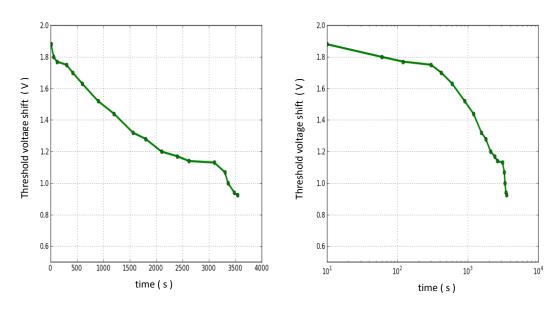

| Figure 4.6: Transfer characteristic curves shift with stressing time on $W=1000\mu m$ and $L=30\mu m$ single spin coating device                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

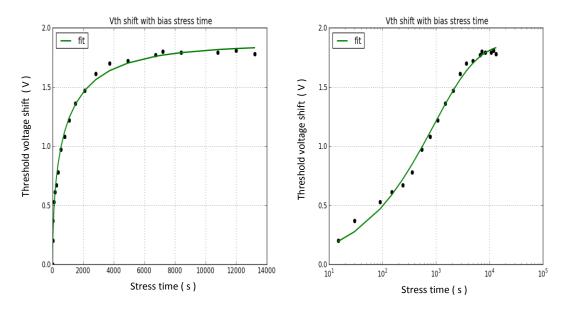

| Figure 4.7: Time dependence of threshed voltage shift under the applied gate bias stress 10V in linear scale and logarithmic scale                                                                                                                                                                                                     |

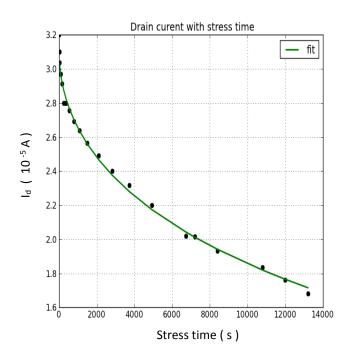

| Figure 4.8: Drain current decrease with stress time                                                                                                                                                                                                                                                                                    |

| Figure 4.9: Transfer characteristics back shift after stress release of device W= $1000 \mu m$ and L= $30 \mu m$ .                                                                                                                                                                                                                     |

| Figure 4.10: Threshold voltage recovery after switching off the gate bias. The data is plotted in both linear and logarithmic scale                                                                                                                                                                                                    |

| Figure 4.11: The output and transfer characteristics of W=1500, L= $40\mu m102$                                                                                                                                                                                                                                                        |

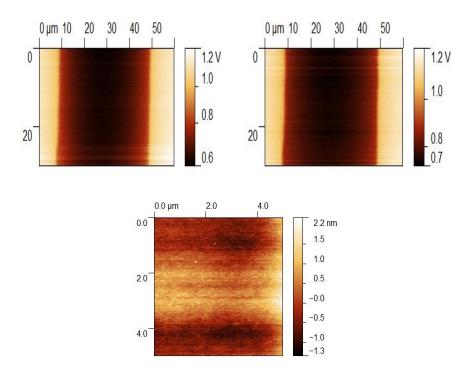

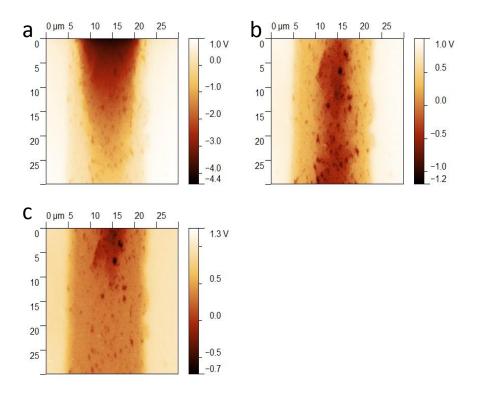

| Figure 4.12: Surface potential images before and after applying +5V gate bias with source and drain electrodes grounded                                                                                                                                                                                                                |

| Figure 4.13: Surface potential image after setting gate bias to zero104                                                                                                                                                                                                                                                                |

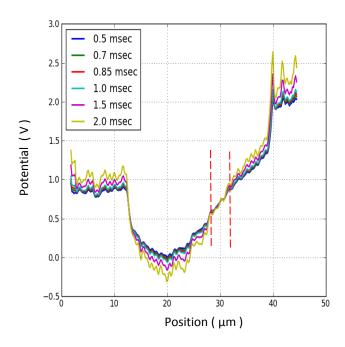

| Figure 4.14: Surface potential profiles variation as a function of scanning time with the slow scan axis disabled                                                                                                                                                                                                                      |

| Figure 4.15: Captured surface potential and line profiles, continuing from Figure 4.14, showing device recovery with time for the second scan from top to bottom                                                                                                                                                                       |

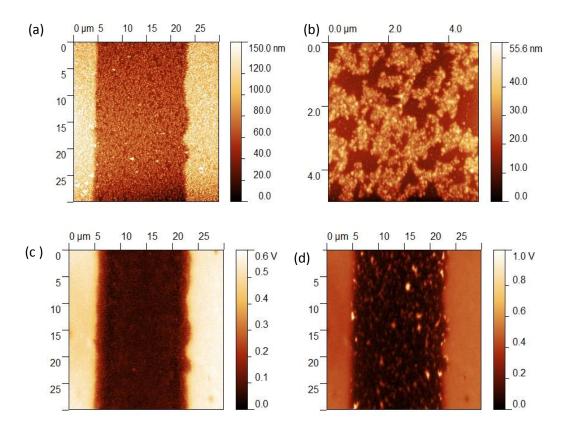

| Figure 4.16: AFM height image a), across two electrodes b), 5µmx5µm AFM image captured between two electrodes c), EFM surface potential before applying gate bias d), EFM after applying +8V gate bias                                                                                                                                 |

| Figure 4.17: Recovery of the device after switching the gate bias to zero. a), Scanning from top to bottom, b), scanning from bottom toward top, c), scanning from top toward bottom. The time taken per image is about 8.1min                                                                                                         |

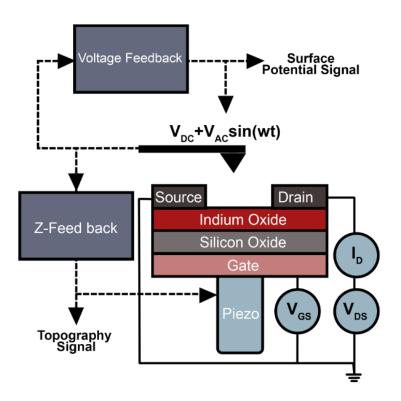

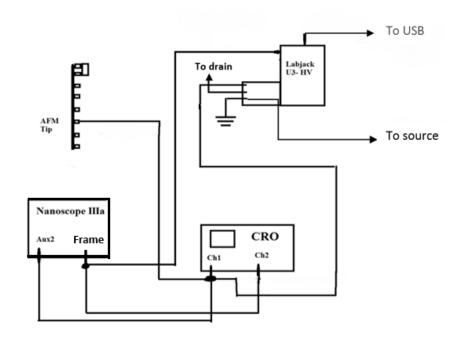

| Figure 4.18: Experimental setup used for indium oxide TFT surface potential measurements                                                                                                                                                                                                                                               |

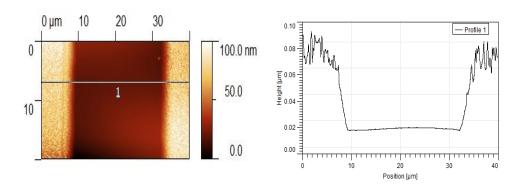

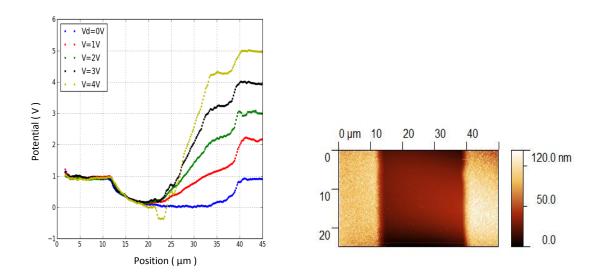

| Figure 4.19: AFM topographic image of W1000L30S device and the corresponding line profile. The channel between electrodes is clearly seen and contain no voids or discontinuity                                                                                                                                                        |

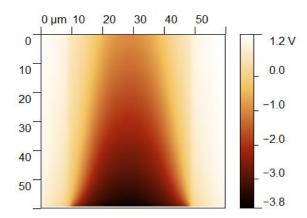

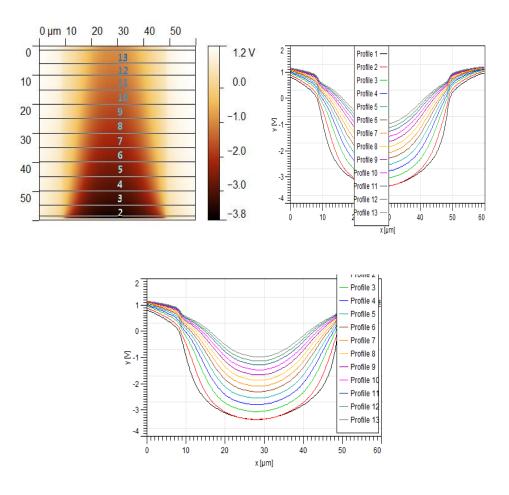

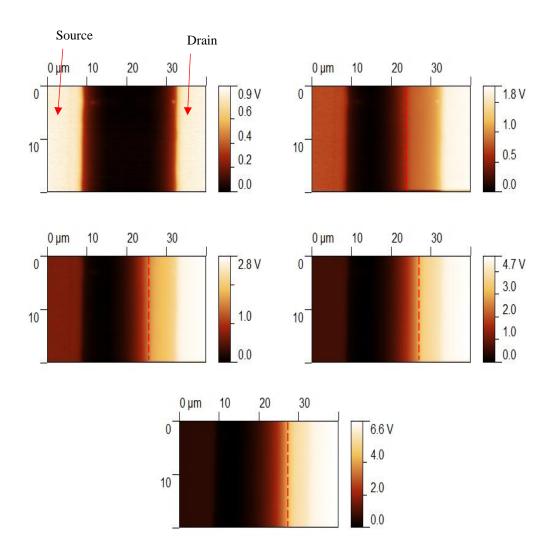

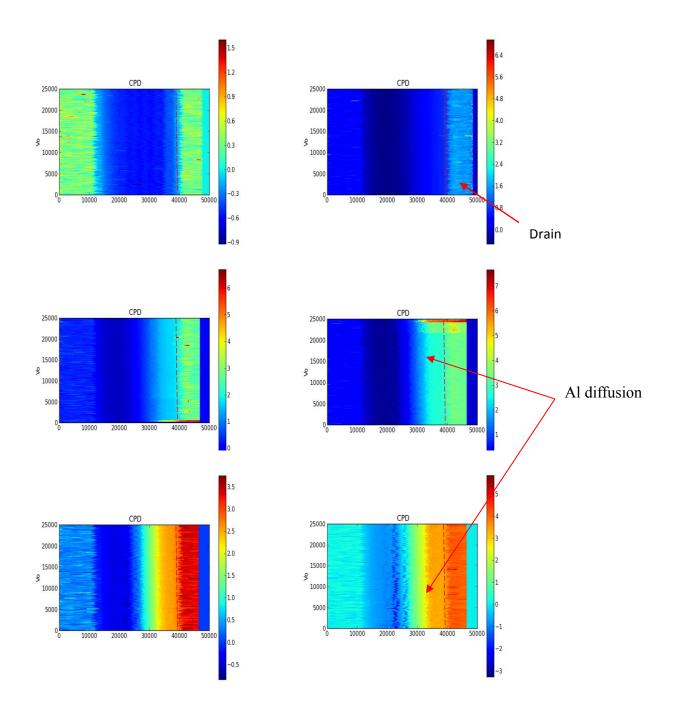

| Figure 4.20: 2D surface potential images of L30W1000S device at 0, 1, 2, 4, and 6V drain bias                                                                                                                                                                                                                                          |

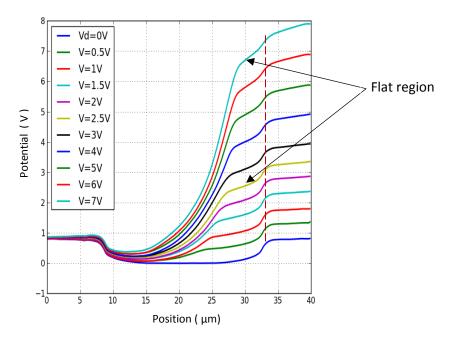

| Figure 4.21: The W1000L30S device potential profiles acquired for different drain biases with grounding the source and gate terminals. The drain electrode edge is marked as a dashed red line                                                                                                                                         |

| Figure 4.22: The W1000L30S device potential profiles at fixed 5V gate voltage and varied drain biases                                                                                                                                                                                                                                  |

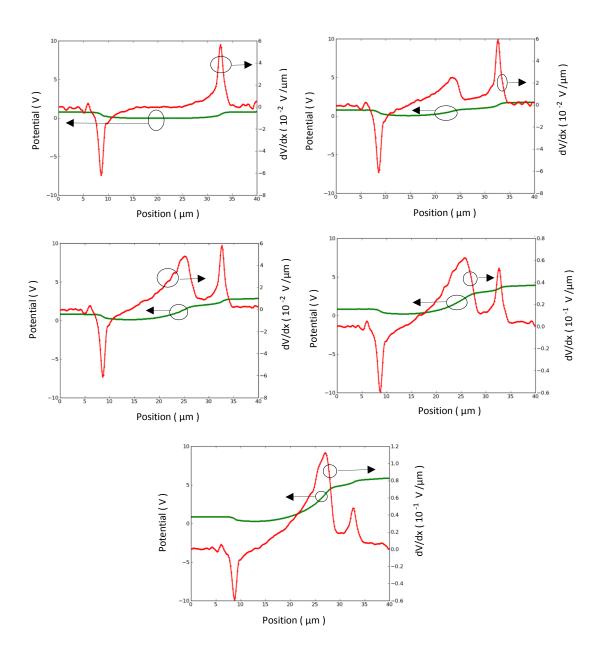

| Figure 4.23: Change of first derivative of potential across the channel and pecification of electrode and diffusion position. The green curves represents the potential and the red curve is the first derivative of potential. The plotted data corresponding to Figure 4.20 and Figure 4.21 for drain bias values 0, 1, 2, 4, and 6V |

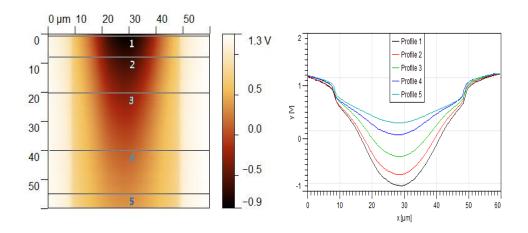

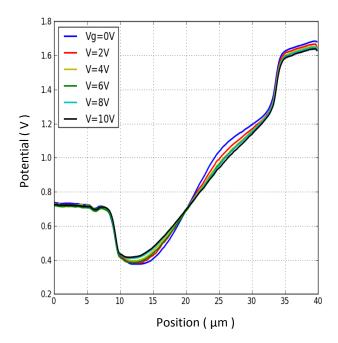

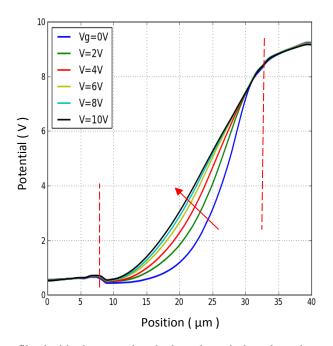

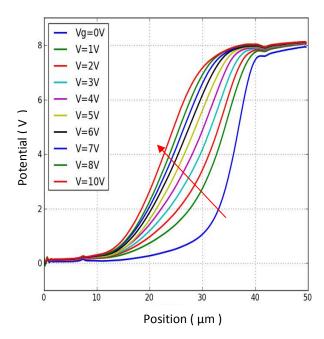

| Figure 4.24: Potential profiles as a function of gate bias where $V_d$ =1V (linear region) and gate bias changed from 0 to 10V step 2V                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.25: Potential profiles inside the operating device where drain voltage kept constant at high voltage 9V and gate bias changed with step 2V from 0 to 10V116                                                                                                                                                                                                                                                                                                             |

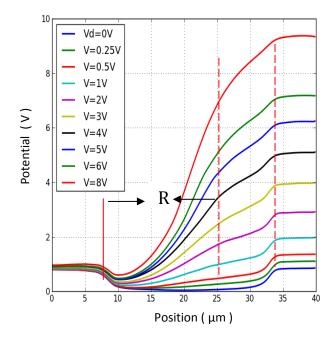

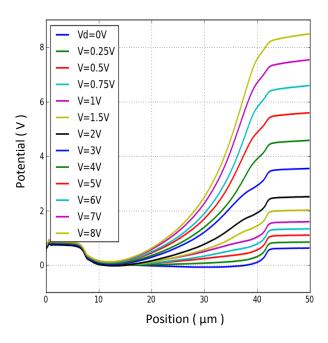

| Figure 4.26: Surface potential profiles across W200L40D device at fixed gate bias +5V.                                                                                                                                                                                                                                                                                                                                                                                           |

| 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.27: Gate voltage dependence potential profiles inside operating L40W200D device. The drain bias was constant +8V during the experiment and gate voltage changed from 1 to 10V step 1V. The profiles obtained after subtraction the reference profile at $V_d$ = 0 from all $V_d$ ≠0                                                                                                                                                                                     |

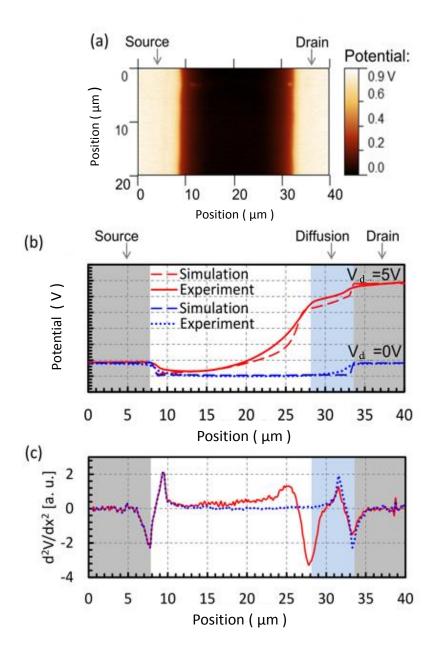

| Figure 4.28: The potential distribution at the surface when the single-spin TFT is grounded. Only the source and drain electrodes can be detected at 0 V. (b) Measured and simulated potential profiles at $V_d$ =0 V and $V_d$ =5 V when $V_g$ =0V. (c) Calculated second derivative of the surface potential at $V_d$ =0 V (dashed line) and $V_d$ =5 V (solid line) represents a change in the lateral electric field and allows determining exactly a diffusion region edge. |

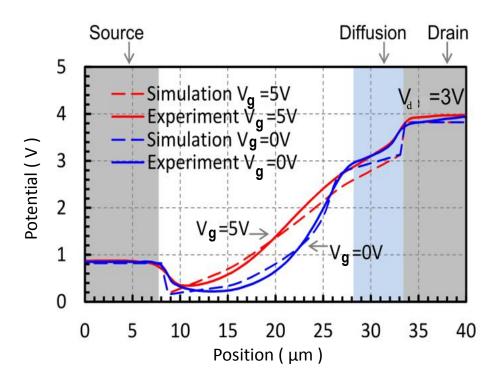

| Figure 4.29: Measured and simulated potential profiles at $V_d$ = 3V for the single –spin $In_2O_3$ TFT at $V_g$ =0 and $V_g$ = 5V                                                                                                                                                                                                                                                                                                                                               |

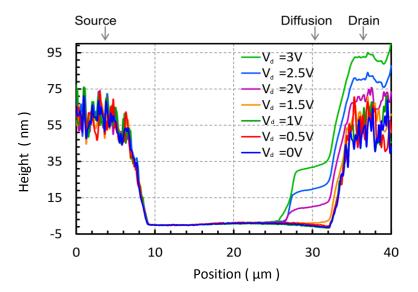

| Figure 4.30: Height line scans for $V_d$ from 0V to 3V demonstrate the electrostatic contribution to the apparent morphology of the sample and for the drain bias $V_d > 2V$ position of the diffusion region can be determined                                                                                                                                                                                                                                                  |

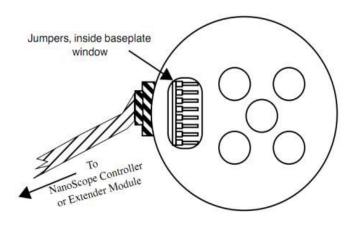

| Figure 5.1: Multimode base plate showing location and orientation of jumpers132                                                                                                                                                                                                                                                                                                                                                                                                  |

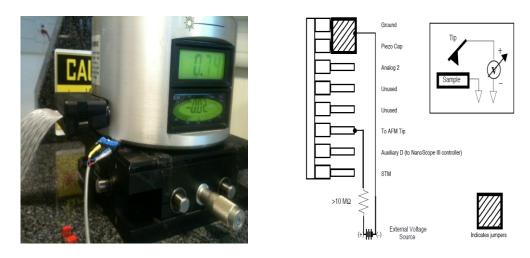

| Figure 5.2: Jumper configuration of applied voltage to the tip                                                                                                                                                                                                                                                                                                                                                                                                                   |

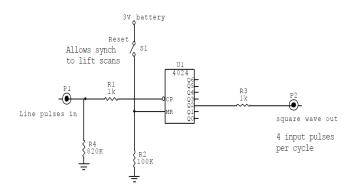

| Figure 5.3: Triggering module for EFM synchronization                                                                                                                                                                                                                                                                                                                                                                                                                            |

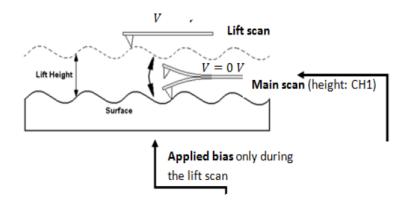

| Figure 5.4: Diagram of EFM scanning process in height and lift mode134                                                                                                                                                                                                                                                                                                                                                                                                           |

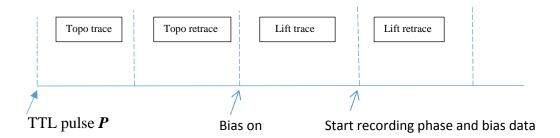

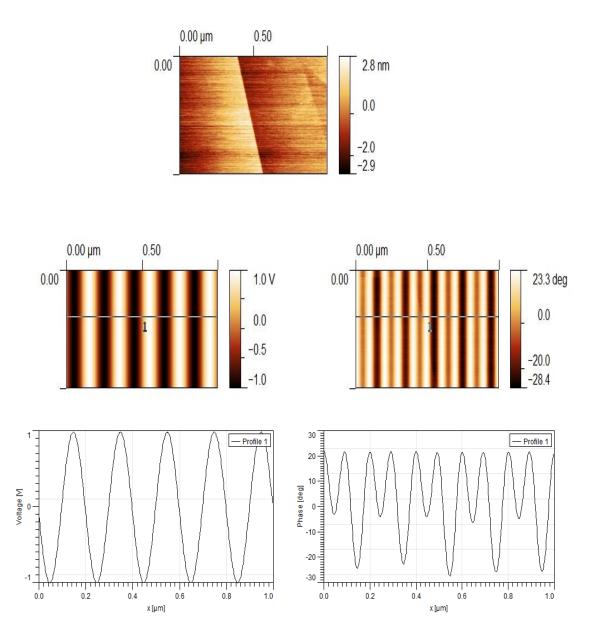

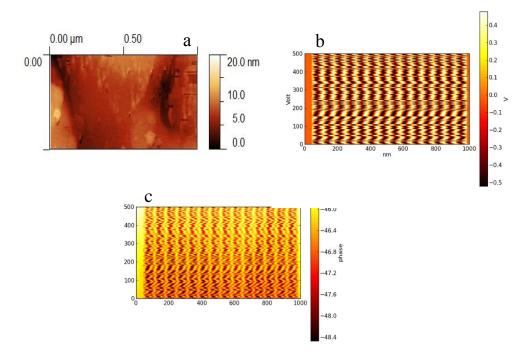

| Figure 5.5: AFM captured image for graphite surface for 1µm scan size. The applied bias and corresponding phase shift                                                                                                                                                                                                                                                                                                                                                            |

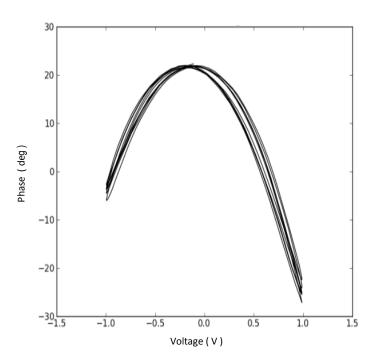

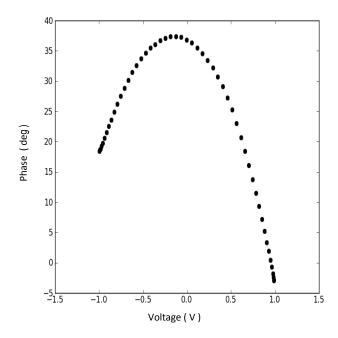

| Figure 5.6: Phase- voltage calibration curve of AC sinusoidal signal at 1V and 10 Hz. The tip height is 20 nm, scan rate 1 Hz and scan size is 1µm                                                                                                                                                                                                                                                                                                                               |

| Figure 5.7: Phase-voltage parabola image for 5nm scan size, 1 Hz scan rate, frequency 10 Hz and bias 1V                                                                                                                                                                                                                                                                                                                                                                          |

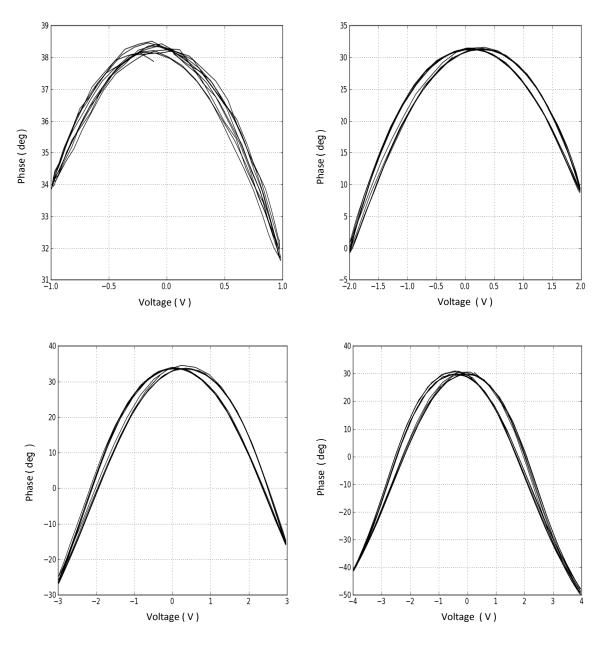

| Figure 5.8: Phase-voltage parabola with different tip height 20nm, 50nm, 70nm, 100 nm, 150nm. Scan size 5nm, tip bias 4.5V and frequency 12 Hz                                                                                                                                                                                                                                                                                                                                   |

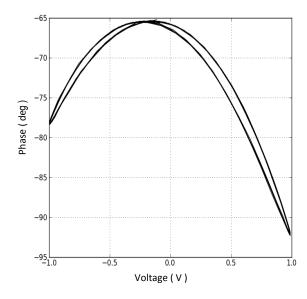

| Figure 5.9: Phase-voltage parabola with tringle wave form of bias 4.5V, frequency 12Hz and tip height 20nm), 50nm, 150nm bottom                                                                                                                                                                                                                                                                                                                                                  |

| Figure 5.10: Phase-voltage calibration curve for various tip biases 1, 2, 3, and 4V. The signal frequency is 10 Hz, tip height 20nm and scan size is 1µm140                                                                                                                                                                                                                                                                                                                      |

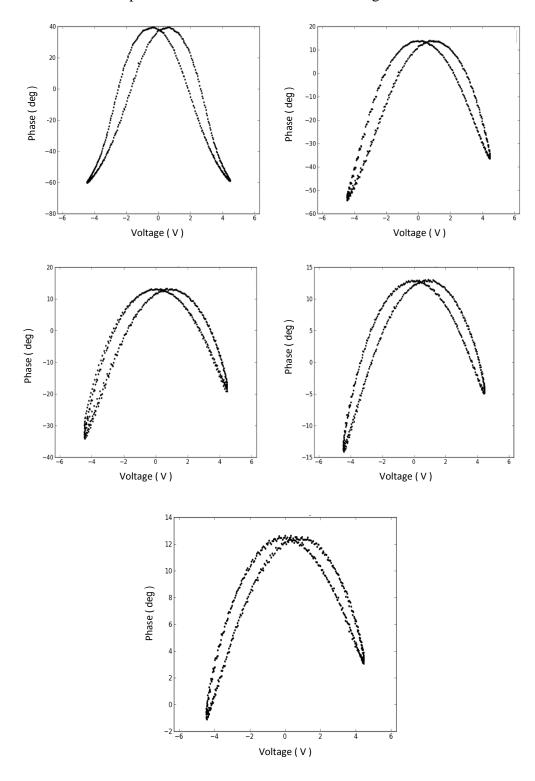

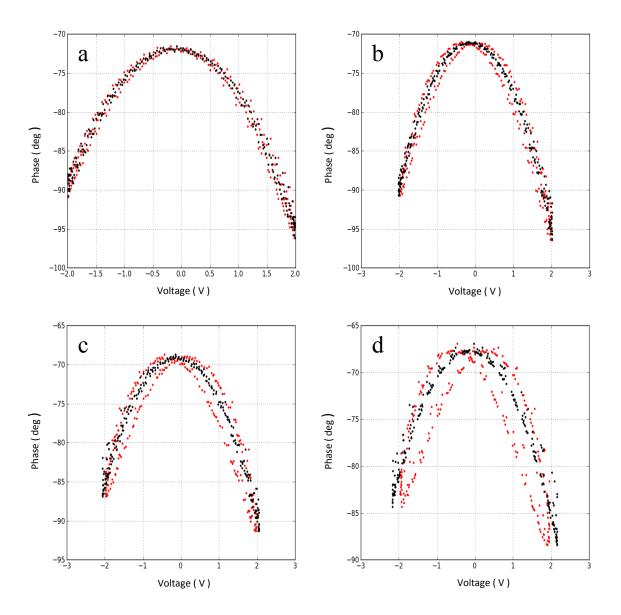

| Figure 5.11: Phase-voltage parabola for sinusoidal wave form of varied frequency at 2Hz, 5Hz, 10 Hz, 15 Hz, 20 Hz and 25 Hz, tip bias 4.5V, and 20nm tip height141                                                                                                                                                                                                                                                                                                               |

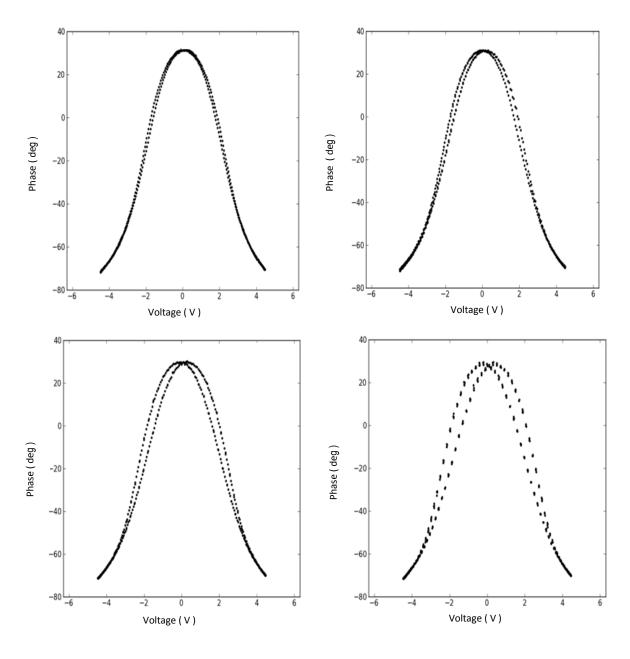

| Figure 5.11b: Phase-Voltage parabola for sinusoidal wave form at frequency 20 Hz and 25 Hz .Tip bias 5.4 V and 20 nm was tip height142                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

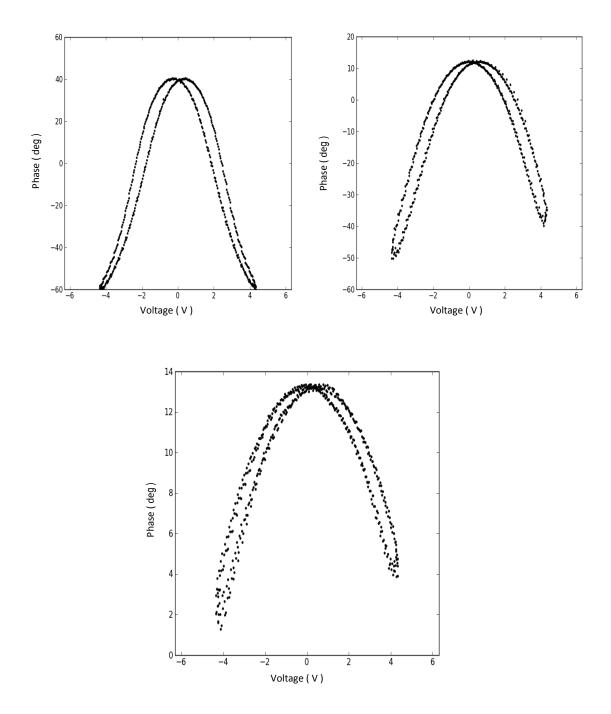

| Figure 5.12: Phase-voltage curves after connecting $8M\Omega$ resistance at frequency $2Hz$ , $5Hz$ , $12Hz$ , $15Hz$ , $20Hz$ , and $30Hz$ . Tip bias is 4.5V, tip –sample separation $20nm$                                                                                                                                     |

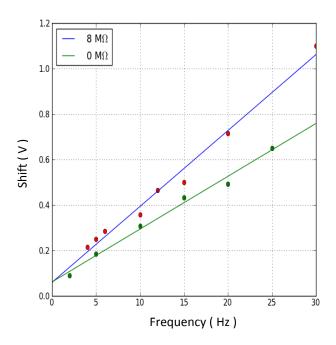

| Figure 5.13: Parabola shifts as a function of frequency with and without connecting 8 $M\Omega$ resistance                                                                                                                                                                                                                        |

| Figure 5.14: The phase-voltage calibration curve for only half of signal145                                                                                                                                                                                                                                                       |

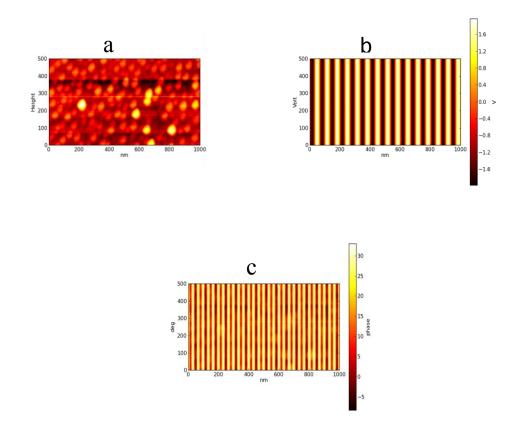

| Figure 5.15: a), Topography, b), bias of signal frequency of 30 Hz, c), the resulting phase shift obtained by using the new software                                                                                                                                                                                              |

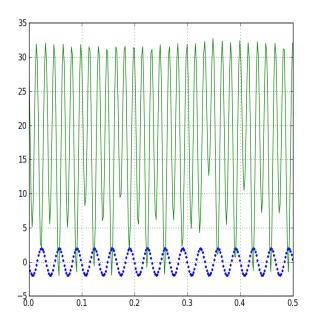

| Figure 5.16: The measured voltage data and corresponding phase for first row obtained from figure 5.15. The applied tip bias is 2V, frequency 30 Hz                                                                                                                                                                               |

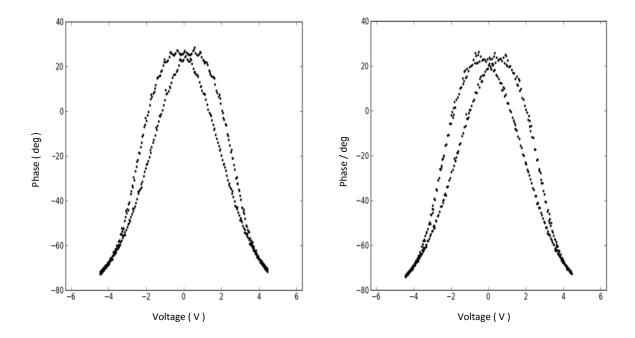

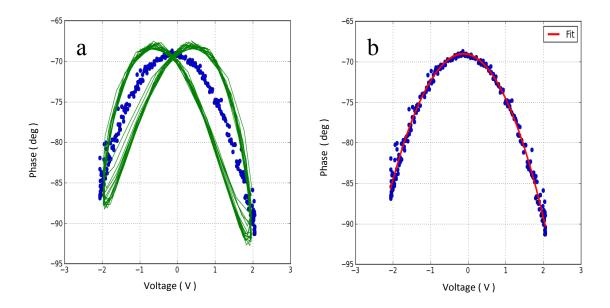

| Figure 5.17: Phase-voltage calibration curves before and after applying time delay for different frequencies. a),10 Hz, b) 20 Hz, c), 30 Hz, d), 50 Hz with tip height 20 nm for all                                                                                                                                              |

| Figure 5.18: An improvement in phase-voltage calibration curve after applying the effect of time delay. The image is for $f=30$ Hz, $d=20$ nm on gold surface. a), green line shows data distribution before applying time delay correction and blue circles indicate data after correction. b), the image after fitting the data |

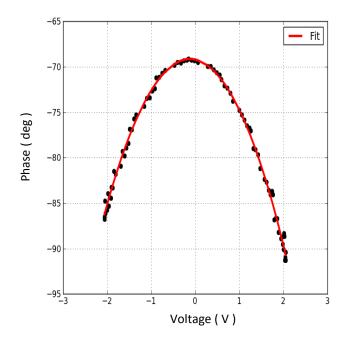

| Figure 5.19: Phase-voltage calibration when nside= $40$ , $f$ = $30$ Hz, tip bias= $2V$ , tip height = $20$ nm, and scan size = $1\mu$ m                                                                                                                                                                                          |

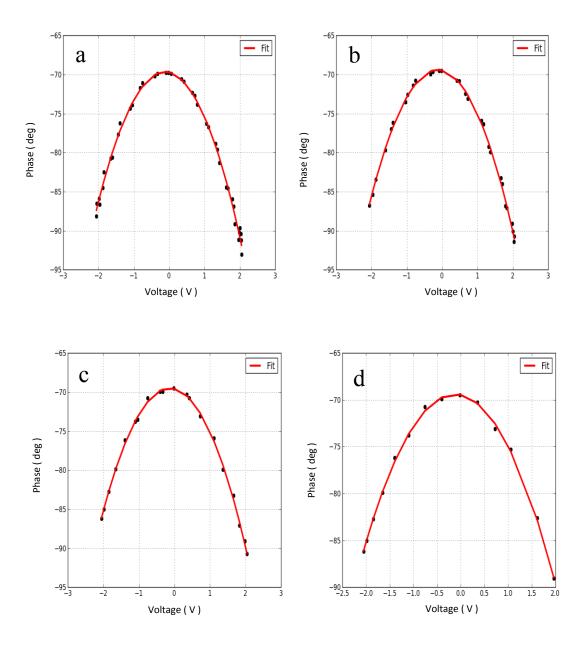

| Figure 5.20: Phase-voltage calibration curves for different values of nside. a) nside= $20$ , b) nside= $15$ , c) nside= $10$ , and d), nside= $10$ . All images for gold Au(111)/mica, tip bias= $10$ , tip height= $10$ nm, and $10$ Hz                                                                                         |

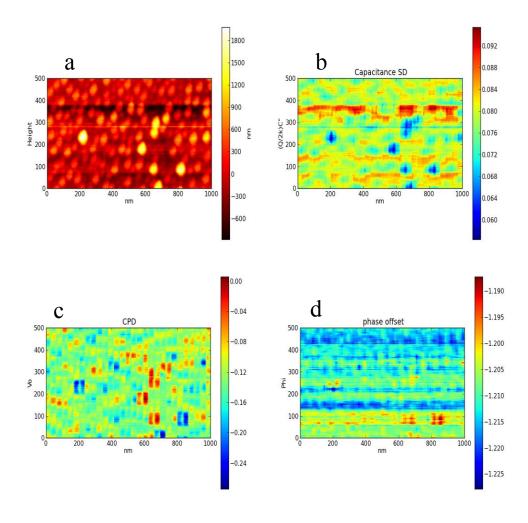

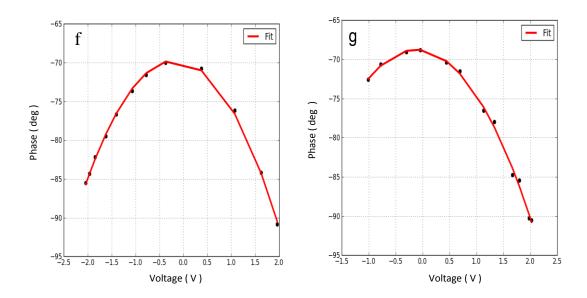

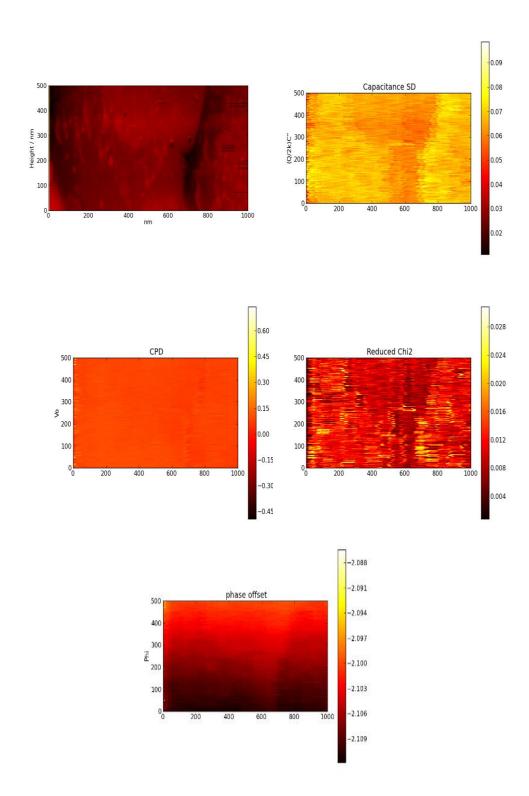

| Figure 5.21: a) Gold topography, b) the second derivative of capacitance, c) 2D images of CPD, d) phase offset, e) reduced chi square. The images taken for $d=20$ nm, $f=30$ Hz, delay = 0.73 msec, nside=6                                                                                                                      |

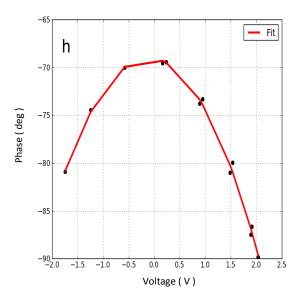

| Figure 5.22: a) MDMO-PPV/PCBM surface topography, b) second derivative of capacitance, c) 2D images of CPD, d) phase offset. The images taken for $d$ =20 nm, f=30Hz154                                                                                                                                                           |

| Figure 5.23: a) Surface topography of Au(111)/mica, b) random AC applied bias to the tip in contrast with Figure 5.15b, c) the resulting phase shift                                                                                                                                                                              |

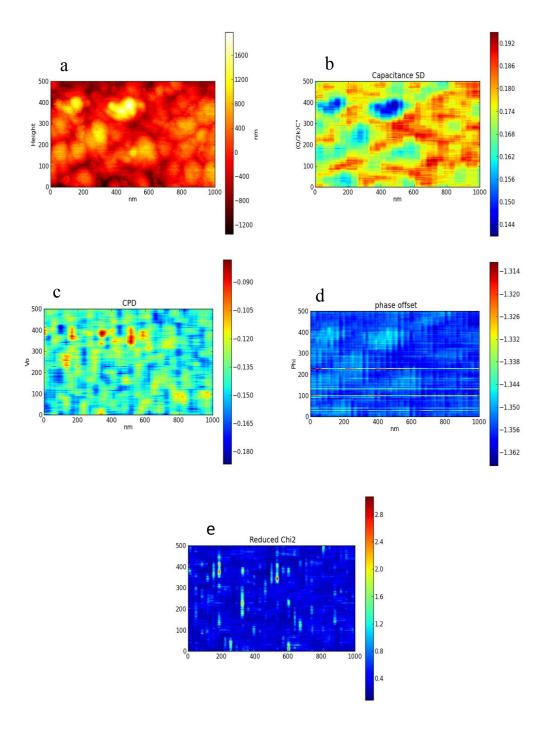

| Figure 5.24: 2D images of Au(111)/ mica surface topography, second derivative of capacitance, CPD, the phase offset and related reduced chi square at tip bias $0.5 \text{ V}$ , $f = 30 \text{ Hz}$ , $d = 20 \text{nm}$                                                                                                         |

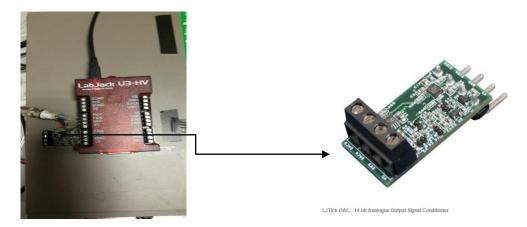

| Figure 5.25: LabJack U3-HV -USB Multifunction data acquisition                                                                                                                                                                                                                                                                    |

| Figure 5.26: EFM experiment set up with controlling program                                                                                                                                                                                                                                                                       |

| Figure 5.27: potential line profiles at $V_d = 0$ , 1, 2, 3, 4 V and $V_g = 0$ V with grounded source. The second figure in the right is a topography image which reveal the position of two electrodes and channel, Aspect ratio is $2/1$                                                                                        |

| Figure 5.28: 2D images for W1000L30D corresponding to the above profiles for $Vd=0$ 1, 2, 3, 4, 5 V                                                                                                                                                  |

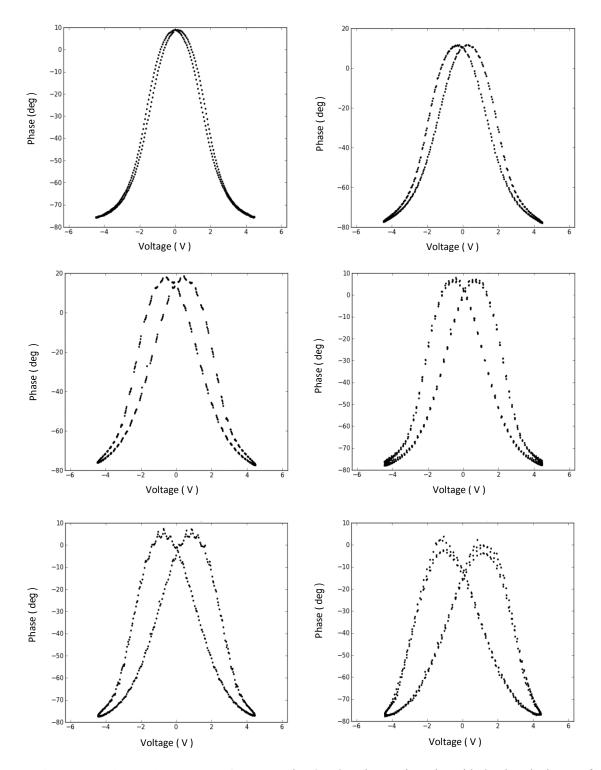

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.29: Effects of time delay changes on potential profile for 1V drain bias162                                                                                                                                                                 |

| Figure 5.30: Effect time delay on potential profile for W1000L30D operating devic under drain bias $V_d = 5$ V and $V_g = 0$ V                                                                                                                       |

| Figure 5.31: The optimal time delay needed for fitting of parabola at drain bia 6V                                                                                                                                                                   |

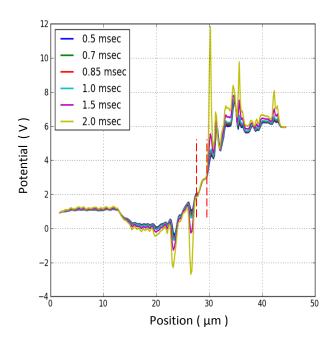

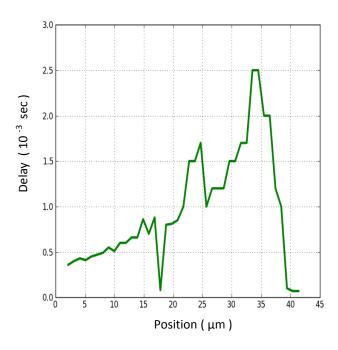

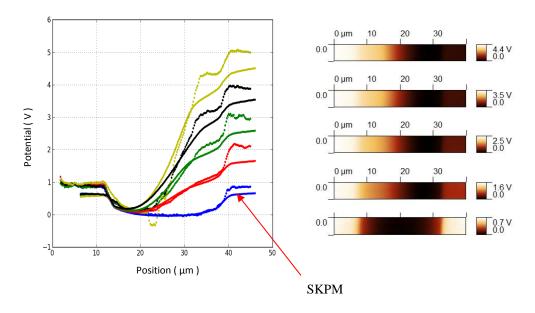

| Figure 5.32: Potential profiles comparison in SKPM (solid lines) and EFM-phase mod (dotted lines) for $V_g = 0$ V and $V_d = 0$ , 1, 2, 3, 4 V. SKPM and EFM profiles confirm Al diffusion region close to the drain which appeared as a flat region |

## List of tables

| Table 1.1: The work functions for some interesting metallic elements                                                                                                                  | 19 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1: The value of roughness (rms) of captured overall AFM images according to decane concentration in blend                                                                     |    |

| Table 3.2: Summarized maximum, minimum, and average mobility results obtained or transistors as a function of anisol:decane ratio                                                     |    |

| Table 3.3: Electrical properties of drop casted TIPS-PEN and aPS blended OFET                                                                                                         | 64 |

| Table 3.4: Summary of mobility measurements presents the average, minimum, and average mobility according to the blend composition                                                    | 72 |

| Table 3.5: Comparison of mean saturated mobility of pure TIPS-PEN and its blend wire polystyrene on PVP and SiO <sub>2</sub>                                                          |    |

| Table 4.1: The electric performance of In <sub>2</sub> O <sub>3</sub> devices of 100nm thick SiO <sub>2</sub> dielectric according to the device dimension W and L and film thickness | 87 |

## List of Abbreviations and symbols

AFM Atomic force microscopy/ microscope

BCBG Bottom contact- bottom gate

C Capacitance

CPD Contact potential difference

D Drain

$\varepsilon_o$  Vacuum permittivity

E<sub>f</sub> Fermi level

EFM Electrostatic force microscopy

FET Field effect transistor

G Gate

HOMO Highest occupied molecular orbital

*K* Dielectric constant

LUMO Lowest unoccupied molecular orbital

MDMO-PPV Poly[2-methoxy-5-(3,7-dimethyloctyloxy)-1,4-phenylenvinylene]

MOS Metal-oxide semiconductor

OFET Organic field effect transistor

OM Optical microscopy/ microscope

OS Organic semiconductor

OSM Organic small molecule

P3HT Poly(3-hexylthiophene-2,5'-diyl)

PCBM Phenyl-C61-butyric acid methyl ester

S Source

SC Semiconductor

SKPM Scanning Kelvin probe microscopy

SP Surface potential

SPM Scanning probe microscopy

TCBG Top contact-bottom gate

TCBG Top contact-bottom gate

TFT Thin film transistor

TIPS-PEN 6,13-bis(triisopropyl-siylethynyl) pentacene

### **Publications**

- 1. Isam Abdullah<sup>a</sup>, He Lan,<sup>b</sup> John Morrison,<sup>b</sup> Ahmed Alharbi, <sup>b</sup> J Emyr Macdonald<sup>a</sup> and Stephen G. Yeates<sup>b,\*</sup> The effect of formulation on the morphology and crystallization of thin film 6,13-bis(triisopropylsilylethynyl-pentacene based semiconductors.

- (a) School of Physics and Astronomy, Cardiff University, The Parade, Cardiff CF24 3AA, U.K. (b) Organic Materials Innovation Centre, School of Chemistry, The University of Manchester, M13, 9PL, Manchester, United Kingdom.

#### Submitted to Thin Solid Films

2. Olga Kryvchenkova\*¹, Isam Abdullah², J. Emyr Macdonald², Martin Elliott², Thomas D. Anthopoulos³, Yen-Hung Lin³, Petar Igić¹, Karol Kalna¹, Richard J. Cobley¹ "A non-destructive method for mapping metal contact diffusion in In₂O₃ thin-film transistors''

<sup>1</sup>Electronic Systems Design Centre, Swansea University.

#### Submitted to ACS Applied Materials and Interfaces

#### **Patent**

**UK Patent Application No. 1514732.5**

"Generic Modulation Analysis Approach For Scanning Probe Microscopy"

Isam Abdullah, J. Emyr Macdonald, Martin Elliott

#### Filed and Submitted

#### Conferences

- 1. Conference of science of inkjet and printed drop 2011 London, Nov.2011. Institute of physics, London UK  $\,$

- 2. Conference of postgraduate students 2012. Cardiff University School of Physics and astronomy, Sep20I2. Cardiff UK.

<sup>&</sup>lt;sup>3</sup>Department of Physics and Centre for Plastic Electronics, Blackett Laboratory, Imperial College London.

## Acknowledgment

#### Put God in the centre and everything will come together

Every successes I have had are due to the gorgeous people around me who I owe a lot of thanks. Firstly, I would like to express my deepest thanks to my supervisors Professor J.E.Macdonald and Dr.M.Elliot, for giving me support and encouragement throughout my research work. I highly appreciate them for guidance, consultations, correcting my mistakes, and listening to my ideas and providing fruitful discussions.

A huge acknowledgment must go to my mother for her confidence in me during childhood which made me believe I could fulfil any goal and achieve any target. I am deeply thankful to my awesome wife Muzhda whose patience, love, ongoing support through my many years of academic study made this thesis possible. A big thanks to my children, brothers, sisters, and all relatives who have always been there to share my joys and sorrows along the way.

Thanks to my friends in the research group; Rangeen, Athraa, Adam, and Susanne for assistance and a lovely friendly atmosphere in our lab. My gratitude to Mr. R Tucker for his help on the technical side.

Finally, a special acknowledgment to the Iraqi Cultural Atteche and Salahaddin University for financial and ongoing support.

#### **Abstract**

Organic and inorganic-metal oxide thin film transistors can be solution-processed, providing large area, low cost and low processing temperature leading to strong industrial and research interest. The nanoscale properties of each material system have been investigated using scanning probe techniques.

Pentacene is a model small molecule organic semiconductor but it is an air sensitive material and insoluble. However, its derivative 6,13-bis(triisopropyl-silylethynyl) pentacene (TIPS-PEN) is amenable to solution processing. The motivation to study TIPS-PEN is not to chase performance figures only but to investigate how the solution deposited film topography can be controlled by varying the solvent composition and the insulating polymer binder concentration. We report the effect of anisole / decane binary solvent mixture and the subsequent addition of low percentage weight of (atactic amorphous polystyrene) aPS on the surface morphology of TIPS-PEN thin films. It was found that addition of up to 20 wt% decane has little impact on micro-scale crystal morphology but has a significant influence on the growth mode, mean grain size and terrace roughness. The effect of the TIPS-PEN / aPS blend ratio up to 20 wt% of aPS in drop-cast thin film was similarly investigated on untreated SiO<sub>2</sub> and on poly(4-vinylphenol) ( PVP) interlayers. It is found that addition of aPS has a vital effect on macroscopic crystal properties such as surface coverage, unity of orientation, long range order, and average field effect mobility. It also changes the surface morphology and layer ordering on the nano-scale. Mobility values obtained from PVP treated surface were higher than those from SiO<sub>2</sub> surface by five times, which was consistent with preferred TIPS-PEN crystal growth on hydrophobic surface PVP of low surface energy.

Indium oxide (In<sub>2</sub>O<sub>3</sub>) is an n-type (electron transport), optical transparent with wide bandgap values between 3.5 and 4 eV, and high performance semiconductor. Spin coating was used to prepare indium oxide thin film transistors (TFT) of two different thicknesses of the device channel.

As the thickness of the In<sub>2</sub>O<sub>3</sub> active layer is increased, the device mobility increases, the threshold voltage is shifted in the negative direction, off-drain current is increased, and on-drain current is less pronounced. A systematic study was carried out to investigate the transistor stability under bias stress.

Applying a positive gate bias stress to indium oxide transparent TFTs was found to induce a parallel shifts of threshold voltage in positive direction without changing the device mobility or the subthreshold gate voltage swing.

Scanning Kelvin Probe Microscopy (SKPM) was used to study the surface potential distribution of operating devices under a range of drain and gate biases. The potential profiles showed evidence of metal contact diffusion into the channel region which appeared as a flatting of the profile close to the drain electrode. The experimental data was confirmed and complemented with simulation results for contact material diffusion into the In<sub>2</sub>O<sub>3</sub> channel.

A new method of performing Electrostatic Force Microscopy (EFM) was developed and applied to the In<sub>2</sub>O<sub>3</sub> TFT. The tip bias was modulated and the resulting phase difference between the cantilever response and the applied bias was recorded. The measurements were affected by a time delay, likely to be caused by capacitive charging of the semiconductor beneath the tip. The effects of the time delay were corrected by the use of an inverse filter in the analysis software developed. This new version of the EFM-phase method was applied to the operating biased In<sub>2</sub>O<sub>3</sub> TFTs and the results compared with those obtained with SKPM.

## Chapter One

## Introduction

The field of nanomaterials research has emerged in the last three decades. It concentrates on the characterisation, manipulation, creation and development of materials at nano-meter length scales. Some materials, which are well understood in the bulk phase offer interesting new properties when the size is decreased to the nano-meter length scale. Nanophysics and nanotechnology are interdisciplinary fields involving materials whose components and structures, due to their nanoscale size, have surprising or enhanced properties. The processing and manipulation of such materials on the nanoscale as well as the fabrication of devices with new sustainable approaches are of paramount importance in view of potential technology based on these materials.

Studies within this area are focused on understanding their properties in order to devise new technologies and, ultimately, to commercialize new devices. Potential applications include: smaller electronic components [1], compact memory [2], more sensitive sensors [3], and energy efficient and faster computers [4].

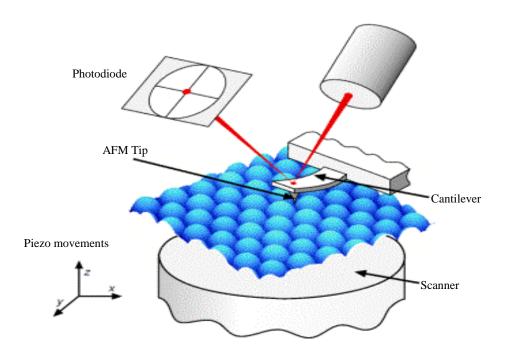

Study of materials at the nanoscale requires imaging and manipulation tools to achieve the goal. In 1986 Binning *et al.*[5] invented Atomic Force Microscopy (AFM) as an extremely versatile tool for imaging of conducting and non-conducting sample topography. AFM detects piconewton local forces with nanometre lateral high resolution [6, 7]. In this technique the sample surface is scanned by a sharp tip of nanometric size fixed to a cantilever. During scanning, different forces (van der Waals, magnetic, capillary, electrostatic) disturb the probe's equilibrium condition. The tip-sample interaction forces is measured by monitoring the deflection of the cantilever. The cantilever deflection is in turn usually measured by an optical lever technique [8, 9] in which a laser beam is focused close to the end of the cantilever Figure 1.1. The reflected beam is detected by a quadrant photodiode which produce a voltage difference between two halves of the photodiode, where the voltage on each half is proportional to the light intensity illuminating it. In principle, the sample image could be obtained by

plotting the cantilever deflection versus its position on the surface. In practice it is much more straightforward to maintain a fixed force between tip and sample by adjusting and recording the height position of the translation stage with a feedback loop.

Figure 1.1: Schematic Atomic Force Microscopy operation. The tip is attached to the cantilever. Tip-sample interaction leads to cantilever deflection which is monitored by Photodiode sensitive to the reflected beam at the tip back side.

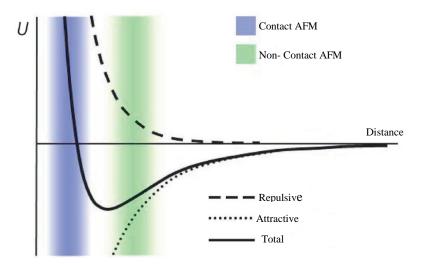

Generally, two modes of scanning in AFM measurements are used; the contact and the non-contact mode. In the contact mode, the tip is kept in physical contact with the surface and operates in the region where the resultant tip-sample interaction is repulsive with a mean value of order of 10<sup>-9</sup> N. The major drawback of this mode is the possibility of distorting the sample surface and damaging the tip as the cantilever drags along the surface Figure 1.2 illustrates tip- sample interaction as a function of surface separations.

Figure 1.2: The tip-sample interaction as a function of the distance. The minimum potential occurs at a typical distance of about 1-2 nm.

The non-contact mode operates in the region where the resultant tip-sample interaction is predominated by the force of attraction. If the tip is scanned at a constant height, there would be a risk that the tip may collide with the surface causing crushing to both the tip and the material under consideration; hence, in most equipment a feedback mechanism is employed to adjust the tip-to-sample surface distance to maintain a constant force between the tip and the sample. Normally, the monitored sample is mounted on a piezoelectric tube is adjusted vertically (the z-direction) to maintain a constant force, while scanning the sample laterally in the *x* and *y* directions.

Intermittent-contact mode, or tapping mode, is another potent technique to probe sample topography with high resolution. In this mode, the cantilever oscillates at or close to its resonant frequency, with the oscillation amplitude being proportional to the amplitude of the AC signal from quadrant photodiode. During scanning in x and y, the feedback loop adjusts z to maintain a constant amplitude (as a fraction of amplitude when the tip is retracted from the surface). Since the tip does not remain in constant contact with the surface, this mode is less destructive to the surface.

The most critical component in AFM is the cantilever spring constant. To achieve excellent sensitivity, a large deflection for a given force is desirable, requiring a soft cantilever (small spring constant). On the other hand, high resonance frequency is best to minimize sensitivity to mechanical vibration and to allow a reasonable high scan speed. A third condition for enhancement of AFM images is the tip sharpness, which is highly recommended for good spatial resolution.

In this thesis, we consider transistor materials which are alternatives to crystalline silicon. Of these, amorphous silicon (a-Si) is the predominant semiconductor used for transistor manufacturing, coming second behind single crystal silicon for use in industry. Amorphous silicon is superior to the polycrystalline form from the viewpoints of processing temperature and device uniformity. However, the carrier mobility in amorphous silicon a-Si:H is of order of 1 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> which is lower than crystalline silicon by about one or two orders of magnitude. The limited mobility in a-Si:H arise from the hopping nature of carrier transport between localized states and band conduction is not achieved [10]. Also, its high photo-induced instability remain the key issues that limiting its applicability[11]. Furthermore, silicon based device are less interesting for transparent electronics because of its rather small band gap and lack of transparency [12].

Among the most interesting materials, organic semiconductors (OS) have been intensively studied and considered as potential candidates to replace amorphous silicon thin film transistors (TFTs). A primary interest for organic materials in thin film transistors is their compatibility for low cost and low temperature processing. Offering possibility of wide use in electronic devices. Kelley *et al.* [13] reported that, with considerable purification, well controlled dielectric, and optimized conditions, TFT mobilities from 0.5 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> to near single crystal values ~ 3 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> could be attained. Pentacene as a small organic molecule has exhibited the highest mobility [14], better on-off ratio, and better reliability then most other OS [15]. Hence, it is a possible candidate to complement and replace the amorphous silicon technology in many electronics applications. Since then, a new hope has been opened in use of organic small molecule (OSM) as a popular material into electronic device fabrication. However, the major drawback of pentacene is that it is insoluble in organic solvents at room temperature.

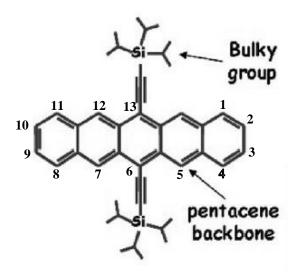

In 2001, Anthony *et al.* [16] reported that adding of functional groups to the positions at 6 and 13 on the pentacene ring has an effect on solid state ordering and the electronic properties of the resulting crystal. Moreover, the resulting molecule should has solubility in the majority of organic solvents and the substituents induce ability for pistacking array to enhance intermolecular orbital overlap. The soluble pentacene derivative, 6, 13-bis(triisopropylsilylethynel)(TIPS) pentacene (TIPS-PEN) can grow crystalline thin films from solution and composed of large crystal domain suitable for organic FET fabrications [17]. Figure 1.3 shows the molecular structure of TIPS-PEN.

Figure 1.3: The molecular structure of 6,13-bis(triisopropyl-siylethynyl) pentacene (TIPS-PEN)

The performance of organic electronic material is quickly enhanced especially with improved device mobility and controlling thin film surface topography. Solution processable blends of highly crystalline (TIPS-PEN) with insulating polymer is a promising approach to provide, large crystals, high mobility, good film uniformity [18], and small device to device variation of organic field effect transistor (OFET).

On the other hand, metal—oxide semiconductors (MOS) have attracted significant interest [19, 20] because it is a unique class of materials which are transparent and have good conductivity[21, 22].

A growing requirement for transparent semiconducting active materials leads to raised attention on the MOS for new sets of electronic devices, because of their high field-effect mobility, environment stability and optical transparency [23].

This interest is driven by a constantly growing requirement for high performance device using cheap processing methods, compatible with temperature sensitive substrates. One metal oxide semiconductor that gained significance is the wide band gap indium oxide In<sub>2</sub>O<sub>3.</sub> Indium oxide can be processed by inexpensive and high throughput solutionbased deposition such as spin coating and inkjet printing[24]. Moreover, solution-based deposition of MO semiconductors constitutes a simple, high fabrication, low temperature, procedure suitable for large-area electronics. Hwang et al. [25] prepared solution based indium oxide TFT by spin coating method. The obtained In<sub>2</sub>O<sub>3</sub> device exhibits good uniformity, mobility of order of 2.6 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, and turn on voltage V<sub>on</sub> around 0V. Kim el al. [26] reported mobility around 2.3 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and I<sub>on</sub>/I<sub>off</sub> (on/off current) ratio of 10<sup>4</sup> for In<sub>2</sub>O<sub>3</sub> precursor (at 300 °C) for TFT of 300 nm SiO<sub>2</sub> gate dielectric and 30 nm Al source and drain. Han et al. [27] fabricated solution processed In<sub>2</sub>O<sub>3</sub> TFT by spin coating method. The synthesized thin film of indium oxide was annealed at different temperature ranging from 200 to 600 °C in air or in an O<sub>2</sub>/O<sub>3</sub> atmospheric environment. For TFT at 500 °C the device showed 55.26 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and  $I_{on}/I_{off}$  ratio about of  $10^7$ . However,  $In_2O_3$  TFT exhibited mobility between 0.8 to 22.14 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and  $I_{on}/I_{off}$  10<sup>5</sup>-10<sup>6</sup> for 200 – 300 °C under O<sub>2</sub>/O<sub>3</sub>. Also, they noted that the annealing atmosphere of O<sub>2</sub>/O<sub>3</sub> can yield TFTs with higher performance at low processing temperature. Vygranenko et al. [28] applied long term gate bias stress on indium oxide TFT of mobility 3.3 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and  $I_{on}/I_{off} \sim 10^6$ . The results showed fast recovery of threshold voltage of threshold voltage of a relaxed device.

This thesis is structured into six main chapters as follow:

Chapter two presents an introduction to TFTs and several electrical measurements including the threshold voltage, field effect mobility, and  $I_{on}/I_{off}$ , and so on. Likewise, we discuss the related mathematical formulas of operating device based on linear and saturation regions. Also, we introduce some important topical information about organic and metal oxide semiconductors.

In chapter three we discuss strategies for controlling the morphology and crystalline microstructure of soluble (TIPS-PEN) as an organic small molecule OSM of interest in fabrication of OFET. The first part of the chapter concentrates on the effect of evaporation-induced flow on the drop cast dried film by controlling binary solvent composition. The effect on surface topography, roughness, and device mobility of the minor solvent (decane) composition will be discussed. The effect of adding insulating polystyrene to the blend for the TFT active layer is discussed in the second part of the chapter. The effect on crystal micro-structure, nano-scale surface topography, roughness, and device mobility as a function of polystyrene and solvent concentration is also presented. Also, we compare large scale optical microscopy images, nano-scale AFM images, and device mobility on both SiO<sub>2</sub> and poly (4-vinyl phenol) PVP surfaces.

Chapter four of the thesis concentrates on In<sub>2</sub>O<sub>3</sub> as a metal oxide semiconductor TFTs. We present the main electrical and morphological properties of top contact (TC), bottom gate (BG) configuration of solution based indium oxide TFT (single and double spin coating). The primary aims of this study are three fold:

- 1. The study of device performance under gate bias stress and its effect on electrical properties of working transistor.

- 2. The use of Scanning Kelvin Probe Microscopy (SKPM) to map the local surface potential in In<sub>2</sub>O<sub>3</sub> metal oxide semiconductor TFTs. We provide direct evidence for the diffusion of Al from drain electrode into the channel, which could prove to be a useful non-destructive probe of metal diffusion at electrodes. We also demonstrate the use of SKPM to detect trapped charge at the interface between the dielectric and the channel.

- 3. We discuss a new simple approach to detect metal diffusion at electrodes using conventional AFM with biased electrodes. This is backed up by modelling performed by colleagues at Swansea University.

In chapter five, we start with the fundamental principles of electrostatic force microscopy EFM and discuss its extension to a mode developed at Cardiff which involves measurements of the phase difference between the cantilever response and the driving signal as a function of applied tip bias.

The power of this approach has been considerably enhanced by the use of simple model in the analysis to correct for experimental time delay related to electrostatic charging. This has been the topic of a recently submitted patent application. An outline of the software developed for this is presented.

Finally in chapter six, the thesis ends with a summary of content and of the main conclusions, together with suggestions for future works in the field.

## Chapter Two

## Theoretical background

#### 2.1 Introduction

Field effect transistors (FET) and circuits based on semiconductors other than silicon have experienced impressive developments in both performance and reliability. As present research moves toward areas like cheap manufacturing techniques and their application in large-volume, inexpensive disposable electronics. Solution deposition of organic and metal oxide semiconducting [29-31] materials as active layers in FET attract interest as a potential alternative of traditional silicon based technology. The main benefit is that layers of these materials can be deposited and patterned at low/room temperature by solution processing [32, 33], making them very suitable for low cost, easily produced, large area electronics and for inexpensive disposable electronics.

The semiconductor layer is not the only factor that determines the device performance. Device architecture, processing, and choice of electrodes are important as well. Moreover, the role of the gate dielectric and the charge trapping mechanism are also important.

In this chapter we will give some descriptions on the working principles of thin film transistors and the use of output and transfer characteristics to extract device parameters. Moreover, we will give a brief discussion on organic semiconductor (OS) and the process of charge transfer. Also, the factors that affect the charge transfer such as the HOMO and LUMO levels, impurities, and temperature are also mentioned. Finally, we conclude the chapter with a short discussion of the metal oxide semiconductor device.

#### 2.2 Thin film transistors

Thin film transistors (TFT) are field effect transistor which can be made by deposition of a metallic electrode and thin film of semiconducting materials as well as dielectric layer on a supporting substrate. The deposited film which forms a conducting and active material can be a polymers[34-36], organic small molecules[37, 38], organic materials[39, 40], and metal oxide semiconductor[41, 42]. Many researchers have used different kinds of thin film (TF) deposition methods such as drop casting, spin coating, and inject print. Conventionally, the most common application of TFTs is in liquid crystal displays (LCD) -in television sets, mobile phones and computer monitors- to improve the image contrast and quality.

Recently, demands in the flat panel industry for high resolution, low power consumption, and large size flat panel displays necessitate using new semiconductor materials such as metal oxides. Metal oxides have high mobility, good homogeneity and are easily fabricated at room temperature. Crucial factors for improving device performance and stability include the quality and stability of the gate dielectric, suitable metallic electrodes, and control over threshold voltage changes. In this thesis we focused on two types of semiconductors as a thin film layer in field effect transistors (FET) devices. TIPS-PEN, a model small molecule organic semiconductor and indium oxide as a metal oxide semiconductor.

#### 2.3 Thin film transistor structure

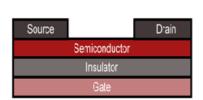

A variety of TFT structures can be prepared, with different configurations of the gate, source and drain electrodes. Each architecture is selected to optimise device performance for the target application. Figure 2.1 shows two such structures, with the top contact bottom gate (TC/BG) and with the bottom contact bottom gate (BC/BG) geometries. This choice affects the approach to deposition of the semiconductor layer. In the top contact structure the source (S) and drain (D) are deposited on top of the semiconductor layer (staggered structure).

However, for the bottom contact design, the source and drain electrodes are first deposited onto the gate (G) dielectric, followed by deposition of the semiconductor

film. This design are described as a coplanar structure because the source and drain are in contact with the dielectric material, being coplanar with the conducting channel. The staggered configuration provides a larger area for charge injection into the semiconductor than for the coplanar geometry, resulting in lower contact resistance and better device performance[43] as the charge injection process to the interface probably occurs across the whole contact surface area rather than the edge of contact as in the coplanar geometry.

Figure 2.1: Basic structures for thin film transistor presenting top contact bottom gate (left hand side) and bottom gate bottom contact (right hand side).